MDPI

Article

# Novel Motor-Kinetic-Energy-Based Power Pulsation Buffer Concept for Single-Phase-Input Electrolytic-Capacitor-Less Motor-Integrated Inverter System

Michael Haider 1,\* Dominik Bortis 1D, Grayson Zulauf 1D, Johann W. Kolar 1D and Yasuo Ono 2

- Power Electronic Systems Laboratory, ETH Zürich, 8092 Zurich, Switzerland; bortis@lem.ee.ethz.ch (D.B.); grayson.d.zulauf@gmail.com (G.Z.); kolar@lem.ee.ethz.ch (J.W.K.)

- <sup>2</sup> Nabtesco R&D Center, Nabtesco Corporation Japan, Kyoto 600-8899, Japan; Yasuo.Ono@adcos.de

- \* Correspondence: haider@lem.ee.ethz.ch

**Abstract:** The motor integration of singe-phase-supplied Variable-Speed Drives (VSDs) is prevented by the significant volume, short lifetime, and operating temperature limit of the electrolytic capacitors required to buffer the pulsating power grid. The DC-link energy storage requirement is eliminated by using the kinetic energy of the motor as a buffer. The proposed concept is called the Motor-Integrated Power Pulsation Buffer (MPPB), and a control technique and structure are detailed that meet the requirements for nominal and faulted operation with a simple reconfiguration of existing controller blocks. A 7.5 kW, motor-integrated hardware demonstrator validated the proposed MPPB concept and loss models for a scroll compressor drive used in auxiliary railway applications. The MPPB drive with a front-end CISPR 11/Class A EMI filter, PFC rectifier stage, and output-side inverter stage achieved a power density of 0.91 kW L<sup>-1</sup> (15 W in<sup>-3</sup>). The grid-to-motor-shaft efficiency exceeded 90% for all loads over 5 kW or 66% of nominal load, with a worst-case loss penalty over a conventional system of only 17%.

**Keywords:** single-phase; electrolytic capacitor-less; VSD; PFC operation; single-phase to three-phase AC/AC converter; motor integration

Citation: Haider, M.; Bortis, D.; Zulauf, G.; Kolar, J.W.; Ono, Y. Novel Motor-Kinetic-Energy-Based Power Pulsation Buffer Concept for Single-Phase-Input Electrolytic-Capacitor-Less Motor-Integrated Inverter System. *Electronics* 2022, 11, 280. https://doi.org/10.3390/ electronics11020280

Academic Editors: Gabriele Grandi, José Matas, Carlos E. Ugalde-Loo and Fushuan Wen

Received: 23 December 2021 Accepted: 10 January 2022 Published: 16 January 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Mobility, transportation, and industrial systems are increasingly electric, from the drivetrain to the auxiliaries, driven by improvements in battery performance and lifetime, government and private mandates to reduce greenhouse gas emissions, and an improved user experience. This electrification includes the traction systems in electric vehicles, but the auxiliary systems must also be electrified with power-dense, efficient, and reliable power conversion stages under unique operating conditions and constraints. In particular, electromechanical systems—including pumps, compressors, and blowers—are required on nearly every vehicle and require VSDs for efficient operation.

An on-board compressor system for the air brakes of railway vehicles was considered here, as shown in Figure 1a. This oil-free scroll compressor [1]—selected for high pressure, low noise, and long maintenance intervals (see [2] for a comparison of compressors)—was used to charge the pressure tank that supplies the air brakes, pantograph, and other critical loads driven by air pressure, necessitating ultra-high reliability. As such, the compressor system is supplied from a tertiary traction transformer winding during normal operation ("grid operation"), as is typical for auxiliary railway applications [3], and from an onboard battery during startup or extended grid interruptions, with a reduced output power. The key specifications for this particular application are given in Table 1. While, in this work, the focus was on the single-phase to three-phase VSD power conversion system for this particular application, the requirements for single-phase to three-phase variable-speed conversion are quite general (e.g., a 10 kW, 230 Vrms, single-phase VSD in [4], or a single-phase to three-phase VSD with Power Factor Correction (PFC) operation in [5]).

Electronics **2022**, 11, 280 2 of 49

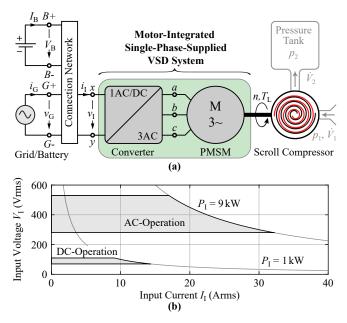

**Figure 1.** (a) Motor-integrated single-phase-supplied Variable-Speed Drive (VSD) system to drive the compressor of an air brake system for railway vehicles. The system can be supplied either from the tertiary winding (AC) of the traction transformer or an on-board battery (DC-supplied operation). (b) Required converter input range, including reduced power for DC-supplied operation.

With a VSD system required to increase compressor performance [6], the application needs a power electronics system to convert the single-phase AC—or DC, under battery operation—input voltage into a symmetrical three-phase voltage system, where the magnitude and frequency can be adjusted to control the motor speed (and, accordingly, output power). A three-phase Permanent Magnet Synchronous Motor (PMSM) was selected for high torque, low weight, high efficiency, and compactness [7]. The VSD was designed for 9 kW of output power (see Figure 1b), to meet the required 7.5 kW of mechanical output power (Table 1) while accounting for system losses and acceleration, must comply with CISPR 11/Class A [8], and must operate under unity power factor operation to minimize harmonic distortion and reactive grid power [9].

Table 1. Key system specifications.

| Air Flow Rate at Pressure                                                                                                                                        | $850 \mathrm{L}\mathrm{min}^{-1}$ , $0.83 \mathrm{MPa}$                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Nominal Speed $(n_{\rm N})$<br>Nominal Mech. Power, Grid $(P_{0,\rm N})$<br>Nominal Mech. Power, Batt. $(P_{0\rm DC,N})$<br>Nominal Grid Voltage $(V_{\rm G,N})$ | 3700 rpm<br>7.5 kW<br>1.0 kW<br>400 Vrms                                   |

| Grid Voltage Range ( $V_{ m G}$ ) Grid Frequency ( $f_{ m G}$ ) Battery Voltage Range ( $V_{ m B}$ ) EMI Standard (Input)                                        | 280 Vrms to 530 Vrms<br>50 Hz<br>70 Vdc to 120 Vdc<br>CISPR 11/Class A [8] |

Conventionally, these power conversion systems are realized with a two-stage system [10] comprising a front-end PFC rectifier, an electrolytic DC-link capacitor to buffer the power pulsation from the single-phase grid supply, and a VSD inverter to drive the motor and compressor [11]. For auxiliary motor drive applications, though, efficiency is not the primary concern—due to the low duty-cycle of operation—and the power density should be maximized for the space- and weight-constrained mobility application. The highest-power-density solution, in the end, is a motor-integrated drive system [12], which eliminates expensive shielded cables [13] and cable reflections [14], which allows for higher

Electronics **2022**, 11, 280 3 of 49

slew rates of the inverter stage power semiconductor switching voltage transitions and/or lower switching losses, exhibits better Electromagnetic Interference (EMI) behavior [12] from integration in a single housing, and allows for combined cooling of the electronics and motor [15]. Motor-integrated VSDs, in sum, result in lower installation and operating costs, but require the integration of all drive components—even the EMI input filter [16]. The requirement for electrolytic capacitors as the single-phase power buffer, though, prevents motor integration, with the elevated operating temperatures [17] of the integrated converter (85 °C to 105 °C) [18] degrading lifetime [19] and/or requiring substantial overdimensioning of these large capacitors.

For the highly desired motor integration of the converter system for these singlephase to three-phase drive applications, then, alternatives to the traditional two-stage approach with an electrolytic capacitor are required. Solutions that synergistically employ the components are considered first. Ultra-low-cost implementations use the grid voltage effectively as one of the motor line-to-line voltages and employ four power MOSFETs and a TRIAC [20], but do not allow a wider range of speed control. To utilize the motor star point as one of the connecting points to the single-phase grid, the motor leakage inductance may be utilized as a boost inductor [21], but this results in unacceptably high voltage stresses (twice the grid peak voltage) for this application, which already features a high-grid-input voltage. The same issue occurs in a low-cost implementation that employs a front-end PFC rectifier with only one bridge-leg and a split DC-link [22]. Coupled power electronics (rectifier to inverter) approaches, such as Z-source-based concepts [23] or matrix converters [24], typically feature an (integrated) active buffer for power decoupling [25], a basic requirement since the matrix converter does not include energy storage [26], which drives the complexity and high component stresses. Current-source structures [27], in the end, only replace the boost inductor with a DC-link inductor (since voltage-source inverters do not require an output filter here) while requiring bidirectional switches, and therefore do not improve the potential for integration. The synergistic approaches, then, do not hold the promise of eliminating the large energy storage components required to buffer the single-phase power pulsation—and if they do start to alleviate the requirement, the penalties appear unacceptably high.

Accordingly, this work proposes to use the motor (and load) inertia as a power buffer, eliminating the need for power buffering in the DC-link capacitors, an approach called the MPPB and introduced in [28]. A conventional two-stage structure was utilized, with a single-phase front-end PFC rectifier and a three-phase VSD inverter, with the power flow for a conventional system and the MPPB system shown in Figure 2a. Although particular rectifier and inverter topologies were selected and demonstrated here, the findings are applicable to any specific implementation of the rectifier and inverter.

The MPPB concept was previously proposed with the PFC rectifier omitted and the inverter stage directly supplied from a single-phase-grid diode bridge rectifier [29]. This concept results in a rectifier sine wave voltage at the DC-link, so the input current is only sinusoidal if the motor voltage stays below the rectified input voltage [30]. This concept, then, is limited to motors with a low back Electromotive Force (EMF) and/or applications where a large speed variation is acceptable—but in both cases, a unity power factor cannot be achieved. In [31], a solution to this problem was proposed, where a reactive current component was injected into the motor to keep the back EMF of the motor below the input voltage. Here, the PFC rectifier can indeed be omitted, but the small motor inductance leads to large motor currents and excessive losses. With this constraint and the large fluctuating DC-link voltage, which increase the system complexity, applications for this approach are restricted to drive systems with special low-voltage motors that do not operate at common voltages.

Electronics **2022**, 11, 280 4 of 49

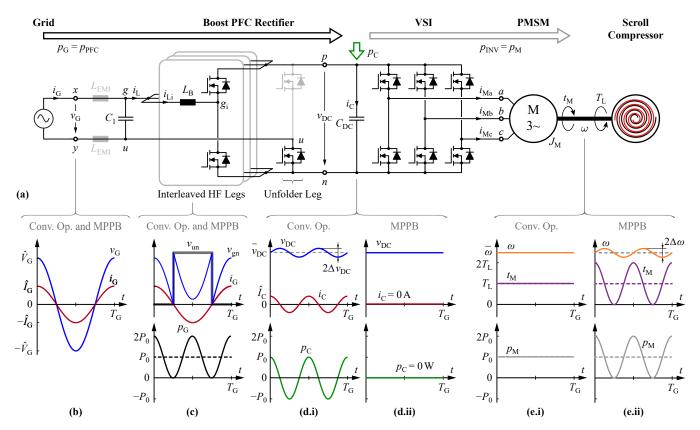

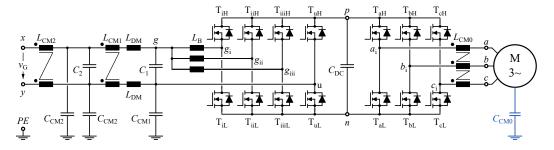

**Figure 2.** (a) Circuit diagram of the selected converter implementation, with a single-phase boost-type totem-pole PFC rectifier to achieve a sinusoidal input current and a conventional two-level three-phase variable-speed inverter that enable the speed control of the associated PMSM. The two converter stages are high-frequencywise, decoupled by a DC-link capacitor  $C_{\rm DC}$ . The power flow is indicated with arrows. (b-e) Characteristic voltage, current, speed, torque, and power waveforms (d.i.e.i) for conventional operation with an electrolytic capacitor  $C_{\rm DC}$ , which buffers the pulsating power drawn from the grid and (d.ii,e.ii) for the proposed MPPB concept, where the input power pulsation is buffered by the inertia of the motor and no electrolytic capacitor is needed.  $t_{\rm M}$  denominates the inner motor torque. In DC-supplied operation, the battery is connected to the input terminals x and y. © 2018 IEEE. Adapted, with permission, from [28].

In this work, a single-phase-supplied electrolytic-less VSD system with dedicated rectifier and inverter stages that realizes a high lifetime and reduced volume for motor integration is designed, modeled, and implemented. In Section 2, the rectifier and inverter topologies are selected, introduced, and evaluated with the concept and control of the novel proposed MPPB approach to eliminate electrolytic capacitors. In this section, the operational limits for the proposed approach are evaluated for different load cases. The novel control concept for MPPB operation is derived and explained in detail, with verification based on circuit simulation, and finally, the phase currents are investigated in detail to compare the performance of the novel MPPB approach to a conventional system. Section 3 details the implementation of the motor-integrated drive system with volume and loss distributions, including showcasing the motor integration that is uniquely enabled by the novel, proposed MPPB approach. Section 4 verifies the system operation in the time domain for the steady-state and transients, loss models across the full torque range, and EMI requirements and compares the system losses between the MPPB and conventional systems. In Section 5, the extended functionality required for the considered application is demonstrated, including ride-through and battery-supplied operation. The novel control structure can also be employed for DC-supply operation with a single structure that simplifies the implementation and maintenance effort of the system. Section 6 concludes and summarizes the MPPB approach and results of the work, with Appendices that specifically

Electronics **2022**, 11, 280 5 of 49

investigate low-speed operation in the context of the proposed approach (Appendix A), controller design and future enhancements (Appendix B) to reduce the DC-link voltage ripple (including novel feedforward terms), and the detailed phase currents under MPPB operation (Appendix C).

## 2. Topology Selection and Proposed MPPB Concept and Control

## 2.1. Topology

Although the proposed MPPB concept is applicable to a broad range of inverter and rectifier topologies, a particular configuration for the demonstration was selected in this paper to explain and, later, showcase the MPPB concept. Conventional systems in these applications utilize a two-stage design with a single-phase PFC rectifier, a large low- and high-frequency-decoupling DC-link capacitor, and a three-phase VSD inverter. A similar two-stage topology was desired here for a straightforward comparison and implementation of the MPPB concept relative to the state-of-the-art.

A single-phase PFC rectifier can be implemented with multiple topologies, components, and control schemes, and these options were reviewed extensively in [32]. A unidirectional boost PFC rectifier with a diode bridge, boost inductor, and transistor and diode pair is widely used for simplicity and low-cost [33]; here, instead, a totem-pole PFC with an unfolder bridge-leg (see Figure 2a) was selected to improve the performance by avoiding the diode conduction losses [34]. While Zero-Voltage Switching (ZVS) triangular-current-mode schemes could further reduce the semiconductor switching losses [35], a simple Pulse-Width-Modulation (PWM) scheme with a constant switching frequency is preferred for the simplicity of interleaving and operation across a wide AC input voltage range (see Figure 1b). Finally, with a DC-link voltage above 750 V (the peak voltage of the maximum grid voltage), 1200 V power semiconductors must be used, and Silicon Carbide (SiC) Metal Oxide Semiconductor Field Effect Transistors (MOSFETs) were chosen over Insulated Gate Bipolar Transistors (IGBTs) for the lower loss characteristics.

Similarly, a straightforward two-level, three-phase inverter utilizing SiC MOSFETs and directly connected to the motor [36] was selected for the power topology. With SiC MOSFETs and no output filter, a voltage slew rate limitation was required to prevent motor insulating aging [37], with the options and tradeoffs for this slew rate value and implementation highlighted in [38].

The resulting structure with the indicated power flow is shown in Figure 2a, with the grid and rectifier input waveforms under conventional operation shown in Figure 2b,c (see [34] for a more detailed explanation). This structure also supports the necessary DC-input operation, with the battery terminals directly connected to x and y. In this mode, the PFC rectifier operates as a conventional DC/DC boost converter.

# 2.2. MPPB Concept

At the single-phase grid input, the unity power factor operation dictates that the drive system behaves as an ohmic load with a sinusoidal input current  $i_G(t) = \hat{I}_G \cos(2\pi f_G t)$  in phase with the grid voltage  $v_G(t) = \hat{V}_G \cos(2\pi f_G t)$ , as shown in Figure 2b. The instantaneous input power, however, varies as:

$$p_{G}(t) = v_{G}(t) i_{G}(t) = P_{0} + \tilde{p}_{G}(t),$$

(1)

with  $P_0 = \hat{V}_G \hat{I}_G/2$  (see Figure 2c). A lossless system implies that  $p_G(t) = p_{PFC}(t)$  and  $p_M(t) = p_{INV}(t)$ , and an instantaneous power balance results in:

$$p_{\rm G}(t) = p_{\rm C}(t) + p_{\rm M}(t).$$

(2)

Thus, the twice-grid-frequency pulsation  $\tilde{p}_G(t) = P_0 \cos(2\pi f_P t)$  with  $f_P = 2f_G$  is then forwarded to the DC-link capacitor  $C_{DC}$ , under conventional operation, or, under the proposed MPPB approach, through the DC-link and the inverter to the motor.

Electronics **2022**, 11, 280 6 of 49

## 2.2.1. Conventional Operation with an Electrolytic Capacitor

First, system operation with a conventional approach, utilizing a large electrolytic capacitor at the DC-link, is outlined. The waveforms are shown in Figure 2(d.i),(e.i) for each stage.

Under constant speed  $\omega(t) = \bar{\omega}$  and constant torque  $t_{\rm M}(t) = T_{\rm L}$  operation, the motor power is constant ( $p_{\rm M}(t) = \omega(t) \, t_{\rm M}(t) = p_{\rm INV}(t) \equiv P_0$ ), as shown in Figure 2(e.i). With this constant power  $P_0$  and the twice-line-frequency power pulsation, from the grid input, a large intermediate DC-link capacitor  $C_{\rm DC}$  was used to cover the active power mismatch between the two stages, where the instantaneous capacitor power is:

$$p_{\rm C}(t) \equiv p_{\rm G}(t) - p_{\rm M}(t) = \tilde{p}_{\rm G}(t) = P_0 \cos(2\pi f_{\rm P} t)$$

(3)

and the average capacitor power is zero,  $P_C = \bar{p}_C(t) = 0$  W, as it must be for the periodic steady-state (see Figure 2(d.i)).

With a nearly constant DC-link voltage  $v_{\rm DC}(t) \approx \bar{v}_{\rm DC}$  and under the power balance of the capacitor  $p_{\rm C}(t) = v_{\rm DC}(t)\,i_{\rm C}(t)$ , the capacitor current must have an approximately sinusoidal waveform  $i_{\rm C} \approx \tilde{p}_{\rm G}(t)/\bar{v}_{\rm DC}$  with amplitude  $\hat{I}_{\rm C} \approx P_0/\bar{v}_{\rm DC}$ . This capacitor current causes a voltage ripple with amplitude  $\Delta v_{\rm DC}$ , which is typically limited to a certain percentage of the DC-link voltage  $v_{\rm DC}$  to provide a nearly constant voltage (as previously assumed) to the inverter. The required capacitance value  $C_{\rm DC}$  is:

$$C_{\rm DC} = \frac{P_0}{2\pi f_{\rm P}} \, \frac{1}{\bar{v}_{\rm DC} \Delta v_{\rm DC}},\tag{4}$$

and for this application, a value in the mF range is required. This large capacitance value is, therefore, typically realized with electrolytic capacitors. The capacitor current, in addition to causing the voltage ripple, also results in a low-frequency Root Mean Square (RMS) current stress of the capacitor of  $I_{C,LFrms} = \hat{I}_C/\sqrt{2} = P_0/\bar{v}_{DC} 1/\sqrt{2}$ .

For the nominal operating point of  $f_{\rm G}=50\,{\rm Hz}$ ,  $\bar{v}_{\rm DC}=650\,{\rm V}$  (see Table 2),  $P_0=8\,{\rm kW}$ , and a selected  $\Delta v_{\rm DC}=20\,{\rm V}$  (see Figure 2(d.i)), the required capacitance is  $C_{\rm DC}=0.98\,{\rm mF}$  with a current stress of  $I_{\rm C,LFrms}=8.7\,{\rm A}$ . This DC-link capacitance can be realized with four 1 mF capacitors B43742A6108M000 [39] (rated for 500 V and 4.9 A at 105 °C), which are connected in a 2  $\times$  2 array. This DC-link capacitor alone corresponds to a box volume of 1 L (61 in³) and 6 W of losses before including the PFC and VSD high-frequency currents. This large—and required—electrolytic DC-link capacitor is a major limitation for power density, motor integration, and converter lifetime [40].

**Table 2.** Nominal operating point.

| Nominal Speed $(n_N)$                 | 3700 rpm |

|---------------------------------------|----------|

| Nominal Mech. Power, Grid $(P_{0,N})$ | 7.5 kW   |

| Nominal Grid Voltage ( $V_{G,N}$ )    | 400 Vrms |

| Grid Frequency ( $f_G$ )              | 50 Hz    |

| DC-Link Voltage ( $V_{DC}$ )          | 650 Vdc  |

To overcome these limitations, alternate capacitor-based Power Pulsation Buffer (PPB) buffer concepts have been proposed in the literature [41]. These circuits all contain an active switching stage and a buffer capacitor stage [42] (often separate, in series [43], or in parallel [44], from the existing DC-link capacitor) with a capacitor cycled with a large voltage ripple  $\Delta v_{\rm C}$ . With a larger voltage ripple, the required capacitance value is much smaller (according to Equation (4)) and enables foil- or ceramic-based capacitor implementations, but the additional active switching stages incur significant realization effort, complexity, and cost for the overall drive system.

Electronics **2022**, 11, 280 7 of 49

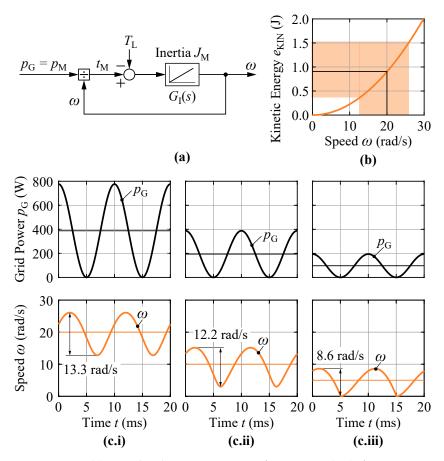

## 2.2.2. Motor Power Pulsation Buffer Concept

Rather than adding complexity to the drive system's electronics, the pulsating power component  $\tilde{p}_G$  can be removed from the converter system by enforcing  $p_C(t) \equiv 0 \, \text{W}$ , rather than only enforcing the periodic steady-state condition  $\bar{p}_C(t) \equiv 0 \, \text{W}$ . This condition is shown in Figure 2(d.ii). With this constraint and the power balance of Equation (2), the only possible result is to forward to complete the input power through the DC-link and the inverter to the motor [28]. The motor, then, is no longer operated with a constant output power, but with the pulsating grid power itself as  $p_M(t) = \omega(t) \, t_M(t) \equiv p_G = P_0[1 + \cos(2\pi f_P t)]$ .

Due to the motor inertia  $J_{\rm M}$  (and any additional load inertia), the speed  $\omega$  changes slowly ( $\omega(t)\approx\bar{\omega}$ ), resulting in a pulsating torque  $t_{\rm M}(t)\approx p_{\rm G}(t)/\bar{\omega}$  at twice the grid frequency (Figure 2(e.ii)). When the instantaneous input power is larger than the average power, positive torque is applied to the inertia, and the rotating mass is accelerated (speed increases), with the excessive power stored as an increase in kinetic energy  $e_{\rm KIN}=J_{\rm M}\omega^2/2$ . In the other part of the mains period, when the input power drops below the average power, negative torque is applied and the rotating mass is decelerated. This causes a pulsating rotational speed  $\omega(t)$  with an average  $\bar{\omega}$ , analogous to the DC-link voltage in the conventional system, where the amplitude of the speed ripple  $\Delta\omega$  is (and recalling  $P_0=\bar{\omega}T_{\rm L}$ , where  $T_{\rm L}$  is the load torque):

$$\Delta\omega \approx \frac{1}{2\pi f_{\rm P}} \frac{P_0}{\bar{\omega} J_{\rm M}} = \frac{1}{2\pi f_{\rm P}} \frac{T_{\rm L}}{J_{\rm M}}.$$

(5)

This concept buffers the pulsating power in the inertia of the motor, an approach called the Motor-Integrated Power Pulsation Buffer. The basic operation is similar to the working principle of conventional single-phase motors [45], although with the VSD capabilities required here and for most modern motors.

Another way to conceive of the approach, then, is that the motor acts as both a drive and a flywheel, which are used independently for peak power reduction in traction systems [46], peak power supply within railway grids [47], smoothing of the output power of renewable power sources such as wind power [48], or within dynamic voltage restorers [49]. Because low-speed motors have a large moment of inertia  $J_{\rm M}$  and high-speed motors have high rotational speeds  $\omega$ , the stored kinetic energy of the mechanical system is typically orders of magnitude larger than the required energy to buffer the electric power pulsation at the input, leading to a very small variation in the rotational speed  $\omega$  around its average value  $\bar{\omega}$  (for  $J_{\rm M}$  according to Table 3,  $\Delta\omega=7.3\,{\rm rad/s}=70\,{\rm rpm}$  or 1.9%). Analogous to the capacitor current, though—although here with a DC offset of the average torque—the MPPB concept results in a large twice-line-frequency variation in the mechanical torque between zero and twice the average torque value. The MPPB concept offers a fundamental simplicity with the potential to significantly reduce or, theoretically, even eliminate the DC-link capacitor as the energy storage.

In Equation (5), a linear relationship between the speed ripple amplitude  $\Delta\omega$  and the load torque  $T_{\rm L}$  is observed, and the validity of the MPPB concept across the complete range of motor speeds must be investigated. Under variable speed operation, the load torque may also depend on the current speed based on the load torque speed characteristic. This relationship is defined around the nominal load torque  $T_{\rm L,N}$  at a nominal average speed  $\omega_{\rm N}$ , with an exponential dependence between torque and speed as  $T_{\rm L} = T_{\rm L,N} (\bar{\omega}/\omega_{\rm N})^k$ . The speed ripple under the MPPB operation can then be defined as:

$$\Delta\omega \approx \frac{1}{2\pi f_{\rm P}} \frac{T_{\rm L,N}}{J_{\rm M}\omega_{\rm N}^k} \bar{\omega}^k. \tag{6}$$

For k > 1, which includes fans, blowers, or centrifugal pumps (k = 2), the load torque and speed ripple grow faster than the average speed ( $\Delta \omega \propto \bar{\omega}^2$ ), so the worst-case ripple in both absolute and relative terms occurs at the nominal speed and nominal torque operating

Electronics 2022, 11, 280 8 of 49

point. For k=1, the ripple amplitude scales linearly with speed ( $\Delta\omega \propto \bar{\omega}$ ), resulting in a constant relative ripple. It is important to point out that in both cases, i.e., for  $k\geq 1$ , the speed ripple will be much less than the average speed ( $\Delta\omega <<\bar{\omega}$ ) at all operating points—including speeds close to zero—if the condition is met at the nominal operating point, and the time-varying speed is defined as  $\omega(t)\approx\bar{\omega}$ .

For applications where  $0 \le k < 1$ , however, the absolute speed ripple grows slower than the average speed  $(\Delta\omega \propto \bar{\omega}^k)$ . This may occur for a constant torque load  $T_{\rm L}$  (the k=0 condition), for which an application could be a compressor with constant back pressure [50]—the use case considered in this paper. In this case, the absolute speed ripple amplitude is in a first approximation (see Equation (6)) independent of the speed and constant. This condition results in a lower limit on the average speed, since an instantaneous negative speed needs to be prevented for the MPPB operation (to avoid a transfer of energy from the motor to the DC-link). To a first approximation, this implies a lower absolute speed limit of  $\bar{\omega} - \Delta\omega = 0\,{\rm rad/s}$  and a lower speed limit for continuous operation of  $\bar{\omega}_{\rm min} \approx \Delta\omega$  (this limit does not apply to transient operation). In the vicinity of  $\bar{\omega}_{\rm min}$ , however, the approximation  $\omega(t) \approx \bar{\omega}$  is no longer valid. Therefore, this lower speed limit is investigated in detail in Appendix A.

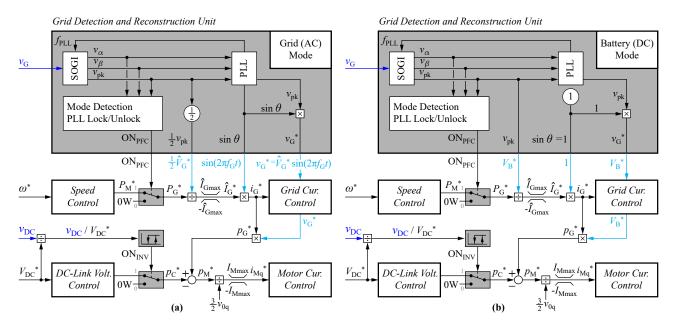

#### 2.3. Control

Relative to the conventional control technique for a two-stage system, the MPPB control can be realized with identical high-frequency current control and a modification of only the coupling in the top-level structure between the PFC rectifier and the inverter. Therefore, the control structure of a conventional system is detailed first before moving to the needed modifications for the MPPB technique.

#### 2.3.1. Conventional Control Overview

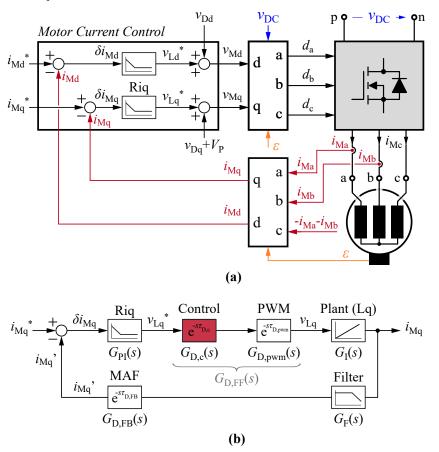

In conventional single-phase-supplied VSD systems, the PFC rectifier and the inverter stage are decoupled from one another by the large intermediate DC-link capacitor. The control structures are also mostly decoupled, as shown in Figure 3a.

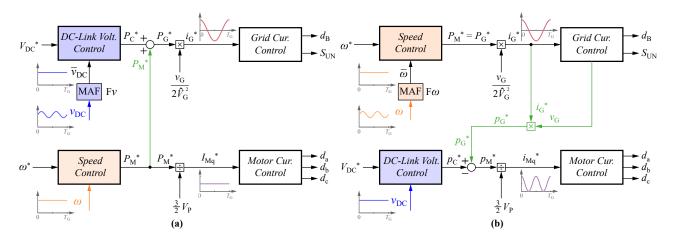

**Figure 3.** Simplified control structure of (a) a conventional implementation of a single-phase-supplied VSD with an electrolytic capacitor and (b) the proposed MPPB concept without an electrolytic capacitor. Feedforward signals improve the control quality and are highlighted in green, with characteristic waveforms over one grid period shown adjacent to the relevant control signals. © 2018 IEEE. Adapted, with permission, from [28].

The PFC rectifier control provides a constant DC-link voltage while drawing a sinusoidal current from the grid. Firstly, the power-pulsation-associated voltage ripple in the measured signal is eliminated, either by a Moving-Average Filter (MAF) [51] (shown here) or a conventional low-pass filter. The output of this filter, the obtained average value  $\bar{v}_{DC}$ , is then compared to the reference  $V_{DC}^*$ , and the DC-link voltage control derives the average

Electronics **2022**, 11, 280 9 of 49

capacitor power  $P_{C}^{*}$ , which can be taken as the average grid power  $P_{G}^{*}$ , and is then used to generate the input current reference  $i_{G}^{*}$  for the grid current controller [52]. This results in the duty-cycle for the boost stage  $d_{B}$  and the corresponding switching state of the unfolder leg  $S_{UN}$ .

The task of the inverter control is to track the speed reference  $\omega^*$ , a target that is typically accomplished with a control structure in the dq-coordinate system [53]. The speed control results in the reference motor torque  $T_{\rm M}^*$ , or as shown here, in the reference motor power  $P_{\rm M}^* = \omega^* T_{\rm M}^*$ . Considering a rotor field-oriented control in a rotating dq-reference frame [54], this request can be translated to the torque-generating current  $I_{\rm Mq}^*$  by the torque constant  $k_{\rm T}$  or, based on the power balance  $P_{\rm M}^* = 3V_{\rm P}I_{\rm Mq}^*/2$ , where  $V_{\rm P}$  is the induced voltage (assumed proportional to the reference speed and aligned with the q-axis), and the dq-quantities correspond to the phase amplitudes. The motor current control, in the end, determines the duty-cycles  $d_{\rm a}$ ,  $d_{\rm b}$  and  $d_{\rm c}$  of the inverter switching stages.

In the conventional approach, the DC-link capacitor compensates the difference of the instantaneous grid power  $p_G(t)$  and motor power  $P_M$ , so only the average power of the grid  $P_G$  and the inverter  $P_M$  have to be equal. To achieve this, the conventional control structure typically employs a feedforward of the average motor power  $P_M^*$ , where the inverter stage directly informs the rectifier stage about the needed output power (Figure 3a) and thus improves the control performance of the PFC rectifier. For PFC operation,  $P_G^*$  is not allowed to vary within a grid period  $T_G$ , which requires a slow DC-link voltage control and a bandwidth-limited feedforward (or this could be achieved with an additional low-pass filter, which is not shown here).

#### 2.3.2. MPPB Control Overview

For the proposed MPPB control structure, the average grid power  $P_{\rm G}$  must still match the average motor power  $P_{\rm M}$ , as  $P_{\rm G}=P_{\rm M}=P_{\rm 0}$ . Here, though, the power pulsation is buffered by the motor inertia, causing a (small) speed ripple that should be eliminated in the signal measurement, as the DC-link voltage ripple was in the conventional control scheme.

The speed controller, then—which drives the required average motor power  $P_{\mathrm{M}}^*$  from the difference between the reference speed  $\omega^*$  and average speed  $\bar{\omega}$ —defines the grid power  $P_{\mathrm{M}}^* = P_{\mathrm{G}}^*$  and, therefore, the grid current  $i_{\mathrm{G}}^*$  (see Figure 3b). Again,  $P_{\mathrm{G}}^*$  must be bandwidth limited (here, slow speed control) to prevent a distortion of the grid current.

The instantaneous input power  $p_{\rm G}^* = v_{\rm G} i_{\rm G}^*$  is derived and feed-forwarded to the motor control, resulting in the time-varying q-current  $i_{\rm Mq'}^*$ , which causes the torque pulsation. Here, though, a stable DC-link voltage  $v_{\rm DC}$  must be ensured, and the DC-link voltage control block achieves this by deriving the instantaneous reference power  $p_{\rm C}^*$  from the reference value  $V_{\rm DC}^*$  and the unfiltered measurement  $v_{\rm DC}$ .

According to the power balance Equation (2), this quantity is then subtracted for the instantaneous motor power request:

$$p_{\mathbf{M}}^{*}(t) = p_{\mathbf{G}}^{*}(t) - p_{\mathbf{C}}^{*}(t). \tag{7}$$

The elegance of the MPPB approach, then, is the utilization of identical control blocks that are simply connected in a different configuration. The MPPB control, then, can be implemented with only software modifications and could even be retrofitted into existing deployments.

## 2.3.3. MPPB Control Details

In the proposed approach, the primary challenge is that the speed control defines the average grid power, but the inverter must ensure that the *instantaneous* input power is forwarded to the motor; otherwise, with a small DC-link capacitance, the difference could charge the DC-link capacitor rapidly and lead to catastrophic failures. To address this critical challenge and highlight the other details of the MPPB control technique, the

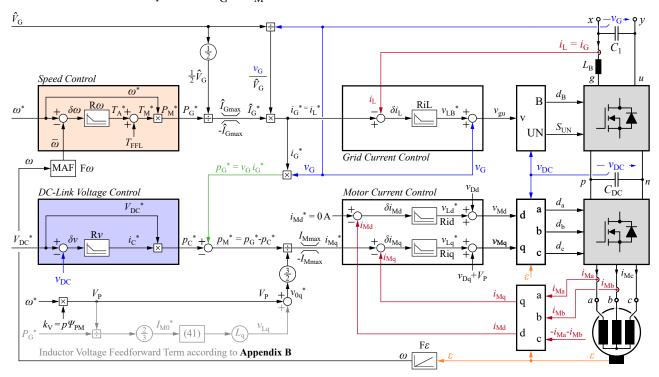

simplified control structure of Figure 3b is extended and shown together with the power topology in Figure 4.

To achieve a high quality for both the power and current alongside a high dynamic control at the output, the control structures were realized in a cascaded fashion. The outer loops for speed and DC-link voltage control provide the current setpoints for the grid and motor current control inner loops, with the motor current control implemented in the dq-coordinate system [53] using the mechanical rotor angle  $\varepsilon$  [54] provided by the encoder of the PMSM.

This encoder angle is also used to derive the instantaneous speed  $\omega$ , shown at the bottom of Figure 4, which is then filtered by a MAF [51] with  $T_{\rm MAF} = T_{\rm P} = T_{\rm G}/2$  to eliminate the speed ripple in the measured signal. Inside the speed control block,  $\bar{\omega}$  is compared to the reference  $\omega^*$ , and the speed controller  $R\omega$  derives the reference average motor torque  $T_{\rm M}^*$ , which results in the reference average motor power  $P_{\rm M}^* = T_{\rm M}^*\omega^*$  and the average grid power as  $P_{\rm G}^* = P_{\rm M}^*$ .

**Figure 4.** Control structure of Figure 3b with full implementation details, indicating the cascaded controller blocks, the dq-coordinate motor current control, and all required measurements. The addition of an inductor voltage feedforward term is described in Appendix B. © 2018 IEEE. Adapted, with permission, from [28].

The grid current controller requires the grid current reference as an input, which is translated from  $P_G^*$  using the power balance of the grid  $\hat{I}_G^* = 2P_G^*/\hat{V}_G$ . This result is then limited to a maximum current amplitude  $\hat{I}_{Gmax}$ , which is the minimum of (a) the maximum rectifier input current and (b) the current amplitude that corresponds to the power the inverter can deliver to the motor (the sum of the instantaneous mechanical output power and the system losses). The instantaneous grid current request, then, results from  $i_G^* = v_G \hat{I}_G^*/\hat{V}_G$  and equals the inductor current as  $i_L^* = i_G^*$ . The grid current controller RiL compares the requested current to the measured inductor current, adds the the resulting boost inductor voltage  $v_{LB}^*$  to the measured terminal voltage  $v_G$ , and translates this sum to the boost duty-cycle  $d_B$  and the switching state of the unfolder  $S_{UN}$ . For interleaved boost bridge-legs, an additional balancer control unit would need to be included [55].

The power feedforward term  $p_G^* = v_G i_G^*$  to the motor current control block, subsequently, is derived from the measured terminal voltage  $v_G$  and the reference grid current

$i_{\rm G}^*$ . This feedforward term significantly reduces the control effort of the DC-link voltage controller, where the capacitor power request  $p_{\rm C}^*$  is derived from the DC-link voltage reference  $V_{\rm DC}^*$  and the measured and unfiltered DC-link voltage  $v_{\rm DC}$ . The reference motor power  $p_{\rm M}^*$ , the input to the motor current controller, results then from Equation (7).

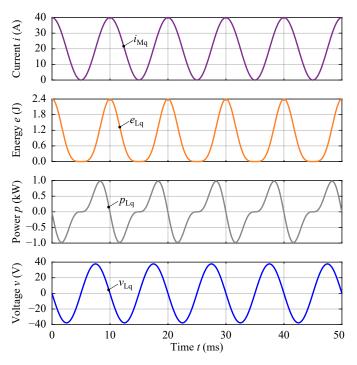

The motor current controller, here, avoids field weakening [56] for simplicity; therefore,  $i_{\mathrm{Md}}^* = 0$  A is selected, and the produced torque is only proportional to the q-current  $i_{\mathrm{Mq}}$ . The motor power balance results in  $p_{\mathrm{M}}^* = 3v_{\mathrm{0q}}^*i_{\mathrm{Mq}}^*/2$  as  $i_{\mathrm{Md}}^* = 0$  A, with  $v_{\mathrm{0q}}^* \approx V_{\mathrm{P}} = p\Psi_{\mathrm{PM}}\omega^*$  as the induced voltage, which is dependent on the speed, the number of pole pairs p, and the permanent magnet flux  $\Psi_{\mathrm{PM}}$  (or, more conventionally, the product of the latter two, the motor constant  $k_{\mathrm{V}} = V_{\mathrm{P}}/\omega^* = p\Psi_{\mathrm{PM}}$ ).

Inside the motor current controller, the current setpoints  $i_{\mathrm{Md}}^*=0\,\mathrm{A}$  and  $i_{\mathrm{Mq}}^*$  are compared to the the instantaneous current values  $i_{\mathrm{Md}}$  and  $i_{\mathrm{Mq}}$ , which are derived from the phase current measurements by the Park transform. The current controllers Rid and Riq then derive the reference motor inner inductor voltages  $v_{\mathrm{Ld}}^*$  and  $v_{\mathrm{Lq}}^*$ , which are translated to the inverter duty-cycles  $d_{\mathrm{a}}$ ,  $d_{\mathrm{b}}$ , and  $d_{\mathrm{c}}$  after including the motor voltage feedforward  $V_{\mathrm{P}}$  and the decoupling terms  $v_{\mathrm{Dd}} = -\omega p L_{\mathrm{q}} i_{\mathrm{Mq}}^*$  and  $v_{\mathrm{Dq}} = \omega p L_{\mathrm{d}} i_{\mathrm{Md}}^*$  (which depend on the reference currents and the motor inductances  $L_{\mathrm{d}}$  and  $L_{\mathrm{q}}$ ) for the required motor voltages  $v_{\mathrm{Md}}$  and  $v_{\mathrm{Mq}}$ . The motor current control supports the inclusion of an additional Common-Mode (CM) voltage component for overmodulation [57], if desired.

## 2.3.4. Simulation Results

With the concept and the detailed control structure for the proposed MPPB concept each outlined, the approach was verified through simulation for the nominal operating point of Table 2. The circuit parameters of Table 3 were used, highlighting especially that only  $60\,\mu F$  of the DC-link capacitance is required for an 8 kW system. The controller design for the simulation (and later, for the implementation) is described in further detail in Appendix B.

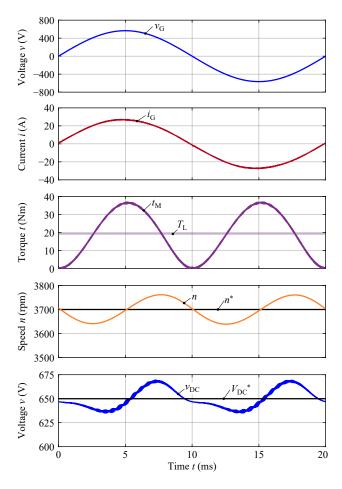

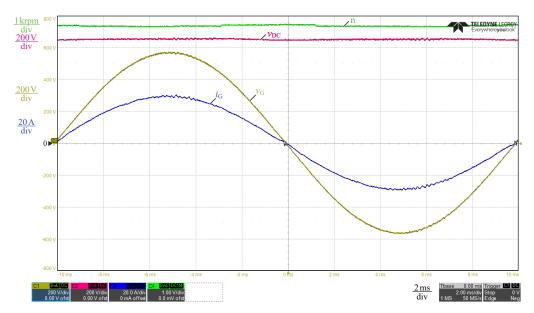

The corresponding waveforms at a mechanical output power of 7.5 kW and 3700 rpm are shown in Figure 5, where the grid current  $i_{\rm G}$  is in phase with the grid voltage  $v_{\rm G}$  for unity power factor operation and the product of the grid current and grid voltage resulting in pulsating input power, translated to a torque pulsation. The torque  $t_{\rm M}$  pulsated, as expected, around the average of  $T_{\rm L}=19.4$  Nm. When  $t_{\rm M}(t)>T_{\rm L}$ , the motor speed increased, and when  $t_{\rm M}(t)< T_{\rm L}$ , the motor speed decreased, resulting here in a symmetric speed ripple amplitude of  $\Delta n=\pm 61$  rpm around the average of 3700 rpm. The DC-link voltage contains a low-frequency peak-to-peak ripple of around 34 Vpkpk, a direct consequence of the limited control bandwidth of the DC-link voltage control and a limitation that can be addressed through the improvements discussed in Appendix B. Overall, the simulation results verified the correct and expected operation, and next, the performance of the MPPB-operated system was evaluated.

# 2.4. Performance Evaluation

Aside from the significant reduction in required DC-link capacitance, the MPPB concept has no effect on the performance of the PFC rectifier or on the performance of the EMI filter. The effect of the proposed concept can be analyzed on only the motor and the inverter, then starting with the time-domain impact and subsequently moving to an analysis of the losses.

#### 2.4.1. Time-Domain Waveforms

Under conventional operation, the magnitude of the q-current is given by  $I_{\text{M0}} = 2P_0/(3V_{\text{P}})$ , and thus,  $i_{\text{Md}}(t) \equiv 0\,\text{A}$  and  $i_{\text{Mq}}(t) = I_{\text{M0}}$ . The phase currents are derived using the inverse Park transform [54] with  $\varepsilon = p\bar{\omega}t + \varepsilon_0$ :

$$\begin{bmatrix} i_{\text{Ma}} \\ i_{\text{Mb}} \\ i_{\text{Mc}} \end{bmatrix} = \begin{bmatrix} \cos(\varepsilon) & -\sin(\varepsilon) \\ \cos(\varepsilon - \frac{2\pi}{3}) & -\sin(\varepsilon - \frac{2\pi}{3}) \\ \cos(\varepsilon + \frac{2\pi}{3}) & -\sin(\varepsilon + \frac{2\pi}{3}) \end{bmatrix} \begin{bmatrix} i_{\text{Md}} \\ i_{\text{Mq}} \end{bmatrix}$$

(8)

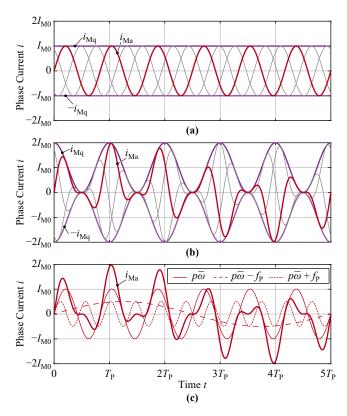

This results in three purely sinusoidal and symmetrical phase currents, each with the peak value  $I_{\rm M0}$ , as shown in Figure 6a. These phase currents are evaluated—and later, compared to the same values under MPPB operation—by the absolute average current  $I_{\rm PH0avg}$ , the RMS value  $I_{\rm PH0rms}$ , and the peak current  $I_{\rm PH0pk}$  as (with T the minimum period of the signal):

$$I_{\text{PH0avg}} = \frac{1}{T} \int_{0}^{T} |i_{\text{Ma}}(\tau)| d\tau = \frac{2}{\pi} I_{\text{M0}}$$

(9)

$$I_{\text{PH0rms}} = \sqrt{\frac{1}{T} \int_0^T i_{\text{Ma}}^2(\tau) d\tau} = \frac{1}{\sqrt{2}} I_{\text{M0}}$$

(10)

$$I_{\text{PH0pk}} = \max i_{\text{Ma}}(t) = I_{\text{M0}}.$$

(11)

**Figure 5.** Simulated waveforms of the grid voltage  $v_G$ , grid current  $i_G$ , motor torque  $t_M$ , rotational speed n, and DC-link voltage  $v_{DC}$  during steady-state, nominal operation, verifying the proposed MPPB concept and control structure. © 2018 IEEE. Adapted, with permission, from [28].

To analyze the proposed MPPB operation, constant speed (with  $\omega(t)\approx\bar{\omega}$ ) was assumed, which resulted in a constant induced voltage  $V_P=k_V\omega\approx k_V\bar{\omega}$ , and the instantaneous q-current was  $i_{\rm Mq}(t)=2p_{\rm M}(t)/(3V_{\rm P})$ . Using  $p_{\rm M}(t)=P_0[1+\cos(2\pi f_{\rm P}t)]$ , the q-current proportional relationship to the instantaneous torque is:

$$i_{\rm Mq}(t) \approx I_{\rm M0}[1 + \cos(2\pi f_{\rm P} t)] \propto t_{\rm M}(t),$$

(12)

where the magnitude  $I_{M0}$  is the same as under conventional operation.

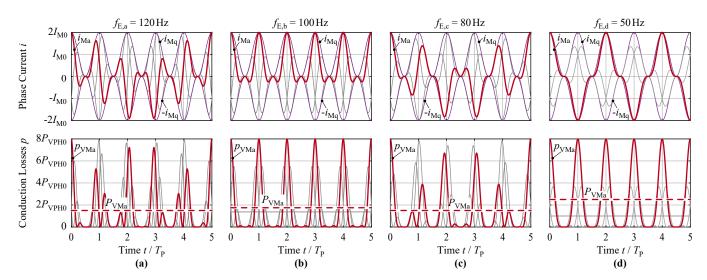

**Figure 6.** Phase currents  $i_{\text{Ma}}$ ,  $i_{\text{Mb}}$ , and  $i_{\text{Mc}}$  and the enveloping currents  $\pm i_{\text{Mq}}$  for the (a) conventional and (b) MPPB operation for  $f_{\text{P}}=100\,\text{Hz}$  and  $p\bar{\omega}/(2\pi)=120\,\text{Hz}$ . (c) Spectral decomposition of the first phase current  $i_{\text{Ma}}$  under MPPB operation. © 2018 IEEE. Adapted, with permission, from [28].

Because the q-current is now, under MPPB operation, pulsating at twice line frequency, the phase currents  $i_{\rm Ma}$ ,  $i_{\rm Mb}$  and  $i_{\rm Mc}$  into the motor are no longer purely sinusoidal. These phase currents were found by applying the inverse Park transform to the q-current and are shown in Figure 6b for  $f_{\rm P}=100\,{\rm Hz}$  and  $p\bar{\omega}=2\pi\,120\,{\rm Hz}$ . The phase current, more precisely, is then  $i_{\rm Ma}=-i_{\rm Mq}\sin(p\bar{\omega}t+\varepsilon_0)$ , or:

$$i_{\text{Ma}}(t) = -I_{\text{M0}} \sin(p\bar{\omega}t + \varepsilon_0)$$

$$-\frac{I_{\text{M0}}}{2} [\sin(p\bar{\omega}t + 2\pi f_{\text{P}}t + \varepsilon_0) + \sin(p\bar{\omega}t - 2\pi f_{\text{P}}t + \varepsilon_0)].$$

(13)

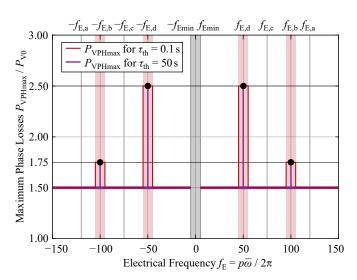

In addition to the fundamental  $p\bar{\omega}$  frequency, the phase currents now contain two additional harmonic components at the frequencies  $|p\bar{\omega}+2\pi f_{\rm P}|$  and  $|p\bar{\omega}-2\pi f_{\rm P}|$  with amplitude  $I_{\rm M0}/2$ , as shown with the spectral decomposition of the phase current for phase a in Figure 6c. For certain frequency ratios, these individual sines may collapse into a single frequency, become DC components, or even result in standing waves and an asymmetric phase stress. The precise effect of different frequency ratios is discussed in Appendix C, with the result that such effects occur only in the vicinity of certain speed values  $\bar{\omega}$ , which are all below or equal to the angular pulsation frequency  $\omega_{\rm P}=2\pi f_{\rm P}$ , and the assumption  $|p\bar{\omega}|>\omega_{\rm P}$  was used for the remaining analysis here.

Only the sinusoid with frequency  $p\bar{\omega}$  is phase aligned with the induced voltage of the corresponding phase, and therefore, only this component generates average torque to drive the load. Because this component is not influenced by the pulsating q-current, there is, as expected, no degradation in the mechanical average torque—but the additional components do increase current stress in the inverter and motor. The RMS current stress was calculated by a superposition of the purely sinusoidal waveforms, with a  $\sqrt{3/2}$  factor increase in RMS current. The average current remains unchanged while the peak current doubles as a result of the pulsating q-current. This large increase in peak current has a

Electronics **2022**, 11, 280 14 of 49

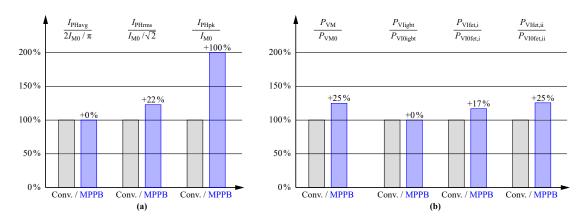

limited effect on the iron in the motor, since motors are typically designed in the thermal (rather than the saturation) limit and the flux is primarily defined by the permanent magnet  $\Psi_{PM}$ . The key current equations are summarized below, and the relative increase of each current is shown in Figure 7a.

$$I_{\text{PHavg}} = \frac{1}{T} \int_0^T |i_{\text{Ma}}(\tau)| d\tau = \frac{2}{\pi} I_{\text{M0}}$$

(14)

$$I_{\text{PHrms}} = \sqrt{\frac{1}{T} \int_0^T i_{\text{Ma}}^2(\tau) d\tau} = \frac{1}{\sqrt{2}} \sqrt{\frac{3}{2}} I_{\text{M0}}$$

(15)

$$I_{\text{PHpk}} = \max i_{\text{Ma}}(t) = 2I_{\text{M0}}.$$

(16)

With the key current ratios defined, the relative inverter and motor losses between conventional and MPPB operation were analyzed.

**Figure 7.** Comparison of (a) loss characteristic currents and (b) losses under conventional and MPPB operation at the nominal operating point. The loss penalty of the MPPB is evaluated for three inverter realizations: IGBT-based ( $P_{\text{VIigbt}}$ ), MOSFET-based with external Miller capacitors to limit the  $dv_{\text{DS}}/dt$  of the switching transitions ( $P_{\text{VIfet,i}}$ ), and MOSFET-based with the explicit LC output filter stage designed for the dv/dt-limitation of the voltage applied to the motor terminals [58] or full-sine-wave output voltage shaping ( $P_{\text{VIfet,ii}}$ ).

#### 2.4.2. Motor Loss Analysis

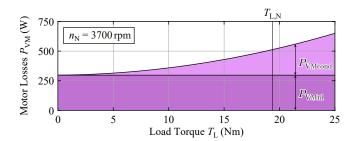

The motor losses  $P_{\rm VM}$  include both speed-dependent no-load losses  $P_{\rm VMnl}$  and load-dependent conduction losses  $P_{\rm VMcond}=3R_{\rm s}I_{\rm PHrms}^2$ , with  $R_{\rm s}$  as the stator winding resistance. The motor losses under conventional operation  $P_{\rm VM0}$  and under the proposed MPPB operation  $P_{\rm VM}$  are:

$$P_{\text{VM0}} = P_{\text{VMnl}} + \frac{3}{2} R_{\text{s}} I_{\text{M0}}^2 \tag{17}$$

$$P_{\rm VM} = P_{\rm VMnl} + \frac{9}{4} R_{\rm s} I_{\rm M0}^2, \tag{18}$$

where the MPPB operation incurs a 50% loss increase in conduction losses due to the increase in the RMS current. If an equal loss distribution between the no-load losses and the load-dependent conduction losses at the nominal operation point is assumed, which is typically close to an optimum design, MPPB operation incurs a motor loss penalty of only 25%. This loss ratio, along with the inverter loss ratios of the next section, is shown in Figure 7b.

### 2.4.3. Inverter Loss Analysis

The inverter semiconductor losses  $P_{\rm VI}$  comprise conduction  $P_{\rm VIcond}$  and switching losses  $P_{\rm VIsw}$ . The conduction losses are, most generally, written as  $P_{\rm VIcond} = 3V_{\rm f}I_{\rm PHavg} + 3R_{\rm on}I_{\rm PHrms}^2$ , where  $V_{\rm f}$  is the on-state voltage drop and  $R_{\rm on}$  is the (differential) on-resistance. The switching losses are written with a quadratic loss function  $e_{\rm sw}(i) = k_0 + k_1 i + k_2 i^2$  [59],

Electronics **2022**, 11, 280 15 of 49

which leads to  $P_{\text{VIsw}} = 3f_{\text{Isw}}(k_0 + k_1I_{\text{PHavg}} + k_2I_{\text{PHrms}}^2)$  with the inverter switching frequency  $f_{\text{Isw}}$ . A quick review of these equations shows that the MPPB concept would only affect the ohmic part of the conduction losses and the quadratic part of the switching losses, both with an increase of 50%, through the increase in the RMS current.

If the semiconductors are implemented as IGBTs, conduction losses are given—to a first approximation—by the on-state voltage drop, and the switching losses can be approximated by the linear part alone. For an IGBT-implemented inverter, then, the inverter losses are identical between conventional ( $P_{\text{VI0iebt}}$ ) and MPPB operation ( $P_{\text{VIiiebt}}$ ):

$$P_{\text{VI0igbt}} = \frac{6}{\pi} V_{\text{f}} I_{\text{M0}} + 3 f_{\text{Isw}} \frac{2}{\pi} k_1 I_{\text{M0}} = P_{\text{VIigbt}}.$$

(19)

IGBTs, however, suffer from high overall losses [60], and inverters with SiC MOSFET-based bridge-legs and a  $dv_{DS}/dt$  limitation should be considered as well.

For a SiC MOSFET-based bridge-leg and external Miller capacitors to limit the voltage slew rate, the conduction losses can be considered ohmic, and the switching losses are described well by the constant and linear part [61], for inverter losses under conventional ( $P_{\text{VI0fet,i}}$ ) and MPPB operation ( $P_{\text{VIIfet,i}}$ ), as:

$$P_{\text{VI0fet,i}} = \frac{3}{2} R_{\text{on}} I_{\text{M0}}^2 + 3 f_{\text{Isw}} \left( k_0 + \frac{2}{\pi} k_1 I_{\text{M0}} \right)$$

(20)

$$P_{\text{VIfet,i}} = \frac{9}{4} R_{\text{on}} I_{\text{M0}}^2 + 3 f_{\text{Isw}} \left( k_0 + \frac{2}{\pi} k_1 I_{\text{M0}} \right). \tag{21}$$

The motor acts as a resistive—inductive load with a reactive power demand and, therefore, requires a current commutation path for the freewheeling current. The high voltage drop of the body diode of the utilized SiC MOSFETs is typically overcome with an anti-parallel SiC Schottky diode, but the MOSFET itself can also be utilized as a synchronous rectifier. In this case, the freewheeling diode only conducts during the dead time, and the additional losses from the body diode conduction can be neglected (this assumption was extensively analyzed in [62] and verified in Section 3). In this context, it should be also mentioned that early high-voltage SiC MOSFETs were associated with bipolar degradation on their intrinsic body diodes [63], but this problem has been solved for state-of-the-art 1.2 kV devices [64].

Conduction losses increase by 50% under the proposed MPPB operation. If each loss contribution (conduction, constant switching losses, and current-dependent switching losses) is assumed to be 1/3 of the overall inverter losses [61] at nominal operation, the inverter loss penalty is around 17% for MPPB operation with a SiC MOSFET-based bridge-leg and external Miller capacitors to limit the voltage slew rate.

Finally, a realization with a hard-switching SiC MOSFET-based bridge-leg with an LC output filter designed for a  $\mathrm{d}v/\mathrm{d}t$ -limitation of the voltage applied to the motor terminals [58] or full-sine-wave output voltage shaping was analyzed. The doubling of the peak current will negatively impact the performance of the filter inductor. Here, conduction losses remain ohmic and the switching losses contain all of the terms, for conventional ( $P_{\mathrm{VI0fet,ii}}$ ) and MPPB inverter losses ( $P_{\mathrm{VIfet,ii}}$ ) of:

$$P_{\text{VI0fet,ii}} = \frac{3}{2}R_{\text{on}}I_{\text{M0}}^2 + 3f_{\text{Isw}}\left(k_0 + \frac{2}{\pi}k_1I_{\text{M0}} + \frac{1}{2}k_2I_{\text{M0}}^2\right)$$

(22)

$$P_{\text{VIfet,ii}} = \frac{9}{4} R_{\text{on}} I_{\text{M0}}^2 + 3 f_{\text{Isw}} \left( k_0 + \frac{2}{\pi} k_1 I_{\text{M0}} + \frac{3}{4} k_2 I_{\text{M0}}^2 \right). \tag{23}$$

If an equal loss contribution is assumed for all four loss components (conduction losses and the three switching loss terms) at nominal operation, MPPB operation carries a 25% loss penalty over conventional operation for the inverter, similar to the penalty in the motor.

A summary of these inverter loss penalties for different bridge-leg implementations is shown in Figure 7b, where, although the MPPB concept increases the conduction losses by 50%, the maximum total loss penalty is 25%—while realizing a potential volume reduction of up to 1 L (or 61 in<sup>3</sup>) by eliminating the DC-link electrolytic capacitors.

## 3. System Design and Implementation

With the power density improvements—and the possibility of motor integration—of the MPPB-operated system attractive, the system proposed in Figure 2a was next designed and implemented. This hardware demonstrator allows a direct comparison between conventional and MPPB systems on the volume and loss distributions. The motor-integrated converter system is the focus of this section, with brief guidelines given for motor selection and PFC rectifier and inverter designs.

### 3.1. Motor Selection and Characterization

With the output power  $P_{0,N}=7.5\,\mathrm{kW}$  and speed requirements  $n_{\mathrm{N}}=3700\,\mathrm{rpm}$  leading to a torque specification of  $T_{\mathrm{L,N}}=19.4\,\mathrm{Nm}$ , the 1FT7-084 from Siemens [65] was selected.

At nominal operation  $n_{\rm N}=3700$  rpm, the motor frequency with p=5 is  $p\omega_{\rm N}=2\pi\,308$  Hz, which is sufficiently above  $f_{\rm P}=100$  Hz to guarantee symmetric phase stresses in the motor and inverter (see Appendix C). The motor inertia of  $J_{\rm M}=4.5$  mkgm² corresponds to a speed ripple amplitude, using Equation (5), of  $\Delta\omega=7.3$  rad/s = 70 rpm, or 1.9% of the nominal speed. The minimal achievable speed in stationary operation for constant torque  $T_{\rm L}(\omega)=T_{\rm L,N}$  is, according to Appendix A,  $\bar{\omega}_{\rm min}=5$  rad/s  $\approx50$  rpm. The torque constant is given with  $k_{\rm T}=T/I_{\rm M0}=0.92$  Nm/A and the given speed constant  $k_{\rm V}$ , which relates the induced pole-wheel peak voltage  $V_{\rm P}$  to the speed n as  $k_{\rm V}=V_{\rm P}/n=67.8$  mV/rpm, resulting in a nominal phase voltage amplitude of  $V_{\rm P,N}=250$  Vpk. The nominal DC-link voltage can then be selected as  $V_{\rm DC,N}=650$  V (cf. Table 2, allowing boost PFC operation up to the nominal input voltage of  $V_{\rm G,N}=400$  Vrms with a 15% margin. For input voltages above nominal, the DC-link voltage is linearly increased up to 800 V at  $V_{\rm Gmax}=530$  Vrms, or a peak voltage of 750 Vpk.

The motor was measured to validate the datasheet and build a complete loss model. The stator phase resistance was measured at  $R_{\rm s}=0.2\,\Omega$  at 40 °C (close to ambient since the winding temperature does not significantly increase during short-time operation and was also respected for the experimental analyses), and the motor inductances were measured at  $L_{\rm d}\approx L_{\rm q}\approx 3.0\,{\rm mH}$ , both within 10% of the datasheet values. The speed-dependent, no-load losses from iron losses and friction [66] were measured with the motor driven mechanically and the torque measured at nominal speed  $n_{\rm N}$ , resulting in a no-load torque of  $T_{\rm Mnl}=0.765\,{\rm Nm}$  and no-load losses of  $P_{\rm VMnl}=\omega_{\rm N}T_{\rm Mnl}=296\,{\rm W}$ .

At nominal speed, the motor current amplitude is  $I_{\rm M0}=(T_{\rm L}+T_{\rm Mnl})/k_{\rm T}$ , which at nominal load is  $I_{\rm M0,N}=21.9\,\rm A$ . Under conventional operation, this RMS phase current is  $I_{\rm PH0rms,N}=I_{\rm M0,N}/\sqrt{2}=15.5\,\rm Arms$  (cf. Equation (10)), and under the proposed MPPB operation, the phase current is  $I_{\rm PHrms,N}=\sqrt{3}I_{\rm M0,N}/2=19\,\rm Arms$  (cf. Equation (15)). With the no-load losses summed with the conduction losses for the total motor losses,  $P_{\rm VM}=P_{\rm VMnl}+P_{\rm VMcond}$ , or:

$$P_{\text{VM}} = \omega_{\text{N}} T_{\text{Mnl}} + \frac{9}{4} R_{\text{s}} \left( \frac{T_{\text{L}} + T_{\text{Mnl}}}{k_{\text{T}}} \right)^2. \tag{24}$$

The no-load torque increases the motor losses  $P_{\rm VM}$  twice—once directly, through the  $P_{\rm VMnl}$  term, and additionally by increasing the motor current as  $T_{\rm Mnl}/k_{\rm T}$  and, therefore, increasing the conduction losses  $P_{\rm VMcond} = 9R_{\rm s}I_{\rm M0}^2/4$ .

The MPPB-operated motor losses at the average torque are shown in Figure 8, with the nominal losses under MPPB operation of  $P_{\rm VM,N}=517\,\rm W$  compared to 443 W under conventional operation. This motor loss increase is 16.7%, less than the 25% predicted in Figure 7b since the no-load losses comprise more than half of the total motor losses.

Electronics **2022**, 11, 280 17 of 49

**Figure 8.** Characterized motor losses  $P_{\text{VM}}$  under MPPB operation at load torque, comprising speed-dependent no-load losses  $P_{\text{VMnol}}$  and torque/current-dependent conduction losses  $P_{\text{VMcond}}$ .

# 3.2. Converter Design

The complete converter topology is shown in Figure 9 with the components of Table 3, and here, the key pieces of the component selection are highlighted.

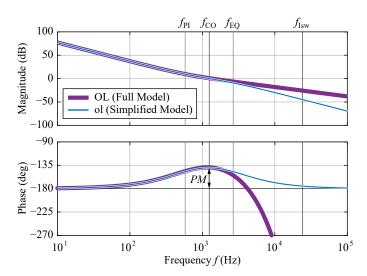

## 3.2.1. Inverter Design

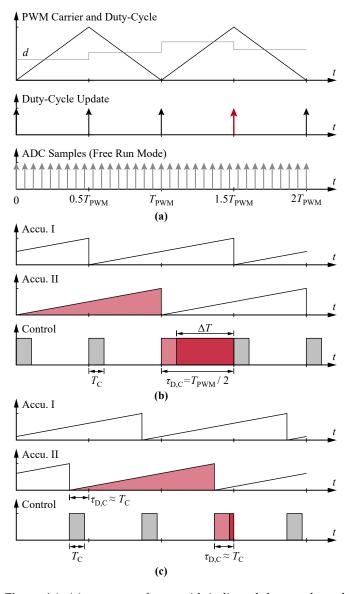

The inverter switching frequency must be outside the audible range (above 16 kHz [67]), but is determined more strictly by the control bandwidth. With a pulsation frequency of  $f_{\rm P}=100\,{\rm Hz}$ , the DC-link voltage control bandwidth was designed to be  $5\times$  higher at  $500\,{\rm Hz}$ , the motor current control bandwidth  $5\times$  higher than that at  $2500\,{\rm Hz}$ , and the inverter switching frequency  $10\times$  higher for an inverter switching frequency of  $f_{\rm Isw}\approx25\,{\rm kHz}$ . Due to EMI considerations [68],  $f_{\rm Isw}=24\,{\rm kHz}$  was selected.

The 1200 V power semiconductors are required to withstand a DC-link voltage that will be as high as 800 V (plus low- and high-frequency voltage ripple), and SiC MOSFETs are employed instead of IGBTs for high performance [60]. These MOSFETs operate at high voltage slew rates, or  $dv_{DS}/dt$  values, which can lead to an unequal distribution of the voltage across the motor windings and partial discharge phenomena [69], resulting in progressive aging of the motor winding insulation [37]. Different solutions to this challenge were discussed and compared in [38], with gate drive modifications preferred [61], for motor-integrated drives that support  $dv_{DS}/dt$  values as high as 15 V ns<sup>-1</sup> (since there are no cable reflections to consider).

**Figure 9.** Complete powertrain, with all included components, for the realized motor-integrated VSD system. The component list is detailed below, in Table 3.

Table 3. Component list.

| Motor Inertia                         | J <sub>M</sub>                                                                                                                                                          | 4.5 mkgm <sup>2</sup>                                           | Siemens 1FT7-084 [65]                                            |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------|

| CM-Motor Capacitance                  | C <sub>CM0</sub>                                                                                                                                                        | 1.9 nF                                                          | Siemens 1FT7-084 (measured)                                      |

| Inverter Transistors                  | $egin{aligned} & T_{aH},  T_{aL},  T_{bH},  T_{bL},  T_{cH},  T_{cL} \ & T_{uH},  T_{uL} \ & T_{iH},  T_{iL},  T_{iiiH},  T_{iiiL},  T_{iiiH},  T_{iiiH} \end{aligned}$ | $16\mathrm{m}\Omega/1.2\mathrm{kV}$                             | Cree C3M0016120K [70]                                            |

| PFC Unfolder Transistors              |                                                                                                                                                                         | $16\mathrm{m}\Omega/1.2\mathrm{kV}$                             | Cree C3M0016120K [70]                                            |

| PFC Boost Transistors                 |                                                                                                                                                                         | $32\mathrm{m}\Omega/1.2\mathrm{kV}$                             | Cree C3M0032120K [71]                                            |

| DC-Link Capacitance<br>Boost Inductor | C <sub>DC</sub><br>L <sub>B</sub>                                                                                                                                       | $3 \times 20 \mu\text{F}/900 \text{V}$ 428 $\mu\text{H}$ (each) | Epcos <i>B32776E9206K000</i> , Foil 4 E-Cores/30 Turns Flat Wire |

| Tal | 1 1 |    | •   | $\sim$ |    |   |

|-----|-----|----|-----|--------|----|---|

| 13  | n   | Δ. | 4 1 |        | าน | + |

|     |     |    |     |        |    |   |

| DM-Filter Capacitance | $C_1$             | $4 	imes 1\mu F$                  | Epcos B32914A5105M000, X1         |

|-----------------------|-------------------|-----------------------------------|-----------------------------------|

| DM-Filter Capacitance | $C_2$             | 1 μF                              | Epcos B32914A5105M000, X1         |

| DM-Filter Inductance  | $L_{\mathrm{DM}}$ | 4.7 μH (each)                     | Wuerth 74436410470                |

| CM-Filter Capacitance | $C_{\text{CM1}}$  | $2 \times 20  \mathrm{nF}$        | Vishay 440LS20-R, Y1              |

| CM-Filter Capacitance | $C_{\rm CM2}$     | $2 \times 20  \mathrm{nF}$ (each) | Vishay 440LS20-R, Y1              |

| CM-Filter Inductance  | $L_{\text{CM0}}$  | 75 μH                             | $6 \times VAC$ L2025-W380, 1 Turn |

| CM-Filter Inductance  | $L_{\text{CM1}}$  | 1.6 mH                            | VAC <i>L2045-V102</i> , 9 Turns   |

| CM-Filter Inductance  | $L_{\text{CM2}}$  | $1.0\mathrm{mH}$                  | VAC <i>L2045-V102</i> , 7 Turns   |

|                       |                   |                                   |                                   |

The optimal chip area was selected for the inverter power semiconductors, all of which were implemented as next-generation  $16\,\mathrm{m}\Omega$  SiC MOSFETs (C3M0016120K [70]). A gate driver with an output clamp variant was selected [72] that drives the transistors at the maximum positive ( $V_{\mathrm{G,on}}=15\,\mathrm{V}$ ) and minimum negative ( $V_{\mathrm{G,off}}=-4\,\mathrm{V}$ ) gate drive voltages for enhanced noise immunity. A  $15\,\Omega$  gate resistor was added for turn-on and turn-off to stay below  $\mathrm{d}v/\mathrm{d}t=15\,\mathrm{V}\,\mathrm{ns}^{-1}$ , as investigated in [61].

As previously mentioned, synchronous rectification was employed for the MOSFETs within the inverter [62], with the body diode therefore only conducting during the dead time  $t_{\rm D}$ . Under the worst-case condition, where the body diode conducts the full-phase current within both dead time intervals of a switching period and with the diode forward voltage drop  $V_{\rm F}=4.6\,{\rm V}$  [70] and the selected inverter dead time of  $t_{\rm D}=400\,{\rm ns}$ , the losses under nominal operation are  $P_{\rm VIdiode}=3\,f_{\rm Isw}2t_{\rm D}\,V_{\rm F}I_{\rm PHavg}=3.7\,{\rm W}$  (where  $I_{\rm PHavg}$  is from Equation (14)). These losses represent less then 5% of the calculated inverter losses  $P_{\rm VI}=81.6\,{\rm W}$  and can be safely neglected.

# 3.2.2. DC-Link Capacitor Selection

The minimum DC-link capacitance was determined by the high-frequency-voltage ripple caused by the PFC rectifier and the inverter [73]. Due to disturbances and the limited control bandwidth of the DC-link voltage control, though, there was a remaining low-frequency voltage ripple (see Figure 5). This ripple could be addressed with increased bandwidth; however, in the end, this would require an increase in switching frequency, and the corresponding increase in switching losses would eliminate this option. Instead, to keep the peak-to-peak voltage ripple below 40 V, an increased DC-link capacitance of  $C_{\rm DC} = 60\,\mu\text{F}$  was selected based on circuit simulations. This capacitance requirement was only  $7.5\,\mu\text{F}\,\text{kW}^{-1}$ .

The chosen capacitors must be rated for at least  $800 \,\mathrm{V}$ , eliminating both ceramic X6S capacitors (which are only available up to  $400 \,\mathrm{V}$ , and would therefore require hundreds of series-stacked capacitors) and CeraLink capacitors, where only small capacitance values are available. Three  $20 \,\mu\mathrm{F}$  foil capacitors B32776E9206K000 [74] were selected, resulting in a total volume of only  $0.13 \,\mathrm{L}$  (or  $8 \,\mathrm{in}^3$ )—equal to just 13% of the required electrolytic capacitor volume under conventional operation.

# 3.2.3. PFC Rectifier Design

Because the rectifier is not affected by the MPPB approach, a conventional PFC rectifier design was implemented (even in [75], the electrolytic capacitors comprised 25% of the overall converter volume). This rectifier must be designed to provide the maximum power across the entire input voltage range (see Figure 1b), with a maximum input current of 32 Arms (or 45 Apk).

The unfolder was implemented with the lowest-possible  $R_{\rm DS,on}$  device C3M0016120K [70], which resulted in a maximum of 19.6 W of conduction losses at the voltage minimum and 9.6 W at nominal operation. To limit the component stresses of the high-frequency bridgeleg, which is subject to high-frequency switching losses, an interleaved design with three branches was selected. This supports an increase in effective switching frequency for the same semiconductor losses [76], an improved loss distribution, and the reuse of the

design for future three-phase-supplied VSD systems. Each bridge-leg was operated with a switching frequency of 48 kHz to keep the frequency multiple below the stricter EMI considerations at 150 kHz. The high-frequency bridge-leg power semiconductors were again selected with the optimal chip area and implemented with  $32\,\mathrm{m}\Omega$  four-pin devices (C3M0032120K [71]) for bridge-leg losses of  $P_{\mathrm{VRhb}} = 8.8\,\mathrm{W}$  at nominal operation.

The PFC rectifier inductor design was selected from the optimal front of a Pareto optimization based on the guidelines of [77], and this selected inductor was implemented with four stacked *K4317E040* Kool-Mu cores with a relative permeability of forty and thirty turns of flat wire (7 mm  $\times$  0.5 mm) (note that the permeability of Kool-Mu is current-dependent, and the inductance varies between 428  $\mu$ H and 342  $\mu$ H [78]). The inductor has a boxed volume of 100 cm<sup>3</sup> (33.6  $\times$  41.5  $\times$  72 mm) and  $P_{VRind} = 9.5$  W of expected losses at the nominal operating point. The filter capacitor  $C_1$  is subject to a current ripple at the interleaved frequency of 144 kHz, with the first and second harmonic canceled, and a 4  $\mu$ F capacitance was selected with an implementation of four parallel X-rated 1  $\mu$ F capacitors.

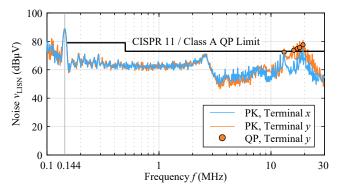

#### 3.2.4. EMI filter

This high-frequency bridge-leg interleaving also eliminates the fourth and fifth harmonic components, and the Differential-Mode (DM) EMI filter therefore needs to be designed to meet CISPR 11/Class A [8] at the DM noise of the PFC rectifier at 288 kHz. With the design guidelines of [79], CISPR 11/Class A can be met with  $C_2 = 1 \, \mu F$  and  $L_{DM} = 4.7 \, \mu H$ .

The common-mode noise is typically defined by the parasitic capacitance to the Earth, which is often dominated by the thermal interface material layer between the power semiconductors and the grounded heat sink. Here, the largest parasitic capacitance originates from the motor [80] at  $C_{\rm CM0}=1.9\,\rm nF$ . The CM EMI filter, therefore, is designed for the inverter noise occurring at the 7th harmonic of 168 kHz. Again, following the design of [79],  $C_{\rm CM1}=C_{\rm CM2}=40\,\rm nF$ ,  $L_{\rm CM1}=1.2\,\rm mH$ , and  $L_{\rm CM2}=0.8\,\rm mH$  meets CISPR 11/Class A at 168 kHz. Both CM inductors were evaluated at 168 kHz, and they employ L2045-V102 nanocrystalline cores [81] with seven and nine turns, respectively. An additional CM choke on the motor side  $L_{\rm CM0}$ —to damp high-frequency CM currents inside the system and reduce the potential for radiated emissions [82]—was implemented with six L2025-W380 [81] cores with one turn each and provided a series impedance of 75  $\mu$ H inductance and a damping resistance of  $100\,\Omega$  at  $168\,\rm kHz$ .

#### 3.3. Volume and Loss Distribution

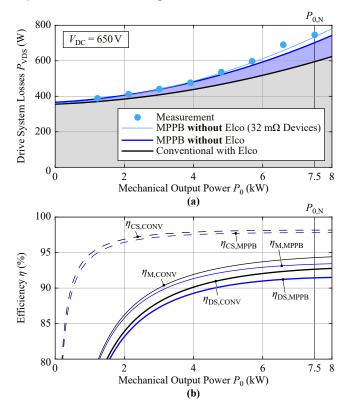

These selected components are summarized in Table 3, resulting in the system loss breakdown at the nominal operating point (Table 2) of Figure 10a. The rectifier ( $P_{\rm VR}=74.9\,\rm W$ ) and inverter ( $P_{\rm VI}=81.6\,\rm W$ ) stages comprise a nearly equal contribution to the system losses, which are dominated by the motor ( $P_{\rm VM}=534\,\rm W$ ). Beyond the no-load and conduction losses characterized in Figure 8, the motor incurs an additional 17 W of capacitive switching losses, where the parasitic motor capacitance is charged and discharged with the PWM voltage impressed by the inverter bridge-legs. The total drive system losses are  $P_{\rm VDS}=703\,\rm W$ , corresponding to a system efficiency at nominal operation of  $\eta_{\rm DS}=91.4\%$ .

The volume distribution of the system is shown in Figure 10b, with a boxed volume of the complete drive system at  $8.2\,L$  (or  $500\,\text{in}^3$ ) resulting in a power density of  $0.91\,\text{kW}\,L^{-1}$  ( $15\,\text{W}\,\text{in}^{-3}$ ). The outer motor dimensions are  $205\,\text{mm} \times 105\,\text{mm} \times 105\,\text{mm}$ , for a total boxed volume of  $4.9\,L$  (or  $300\,\text{in}^3$ ), that is 60% of the system. The converter, at  $3.3\,L$  (or  $200\,\text{in}^3$ ), accounts for the remaining 40% of the system volume (including the encoder). Without the MPPB concept, the electrolytic capacitor volume *alone* would account for  $1\,L$  (or  $61\,\text{in}^3$ ), adding 30% to the converter and 12% to the total system—and preventing integration due to the lifetime considerations discussed previously.

Electronics **2022**, 11, 280 20 of 49

**Figure 10.** (a) Loss breakdown at the nominal operating point for the (i) inverter and (ii) motor. (b) Volume distribution for the realized demonstrator.

# 3.4. Detailed Motor Integration and Implementation

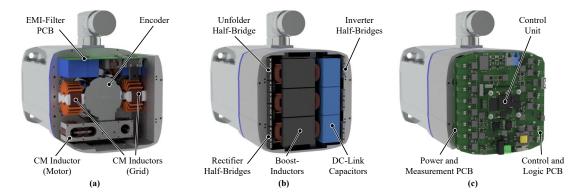

The motor integration must allow a retrofitting of an existing motor within the same flange dimension, mandating an axial stator mount of the power electronics system (options for motor integration were surveyed in [83]). The implementation is shown in Figure 11, with the three-level stack up and construction detailed side by side.

Firstly, the end plate was replaced to provide an interface for the converter system. The first level of the integrated drive system (Figure 11a) contains the EMI filter components, which were distributed around the encoder. Cables were mounted to the corresponding side walls to connect to the grid CM inductors, which were also connected to the filter Printed Circuit Board (PCB). The filter PCB contains all of the remaining DM and CM filter components and was connected to the Earth and the motor housing. An Earth- and housing-connected copper plate (not shown) was installed between the EMI filter and the motor-side CM inductor to provide shielding, and similarly, an aluminum plate was installed between the first and second levels to (a) shield the filter from the bridge-leg high-frequency noise and (b) provide mechanical stability.

The second converter level (Figure 11b) contains all power components, including the power semiconductor bridge-legs, the boost inductors, and the DC-link capacitors. The bridge-legs were connected to the DC-link capacitors through the power PCB and to the motor windings through the motor-side CM inductor. Critically, the vast majority of the converter losses were generated in this second level, resulting in the highest temperature, and this was where the electrolytic capacitors would need to be placed to connect to the DC-link—making a system with electrolytic capacitors infeasible.

Electronics **2022**, 11, 280 21 of 49

**Figure 11.** Motor integration of the VSD system, built up in three layers from left to right. (a) Encoder and filter components, (b) power components, and (c) circuitry and control unit.

The third level (Figure 11c) contains the gate drive, measurement, control, and logic circuitry on two separate PCBs, with the control unit on the top. Converter losses are cooled via the surface—and the thermal resistance (and insulation) can be improved through potting, if desired—with the large thermal capacitance improving the thermal characteristics significantly, since the system is not operated at full power for extended periods. The final motor-integrated drive is shown in Figure 12.

**Figure 12.** Photograph of the complete motor-integrated, MPPB-operated, single-phase-supplied, variable-speed-drive system of Figure 1.

# 4. Hardware Demonstration Verification

To evaluate the motor-integrated hardware demonstrator of Figure 12, the overall operation of the drive system across the continuously varying operating points, motor drive speeds, and torque fluctuation was evaluated. Full operation cannot be validated with a resistor–inductor (RL) load alone, and a complete motor test bench was employed here (instead of driving the compressor itself). This test bench comprises a motor bed, the Device-Under-Test (DUT), a speed and torque sensor (*TM310* with a maximum torque bandwidth of 5 kHz from Magtrol [84]), and a load motor operated with a commercially available drive system from Siemens with a constant load torque [50]. An identical setup was employed for the no-load measurements of Section 3. First, the concept was validated with time-domain measurements and waveforms. Then, the loss model was verified, and

Electronics **2022**, 11, 280 22 of 49

EMI measurements were taken before validating the extended functionality (distorted grid voltage, ride-through operation, and battery supply operation) in Section 5.

Note that, due to the limited availability of the optimal  $16\,\mathrm{m}\Omega$  power semiconductors specified in Table 3, all transistors were implemented as the  $32\,\mathrm{m}\Omega$  device (C3M0032120K [71]) for the following measurements.

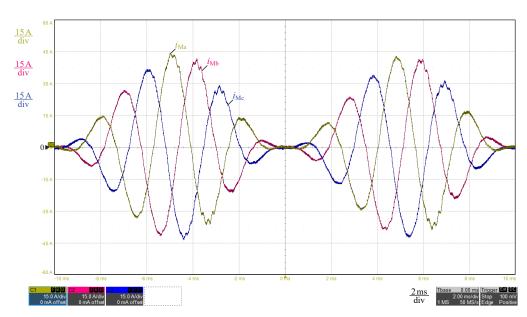

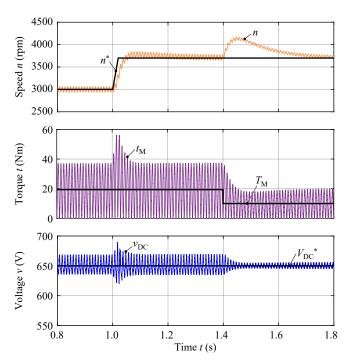

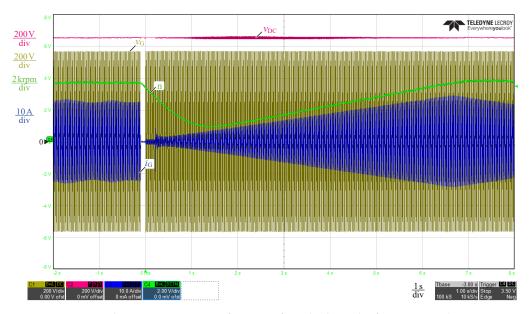

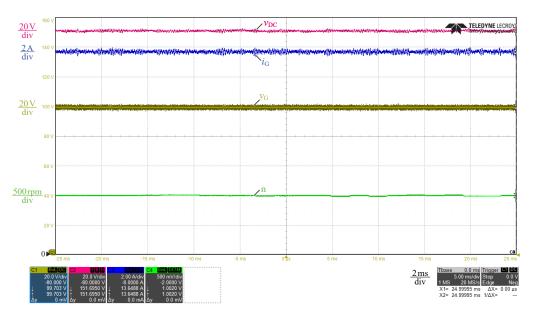

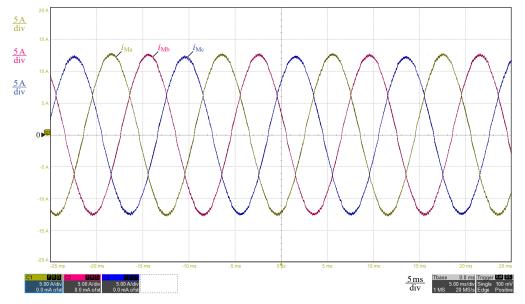

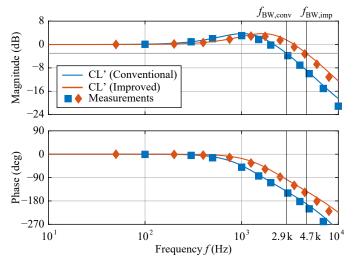

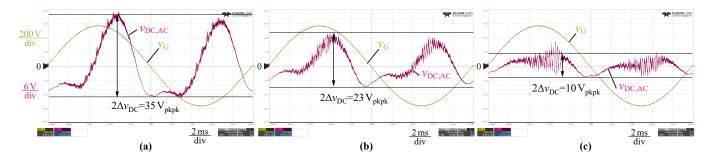

## 4.1. Time-Domain Waveforms and Operation

Firstly, the theoretical aspects of Section 2 were verified for the nominal operating point, as described in Table 2. The measured waveforms are shown in Figure 13, where the grid current (20.6 Arms) and voltage were in-phase for unity power factor operation (measured at 99.95%) at 8.2 kW input power, a steady DC-link voltage near the reference of 650 V, and a speed equal to the reference of 3700 rpm with a speed ripple so small that it is not visible on this oscilloscope capture. The low-frequency ripple of the DC-link voltage is investigated in depth in Appendix B and corresponds here to 35 Vpkpk, nearly identical to the simulation results of 34 Vpkpk shown in Figure 5. The measured motor currents are shown in Figure 14, corresponding to a phase current stress of 18.5 Arms and, again, matching the theoretical results in both behavior and predicted amplitude. Overall, the system behavior was correct and expected, validating the MPPB approach and the predicted operation.

**Figure 13.** Measured waveforms under steady-state, nominal operation: grid voltage (yellow), DC-link voltage (red), grid current (blue), and speed (1000 rpm/div, green).

# 4.2. Efficiency