An Improved Proposed Single Phase Transformerless Inverter with Leakage Current Elimination and Reactive Power Capability for PV Systems Application †

Abstract

:1. Introduction

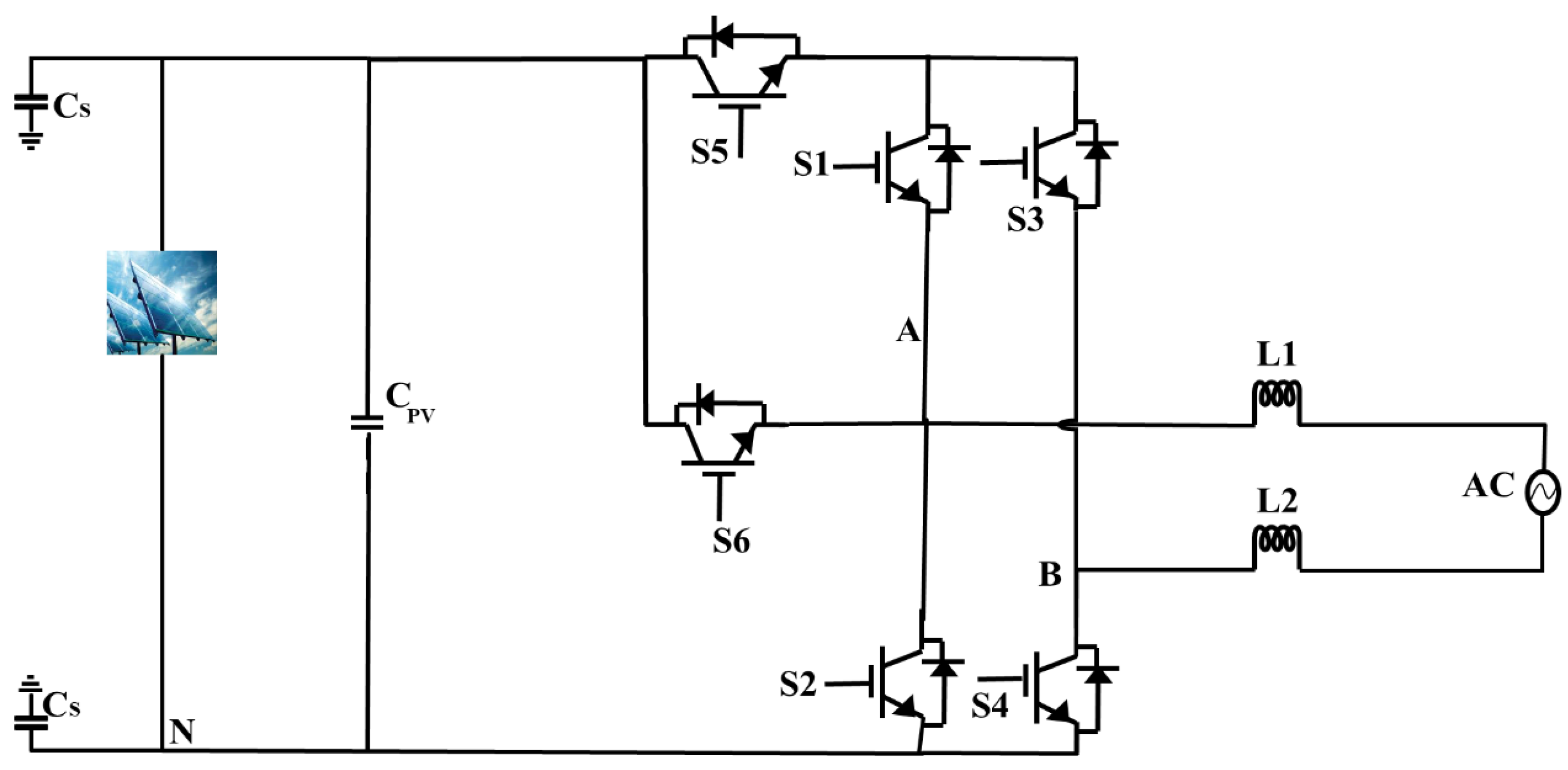

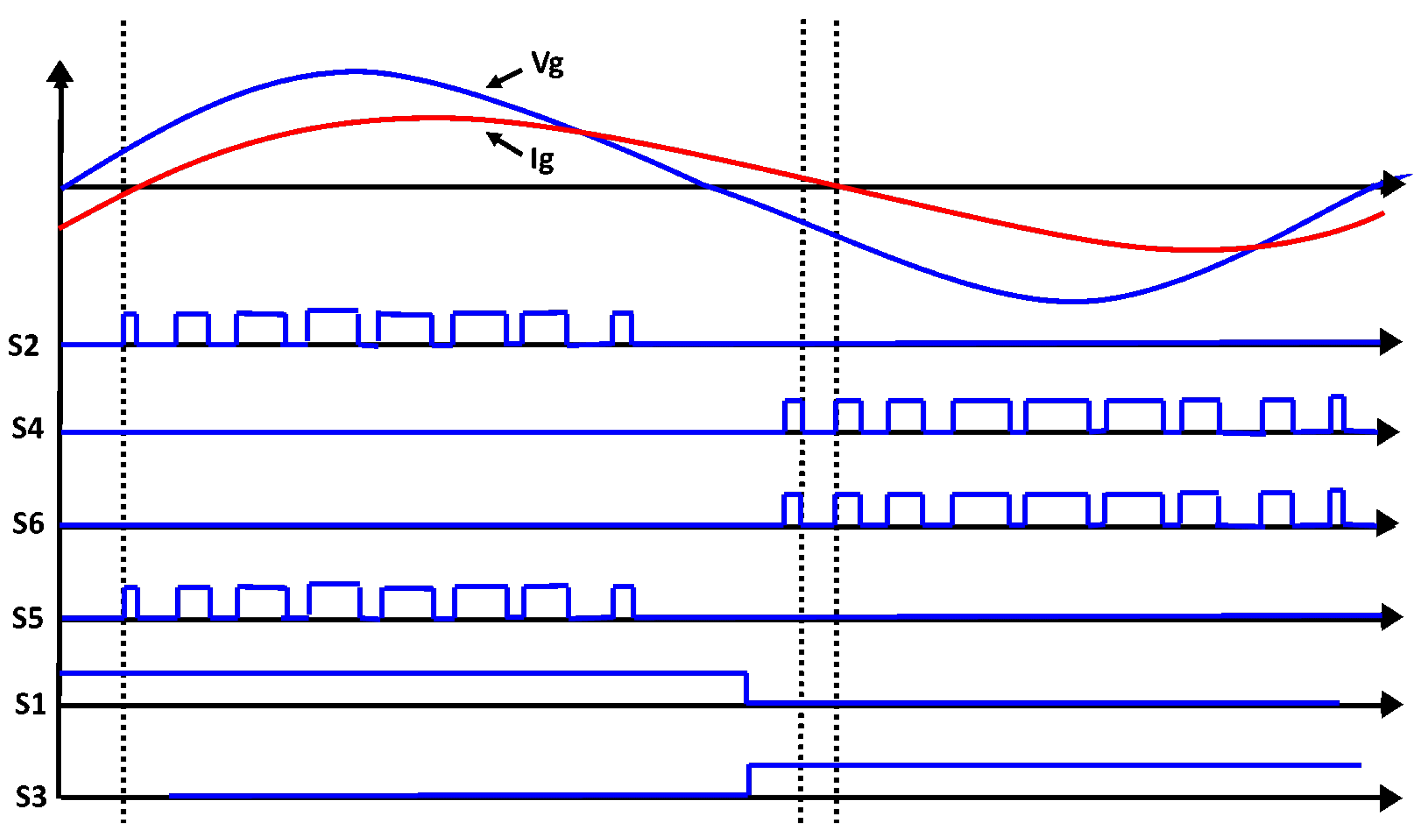

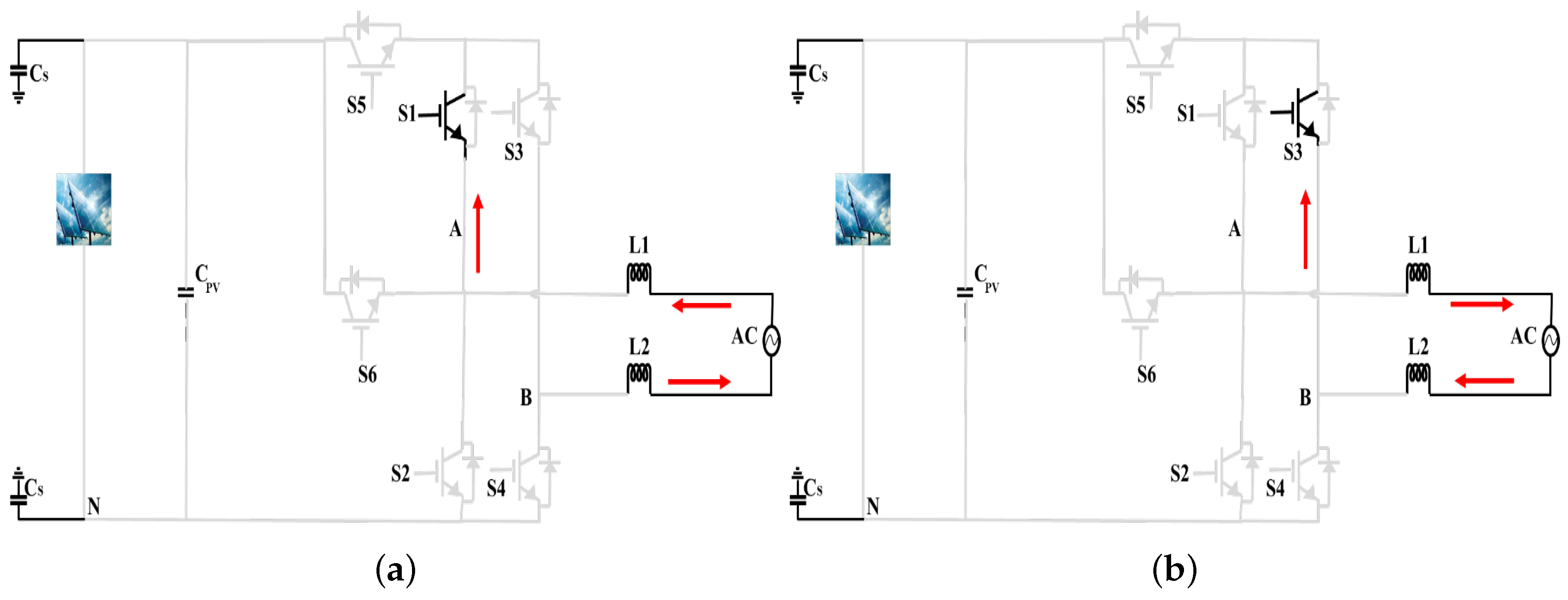

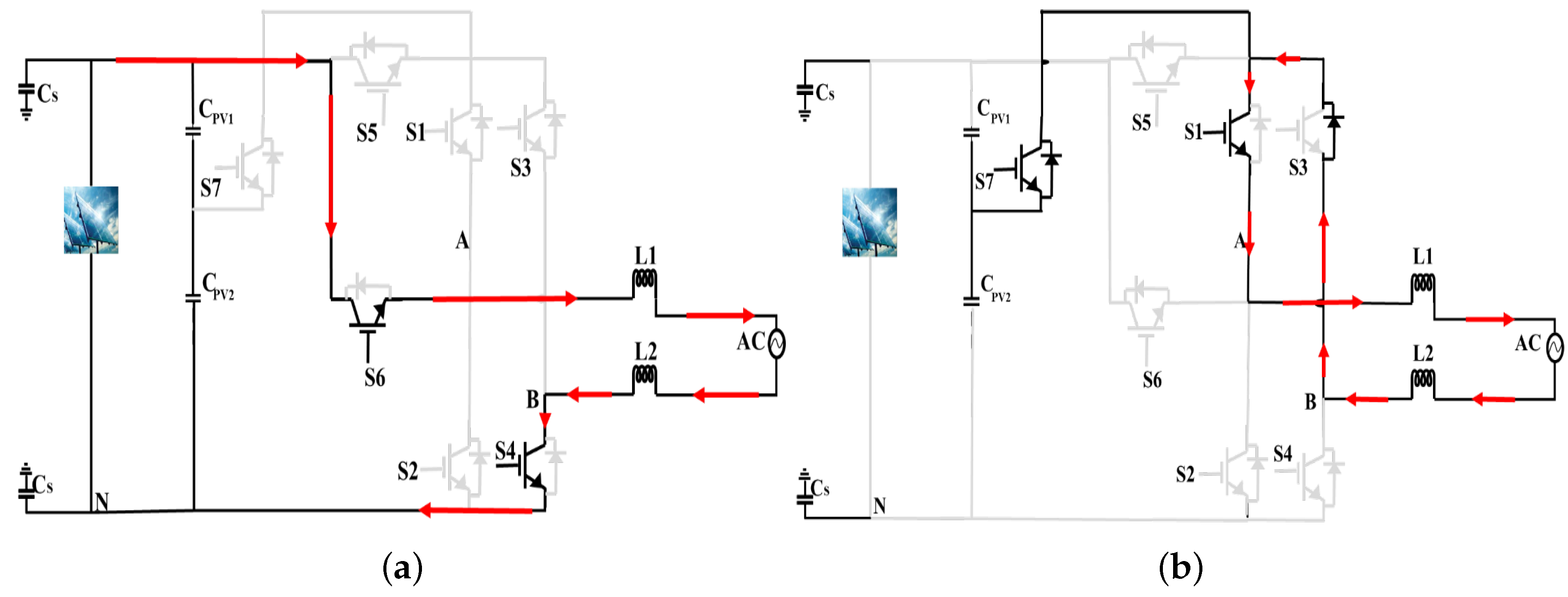

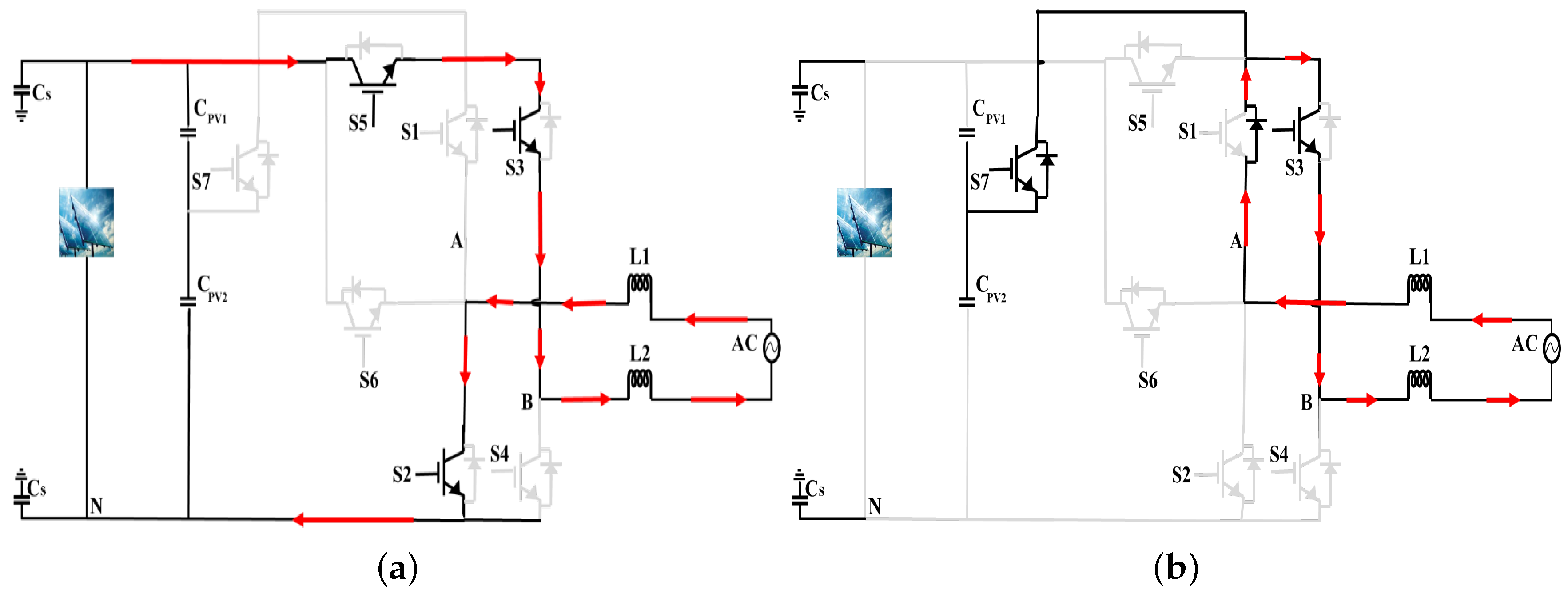

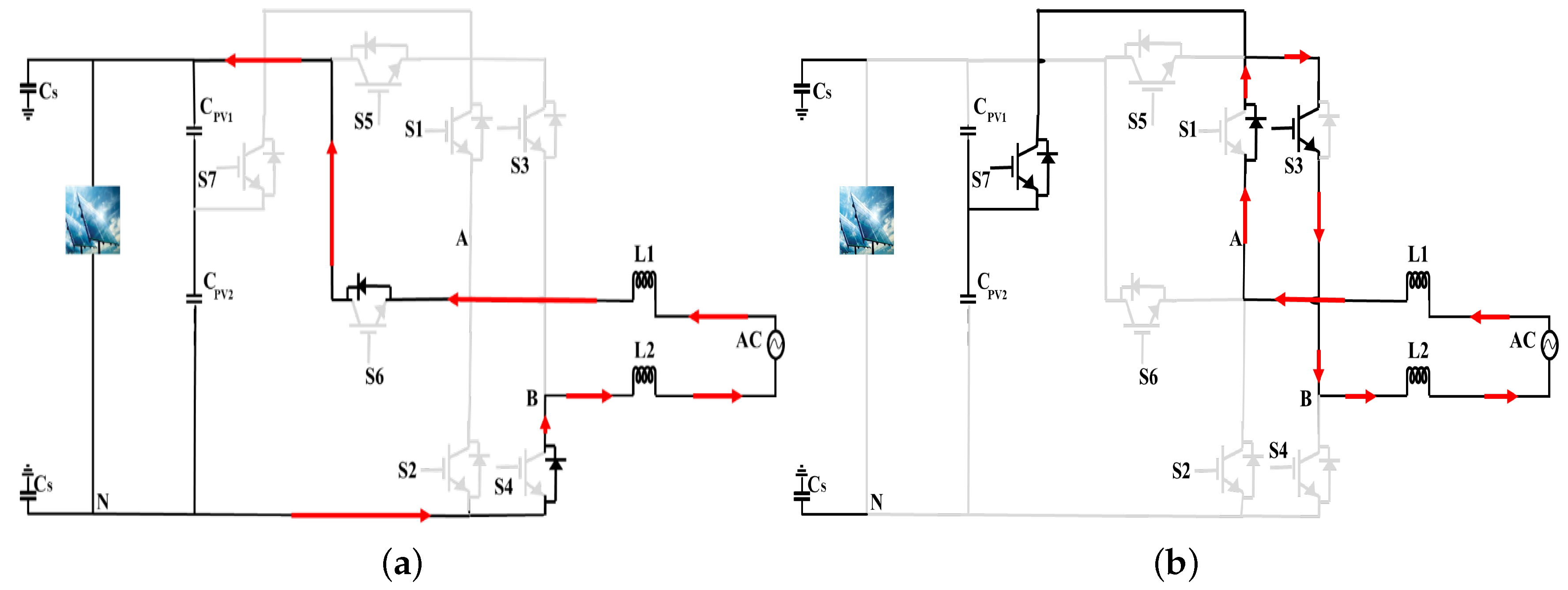

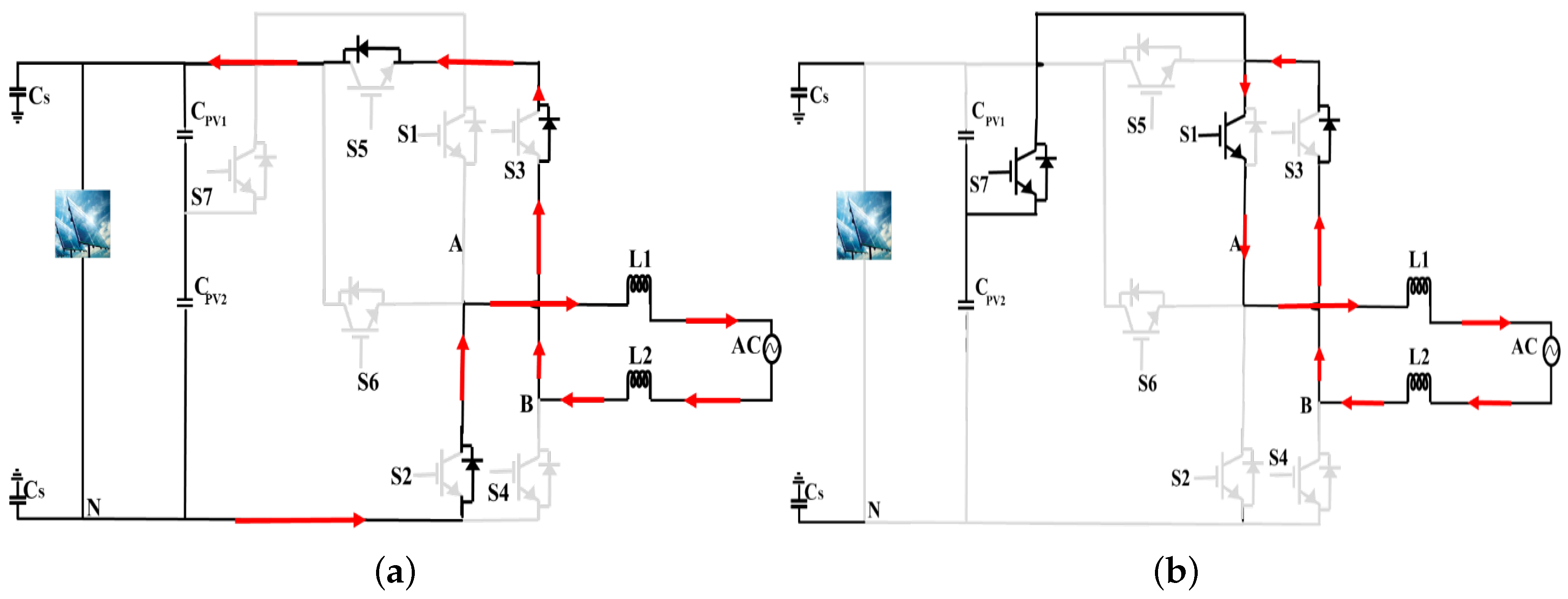

2. Proposed Topology with Leakage Current Elimination and Reactive Power Generation

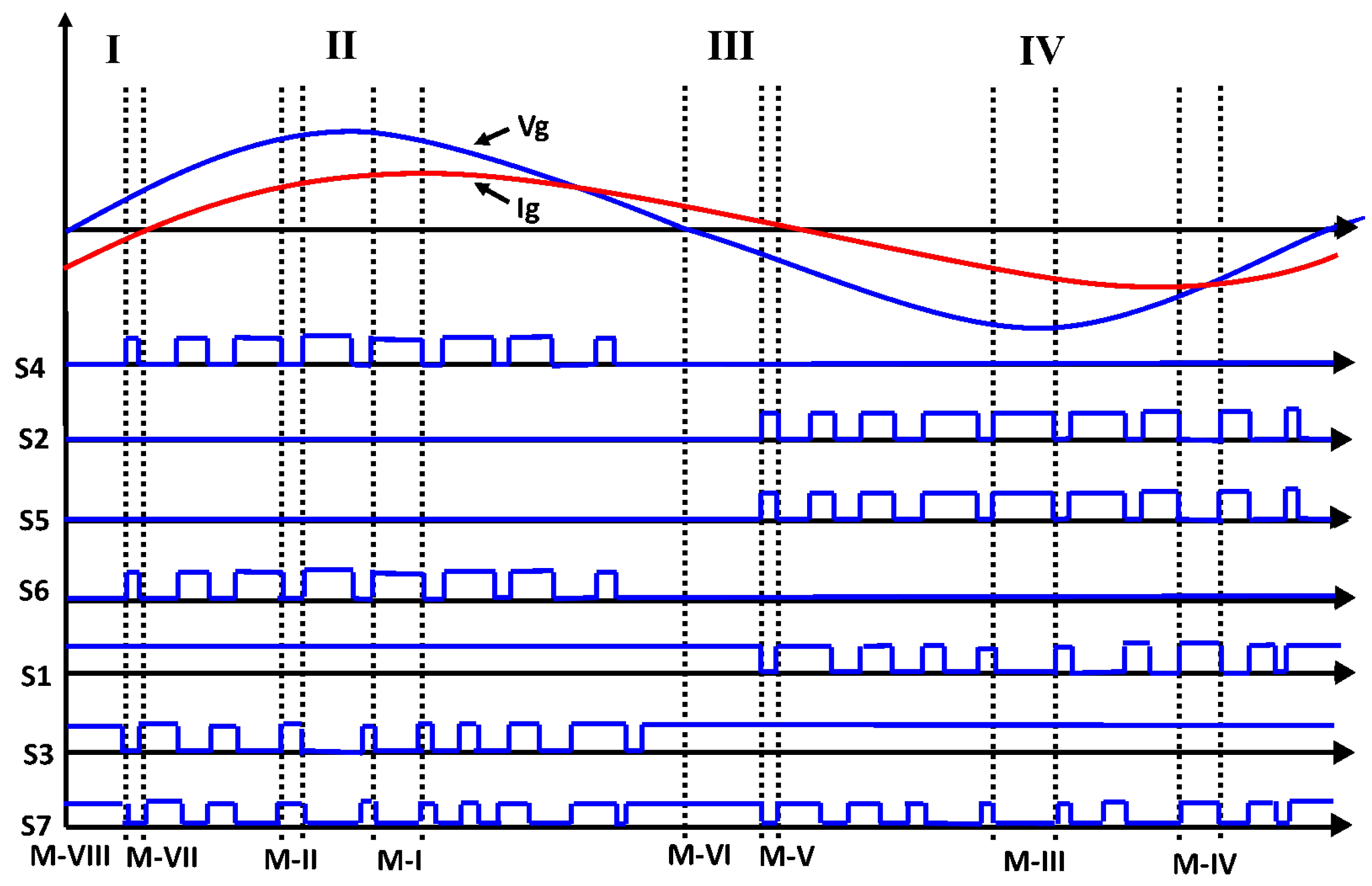

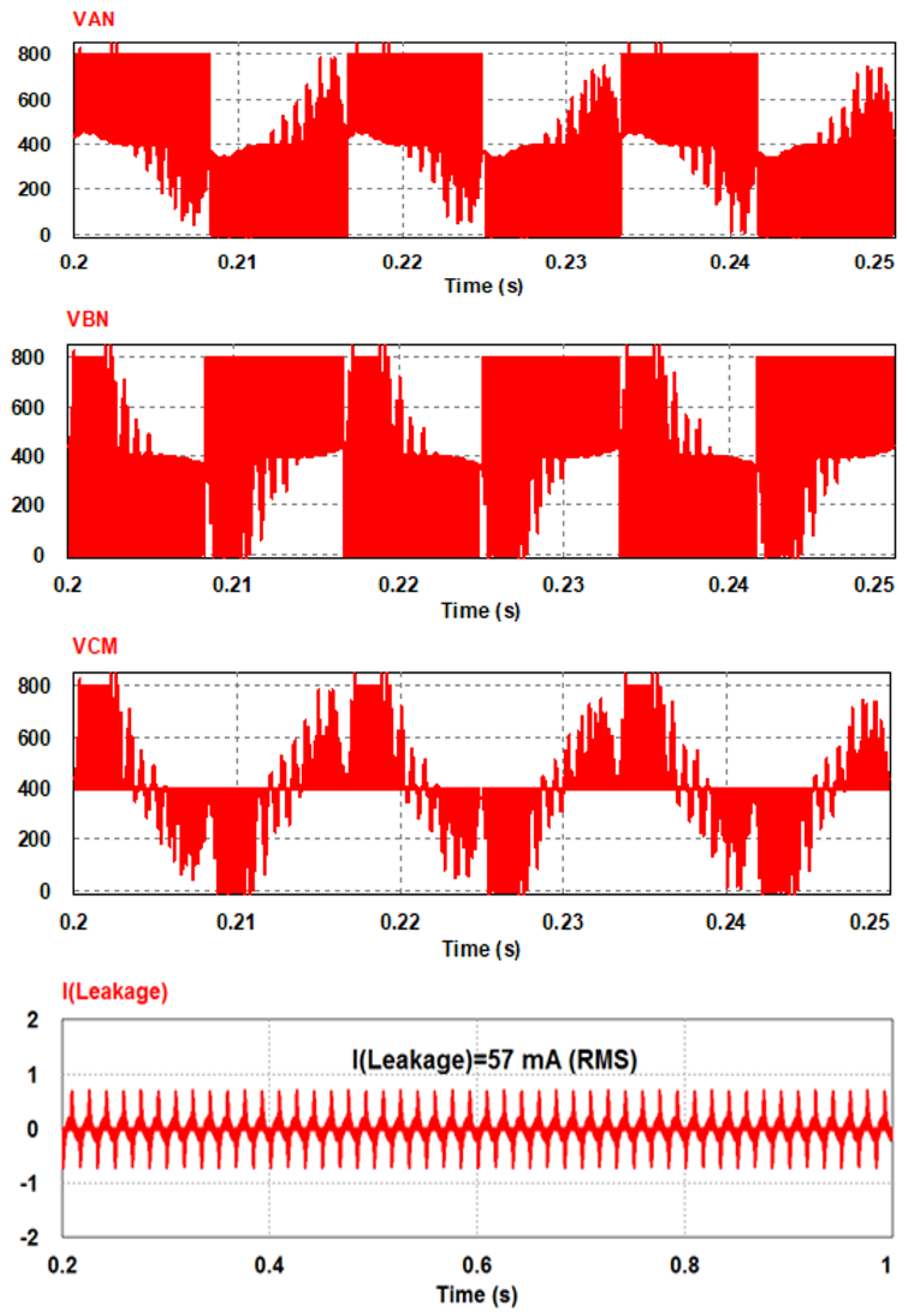

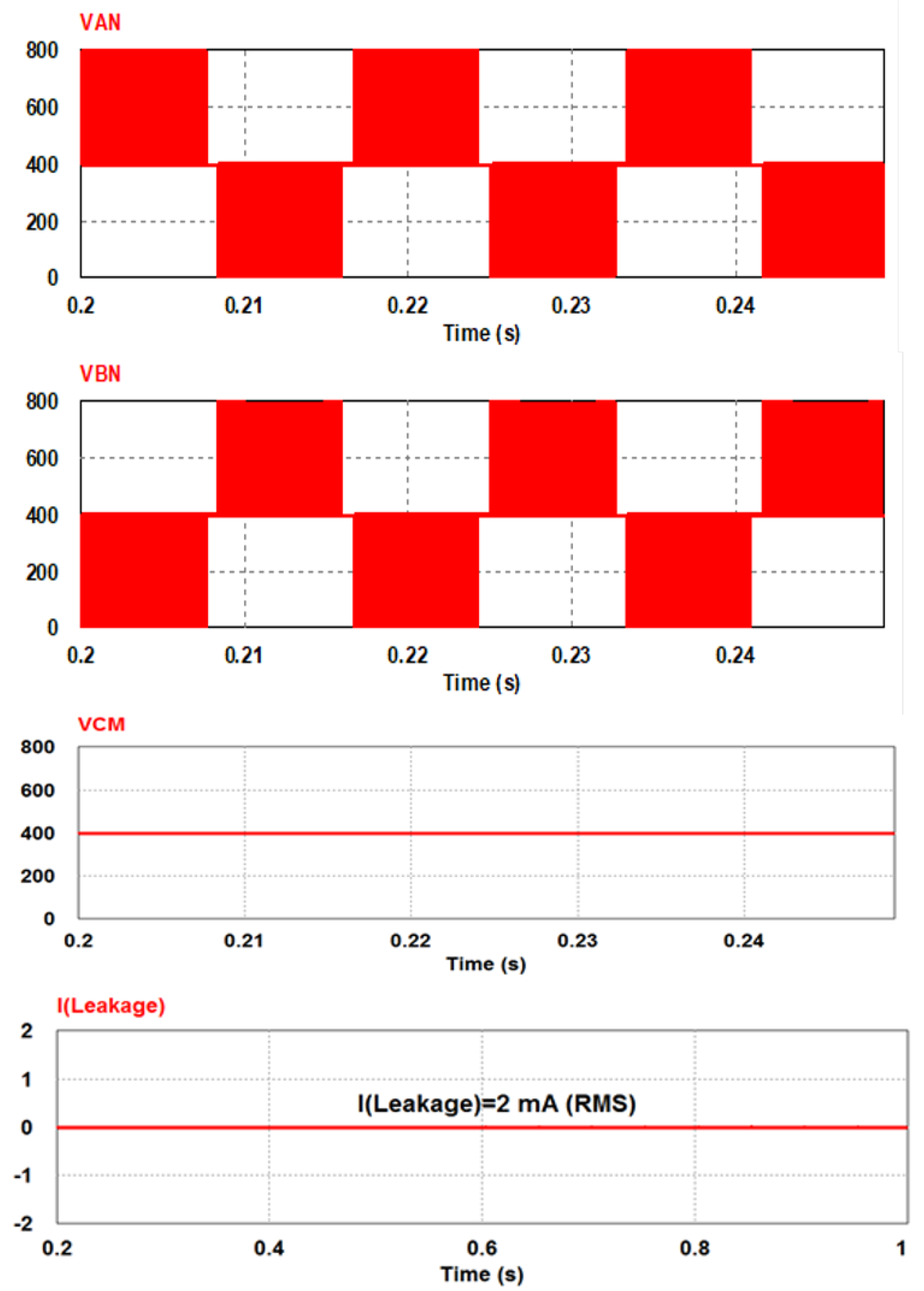

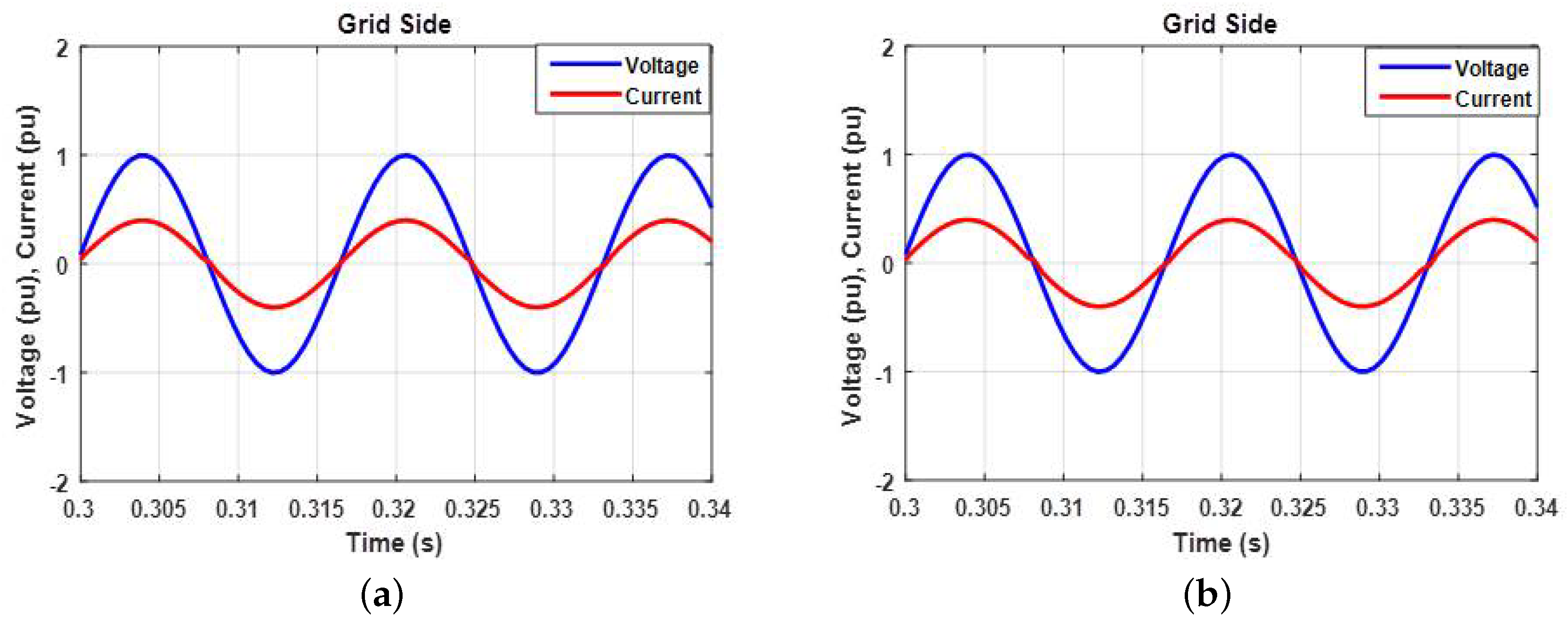

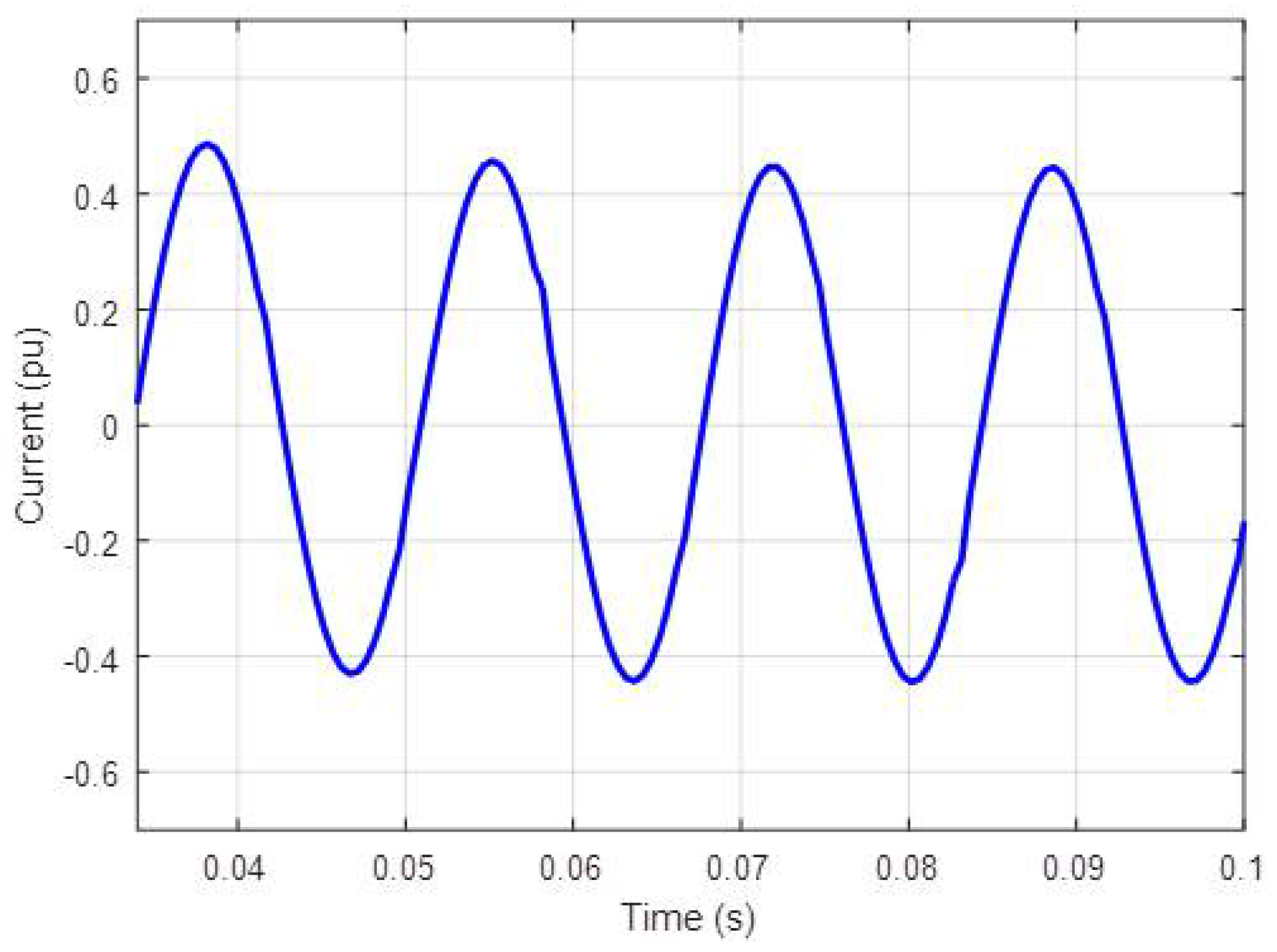

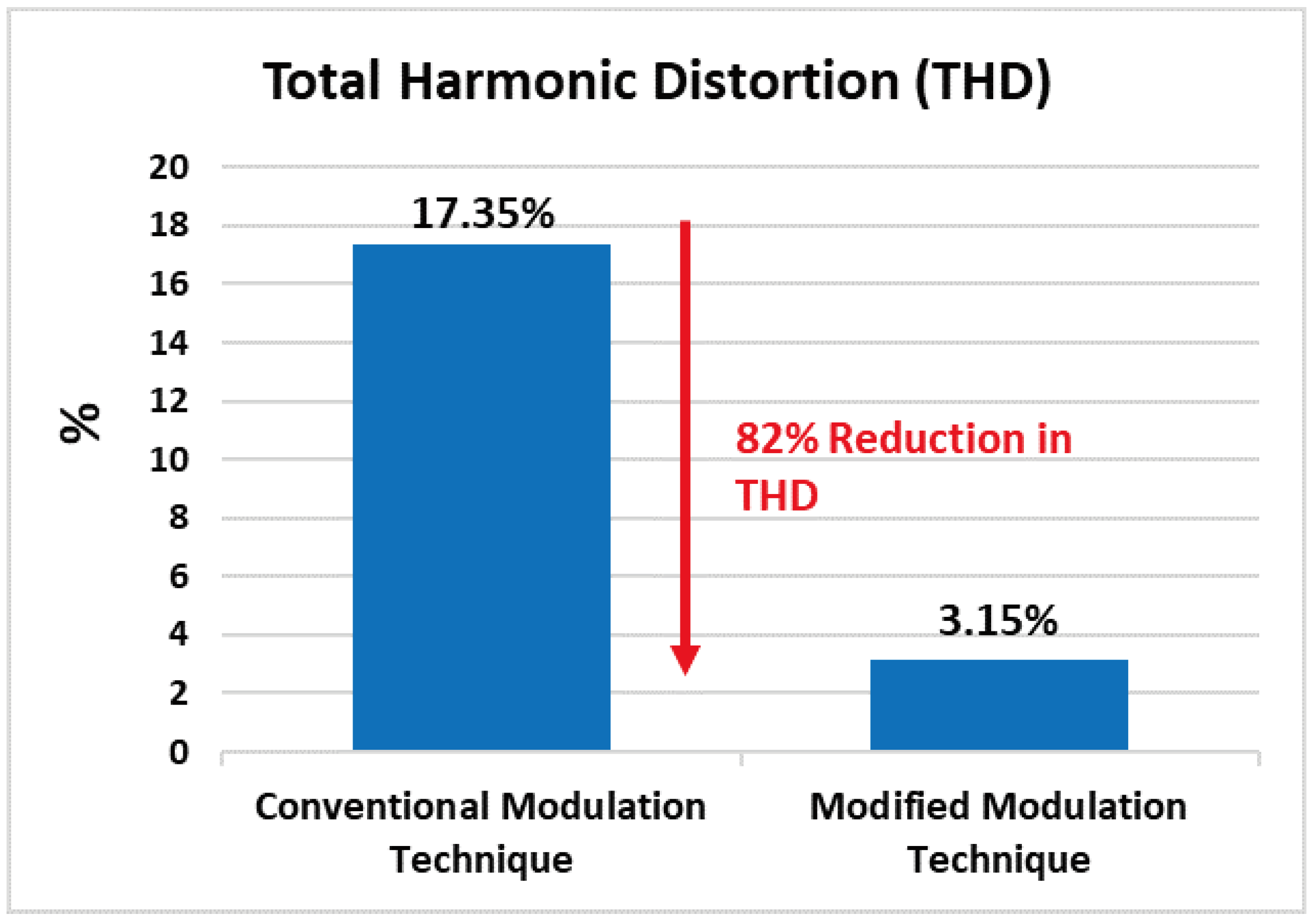

3. Modulation Technique for Reactive Power Generation

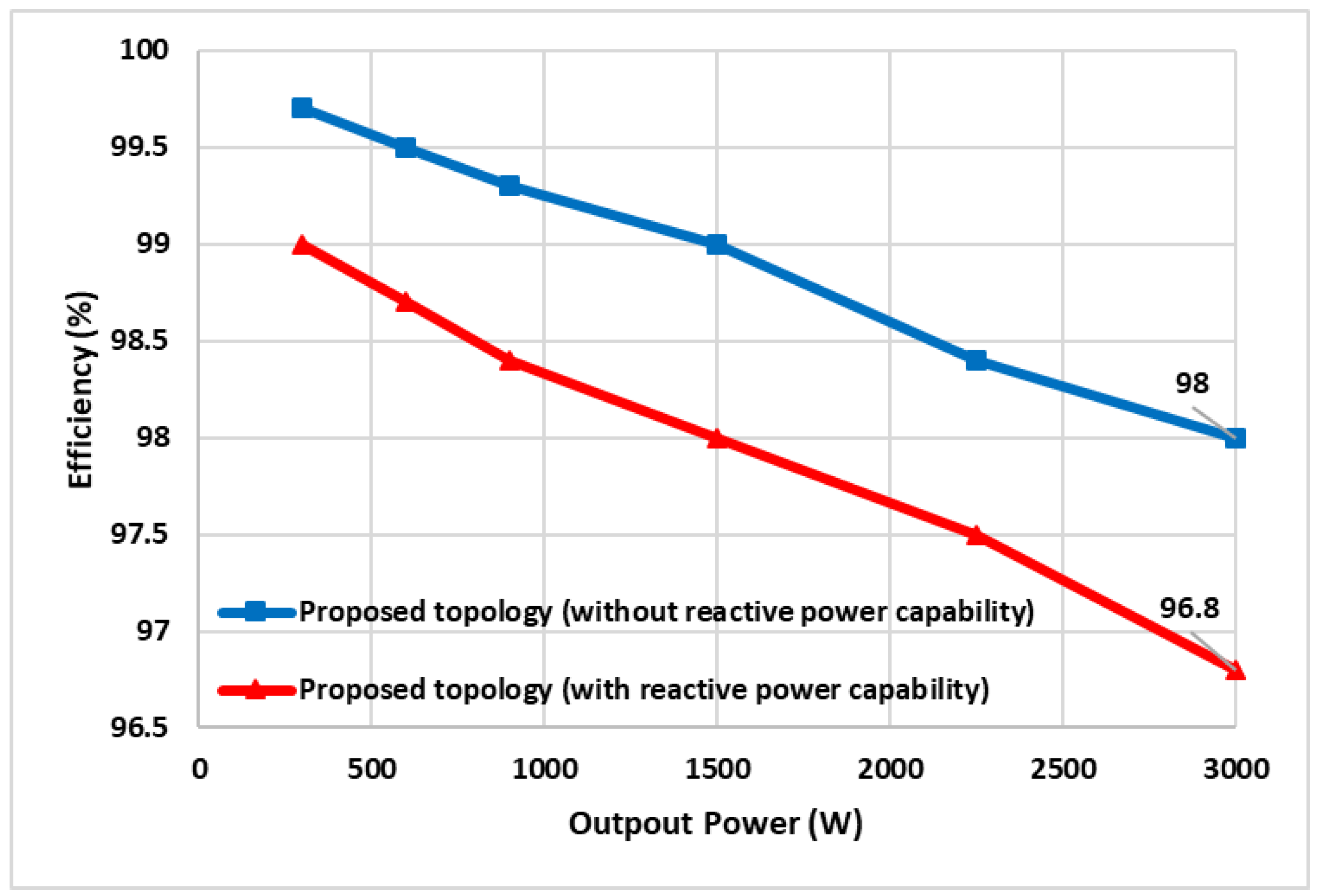

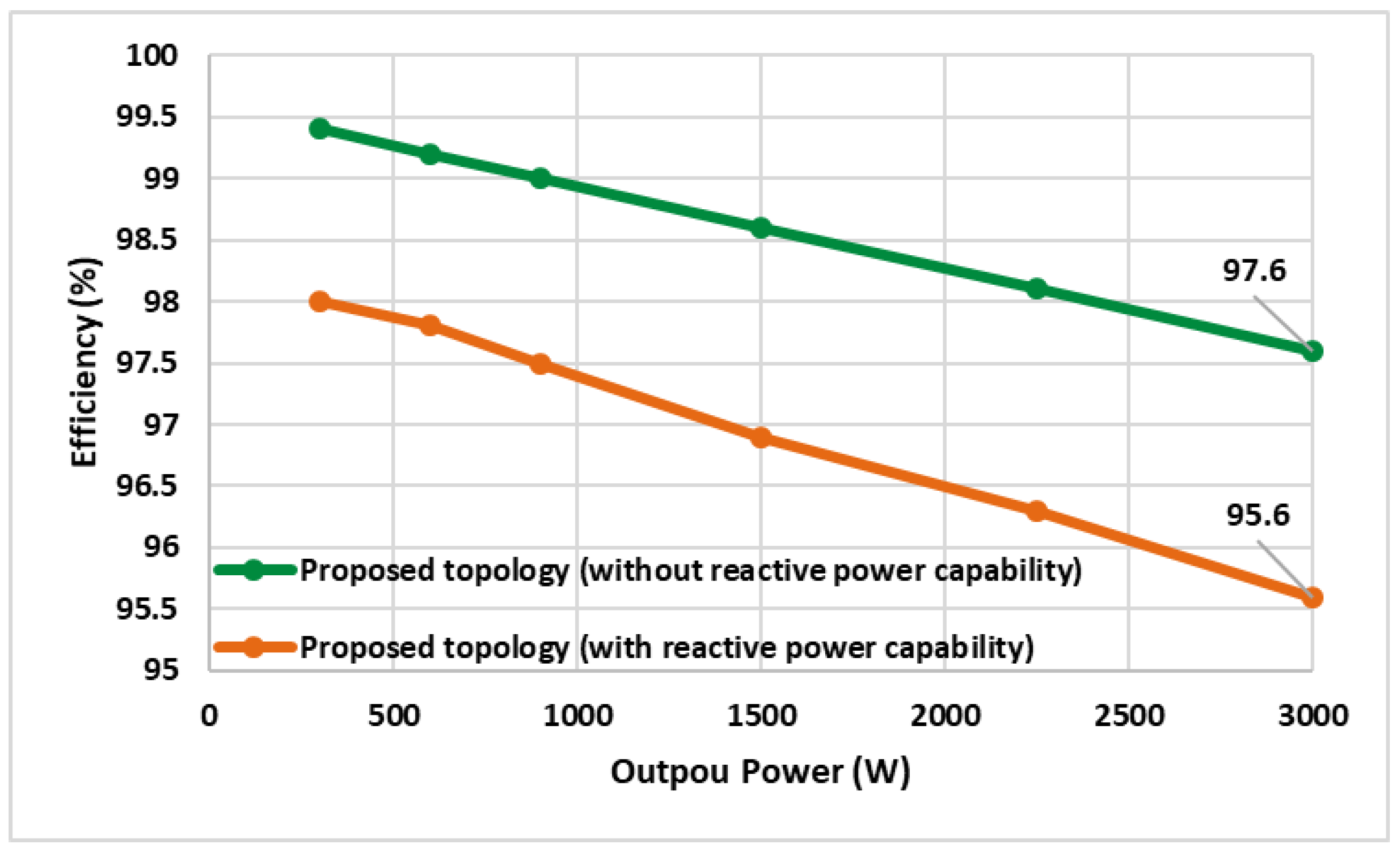

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Li, W.; Gu, Y.; Luo, H.; Cui, W.; He, X.; Xia, C. Topology review and derivation methodology of single-phase transformerless photovoltaic inverters for leakage current suppression. IEEE Trans. Ind. Electron. 2015, 62, 4537–4551. [Google Scholar] [CrossRef]

- Guo, X.; He, R.; Jian, J.; Lu, Z.; Sun, X.; Guerrro, M. Leakage current elimination of four-leg inverter for transformerless three-phase PV systems. IEEE Trans. Power Electron. 2016, 31, 1841–1846. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Rodríguez, P.; Vázquez, G.; Aldabas, E. A new high-efficiency single-phase transformerless PV inverter topology. IEEE Trans. Ind. Electron. 2011, 58, 184–191. [Google Scholar] [CrossRef] [Green Version]

- Dutta, S.; Debnath, D.; Chatterjee, K. A grid-connected single-phase transformerless inverter controlling two solar PV arrays operating under different atmospheric conditions. IEEE Trans. Ind. Electron. 2018, 65, 374–385. [Google Scholar] [CrossRef]

- Knabben, G.C.; Schmitz, L.; Coelho, R.F.; Martins, D.C.; Custódio, O.J.; de Medeiros, R.Z.; Bettiol, A.L. Transformerless micro-inverter for grid-connected photovoltaic systems. In Proceedings of the 52nd International Universities Power Engineering Conference (UPEC), Heraklion, Greece, 28–31 August 2017; pp. 1–6. [Google Scholar] [CrossRef]

- AZhao, T.; Bhavaraju, V.; Nirantare, P.; Xu, J. Evaluation of commercial scale transformerless solar inverter technology. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 5342–5348. [Google Scholar] [CrossRef]

- Chen, B.; Lai, J.S. A family of single-phase transformerless inverters with asymmetric phase-legs. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 2200–2205. [Google Scholar] [CrossRef]

- Lee, J.; Lee, K. New modulation techniques for a leakage current reduction and a neutral-point voltage balance in transformerless photovoltaic systems using a three-level inverter. IEEE Trans. Power Electron. 2014, 29, 1720–1732. [Google Scholar] [CrossRef]

- Freddy, T.; Rahim, N.; Hew, W.; Che, H. Modulation techniques to reduce leakage current in three-phase transformerless H7 photovoltaic inverter. IEEE Trans. Ind. Electron. 2015, 62, 322–331. [Google Scholar] [CrossRef]

- Cha, W.; Kim, K.; Cho, Y.; Lee, S.; Kwon, B. Evaluation and analysis of transformerless photovoltaic inverter topology for efficiency improvement and reduction of leakage current. IET Power Electron. 2014, 8, 255–267. [Google Scholar] [CrossRef]

- Ardashir, F.; Siwakoti, P.; Sabahi, M.; Hosseini, S.; Blaabjerg, F. S4 grid-connected single-phase transformerless inverter for PV application. In Proceedings of the IECON 2016—42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 3–26 October 2016; pp. 2384–2389. [Google Scholar]

- Gotekar, P.; Muley, S.; Kothari, D.; Umre, B. Comparison of full bridge bipolar, H5, H6 and HERIC inverter for single phase photovoltaic systems—A review. In Proceedings of the 2015 Annual IEEE India Conference (INDICON), New Delhi, India, 17–20 December 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Zhang, L.; Sun, K.; Xing, Y.; Xing, M. H6 Transformerless Full-Bridge PV Grid-Tied Inverters. IEEE Trans. Power Electron. 2014, 29, 1229–1238. [Google Scholar] [CrossRef]

- Yang, Y.; Blaabjerg, F.; Wang, H. Low-voltage ride-through of single-phase transformerless photovoltaic inverters. IEEE Trans. Ind. Appl. 2014, 50, 1942–1952. [Google Scholar] [CrossRef]

- Wu, T.; Kuo, C.; Sun, K.; Hsieh, H. Combined unipolar and bipolar PWM for current distortion improvement during power compensation. IEEE Trans. Power Electron. 2013, 29, 1702–1709. [Google Scholar] [CrossRef]

- Bojoi, R.; Limongi, L.; Roiu, D.; Tenconi, A. Enhanced Power Quality Control Strategy for Single-Phase Inverters in Distributed Generation Systems. IEEE Trans. Power Electron. 2011, 26, 798–806. [Google Scholar] [CrossRef]

- Zong, X. A Single Phase Grid Connected DC/AC Inverter with Reactive Power Control for Residential PV Application. Master’s Dissertation, University of Toronto, Toronto, ON, USA, 2011. Available online: https://tspace.library.utoronto.ca/bitstream/1807/31665/1/Zong_Xiangdong_201111_MASC_thesis.pdf (accessed on 11 March 2018).

- Chen, B.; Gu, B.; Zhang, L.; Lai, J. A novel pulse-width modulation method for reactive power generation on a CoolMOS-and SiC-diode-based transformerless inverter. IEEE Trans. Ind. Electron. 2016, 63, 1539–1548. [Google Scholar] [CrossRef]

- Islam, M.; Afrin, N.; Mekhilef, S. Efficient single-phase transformerless inverter for grid-tied PVG system with reactive power control. IEEE Trans. Sustain. Energy. 2016, 7, 1205–1215. [Google Scholar] [CrossRef]

- Jahdi, S.; Alatise, O.; Bonyadi, R.; Alexakis, P.; Fisher, C.A.; Gonzalez, J.A.O.; Ran, L.; Mawby, P. An Analysis of the Switching Performance and Robustness of Power MOSFETs Body Diodes: A Technology Evaluation. IEEE Trans. Power Electron. 2015, 30, 2383–2394. [Google Scholar] [CrossRef] [Green Version]

- Chen, B.; Gu, B.; Zhang, L.; Zahid, Z.U.; Lai, J.S.J.; Liao, Z.; Hao, R. A high-efficiency MOSFET transformerless inverter for nonisolated microinverter applications. IEEE Trans. Power Electron. 2015, 30, 3610–3622. [Google Scholar] [CrossRef]

- Castellazzi, A.; Fayyaz, A.; Romano, G.; Riccio, M.; Irace, A.; Urresti-Ibanez, J.; Wright, N. Transient out-of-SOA robustness of SiC power MOSFETs. Proceeings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017. [Google Scholar] [CrossRef]

- Jordan, J.; Esteve, V.; Sanchis-Kilders, E.; Dede, E.J.; Maset, E.; Ejea, J.B.; Ferreres, A. A comparative performance study of a 1200 V Si and SiC MOSFET intrinsic diode on an induction heating inverter. IEEE Trans. Power Electron. 2014, 29, 2550–2562. [Google Scholar] [CrossRef]

- Wang, Z.; Zhang, J.; Wu, X.; Sheng, K. Evaluation of reverse recovery characteristic of silicon carbide metal–oxide–semiconductor field-effect transistor intrinsic diode. IET Power Electron. 2016, 9, 969–976. [Google Scholar] [CrossRef]

- Kusumoto, O.; Ohoka, A.; Horikawa, N.; Tanaka, K.; Niwayama, M.; Uchida, M.; Kanzawa, Y.; Sawada, K.; Ueda, T. Reliability of Diode-Integrated SiC Power MOSFET(DioMOS). Microelectron. Reliab. 2016, 58, 158–163. [Google Scholar] [CrossRef]

- Chen, K.; Zhao, Z.; Yuan, L.; Lu, T.; He, F. The Impact of Nonlinear Junction Capacitance on Switching Transient and Its Modeling for SiC MOSFET. IEEE Trans. Electron Devices 2015, 62, 333–338. [Google Scholar] [CrossRef]

- Fayyaz, A.; Romano, G.; Castellazzi, A. Body diode reliability investigation of SiC power MOSFETs. Microelectron. Reliab. 2016, 64, 530–534. [Google Scholar] [CrossRef] [Green Version]

- Wang, Z.; Ouyang, J.; Zhang, J.; Wu, X.; Sheng, K. Analysis on reverse recovery characteristic of SiC MOSFET intrinsic diode. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 4–18 September 2014; pp. 2832–2837. [Google Scholar] [CrossRef]

- Liu, H.; Wu, H.; Lu, Y.; Xing, Y.; Sun, K. A high efficiency inverter based on SiC MOSFET without externally antiparalleled diodes. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC 2014, Fort Worth, TX, USA, 16–20 March 2014; pp. 163–167. [Google Scholar] [CrossRef]

- Hou, X.; Boroyevich, D.; Burgos, R. Characterization on latest-generation SiC MOSFET’s body diode. In Proceedings of the 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016; pp. 247–252. [Google Scholar] [CrossRef]

- Almasoudi, F.; Alatawi, K.; Matin, M. High efficiency three level transformerless inverter based on SiC MOSFETs for PV applications. In Proceedings of the 2017 IEEE International Conference on Electro Information Technology (EIT), Lincoln, NE, USA, 14–17 May 2017; pp. 617–622. [Google Scholar] [CrossRef]

- Almasoudi, F.M.; Alatawi, K.S.; Matin, M. High efficiency H6 single-phase transformerless grid-tied PV inverter with proposed modulation for reactive power generation. In Proceedings of the Wide Bandgap Power Devices and Applications II, San Diego, CA, USA, 7–8 August 2017. [Google Scholar]

| Parameter | Value |

|---|---|

| Input Voltage | 800 V |

| Grid Voltage | 120 V |

| Grid Frequency | 60 Hz |

| Switching Frequency | 16 kHz and 100 kHz |

| DC Bus Capacitor () | 970 F |

| Stray Parasitic Capacitance | 300 nF |

| Output Power | 3 kW |

| Output Power | 300 W | 600 W | 900 W | 1500 W | 2250 W | 3000 W | CEC |

|---|---|---|---|---|---|---|---|

| Proposed Topology (without reactive power capability) | 99.7% | 99.5% | 99.3% | 99% | 98.4% | 98% | 98.7% |

| Proposed Topology (with reactive power capability) | 99.2% | 99% | 98.6% | 98.2% | 97.5% | 96.8% | 97.7% |

| Output Power | 300 W | 600 W | 900 W | 1500 W | 2250 W | 3000 W | CEC |

|---|---|---|---|---|---|---|---|

| Proposed Topology (without reactive power capability) | 99.4% | 99.3% | 99% | 98.6% | 98.1% | 97.6% | 98.3% |

| Proposed Topology (with reactive power capability) | 98% | 97.8% | 97.5% | 96.9% | 96.3% | 95.6% | 96.6% |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Almasoudi, F.; Matin, M. An Improved Proposed Single Phase Transformerless Inverter with Leakage Current Elimination and Reactive Power Capability for PV Systems Application. J. Low Power Electron. Appl. 2018, 8, 29. https://doi.org/10.3390/jlpea8030029

Almasoudi F, Matin M. An Improved Proposed Single Phase Transformerless Inverter with Leakage Current Elimination and Reactive Power Capability for PV Systems Application. Journal of Low Power Electronics and Applications. 2018; 8(3):29. https://doi.org/10.3390/jlpea8030029

Chicago/Turabian StyleAlmasoudi, Fahad, and Mohammad Matin. 2018. "An Improved Proposed Single Phase Transformerless Inverter with Leakage Current Elimination and Reactive Power Capability for PV Systems Application" Journal of Low Power Electronics and Applications 8, no. 3: 29. https://doi.org/10.3390/jlpea8030029