# Article Design of a Wideband Antenna for Wireless Network-On-Chip in Multimedia Applications

## Fernando Gutierrez

Liberolab R&D, Milano 20159, Italy; f.gutierrez@libero.it

Academic Editor: Davide Patti Received: 22 January 2017; Accepted: 26 March 2017; Published: 29 March 2017

Abstract: To allow fast communication—at several Gb/s—of multimedia content among processors and memories in a multi-processor system-on-chip, a new approach is emerging in literature: Wireless Network-on-Chip (WiNoC). With reference to this scenario, this paper presents the design of the key element of the WiNoC: the antenna. Specifically, a bow-tie antenna is proposed, which operates at mm-waves and can be implemented on-chip using the top metal layer of a conventional silicon CMOS (Complementary Metal Oxide Semiconductor) technology. The antenna performance is discussed in the paper and is compared to the state-of-the-art, including the zig-zag antenna topology that is typically used in literature as a reference for WiNoC. The proposed bow-tie antenna design for WiNoC stands out for its good trade-off among bandwidth, gain, size and beamwidth vs. the state-of-the-art.

**Keywords:** new trends in Network-on-Chip (NoC) architectures; on-chip antenna; networks-on-chip; wireless on-chip communications; multimedia communications

#### 1. Introduction

The complexity of multi-processor systems-on-chip (MPSoC) computing systems is continuously increasing [1–3]. Implementing multiple on-chip processing cores, and relevant memories, the bottleneck of the computing system becomes the inter-processor communication. To solve the inter-tile communication issue, the state-of-the-art has been characterized by the evolution from standard circuit-switched bus communications, e.g., SoC based on AMBA (Advanced Microcontroller Bus Architecture) bus as in [4], to packet-switched Network-on-Chip (NoC). This is the case of both homogeneous and heterogeneous MPSoCs [5,6]. In Homogeneous MPSoCs [7–10], all the interconnected tiles are of the same type; for example, eight MagicDSP tiles, each integrating an ARM<sup>TM</sup> core plus a VLIW (Very Long Instruction Word) processor, are interconnected through a NoC in [8]. Instead, multiple ARM Cortex cores are integrated on-chip in [10] to implement cloud sever-on-chip solutions. Other examples of homogeneous NoCs are in Ref. [7,9]. In heterogeneous MPSoCs, the tiles are different, see examples in [11-16]. Particularly in multimedia applications, programmable general-purpose cores can be integrated with memories and with co-processors for computing intensive applications. The co-processors are usually integrated as synthetizable IP (Intellectual Property) macrocells for computing intensive tasks such as video coding, motion estimation/compensation, noise removal or image enhancement, and multi-dimensional transforms [17–22].

The NoC is organized as a conventional ISO/OSI (International Standard Organization/Open Systems Interconnection) stack of layers. Indeed, a NoC aims at bringing on-chip the technologies already developed for computer and telecommunication networks [2,23–36]. The key building blocks of a NoC are routers [23–27], network interfaces (NI) [28], and links [29–33]. This paper will focus on links. Particularly, at the bottom of the stack, in the physical layer, conventional metal-wired links are characterized by the following limits:

- poor scalability;

- increased delay when transferring high data rates—at several Gb/s—among cores and/or memories placed at distances greater than 1 cm;

- increased power consumption to switch—at continuously increasing frequencies—the large capacitance offered by long metal wires.

In the recent literature, optical [31,34,35] or wireless [25,27,31,37–44] links are investigated as an alternative solution to classic metal wires to reduce latency and power consumption issues. Wireless NoC (WiNoC) links are easier to integrate on-chip with respect to silicon photonic solutions that, instead, are not yet mature enough to represent a reliable on-chip networking technology.

One of the main technology bottlenecks for WiNoC is printing the antenna on-chip, e.g., using top metal layers. As a matter of fact, using scaled CMOS (Complementary Metal Oxide Semiconductor) technologies, there are several works published in literature, operating from a few GHz to mm-waves, which already integrate on-chip the transmitter and the receiver, see Ref. [45–55]. Also, for the Analog–Digital converter [45,55] and for the building blocks of a NoC (e.g., NI, Router, Link in [23–33]) there are many works proposing on-chip integrated solutions. Instead, for the antenna, there are still open issues on optimizing the trade-off between area, gain and bandwidth. For example, the survey work [56] also declares that the on-chip antenna is still one of the most difficult components to integrate on-chip. Moreover, [56] declares that, although implementations of on-chip antennas have been proposed and studied in literature, there are still many challenges in manufacturing and integrating them in terms of area, performance, and energy overheads, especially as the number of on-chip cores will be scaling up in the future.

Within the above scenario, this work presents the design of a mm-wave antenna, with bow-tie topology, which ensures a compact size implementation and a high bandwidth, suited for WiNoC applications. The large bandwidth of the WiNoC antenna is important to achieve high data-rate connections also in the case of simple modulation schemes with low spectrum efficiency.

After this introduction, the rest of the paper is organized as follows. Section 2 presents the antenna architecture design, whereas Section 3 discusses the design of the layout and the performance characterization of the antenna. A comparison of the proposed antenna vs. the state-of-the-art is addressed in Section 4. Section 5 discusses the impact of the proposed antenna on the performance of the NoC infrastructure. Conclusions are drawn in Section 6.

#### 2. Design of the On-Chip High-Bandwidth Antenna

For the antenna operating frequency, the spectrum range of mm-waves (literally 30 GHz–300 GHz; in this work, restricted to 50 GHz–100 GHz) has been selected. As it has been demonstrated in Ref. [57–67], transceivers operating at such high frequencies can be designed using low-cost and low-power CMOS technologies. Above 50 GHz, the wavelength amounts to a few millimeters. This aspect is useful to reduce the size of the transceiver and of the antenna with respect to other designs operating at frequencies in the X Band (10 GHz) or below (at sub-GHz frequencies), see as an example Ref. [39,68–71].

In literature, a widely used mm-wave frequency range is the spectrum around 60 GHz. Indeed, this spectrum range is already used in high bandwidth communications due to the availability of a large unlicensed spectrum from 57 GHz to 66 GHz. Industrial alliances such as WiGiG or Wireless HD already use the 60 GHz spectrum.

It is worth noting that cm-range communications in WiNoC applications do not suffer from licensing issues since they are spatially limited and self-contained. Therefore, for WiNoC applications, a large spectrum can be addressed, from 50 GHz to 100 GHz in this work. Indeed, new CMOS SOI (Silicon on Insulator) technologies, characterized by a transition frequency Ft of 300 GHz, or higher, allow operating up to 100 GHz.

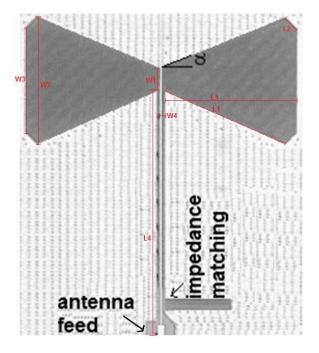

To meet this high bandwidth value, a wide band antenna design is proposed in this paper. To this aim, a bow-tie antenna topology, see Figure 1, is proposed. In classic antenna design, such as the

zig-zag antenna proposed for WiNoC in [31,37], the size of the antenna depends on the wavelength. Therefore, a conventional antenna is frequency-specific. Instead, the proposed bow-tie antenna is specified by angles and hence the bow-tie antenna is inherently a wideband antenna. With respect to an ideal bow-tie design, the antenna in Figure 1 has the following innovations:

- custom circuitry for antenna–driver matching

- rounded corners to reduce charge accumulation phenomena

Figure 1 shows the layout of the antenna with reference to implementation in a 65 nm SOI CMOS technology. Table 1 shows the values of the design parameters of the bow-tie antenna (L1, L2, L3, W1, W2, W3 and angle  $\alpha$  in Figure 1) and of the length and width (L4 and W4 in Figure 1) of the Co-planar Stripline (CPS), which connects the bow-tie antenna to the single-ended port of the transceiver (antenna feed in Figure 1). It is to be noted that the bow-tie antenna is characterized by both horizontal and vertical symmetry, and hence the values of the parameters in Table 1 are valid for both the right and left parts, and for both the top and bottom parts of the bow-tie antenna. Table 1 also shows the area of the rectangle that includes the proposed antenna. The SOI technology has been selected for this work, since it has been proven to be well suited for on-chip antenna integration and for mm-waves operations, see [57,60,61]. Indeed, due to the presence of a high resistive substrate in the SOI technology, it is possible to separate the integrated RF (Radio Frequency) part from the noise coupling due to other circuits (e.g., switching noise of the digital circuits). Moreover, in CMOS SOI technology, passive components can be designed with a higher good-quality factor than in bulk CMOS.

Figure 1. Bow-tie wideband antenna design, 65 nm CMOS SOI.

**Table 1.** Values of the antenna parameters in Figure 1.

| Parameter                                   | L1                                                                                                    | L2    | L3     | L4     | W1    | W2     | W3     | W4    | α            |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|--------|--------|-------|--------|--------|-------|--------------|

| Value                                       | 350 µm                                                                                                | 50 µm | 350 µm | 637 µm | 60 µm | 330 µm | 275 µm | 20 µm | $25^{\circ}$ |

| Area of the rectangle including the antenna | $[L4 + 0.5 \times (W1 + W2)] \times (2 \times L3 + W4) = 832 \ \mu m \times 720 \ \mu m = 0.6 \ mm^2$ |       |        |        |       |        |        |       |              |

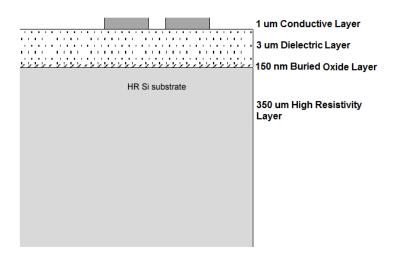

In the proposed on-chip realization, a conductive copper layer with a thickness of about 1  $\mu$ m is printed on a multi-layer substrate that includes:

- a dielectric layer with a thickness of about 3 μm and a relative dielectric permittivity εr of about 3.5;

- (2) a buried oxide layer with a thickness of 150 nm (a value typical for SOI manufacturing technology, see p. 11 of [72]) and a relative dielectric permittivity εr of about 4;

- (3) a high-resistivity (HR) layer with a thickness of 350  $\mu$ m (a value typical for wafers used in RF applications, see [73]) and the following electrical parameters:  $\rho = 5 \text{ k}\Omega \cdot \text{cm}$  and  $\varepsilon r = 11.7$ .

Figure 2 shows a side view of the multi-layer structure in the example case of the CPS implementation. For the sake of space, the figure is not to scale, since the height of the high resistivity layer is two orders of magnitude higher than the height of the conductive and dielectric layers, and three orders of magnitude higher than the height of the buried oxide layer. Moreover, on top of the layers in Figure 2, a passivation layer may be needed due to packaging issues. The effect of a passivation layer and of the packaging on the proposed on-chip antenna is out of the scope of this paper.

The antenna-feeding network is also included in Figure 1. It is represented by the CPS circuit of length L4 and total width W4, whose values are reported in Table 1. The gap between the two strip-lines of the CPS is about 1  $\mu$ m. To design the antenna, and to properly size all parameters reported in Table 1, electromagnetic simulations have been carried out using the CAD (Computer Aided Design) environment CST (Computer Simulation Technology) Microwave Studio. It is to be noted that there is no equation that is able to size the antenna, but the antenna sizing is the result of an iterative process, supported by simulations in the CAD environment. After several simulations and design trials in the CST Microwave Studio tool, the values in Table 1 have been achieved. The area of the rectangle including the antenna is about 0.6 mm<sup>2</sup>, which is much lower than the area of some cm<sup>2</sup> for the antennas proposed by [67,70]. This sizing is not valid for only a specific frequency, but the same antenna has been characterized in a wide frequency range.

**Figure 2.** Side view (in the case of a Co-planar Stripline (CPS) implementation) of the adopted single-chip multi-layer structure.

#### 3. Antenna Characterization

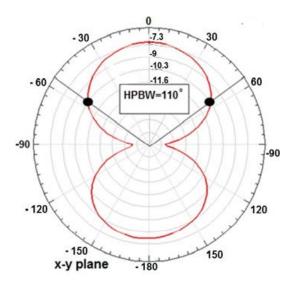

With reference to the antenna whose layout is depicted in Figure 1, Figure 3 shows the performance achieved in terms of radiation pattern along the X–Y plane. The relevant half-power beamwidth (HPBW) angle is also shown: the HPBW along the X–Y plane is 110 degrees. Instead, the HPBW along the X–Z plane is 65 degrees.

It is to be noted that for WiNoC applications, where a processing core has to be connected with other processor cores or memory tiles, placed on the same plane, the radiated power of interest is that along the X–Y plane. The power radiated along the Z-axis would be just wasted. This is why the antenna

is designed to be directional in its X–Y radiation pattern, featuring a large HPBW of 110 degrees in both directions of positive and negative values of the X axis. The only application where radiation along the Z axis would be useful is in the case of a WiNoC communication in a multi-core system-on-chip fabricated using 3D assembly technology. In such a case, the wireless link is also between cores aligned in the vertical direction, and not only between cores placed in the same plane. However, the use of WiNoC technology in the framework of 3D integration technology is out of the scope of this paper.

Figure 3. Antenna radiation pattern at 60 GHz along the X–Y plane.

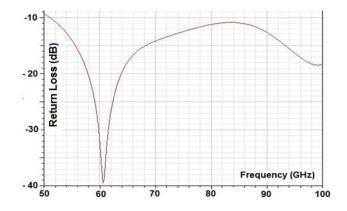

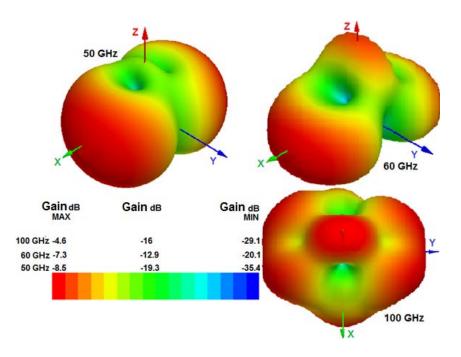

At 60 GHz, the performance in terms of S-parameters has a maximum gain (from CST simulations) of about -7 dBi and a return loss of -39.5 dB. The percentage radiation efficiency  $\eta$  is about 20%. In the state-of-the-art, the antenna bandwidth capability is calculated as the frequency range where the return loss parameter is below -10 dB [74]. Figure 4 shows the S11 antenna performance vs. frequency. From the results in Figure 4, the return loss is always below -10 dB in the range of 51 GHz to 100 GHz, hence an antenna bandwidth capability from 51 GHz to 100 GHz is determined. Frequency values above 100 GHz are not taken into account in this work, since above 100 GHz the CMOS technology is not a suited technology for the integration of the transceivers. Indeed, above 100 GHz, the gain values of the low noise amplifier (LNA) and of the power amplifier (PA) will be too low, and the receiver noise figure (NF) will be too high. Figure 5 shows the 3D radiation pattern and the antenna gain as a function of frequency, at 50 GHz, 60 GHz and 100 GHz, considering a direction of 0 degrees in the X–Y plane in Figure 3.

Figure 4. Return loss of the antenna as a function of frequency.

Figure 5. Radiation pattern and antenna gain at 50 GHz, 60 GHz, 100 GHz.

## 4. Comparison of the Designed Antenna vs. the State-of-the-Art

This section compares the achieved performance vs. known works published in recent literature, e.g., Ref. [31,37,40,67,69,75–94]. Specifically, Table 2 compares the proposed design to [31,37,40,67,79,83] in terms of area, gain, HPBW and bandwidth.

| Antenna       | Area, mm <sup>2</sup> | Feed/Match Circuit | Gain, dB        | HPBWxy        | Bandwidth     |

|---------------|-----------------------|--------------------|-----------------|---------------|---------------|

| This work     | 0.512                 | Included           | -7.3 @ 60 GHz   | $110^{\circ}$ | 51 to 100 GHz |

| [31,37]       | 0.023                 | Not included       | -26.5 @ 60 GHz  | $60^{\circ}$  | 51 to 66 GHz  |

| [40], Dipole  | 375                   | Included           | 5.8 @ 10 GHz    | $65^{\circ}$  | 8 to 11 GHz   |

| [40], Vivaldi | 300                   | Included           | 2.8 @ 10 GHz    | $85^{\circ}$  | 9 to 11 GHz   |

| [67]          | 156                   | Included           | 5 @ 60 GHz      | $184^{\circ}$ | 57 to 64 GHz  |

| [79]          | 2                     | Included           | -30 @ 3 GHz     | N/A           | N/A           |

| [83]          | 1.4                   | Not included       | -38.65 @ 60 GHz | 33°           | 6 GHz         |

| Table 2. Comparison | to the state-of-the-art. |

|---------------------|--------------------------|

|---------------------|--------------------------|

With respect to antennas in the sub-10 GHz domain [40,69], the area occupation of the antenna design in Section 3 is limited to about 0.6 mm<sup>2</sup>. This size is compliant with integration on a single-chip. On the contrary, the size of the antennas proposed in Ref. [40,69] is orders of magnitude higher than the on-chip bow-tie antenna in this work. Indeed, in Ref. [40], the authors present a 3 cm<sup>2</sup> dipole antenna, operating at 10 GHz, with a 2.8 dBi gain and a HPBW of 85 degrees at 10 GHz. Still at 10 GHz, in Ref. [40], the authors also present a 3.75 cm<sup>2</sup> Vivaldi antenna with a gain of 5.8 dBi and a HPBW of 65 degrees.

With respect to other on-chip antennas, operating at around 60 GHz, and proposed in literature, the antenna design in Section 3 offers a better trade-off between size, gain, bandwidth and HPBW. For example, the zig-zag antenna adopted for WiNoC in [31] has been designed with a trace width of 10  $\mu$ m, with an arm length of 60  $\mu$ m and a bend angle of 30 degrees. The axial length of the zig-zag antenna is 0.38 mm. The substrate is represented by a 2  $\mu$ m thick SiO<sub>2</sub> layer, with a relative dielectric permittivity constant  $\varepsilon$ r of 3.9. The substrate is a high-resistivity silicon substrate with a thickness of 633  $\mu$ m and electrical parameters of  $\rho = 5 \text{ k}\Omega \cdot \text{cm}$  and  $\varepsilon$ r = 11.7. The same antenna has also been adopted in [37]. The zig-zag antenna has a lower size, 60  $\mu$ m × 380  $\mu$ m, than the proposed

7 of 13

bow-tie antenna, although the reported area for the zig-zag antenna does not consider the feeding and impedance matching network. The maximum gain of the zig-zag antenna is only -26.8 dBi at 60 GHz: i.e., the gain is about 19 dB lower than the antenna design proposed in this work. The connection distance using the zig-zag antenna is limited to 2 cm in [31]. For example, in a complex MPSoC design with a size L of some centimeters per side, e.g., the INTEL48 core in [95] with L about 2.5 cm, the tiles that are placed in the layout at opposite parts of the MPSoC can have a distance (along the diagonal of the chip) up to 3.5 cm. Moreover, the return loss for the zig-zag antenna is below -10 dB only in the spectrum range from 51 GHz to 66 GHz. Instead, the proposed bow-tie antenna has an upper bound limit of 100 GHz. In terms of HPBW, along the X–Y plane of interest, the zig-zag antenna has a value of about 60 degrees, almost halved vs. the 110 degrees of the proposed design, see Figure 3.

The half-wave dipole and the double-slot antennas proposed in 65 nm SOI technologies in Ref. [59], having a comparable size to the bow-tie design, reach a positive gain of a few dBi, but use a PEC (Perfect Electric Conductor) plane under the chip. Similarly, the slot bow-tie antenna in [62] has an area 2.5 times larger than the proposed design; realized in 180 nm SiGe technology, and using a PEC layer under the substrate, [66] achieves a gain from -3 dBi to 0 dBi operating from 70 GHz to 110 GHz. However, for this antenna, the radiation pattern is directed along the Z-axis, which is unsuitable for WiNoC applications where the communication is towards co-planar nodes. High gain antennas have been proposed at 60 GHz such as the Fan-like antenna in [67]. The antenna in [67] exhibits a beamwidth of 184 degrees, a gain varying from 1.6 dBi to 6.4 dBi from 57 GHz to 64 GHz, but for an area of 156 mm<sup>2</sup>, which is orders of magnitude higher than our proposed design. Some antennas operating at around 60 GHz are reviewed in [93,94], but their area occupation is at least tens of mm<sup>2</sup>. Therefore, they are more suited for wireless sensor networking applications, in off-chip short-range communications, rather than for WiNoC.

As far as the antennas at sub-GHz are concerned, as in Ref. [68,70,71,81], the gain of the antennas is higher than the gain of the proposed bow-tie antenna, but the bandwidth in [68,70,71,81] is so low that the data-rate is limited to a few kb/s. Such antennas are suitable for wireless sensor networks, but not for on-chip high-rate connections among several processors or between a processor and a memory tile.

Carbon Nanotube (CN) antennas have also been proposed in literature in Ref. [75–77] to achieve a Terahertz frequency operating range. The CN antennas, operating in Terahertz frequency range, can provide much higher communication data rates than on-chip antennas, operating up to 100 GHz. The CN antennas can also have extremely high current density, compared with copper, thus allowing for a higher transmission power. Therefore, they can be suitable for long-distance communications. However, CN antennas are still facing significant manufacturing challenges.

The design of Ultra Wide Band (UWB) antennas was also proposed for on-chip wireless communication in Ref. [78–80]. The UWB antenna design approach can provide high bandwidth, low power and short-range communication for WiNoCs. However, the UWB-based antenna in Ref. [78–80], implemented in a 180 nm CMOS technology as a meander-type dipole antenna with a length of about 3 mm, and integrated in a complete on-chip transceiver, allows for a transmission range limited to 1 mm. The area occupation of the antenna in the layout of Ref. [79], including the feeding circuitry, is about 2 mm<sup>2</sup>, i.e., 4 mm × 0.5 mm. The short transmission range, compared with the current die area, would require multi-hop wireless communication across the chip, which makes it less efficient for a communication distance above 1 mm.

Another class of antennas proposed for WiNoC is the PLPA (planar log-periodic on-chip antenna) one, see Ref. [82–84]. The authors of [82–84] propose the design of an on-chip PLPA with a bandwidth of about 10% of the central frequency, e.g., 6 GHz of bandwidth around a central frequency of 60 GHz and featuring end-fire directivity. It is to be noted that the PLPA in [82–84] can also resonate at other frequencies, e.g., 44 GHz. From CAD simulations, the HPBW of the PLPA is 33° along the end-fire direction, whereas the HPBW along the elevation is 30°. At 60 GHz, the antenna gain is –38.65 dBi. The longest dimension of the antenna is 1.1825 mm, which is comparable to the wavelength of the signal in the dielectric medium. The area is about 1.4 mm<sup>2</sup>, but this value does not include the feeding

network, which instead is included in the area values of the other antennas considered in Table 2. It is worth noting that the performance of the PLPA in [82–84] at 60 GHz, in terms of bandwidth, gain and HPBW, is lower than the design proposed in this work.

Several on-chip antennas are proposed by Kenneth et al. in [85–92]. With respect to these designs, the bow-tie antenna proposed in this work stands out for its large bandwidth, which is an added value of the selected bow-tie approach. More in detail, Kenneth et al., in [85], discuss the impact of on-chip metal interference structures, such as a power grid, local clock trees and data lines, on the performance of on-chip antennas. In Ref. [86], Kenneth et al. propose on-chip wireless interconnections for clock signal distribution. In Ref. [87–92], Kenneth et al. present several on-chip antennas operating at 24 GHz, 5.8 GHz and 60 GHz. Particularly, a communication range of 10 m operating at 100 kb/s is possible using on-chip antennas at 24 GHz (a 3-mm long zig-zag dipole antenna fabricated on a  $20-\Omega$ -cm substrate and having an efficiency of 25%). At 5.8 GHz, using a pair of 6-mm long monopoles, Kenneth at al. demonstrated that a communication range of 30 m can be achieved. A bond wire antenna, operating at 60 GHz, has also been proposed with an efficiency of about 15%.

#### 5. Impact of the Proposed Antenna on the NoC Infrastructure Performance

This section evaluates the impact of the proposed antenna on the performance of the whole NoC infrastructure, and hence on the performance of an MPSoC, with respect to the use of a zig-zag antenna, as in [31,37]. It is worth noting that the higher HPBW of our design vs. zig-zag antenna in [31,37] leads to a larger number of cores that can be reached by the WiNoC.

Moreover, the increased antenna gain of about 19 dB (-7.5 dBi in our case vs. -26.5 dBi in [31,37]) can be exploited to reduce the power consumption of the NoC infrastructure, and hence of the MPSoC. Indeed, in the link budget of a wireless connection, the received power in dB depends on the transmitted power plus the gain of the transmitting and receiving antennas (i.e., twice the gain of the antenna in dB if the same antenna is used during transmission and receiving phases), minus the path loss. By increasing the antenna gain by 19 dB, adopting the design proposed in Section 3 instead of a zig-zag antenna topology, then to achieve the same distance with the same path loss of [31,37], the transmitted power can be decreased by about 38 dB. For example, instead of transmitting 1 mW of power (which is drained from the power supply), the WiNoC transceiver can transmit about 200 nW, with a power saving by a factor 5.

Finally, the larger antenna bandwidth, measured in GHz (see Table 2), can be exploited to sustain a higher bit-rate vs. [31,37], measured in Gb/s, when using the same transceiver and the same modulation and coding scheme (i.e., with equal spectrum efficiency, measured as b/s/Hz).

### 6. Conclusions

The design of a mm-wave antenna for wideband wireless communications on-chip, WiNoC, is presented in this work. WiNoC is an emerging trend in on-chip communications to solve power consumption and latency issues of conventional metal-wires in the case of links above 1 cm in size (e.g., distant tiles in a multi-processor system-on-chip). The aim is to interconnect multiple macrocells of homogenous or heterogeneous MPSoCs. The proposed bow-tie antenna design has been characterized in the range from 50 GHz to 100 GHz in terms of area, efficiency, and beamwidth. With respect to the state-of-the-art, the antenna stands out for its better trade-off in terms of size, gain, HPBW and bandwidth. With respect to the zig-zag antenna, typically used as a reference for WiNoC design in literature, the proposed design stands out for its much higher gain, about 19 dB higher and almost doubled beamwidth. The higher gain is useful to connect tiles at opposite sides of large MPSoC designs (in [31], the zig-zag antenna is limited to 2 cm) or—giving the same distance and path loss—to reduce the transmitted power, thus saving power.

Conflicts of Interest: The author declares no conflict of interest.

## References

- Torres, L.; Benoit, P.; Sassatelli, G.; Robert, M.; Clermidy, F.; Puschini, D. An Introduction to Multi-Core System-on-Chip: Trends and Challenges. In *Multiprocessor System-on-Chip*; Springer: New York, NY, USA, 2011; pp. 1–21.

- 2. Bertozzi, D.; Benini, L. Xpipes: A Network-on-Chip architecture for gigascale systems-on-chip. *IEEE Circuits Syst. Mag.* **2004**, *4*, 18–31. [CrossRef]

- Saponara, S.; Coppola, M.; Fanucci, L. How green is your cloud?-A 64-b ARM-based heterogeneous computing platform with NoC interconnect for server-on-chip energy-efficient cloud computing. In Proceedings of the 2nd International Conference on Cloud Computing and Services Science—CLOSER 2012, Porto, Portugal, 18–21 April 2012; pp. 135–140.

- 4. Bacciarelli, L.; Lucia, G.; Saponara, S.; Fanucci, L.; Forliti, M. Design, testing and prototyping of a software programmable I2C/SPI IP on AMBA bus. In Proceedings of the 2006 Ph.D. Research in Microelectronics and Electronics, Otranto, Italy, 12–15 June 2006; pp. 373–376.

- Jalier, C.; Lattard, D.; Jerraya, A.A.; Sassatelli, G.; Benoit, P.; Torres, L. Heterogeneous vs homogeneous MPSoC approaches for a mobile LTE modem. In Proceedings of the 2010 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 8–12 March 2010; pp. 184–189.

- Saponara, S.; Fanucci, L. Homogeneous and heterogeneous MPSoC architectures with Network-on-Chip connectivity for low-power and real-time multimedia signal processing. *VLSI Des.* 2012, 2012, 1–17. [CrossRef]

- Airoldi, R.; Garzia, F.; Anjum, O.; Nurmi, J. Homogeneous MPSoC as baseband signal processing engine for OFDM systems. In Proceedings of the 2010 International Symposium on System on Chip (SoC), Tampere, Finland, 29–30 September 2010.

- 8. Saponara, S.; Fanucci, L.; Coppola, M. Design and coverage-driven verification of a novel network-interface IP macrocell for network-on-chip interconnects. *Microprocess. Microsyst.* **2011**, *35*, 579–592.

- 9. Tota, S.; Casu, M.R.; Ruo Roch, M.; Macchiarulo, L.; Zamboni, M. A case study for NoC based homogeneous MPSoC architectures. *IEEE Trans. VLSI Syst.* **2009**, *17*, 384–388. [CrossRef]

- 10. Saponara, S.; Fanucci, L.; Coppola, M. Many-core platform with NoC interconnect for low cost and energy sustainable cloud server-on-chip. In Proceedings of the 2012 Sustainable Internet and ICT for Sustainability (SustainIT), Pisa, Italy, 4–5 October 2012.

- Yue, H.; Wang, Z.; Dai, K. A Heterogeneous Embedded MPSoC for Multimedia Applications. In *Lecture Notes in Computer Science, Proceedings of the High Performance Computing and Communications, Munich, Germany,* 13–15 September 2006; Springer: Berlin/Heidelberg, Germany, 2006; Volume 4208, pp. 591–600.

- 12. Saponara, S.; Fanucci, L.; Petri, E. A multi-processor NoC-based architecture for real-time image/video enhancement. *J. Real-Time Image Process.* **2013**, *8*, 111–125. [CrossRef]

- 13. Bouthaina, D.; Baklouti, M.; Niar, S.; Abid, M. Shared hardware accelerator architectures for heterogeneous MPSoCs. In Proceedings of the 2013 8th International Workshop on Reconfigurable and Communication-Centric Systems-on-Chip (ReCoSoC), Darmstadt, Germany, 10–12 July 2013.

- Saponara, S.; Martina, M.; Casula, M.; Fanucci, L.; Masera, G. Motion estimation and CABAC VLSI co-processors for real-time high-quality H.264/AVC video coding. *Microprocess. Microsyst.* 2010, 34, 316–328. [CrossRef]

- Miyamori, T. Heterogeneous Multi & Many Core Processors for Multimedia Applications. In Proceedings of the 11th International Forum on Embedded MPSoC and Multicore (MPSoC 2011), Beaune, France, 4–8 July 2011.

- Marsi, S.; Saponara, S. Integrated video motion estimator with Retinex-like pre-processing for robust motion analysis in automotive scenarios: Algorithmic and real-time architecture design. *J. Real-Time Image Process.* 2010, *5*, 275–289. [CrossRef]

- 17. Chimenti, A.; Fanucci, L.; Locatelli, R.; Saponara, S. VLSI architecture for a low-power video codec system. *Microelectron. J.* **2002**, *33*, 417–427. [CrossRef]

- 18. Fanucci, L.; Saponara, S. Data driven power saving for DCT/IDCT VLSI macrocell. *IEICE Trans. Fundam. Electron. Commun. Comput. Sci.* **2002**, *E85A*, 1760–1765.

- Fanucci, L.; Saponara, S.; Bertini, L. A parametric VLSI architecture for video motion estimation. *Integr. VLSI J.* 2001, *31*, 79–100. [CrossRef]

- 20. Fanucci, L.; Saletti, R.; Saponara, S. Parametrized and reusable VLSI macro cells for the low-power realization of 2-D discrete-cosine-transform. *Microelectron. J.* **2001**, *32*, 1035–1045. [CrossRef]

- 21. Saponara, S.; Fanucci, L.; Marsi, S.; Ramponi, G. Algorithmic and architectural design for real-time and power-efficient Retinex image/video processing. *J. Real-Time Image Process.* **2007**, *1*, 267–283. [CrossRef]

- 22. Turturici, M.; Saponara, S.; Fanucci, L.; Franchi, E. Low-power DSP system for real-time correction of fish-eye cameras in automotive driver assistance applications. *J. Real-Time Image Process.* **2014**, *9*, 463–478. [CrossRef]

- 23. Palesi, M.; Daneshtalab, M. Routing Algorithms in Networks-on-Chip; Springer: Berlin, Germany, 2011.

- 24. Saponara, S.; Fanucci, L. Configurable network-on-chip router macrocells. *Microprocess. Microsyst.* **2016**, 45, 141–150. [CrossRef]

- 25. Wettin, P.; Kim, R.; Murray, J.; Yu, X.; Pande, P.P.; Ganguly, A.; Heo, D. Design space exploration for wireless NoCs incorporating irregular network routing. *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.* **2014**, *33*, 1732–1745.

- 26. Saponara, S.; Vitullo, F.; Petri, E.; Fanucci, L.; Coppola, M.; Locatelli, R. Coverage-Driven Verification of HDL IP Cores: Case Study of a Router for Network-on-Chip Communication in Embedded Systems. In *Solutions* on *Embedded Systems*; Lecture Notes in Electrical Engineering; Springer: New York, NY, USA, 2011; Volume 81, pp. 105–119.

- 27. Wettin, P.; Murray, J.; Kim, R.; Yu, X.; Pande, P.P.; Heo, D. Performance Evaluation of Wireless NoCs in Presence of Irregular Network Routing Strategies. In Proceedings of the 2014 Design, Automation and Test in Europe Conference and Exhibition (DATE), Dresden, Germany, 24–28 March 2014.

- 28. Saponara, S.; Bacchillone, T.; Petri, E.; Fanucci, L.; Locatelli, R.; Coppola, M. Design of an NoC interface macrocell with hardware support of advanced networking functionalities. *IEEE Trans. Comput.* **2014**, *63*, 609–621.

- Hoppner, S.; Eisenreich, H.; Henker, S.; Walter, D.; Ellguth, G.; Schuffny, R. A Compact Clock Generator for Heterogeneous GALS MPSoCs in 65-nm CMOS Technology. *IEEE Trans. VLSI Syst.* 2013, 21, 566–570. [CrossRef]

- 30. Saponara, S.; Vitullo, F.; Locatelli, R.; Teninge, P.; Coppola, M.; Fanucci, L. LIME: A low-latency and low-complexity on-chip mesochronous link with integrated flow control. In Proceedings of the 11th EUROMICRO Conference on Digital System Design Architectures, Methods and Tools (DSD '08), Parma, Italy, 3–5 September 2008.

- 31. Deb, S.; Ganguly, A.; Pande, P.P.; Belzer, B.; Heo, D. Wireless NoC as interconnection backbone for multicore chips: Promises and challenges. *IEEE J. Emerg. Sel. Top. Circuits Syst.* **2012**, *2*, 228–239. [CrossRef]

- 32. Vitullo, F.; L'Insalata, N.E.; Petri, E.; Saponara, S.; Fanucci, L.; Casula, M.; Locatelli, R.; Coppola, M. Low-complexity link microarchitecture for mesochronous communication in Networks-on-Chip. *IEEE Trans. Comput.* **2008**, *57*, 1196–1201.

- Vitullo, F.; L'Insalata, N.E.; Petri, E.; Casula, M.; Saponara, S.; Fanucci, L.; Locatelli, R.; Coppola, M. A mesochronous physical link architecture for network-on-chip interconnects. In Proceedings of the 2007 Ph.D. Research in Microelectronics and Electronics Conference (PRIME 2007), Talence, France, 2–5 July 2007; pp. 29–32.

- Cheng, L.; Gratz, P.V.; Palermo, S. Nano-Photonic Networks-on-Chip for Future Chip Multiprocessors. In *More than Moore Technologies for Next Generation Computer Design*; Springer: New York, NY, USA, 2015; pp. 155–186.

- 35. Shacham, A.; Bergman, K.; Carloni, L.P. Photonic Networks-on-Chip for Future Generations of Chip Multiprocessors. *IEEE Trans. Comput.* **2008**, *57*, 1246–1260. [CrossRef]

- 36. Saponara, S.; Bacchillone, T. Network architecture, security issues, and hardware implementation of a home area network for smart grid. *J. Comput. Netw. Commun.* **2012**, 2012, 534512. [CrossRef]

- 37. Mineo, A.; Palesi, M.; Ascia, G.; Catania, V. Runtime tunable transmitting power technique in mm-Wave WiNoC architectures. *IEEE Trans. VLSI Syst.* **2016**, *24*, 1535–1545. [CrossRef]

- Catania, V.; Mineo, A.; Monteleone, S.; Palesi, M.; Patti, D. Energy efficient transceiver in wireless Network on Chip architectures. In Proceedings of the 2016 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 14–8 March 2016.

- Catania, V.; Mineo, A.; Monteleone, S.; Palesi, M.; Patti, D. Improving the energy efficiency of wireless Network on Chip architectures through online selective buffers and receivers shutdown. In Proceedings of the Consumer Communications & Networking Conference (CCNC), Las Vegas, NV, USA, 8–11 January 2016.

- 40. Martin, P.M.; Le Gouguec, T.; Mahdi, N. Wireless interconnects by using printed antennas for inter-chip communications in PCB context. In Proceedings of the 2014 44th European Microwave Conference (EuMC), Rome, Italy, 6–9 October 2014; pp. 486–489.

- 41. Pande, P.P.; Ganguly, A.; Chang, K.; Teuscher, C. Hybrid wireless Network on Chip: A new paradigm in multi-core design. In Proceedings of the 2nd International Workshop on Network on Chip Architectures (NoCArc 2009), New York, NY, USA, 12–16 December 2009.

- 42. Vitullo, F.; Saponara, S.; Petri, E.; Casula, M.; Fanucci, L.; Maruccia, G.; Locatelli, R.; Coppola, M. A reusable coverage-driven verification environment for Network-on-Chip communication in embedded system platforms. In Proceedings of the 7th Workshop on Intelligent Solutions in Embedded Systems(WISES 2009), Ancona, Italy, 25–26 June 2009; pp. 71–77.

- 43. Mineo, A.; Rusli, M.S.; Palesi, M.; Ascia, G.; Catania, V.; Marsono, M.N. A closed loop transmitting power self-calibration scheme for energy efficient winoc architectures. In Proceedings of the 2015 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 9–13 March 2015.

- 44. Mineo, A.; Palesi, M.; Ascia, G.; Catania, V. An adaptive transmitting power technique for energy efficient mm-wave wireless NoCs. In Proceedings of the 2014 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 24–28 March 2014.

- 45. Saponara, S.; Mattii, L.; Neri, B.; Baronti, F.; Fanucci, L. Design of a 2 Gb/s transceiver at 60 GHz with integrated antenna in bulk CMOS technology. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference (EuMIC), Rome, Italy, 6–7 October 2014; pp. 33–36.

- 46. Saponara, S.; Nuzzo, P.; Nani, C.; Van der Plas, G.; Fanucci, L. Architectural exploration and design of Time-interleaved SAR arrays for low-power and high speed A/D converters. *IEICE Trans. Electron.* **2009**, *E92-C*, 843–851. [CrossRef]

- 47. Saponara, S.; Neri, B. System-level analysis for integrated power amplifier design in mmWave consumer wireless communications. In *Lecture Notes in Electrical Engineering*; Springer: New York, NY, USA, 2017; Volume 409, pp. 167–174.

- 48. Guo, S.; Xi, T.; Gui, P.; Zhang, J.; Choi, W.; Kenneth, K.O.; Fan, Y.; Huang, D.; Gu, R.; Morgan, M.; et al. 54 GHz CMOS LNAs with 3.6 dB NF and 28.2 dB gain using transformer feedback Gm-boosting technique. In Proceedings of the IEEE Asian Solid-State Circuits Conference(A-SSCC), Taiwan, China, 10–12 November 2014; pp. 185–188.

- 49. Saponara, S.; Neri, B. mm-wave integrated wireless transceivers: Enabling technology for high bandwidth connections in IoT. In Proceedings of the IEEE World Forum on Internet of Things (WF-IoT 2015), Milan, Italy, 14–16 December 2015; pp. 149–153.

- 50. Xi, T.; Huang, S.; Guo, S.; Gui, P.; Zhang, J.; Choi, W.; Huang, D.; Kenneth, K.O.; Fan, Y. A new compact high-efficiency mmWave power amplifier in 65 nm CMOS process. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS 2015), Phoenix, AZ, USA, 17–22 May 2015.

- Saponara, S.; Neri, B. Fully Integrated 60 GHz Transceiver for Wireless hd/wigig Short-Range Multi-Gbit Connections. In *Lecture Notes in Electrical Engineering*; Springer: New York, NY, USA, 2016; Volume 351, pp. 131–137.

- 52. Zhang, J.; Sharma, N.; Kenneth, K.O. 21.5-to-33.4 GHz voltage-controlled oscillator using NMOS switched inductors in CMOS. *IEEE Microw. Wirel. Compon. Lett.* **2014**, *24*, 478–480. [CrossRef]

- 53. Saponara, S.; Neri, B. Gbps wireless transceivers for high bandwidth interconnections in distributed cyber physical systems. *Proc. SPIE* **2015**, *9517*. [CrossRef]

- 54. Xi, T.; Guo, S.; Gui, P.; Zhang, J.; Kenneth, K.O.; Fan, Y.; Huang, D.; Gu, R.; Morgan, M. Low-phase-noise 54 GHz quadrature VCO and 76 GHz/90 GHz VCOs in 65nm CMOS process. In Proceedings of the 2014 IEEE Radio Frequency Integrated Circuits Symposium, Tampa, FL, USA, 1–3 June 2014; pp. 257–260.

- 55. Saponara, S. Configurable array of low-complex SAR ADCs. *Analog Integr. Circuits Signal Process.* **2016**, *67*, 103–107. [CrossRef]

- 56. Wang, S.; Jin, T. Wireless network-on-chip: A survey. IET J. Eng. 2014. [CrossRef]

- 57. Fonte, A.; Saponara, S.; Pinto, G.; Neri, B. Feasibility study and on-chip antenna for fully integrated μRFID tag at 60 GHz in 65 nm CMOS SOI. In Proceedings of the 2011 IEEE International Conference on RFID-Technologies and Applications (RFID-TA), Barcelona, Spain, 15–16 September 2011; pp. 457–462.

- 58. Yu, X.M.; Rashtian, H.; Mirabbasi, S.; Pande, P.P.; Heo, D. An 18.7-Gb/s 60-GHz OOK Demodulator in 65-nm CMOS for Wireless Network-on-Chip. *IEEE Trans. Circuits Syst.* **2015**, *62*, 799–806. [CrossRef]

- 59. Saponara, S.; Neri, B. mm-wave integrated wireless transceiver: enabling technology for high bandwidth short-range networking in cyber physical systems. *Microsyst. Technol.* **2016**, *22*, 1893–1903. [CrossRef]

- 60. Park, S.; Park, S.; Krishna, T.; Chen, C.H.; Daya, B.; Chandrakasan, A.P.; Peh, L.S. Approaching the Theoretical Limits of a Mesh NoC with a 16-Node Chip Prototype in 45 nm SOI. In Proceedings of the 2012 49th ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 3–7 June 2012.

- Fonte, A.; Saponara, S.; Pinto, G.; Fanucci, L.; Neri, B. 60-GHz Single-Chip Integrated Antenna and Low Noise Amplifier in 65-nm CMOS SOI Technology for Shortrange Wireless Gbits/s Applications. In Proceedings of the 2011 International Conference on Applied Electronics (AE 2011), Pilsen, Czech Republic, 7–8 September 2011.

- 62. Saponara, S.; Giannetti, F.; Neri, B. Design Exploration of mm-Wave Integrated Transceivers for Short-Range Mobile Communications towards 5G. J. Circuits Syst. Comput. **2017**, *26*, 1750069. [CrossRef]

- 63. Pan, S.; Gilreath, L.; Heydari, P.; Capolino, F. An on-chip W-Band bowtie slot antenna in silicon. In Proceedings of the IEEE Antennas and Propagation Society International Symposium (APSURSI), Chicago, IL, USA, 8–14 July 2012; pp. 1–2.

- 64. Saponara, S.; Neri, B. Integrated 60 GHz Antenna, LNA and Fast ADC Architecture for Embedded Systems with Wireless Gbit Connectivity. J. Circuits Syst. Comput. 2012, 21, 1–24. [CrossRef]

- 65. Fonte, A.; Saponara, S.; Pinto, G.; Fanucci, L.; Neri, B. Design of a Low Noise Amplifier with Integrated Antenna for 60 GHz Wireless Communications. In Proceedings of the 2011 IEEE MTT-S International Microwave Workshop Series on Millimeter Wave Integration Technologies (IMWS), Sitges, Spain, 15–16 September 2011; pp. 160–163.

- 66. Mineo, A.; Palesi, M.; Ascia, G.; Catania, V. Exploiting antenna directivity in wireless NoC architectures. *Microprocess. Microsyst.* **2016**, *43*, 59–66. [CrossRef]

- 67. Chen, Z.N.; Qing, X.; Sun, M.; Gong, K.; Hong, W. 60-GHz antennas on PCB. In Proceedings of the IEEE European Conference on Antennas and Propagation (EuCAP), The Hague, The Netherlands, 6–11 April 2014; pp. 533–536.

- Genovesi, S.; Saponara, S.; Monorchio, A. Parametric Design of Compact Dual-Frequency Antennas for Wireless Sensor Networks. *IEEE Trans. Antennas Propag.* 2011, 59, 2619–2627. [CrossRef]

- 69. Gambini, S.; Crossley, J.; Alon, E.; Rabaey, J.M. A Fully integrated 290 pJ/bit UWB dual-mode transceiver for cm-range wireless interconnects. *IEEE J. Solid-Sate Circuits* **2012**, *47*, 586–598. [CrossRef]

- 70. Genovesi, S.; Monorchio, A.; Saponara, S. Compact Triple-Frequency Antenna for Sub-GHz Wireless Communications. *IEEE Antennas Wirel. Propag. Lett.* **2012**, *1*, 14–17. [CrossRef]

- 71. Genovesi, S.; Monorchio, A.; Saponara, S. Double-loop antenna for wireless tyre pressure monitoring. *Electron. Lett.* **2008**, *44*, 1385–1387. [CrossRef]

- 72. Kononchuk, O.; Nguyen, B.-Y. Silicon-On-Insulator (SOI) Technology: Manufacture and Applications; Woodhead Publishing: Sawston, Cambridge, UK, 2014.

- 73. Iannacci, J. Practical Guide to RF MEMS; Wiley: Hoboken, NJ, USA, 2013.

- Prakoso, T.; Ngah, R.; Rahman, T. Representation of antenna in two-port network S-parameter. In Proceedings of the IEEE International RF and Microwave Conference Proceedings, Kuala Lumpur, Malaysia, 2–4 December 2008; pp. 293–297.

- 75. Kempa, K.; Rybczynski, J.; Huang, Z.; Gregorczyk, K.; Vidan, A.; Kimball, B.; Carlson, J.; Benham, G.; Wang, Y.; Herczynski, A.; Ren, Z. Carbon nanotubes as optical antennas. *Adv. Mater.* **2007**, *19*, 421–426.

- 76. Burke, P.J.; Li, S.; Yu, Z. Quantitative theory of nanowire and nanotube antenna performance. *IEEE Trans. Nanotechnol.* **2006**, *5*, 314–334.

- 77. Huang, Y.; Yin, W.Y.; Liu, Q.H. Performance prediction of carbon nanotube bundle dipole antennas. *IEEE Trans. Nanotechnol.* **2008**, *7*, 331–337. [CrossRef]

- 78. Fukuda, M.; Saha, P.K.; Sasaki, N.; Kikkawa, T. A 0.18 μm CMOS impulse radio based UWB transmitter for global wireless interconnections of 3D stacked-chip system. In Proceedings of the International Conference on Solid State Devices and Materials, Tsukuba, Japan, 26–29 September 2006; pp. 72–73.

- 79. Sasaki, N.; Kimoto, K.; Moriyama, W.; Kikkawa, T. A Single-Chip Ultra-Wideband Receiver Using Silicon Integrated Antennas for Inter-Chip Wireless Interconnection. *J. Solid State Circuits* **2009**, *42*, 382–393.

- 80. Zhao, D.; Wang, Y. Sd-mac: Design and synthesis of a hardware efficient collision-free QoS-aware MAC protocol for wireless network-on-chip. *IEEE Trans. Comput.* **2008**, *57*, 1230–1245. [CrossRef]

- Iacopetti, F.; Saponara, S.; Fanucci, L. Improving power efficiency and reliability in RF tire pressure monitoring modules. In Proceedings of the IEEE International Conference on Electronics, Circuits, and Systems, Marrakech, Morocco, 11–14 December 2007; pp. 878–881.

- 82. Shamim, M.S.; Mansoor, N.; Samaiyar, A.; Ganguly, A.; Deb, S.; Ram, S.S. Energy-efficient wireless network-on-chip architecture with log-periodic on-chip antennas. In Proceedings of the IEEE Great Lakes Symposium on VLSI, Houston, TX, USA, 21–23 May 2014; pp. 85–86.

- 83. Samaiyar, A.; Deb, S.; Ram, S.S. Millimeter-wave planar log periodic antenna for on-chip wireless interconnects. In Proceedings of the IEEE 8th European Conference on Antennas and Propagation (EuCAP), The Hauge, The Netherlands, 6–11 April 2014.

- 84. Mondal, H.; Gade, S.; Shamim, M.; Deb, S.; Ganguly, A. Interference-aware wireless network-on-chip architecture using directional antennas. *IEEE Trans. Multi-Scale Comput. Syst.* **2016**. [CrossRef]

- 85. Seok, E.; Kenneth, K. Design rules for improving predictability of on-chip antenna characteristics in the presence of other metal structures. In Proceedings of the IEEE International Interconnect Technology Conference, Burligame, CA, USA, 6–8 June 2005; pp. 120–122.

- 86. Floyd, B.A.; Hung, C.M.; Kenneth, K.O. Intra-chip wireless interconnect for clock distribution implemented with integrated antennas, receivers, and transmitters. *IEEE J. Solid-State Circuits* **2002**, *37*, 543–552. [CrossRef]

- Wu, H.T.; Lerdsitsomboon, W.; Shim, D.; Wu, C.L.; Yun, Y.H.; Lin, J.J.; Yu, S.; Cao, C.; Ding, Y.; Seok, E.Y.; Kenneth, K.O. Antennas in silicon integrated circuits. In Proceedings of the IEEE International Symposium on Radio-Frequency Integration Technology (RFIT 2009), Singapore, 9–11 December 2009; pp. 170–173.

- Kenneth, K.O.; Kim, K.; Floyd, B.; Mehta, J.; Yoon, H.; Hung, C.-M.; Bravo, D.; Dickson, D.; Guo, X.; Li, R.; et al. Silicon integrated circuits incorporating antennas. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 10–13 September 2006; pp. 473–480.

- 89. Lin, J.J.; Wu, H.T.; Su, Y.; Gao, L.; Sugavanam, A.; Brewer, J.E.; Kenneth, K.O. Communication using antennas fabricated in silicon integrated circuits. *IEEE J. Solid-State Circuits* **2007**, *42*, 1678–1686.

- 90. Wu, H.T.; Lin, J.J.; Kenneth, K.O. Inter-chip wireless communication. In Proceedings of the 7th European Conference on Antennas and Propagation (EuCAP), Goteborg, Sweden, 8–12 April 2013; pp. 3647–3649.

- 91. Wu, H.T.; Tekle, M.; Nallani, C.S.; Zhang, N.; Kenneth, K.O. Bond wire antenna/feed for operation near 60 GHz. *IEEE Trans. Microw. Theory Tech.* **2009**, *57*, 2966–2972.

- 92. Cao, C.; Ding, Y.; Yang, X.; Lin, J.J.; Wu, H.T.; Verma, A.K.; Lin, J.; Martin, F.; Kenneth, K.O. A 24-GHz transmitter with on-chip dipole antenna in 0.13-μm CMOS. *IEEE J. Solid-State Circuits* 2008, 43, 1394–1402. [CrossRef]

- Saponara, S.; Giannetti, F.; Neri, B. Design exploration for millimeter-wave short-range industrial wireless communications. In Proceedings of the 42nd Annual Conference of the IEEE Industrial Electronics Society (IECON), Florence, Italy, 24–27 October 2016; pp. 6038–6043.

- 94. Saponara, S.; Giannetti, F.; Neri, B.; Anastasi, G. Exploiting mm-wave communications to boost the performance of industrial wireless networks. *IEEE Trans. Ind. Inform.* **2017**, 1–11. [CrossRef]

- 95. Totoni, E.; Behzad, B.; Ghike, S.; Torrellas, J. Comparing the power and performance of Intel's SCC to state-of-the-art CPUs and GPUs. In Proceedings of the IEEE ISPASS (International Symposium on Performance Analysis of Systems and Software), New Brunswick, NJ, Canada, 1–3 April 2012; pp. 78–87.

© 2017 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).