Mastering the Art of High Mobility Material Integration on Si: A Path towards Power-Efficient CMOS and Functional Scaling

Abstract

:1. Introduction

2. High Mobility Materials

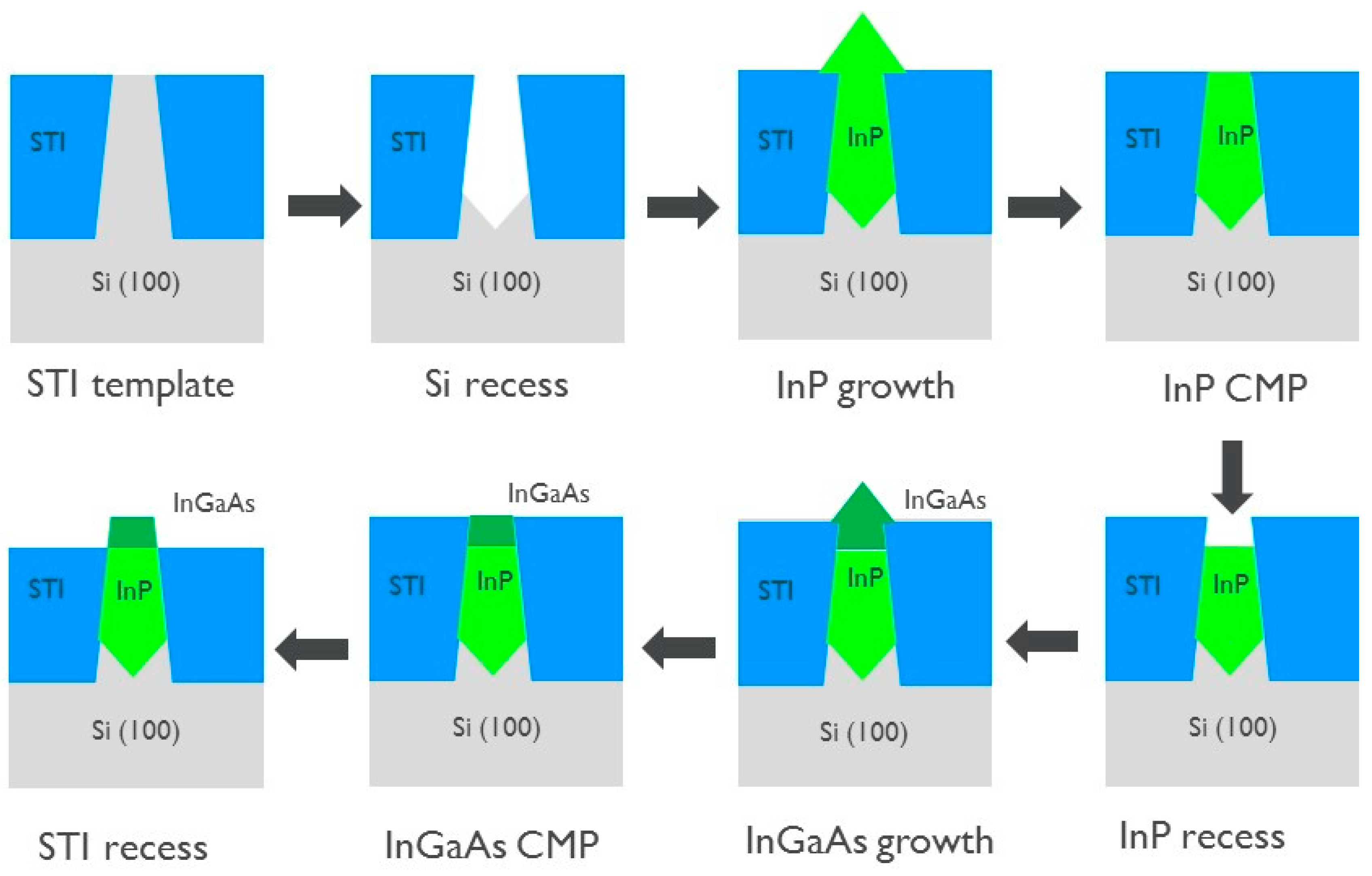

3. Ge and III-V Integration on Si Substrates

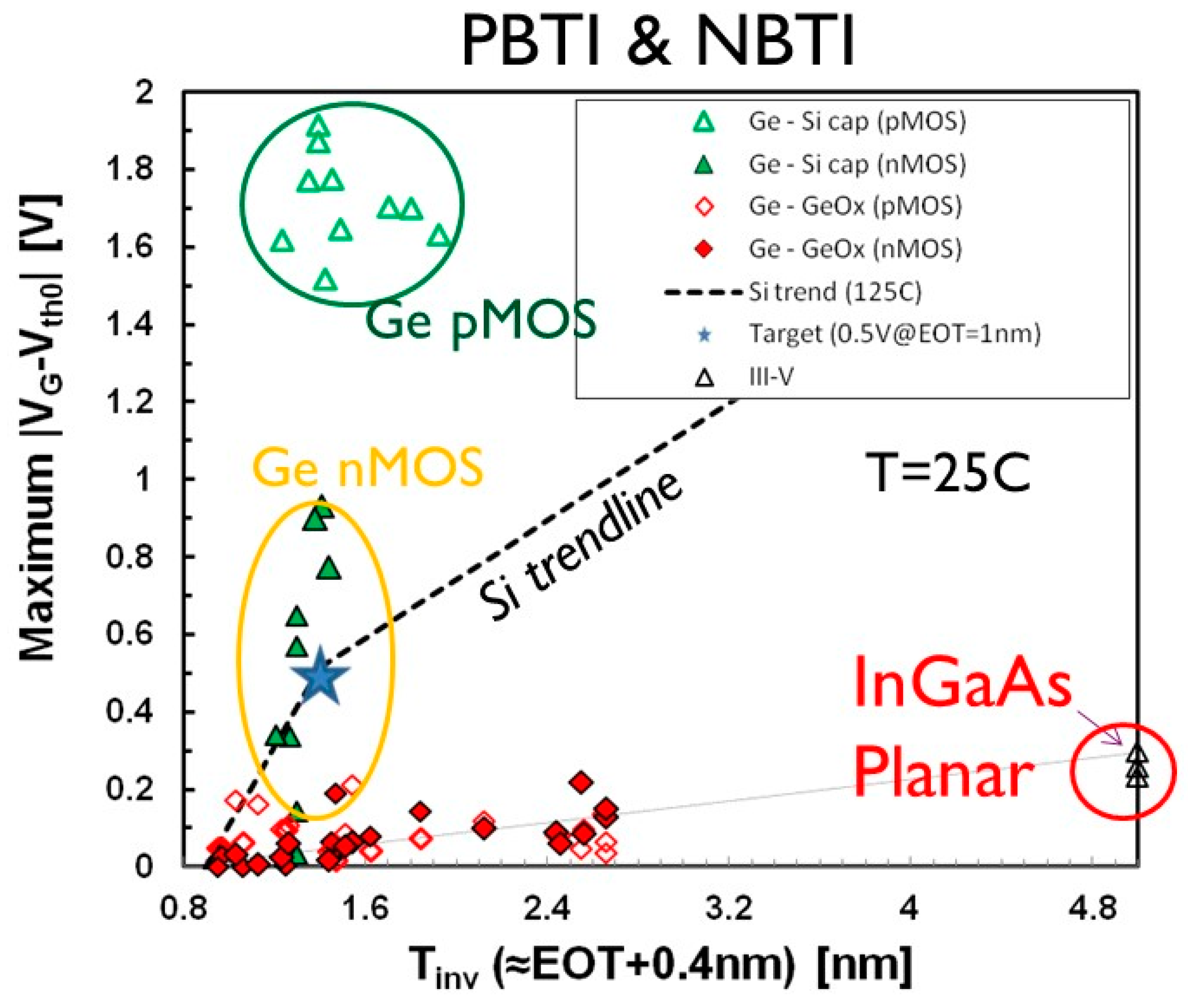

4. Innovations in Gate Stack

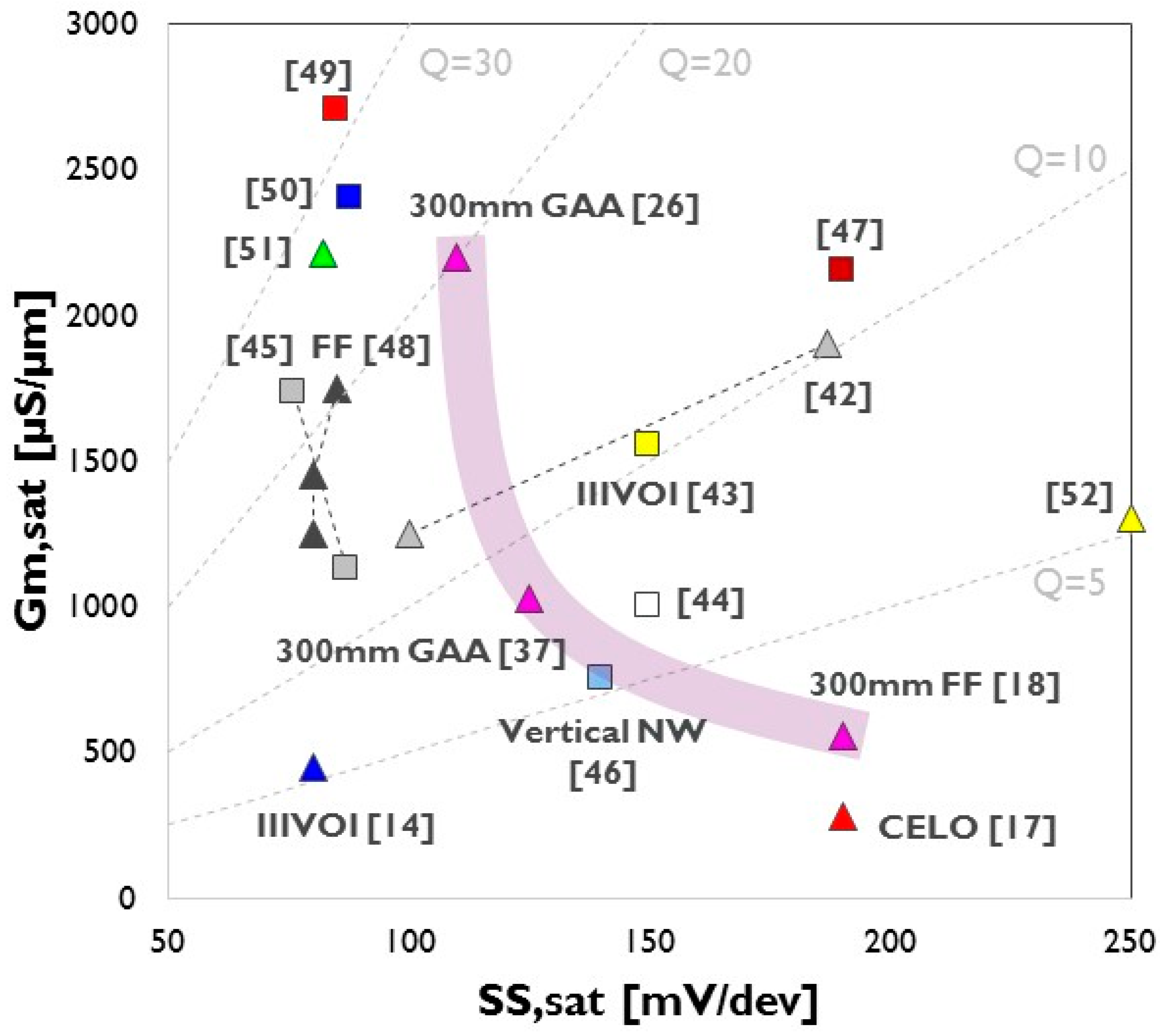

5. Performance of Scaled High Mobility Devices

6. Towards Functional Scaling

7. Conclusions

Acknowledgments

Conflicts of Interest

References

- Eryilmaz, S.B.; Kuzum, D.; Yu, S.; Wong, H.S.P. Device and System Level Design Considerations for Analog-Non-Volatile-Memory Based Neuromorphic Architectures. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 64–67.

- Simmons, M.Y. Quantum computing in Silicon. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 6–9.

- Steegen, A. Technology innovation in an IoT Era. In Proceedings of the 2015 Symposium on VLSI Circuits, Kyoto, Japan, 17–19 June 2015; pp. C170–C171.

- Golikova, O.A.; Moizhez, B.Y.; Stilbans, L.S. Hole mobility of germanium as a function of concentration and temperature. Sov. Phys. Solid State 1962, 3, 2259–2265. [Google Scholar]

- Rode, D.L. Semiconductors and Semimetals; Willardson, R.K., Beer, A.C., Eds.; Academic Press: Cambridge, MA, USA, 1975; Volome 10, p. 1. [Google Scholar]

- Magnone, P.; Crupi, F.; Alioto, M.; Kaczer, B.; de Jaeger, B. Understanding the Potential and the Limits of Germanium pMOSFETs for VLSI Circuits from Experimental Measurements. IEEE Trans. VLSI Syst. 2011, 19, 1569–1582. [Google Scholar] [CrossRef]

- Ghosh, S.; Leonhardt, D.; Han, S.M. Effect of threading dislocation density and dielectric layer on temperature-dependent electrical characteristics of high-hole-mobility metal semiconductor field effect transistors fabricated from wafer-scale epitaxially grown p-type germanium on silicon substrates. J. Appl. Phys. 2014, 115, 094507. [Google Scholar]

- Koslowski, G.; Fursenko, O.; Zaumseil, P.; Schroeder, T.; Vorderwestner, M.; Storck, P. The epitaxial growth of low defect SiGe buffer layers for integration of new materials on 300 mm silicon wafers. ECS Trans. 2012, 50, 613–621. [Google Scholar] [CrossRef]

- Huang, M.L.; Chang, S.W.; Chen, M.K.; Fan, C.H.; Lin, H.T.; Lin, C.H.; Chu, R.L.; Lee, K.Y.; Khaderbad, M.A.; Chen, Z.C.; et al. In0.53Ga0.47As MOSFETs with high channel mobility and gate stack quality fabricated on 300 mm Si substrate. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; p. T205.

- Goh, K.H.; Tan, K.H.; Yadav, S.; Yoon, S.F.; Liang, G.; Gong, X.; Yeo, Y.C. Gate-All-Around CMOS (InAs n-FET and GaSb p-FET) based on Vertically-Stacked Nanowires on a Si Platform, Enabled by Extremely-Thin Buffer Layer Technology and Common Gate Stack and Contact Modules. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 394–397.

- Mitard, J.; Witters, L.; Loo, R.; Lee, S.H.; Sun, J.W.; Franco, J.; Ragnarsson, L.Å.; Brand, A.; Lu, X.; Yoshida, N.; et al. 15 nm-WFIN high-performance low-defectivity strained-germanium pFinFETs with low temperature STI-last process. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2.

- Bury, E.; Kaczer, B.; Mitard, J.; Collaert, N.; Khatami, N.S.; Aksamija, Z.; Vasileska, D.; Raleva, K.; Witters, L.; Hellings, G.; et al. Characterization of Self-Heating in High-Mobility Ge FinFET pMOS devices. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; p. T60.

- Nakaharai, S.; Tezuka, T.; Sugiyama, N.; Moriyama, Y.; Takagi, S. Characterization of 7-nm-thick strained Ge-on-insulator layer fabricated by Ge-condensation technique. Appl. Phys. Lett. 2003, 83, 3516–3518. [Google Scholar] [CrossRef]

- Djara, V.; Deshpande, V.; Uccelli, E.; Daix, N.; Caimi, D.; Rossel, C.; Sousa, M.; Siegwart, H.; Marchiori, C.; Hartmann, J.M.; et al. An InGaAs on Si Platform for CMOS with 200 mm InGaAs-OI Substrate, Gate-first, Replacement Gate Planar and FinFETs Down to 120 nm Contact Pitch. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T176–T177.

- Hashemi, P.; Balakrishnan, K.; Engelmann, S.U.; Ott, J.A.; Khakifirooz, A.; Baraskar, A.; Hopstaken, M.; Newbury, J.S.; Chan, K.K.; Leobandung, E.; Mo, R.T.; et al. First demonstration of high-Ge-content strained-Si1-xGex (x = 0.5) on insulator PMOS FinFETs with high hole mobility and aggressively scaled fin dimensions and gate lengths for high-performance applications. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 16.1.1–16.1.4.

- Yokoyama, M.; Kim, S.H.; Zhang, R.; Taoka, N.; Urabe, Y.; Maeda, T.; Takagi, H.; Yasuda, T.; Yamada, H.; Ichikawa, O.; et al. CMOS integration of InGaAs nMOSFETs and Ge pMOSFETs with self-align Ni-based metal S/D using direct wafer bonding. In Proceedings of the 2011 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 14–16 June 2011; pp. 60–61.

- Czornomaz, L.; Uccelli, E.; Sousa, M.; Deshpande, V.; Djara, V.; Caimi, D.; Rossell, M.D.; Erni, R.; Fompeyrine, J. Confined Epitaxial Lateral Overgrowth (CELO): A Novel Concept for Scalable Integration of CMOS-compatible InGaAs-on-insulator MOSFETs on Large-Area Si Substrates. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T172–T173.

- Waldron, N.; Merckling, C.; Guo, W.; Ong, P.; Teugels, L.; Ansar, S.; Tsvetanova, D.; Sebaai, F.; van Dorp, D.H.; Milenin, A.; et al. An InGaAs/InP Quantum Well FinFet Using the Replacement Fin Process Integrated in an RMG Flow on 300 mm Si Substrates. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2.

- Merckling, C.; Waldron, N.; Jiang, S.; Guo, W.; Ryan, P.; Collaert, N.; Caymax, M.; Barla, K.; Heyns, M.; Thean, A.; et al. Selective-Area Metal Organic Vapor-Phase Epitaxy of InGaAs/InP Heterostrucures on Si For Advanced CMOS Devices. ECS Trans. 2014, 61, 107–112. [Google Scholar] [CrossRef]

- Witters, L.; Mitard, J.; Loo, R.; Demuynck, S.; Chew, S.A.; Schram, T.; Tao, Z.; Hikavyy, A.; Sun, J.W.; Milenin, A.P.; et al. Strained germanium quantum well p-finFETs fabricated on 45 nm fin pitch using replacement channel, replacement metal gate and germanide-free local interconnect. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T56–T57.

- Kita, K.; Suzuki, S.; Nomura, H.; Takahashi, T.; Nishimura, T.; Toriumi, A. Direct Evidence of GeO Volatilization from GeO2/Ge and Impact of Its Suppression on GeO2/Ge Metal-Insulator-Semiconductor Characteristics. Jpn. J. Appl. Phys. 2008, 47, 2349. [Google Scholar] [CrossRef]

- Leys, F.E.; Bonzom, R.; Kaczer, B.; Janssens, T.; Vandervorst, W.; De Jaeger, B.; Van Steenbergen, J.; Martens, K.; Hellin, D.; Rip, J.; et al. Thin epitaxial Si films as a passivation method for Ge(001): Influence of deposition temperature on Ge surface segregation and the high-k/Ge interface quality. Mater. Sci. Semicond. Process. 2006, 9, 679–684. [Google Scholar] [CrossRef]

- Groeseneken, G.; Franco, J.; Cho, M.; Kaczer, B.; Toledano-Luque, M.; Roussel, Ph.; Kauerauf, T.; Alian, A.; Mitard, J.; Arimura, H.; et al. BTI reliability of advanced gate stacks for Beyond-Silicon devices: Challenges and opportunities. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 34.4.1–34.4.4.

- Zhang, R.; Taoka, N.; Huang, P.C.; Takenaka, M.; Takagi, S. 1-nm-thick EOT High Mobility Ge n- and p-MOSFETs with Ultrathin GeOx/Ge MOS Interfaces Fabricated by Plasma Post Oxidation. In Proceedings of the 2011 IEEE International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 642–645.

- Sun, Y.; Kiewra, E.W.; de Souza, J.P.; Bucchignano, J.J.; Fogel, K.E.; Sadana, D.K.; Shahidi, G.G. High-Performance In0.7Ga0.3As-Channel MOSFETs with High-κ Gate Dielectrics and α-Si Passivation. IEEE Electron. Device Lett. 2009, 30, 5–7. [Google Scholar] [CrossRef]

- Waldron, N.; Sioncke, S.; Franco, J.; Nyns, L.; Vais, A.; Zhou, X.; Lin, H.C.; Boccardi, G.; Maes, J.W.; Xie, Q.; et al. Gate-All-Around InGaAs Nanowire FETs with Peak Transconductance of 2200µA/µm at 50 nm Lg using a Replacement Fin RMG Flow. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 799–802.

- Brammertz, G.; Lin, H.C.; Martens, K.; Alian, A.; Merckling, C.; Penaud, J.; Kohen, D.; Wang, W.E.; Sioncke, S.; Delabie, A.; et al. Electronic properties of III-V/oxide interfaces. ECS Trans. 2009, 19, 375–386. [Google Scholar]

- Scarrozza, M.; Pourtois, G.; Houssa, M.; Caymax, M.; Stesmans, A.; Meuris, M.; Heyns, M.M. A first-principles study of the structural and electronic properties of III-V/thermal oxide interfaces. Microelectron. Eng. 2009, 86, 1747–1750. [Google Scholar] [CrossRef]

- Ye, P.D.; Wilk, G.D.; Kwo, J.; Yang, B.; Gossmann, H.J.L.; Frei, M.; Chu, S.N.G.; Mannaerts, J.P.; Sergent, M.; Hong, M.; Ng, K.K.; Bude, J. GaAs MOSFET with oxide gate dielectric grown by atomic layer deposition. IEEE Electron. Device Lett. 2003, 24, 209–211. [Google Scholar] [CrossRef]

- Franco, J.; Kaczer, B.; Waldron, N.; Roussel, Ph.J.; Alian, A.; Pourghaderi, M.A.; Ji, Z.; Grasser, T.; Kauerauf, T.; Sioncke, S.; Collaert, N.; Thean, A.; Groeseneken, G. RTN and PBTI-induced Time-Dependent Variability of Replacement Metal-Gate High-k InGaAs FinFETs. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 506–509.

- Eneman, G.; De Jaeger, B.; Simoen, E.; Brunco, D.P.; Hellings, G.; Mitard, J.; De Meyer, K.; Meuris, M.; Heyns, M. Quantification of Drain Extension Leakage in a Scaled Bulk Germanium PMOS Technology. IEEE Trans. Electron. Devices 2009, 56, 3115–3121. [Google Scholar] [CrossRef]

- Lin, J.; Zhao, X.; Antoniadis, D.A.; del Alamo, J.A. A New Self-aligned Quantum-Well MOSFET Architecture Fabricated by a Scalable Tight-Pitch Process. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 421–424.

- Crupi, F.; Alioto, M.; Franco, J.; Magnone, P.; Kaczer, B.; Groeseneken, G.; Mitard, J.; Witters, L.; Hoffmann, T.Y. Buried Silicon-Germanium pMOSFETs: Experimental Analysis in VLSI Circuits under Aggressive Voltage Scaling. IEEE Trans. VLSI Syst. 2012, 20, 1487–1495. [Google Scholar] [CrossRef]

- Krishnamohan, T.; Kim, D.; Nguyen, C.D.; Jungemann, C.; Nishi, Y.; Saraswat, K.C. High-mobility low band-to-band-tunneling strained-Germanium double-gate heterostructure FETs: Simulations. IEEE Trans. Electron. Devices 2006, 53, 1000–1009. [Google Scholar] [CrossRef]

- Zerveas, G.; Caruso, E.; Baccarani, G.; Czornomaz, L.; Daix, N.; Esseni, D.; Gnani, E.; Gnudi, A.; Grassi, R.; Luisier, M.; et al. Comprehensive comparison and experimental validation of band-structure calculation methods in III-V semiconductor quantum wells. Solid-State Electron. 2016, 115 Pt B, 92–102. [Google Scholar] [CrossRef] [Green Version]

- Alian, A.; Pourghaderi, M.A.; Mols, Y.; Cantoro, M.; Ivanov, T.; Collaert, N.; Thean, A. Impact of the channel thickness on the performance of ultrathin InGaAs channel MOSFET devices. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 16.6.1–16.6.4.

- Waldron, N.; Merckling, C.; Teugels, L.; Ong, P.; Ibrahim, S.A.U.; Sebaai, F.; Pourghaderi, A.; Barla, K.; Collaert, N.; Thean, A.V.Y. InGaAs Gate-All-Around Nanowire Devices on 300 mm Si Substrates. IEEE Electron. Device Lett. 2014, 35, 1097–1099. [Google Scholar] [CrossRef]

- Duriez, B.; Vellianitis, G.; van Dal, M.J.H.; Doornbos, G.; Oxland, R.; Bhuwalka, K.K.; Holland, M.; Chang, Y.S.; Hsieh, C.H.; Yin, K.M.; et al. Scaled p-channel Ge FinFET with optimized gate stack and record performance integrated on 300 mm Si wafers. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 522–525.

- Mitard, J.; Witters, L.; Eneman, G.; Hellings, G.; Pantisano, L.; Hikavyy, A.; Loo, R.; Eyben, P.; Horiguchi, N.; Thean, A. 85 nm-Wide 1.5mA/μm-ION IFQW SiGe-pFET: Raised vs. Embedded Si0.75Ge0.25 S/D Benchmarking and in-Depth Hole Transport Study. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 163–164.

- Pillarisetty, R.; Chu-Kung, B.; Corcoran, S.; Dewey, G.; Kavalieros, J.; Kennel, H.; Kotlyar, R.; Le, V.; Lionberger, D.; Metz, M.; et al. High Mobility Strained Germanium Quantum Well Field Effect Transistor as the P-Channel Device Option for Low Power (Vcc = 0.5 V) III–V CMOS Architecture. In Proceedings of the 2010 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 6.7.1–6.7.4.

- Witters, L.; Mitard, J.; Loo, R.; Eneman, G.; Mertens, H.; Brunco, D.P.; Lee, S.H.; Waldron, N.; Hikavyy, A.; Favia, P.; et al. Strained Germanium Quantum Well pMOS FinFETs Fabricated on in situ Phosphorus-Doped SiGe Strain Relaxed Buffer Layers Using a Replacement Fin Process. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 534–537.

- Egard, M.; Ohlsson, L.; Borg, B.M.; Lenrick, F.; Wallenberg, R.; Wernersson, L.E.; Lind, E. High Transconductance Self-Aligned Gate-Last Surface Channel In0.53Ga0.47As MOSFET. In Proceedings of the 2011 IEEE International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 303–306.

- Ko, H.; Takei, K.; Kapadia, R.; Chuang, S.; Fang, H.; Leu, P.W.; Ganapathi, K.; Plis, E.; Kim, H.S.; Chen, S.Y.; et al. Ultrathin compound semiconductor on insulator layers for high-performance nanoscale transistors. Nature 2010, 468, 286–289. [Google Scholar] [CrossRef] [PubMed]

- Hill, R.; Park, C.; Barnett, J.; Price, J.; Huang, J.; Goel, N.; Loh, W.Y.; Oh, J.; Smith, C.E.; Kirsch, P.; Majhi, P.; Jammy, R. Self-aligned III-V MOSFETs heterointegrated on a 200 mm Si substrate using an industry standard process flow. In Proceedings of the 2010 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 6.2.1–6.2.4.

- Thathachar, A.V.; Agrawal, N.; Bhuwalka, K.K.; Cantoro, M.; Heo, Y.C.; Lavallee, G.; Maeda, S.; Datta, S. Indium Arsenide (InAs) Single and Dual Quantum-Well Heterostructure FinFETs. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T208–T209.

- Thelander, C.; Froberg, L.E.; Rehnstedt, C.; Samuelson, L.; Wernersson, L.E. Vertical enhancement-mode InAs nanowire field-effect transistor with 50-nm wrap gate. IEEE Electron Device Lett. 2008, 29, 206–208. [Google Scholar] [CrossRef]

- Lee, S.; Huang, C.Y.; Carter, A.D.; Elias, D.C.; Law, J.J.M.; Chobpattana, V.; Krämer, S.; Thibeault, B.J.; Mitchell, W.; Stemmer, S.; et al. Record Extrinsic Transconductance (2.45 mS/μm at VDS = 0.5 V) InAs/In0.53Ga0.47As Channel MOSFETs Using MOCVD Source-Drain Regrowth. In Proceedings of the 2015 Symposium on VLSI Technology (VLSIT), Kyoto, Japan, 11–13 June 2013; p. T247.

- Radosavljevic, M.; Chu-Kung, B.; Corcoran, S.; Dewey, G.; Hudait, M.K.; Fastenau, J.M.; Kavalieros, J.; Liu, W.K.; Lubyshev, D.; Metz, M.; et al. Advanced High-K Gate Dielectric for High-Performance Short-Channel In0.7Ga0.3As Quantum Well Field Effect Transistors on Silicon Substrate for Low Power Logic Applications. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 319–322.

- Chang, S.W.; Li, X.; Oxland, R.; Wang, S.W.; Wang, C.H.; Contreras-Guerrero, R.; Bhuwalka, K.K.; Doornbos, G.; Vasen, T.; Holland, M.C.; et al. InAs N-MOSFETs with record performance of Ion = 600 μA/μm at Ioff = 100 nA/mm (Vd = 0.5 V). In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 417–420.

- Lee, S.; Chobpattana, V.; Huang, C.-Y.; Thibeault, B.J.; Mitchell, W.; Stemmer, S.; Gossard, A.C.; Rodwell, M.J.W. Record Ion (0.50 mA/μm at VDD = 0.5 V and Ioff = 100 nA/μm) 25 nm-Gate-Length ZrO2/InAs/InAlAs MOSFETs. VLSI Technol. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 64–65.

- Zhou, X.; Alian, A.; Mols, Y.; Rooyackers, R.; Eneman, G.; Lin, D.; Ivanov, T.; Pourghaderi, A.; Collaert, N.; Thean, A. In0.53Ga0.47As quantum-well MOSFET with source/drain regrowth for low power logic applications. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2.

- Wu, Y.Q.; Wang, R.S.; Shen, T.; Gu, J.J.; Ye, P.D. First Experimental Demonstration of 100 nm Inversion-mode InGaAs FinFET through Damage-free Sidewall Etching. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 331–334.

- Takenaka, M.; Kim, Y.; Han, J.; Kang, J.; Ikku, Y.; Cheng, Y.; Park, J.K.; Kim, S.H.; Takagi, S. CMOS photonics technologies based on heterogeneous integration of SiGe/Ge and III-V on Si. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 815–818.

- Wang, Z.; Tian, B.; Pantouvaki, M.; Guo, W.; Absil, P.; Van Campenhout, J.; Merckling, C.; Van Thourhout, D. Room-temperature InP distributed feedback laser array directly grown on silicon. Nat. Photonics 2015, 9, 837–842. [Google Scholar] [CrossRef]

- Kim, D.H.; del Alamo, J.A.; Chen, P.; Ha, W.; Urteaga, M.; Brar, B. 50-nm E-mode In0.7Ga0.3As PHEMTs on 100-mm InP substrate with fmax > 1 THz. In Proceedings of the 2010 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 692–695.

- Ida, M.; Kurishima, K.; Watanabe, N. Over 300 GHz f/sub T/ and f/sub max/ InP/InGaAs double heterojunction bipolar transistors with a thin pseudomorphic base. IEEE Electron. Device Lett. 2002, 23, 694–696. [Google Scholar] [CrossRef]

- Hoke, W.E.; Chelakara, R.V.; Bettencourt, J.P.; Kazior, T.E.; LaRoche, J.R.; Kennedy, T.D.; Mosca, J.J.; Torabi, A.; Kerr, A.J.; Lee, H.S.; et al. Monolithic integration of silicon CMOS and GaN transistors in a current mirror circuit. J. Vac. Sci. Technol. B 2012, 30, 02B101. [Google Scholar] [CrossRef]

- Ge, T.; Guo, L.; He, H.; Yang, K.; Jia, Y.; Chang, J. Envelope Tracking RF Power Amplifiers: Fundamentals, Design Challenges, and Unique Opportunities Offered by LEES-SMART InGaAs-on-CMOS Process. Procedia Eng. 2016, 141, 94–97. [Google Scholar] [CrossRef]

- Desphande, V.; Djara, V.; O’Connor, E.; Caimi, D.; Sousa, M.; Czornomaz, L.; Fompeyrine, J.; Hashemi, P.; Balakrishnan, K. First RF Characterization of InGaAs Replacement Metal Gate (RMG) nFETs on SiGe-OI FinFETs Fabricated by 3D Monolithic Integration. In Proceedings of the EUROSOI/ULIS Conference, Vienna, Austria, 25–27 January 2016; pp. 127–130.

© 2016 by the author; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Collaert, N. Mastering the Art of High Mobility Material Integration on Si: A Path towards Power-Efficient CMOS and Functional Scaling. J. Low Power Electron. Appl. 2016, 6, 9. https://doi.org/10.3390/jlpea6020009

Collaert N. Mastering the Art of High Mobility Material Integration on Si: A Path towards Power-Efficient CMOS and Functional Scaling. Journal of Low Power Electronics and Applications. 2016; 6(2):9. https://doi.org/10.3390/jlpea6020009

Chicago/Turabian StyleCollaert, Nadine. 2016. "Mastering the Art of High Mobility Material Integration on Si: A Path towards Power-Efficient CMOS and Functional Scaling" Journal of Low Power Electronics and Applications 6, no. 2: 9. https://doi.org/10.3390/jlpea6020009