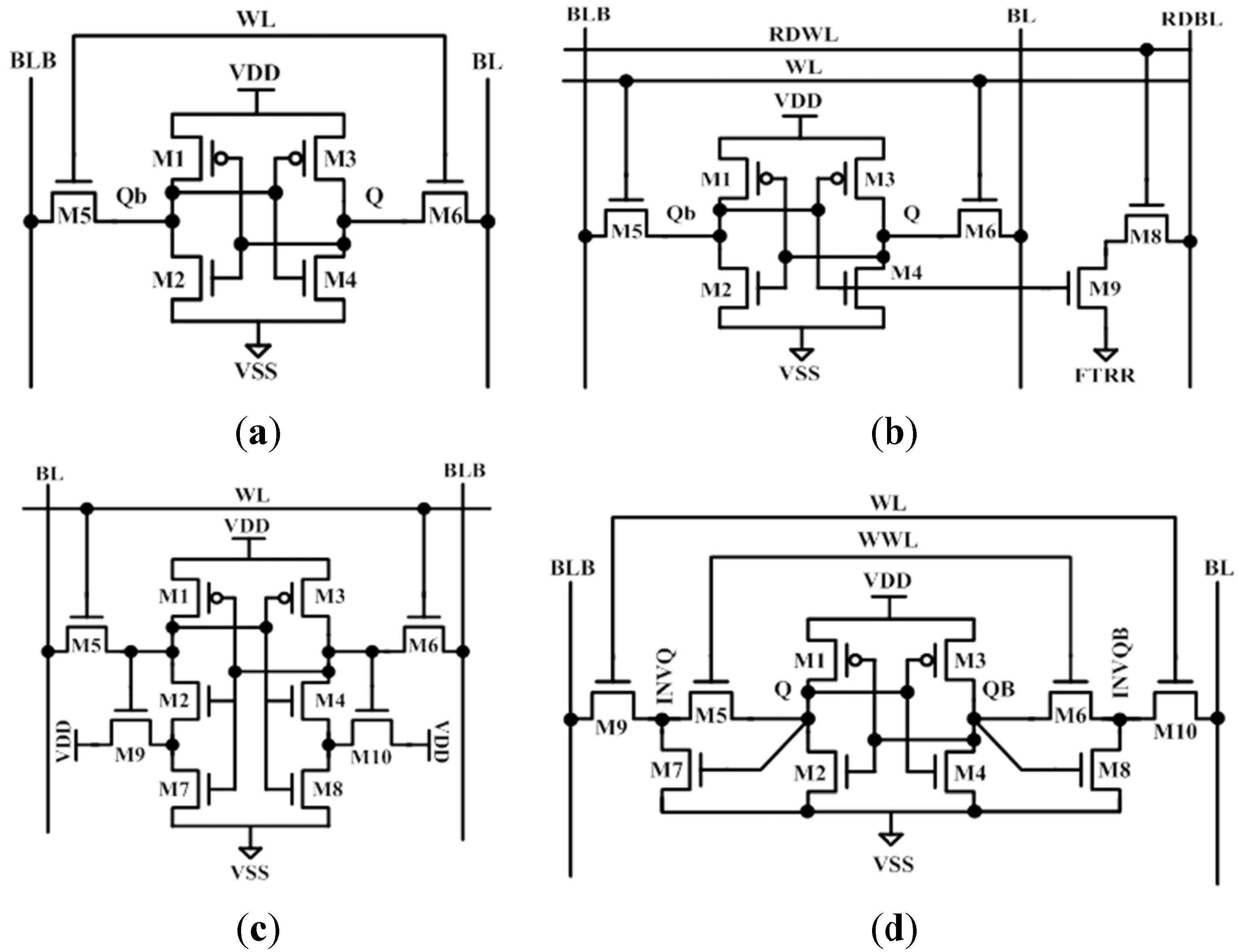

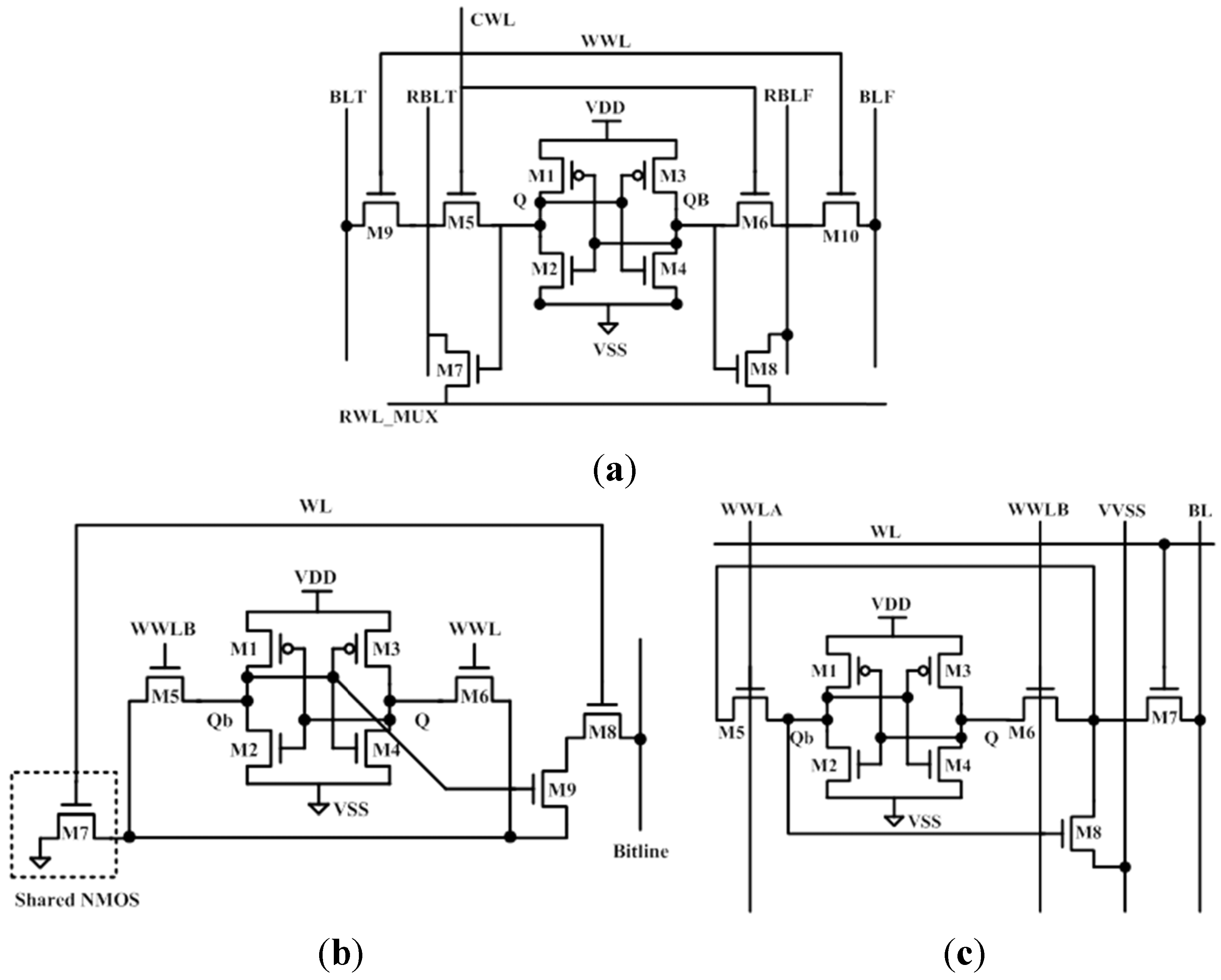

In this section, initially we discuss and compare the results of the energy and delay numbers of the bitcells, and later we move on to the comparisons from energy per operation perspective. In order to do a fair comparison, we size the 6T structures (back-to-back inverters: M1, M2, M3, M4 (

Figure 1 and

Figure 2) and two NMOS pass transistors: M5 and M6 (

Figure 1 and

Figure 2) which are the same in all the aforementioned bitcells (W

M1, M3 = 0.4u, L

M1, M3, M5, M6, M7 = 0.22u, W

M2, M4 = 0.28u, L

M2, M4, M8, M9 = 0.15u, W

M5, M6, M7 = 0.45u). Due to this reason, for all the bitcells under local and global variations we make the µ data retention voltage (DRV) nearly 74 mV, and the µ hold static noise margin (HSNM) roughly equal to 154 mV at the TT_0.4V_27C corner. As the bitcells have different read and write paths, it is hard to size them same with respect to multiple design metrics. However, we tried to make the bitcells’ read and write paths similar. Apart from the M1–M6 being sized the same for all the bitcells, we size the W

M8, M9 = 0.36u and L

M8, M9 = 0.15u for conventional 8T, this work, and Chiu’s bitcell, W

M7, M8 = 0.36u and L

M7, M8 = 0.15u for Chang’s, Feki’s and Yang’s bitcell, W

M9, M10 = 0.45u and L

M9, M10 = 0.22u for Chang’s and Feki’s bitcell, W

M7 = 0.45u and L

M7 = 0.22u for Chiu’s bitcell and W

M7, M8, M9, M10 = 0.16u and L

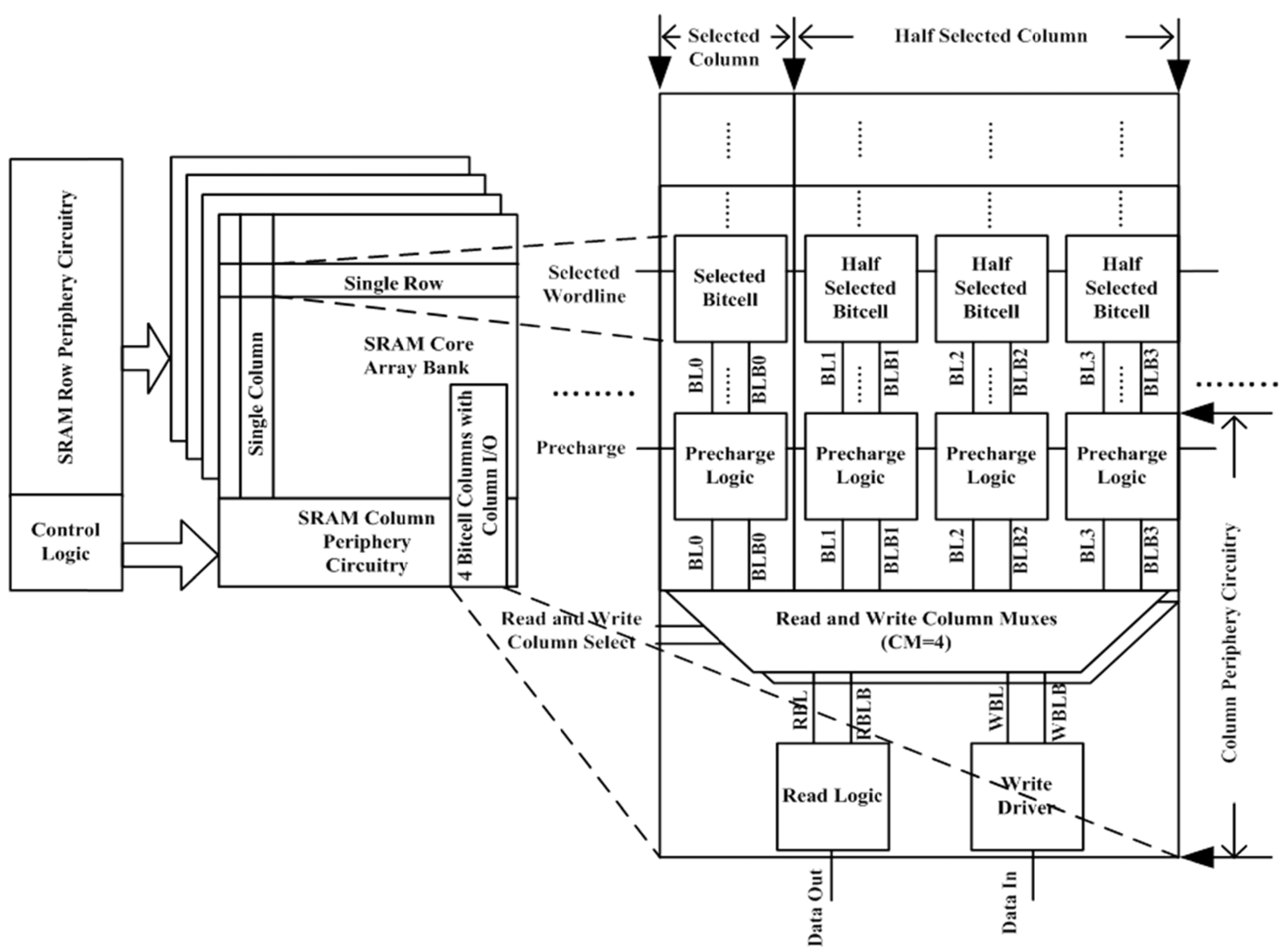

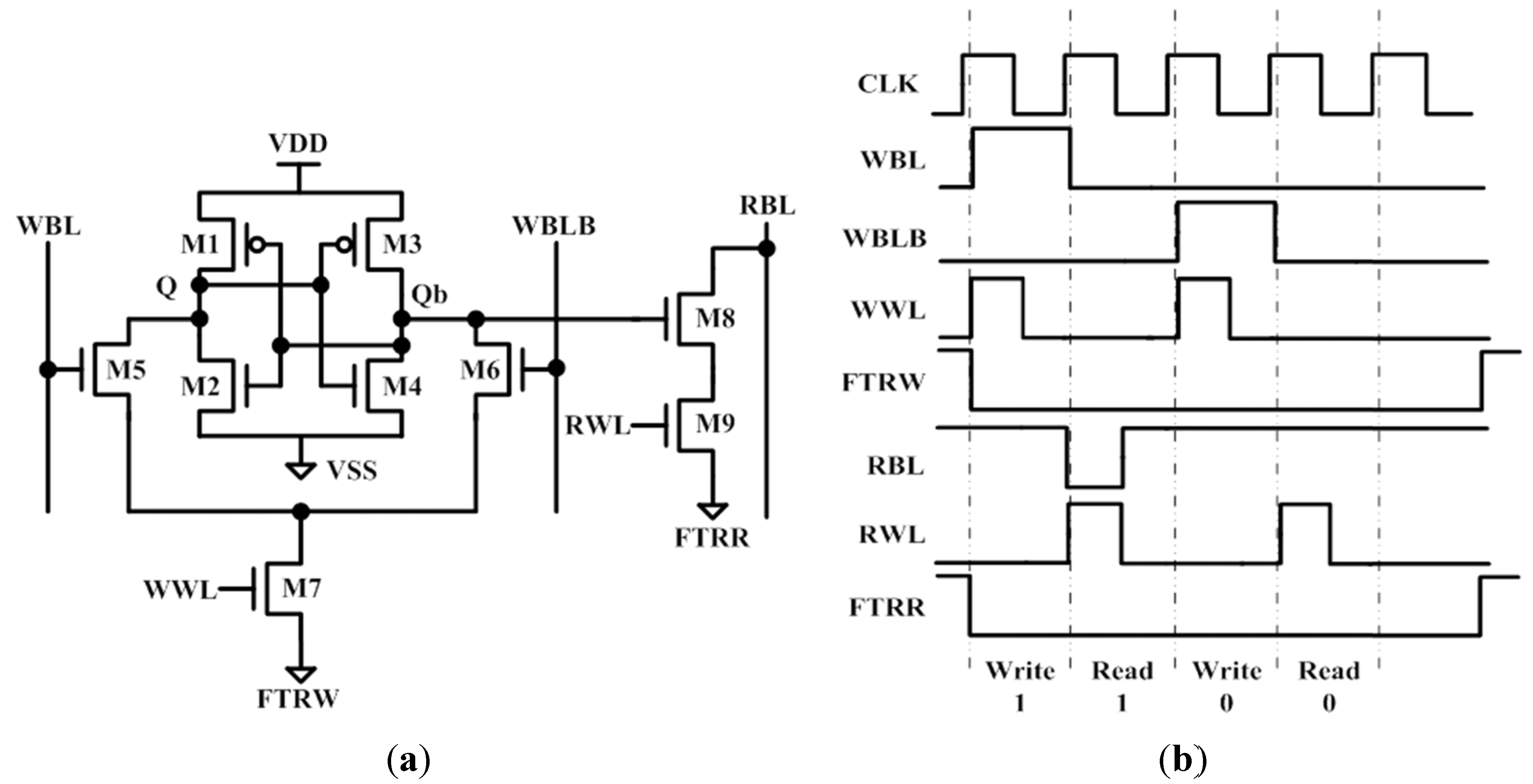

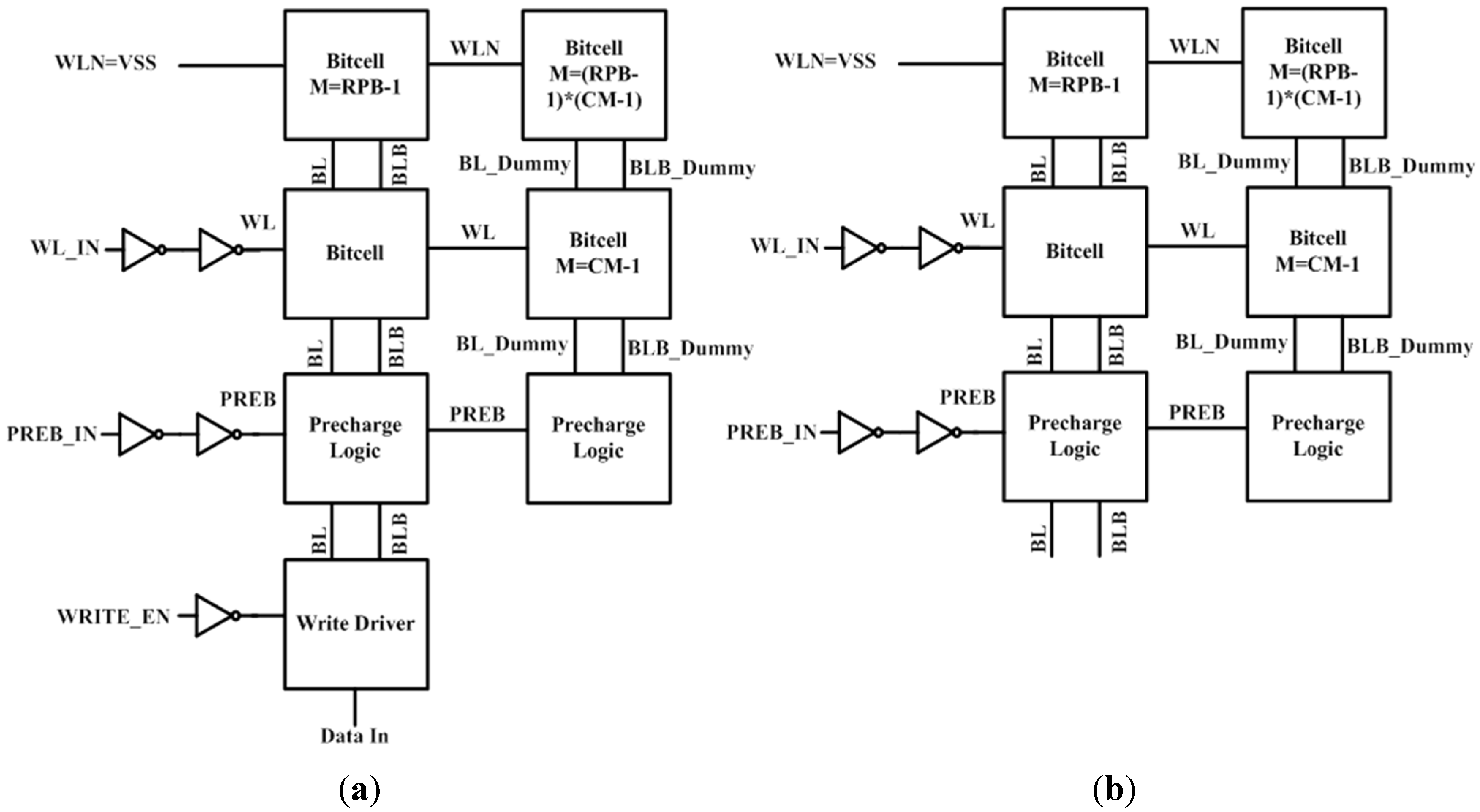

M7, M8, M9, M10 = 0.12u for Kulkarni’s bitcell. For capturing unnecessary energy drainage, we constructed a 4 × 4 modeled array (

Figure 6a,b) without the drivers for wordline,

etc.) using RPB = 4 and column mux factor (CM) = 4. This model is similar to a 4 × 4 array in the presence of 4:1 column mux, which reveals the dynamic energy loss due to the effect of half-select problem and signal toggling. Comparing with the half-select-free bitcells, the mean read energy of this work is 3.18× lower than Chang’s [

7], 2.52× lower than Feki’s [

8], 2.05× lower than 8T [

10], and 5.6% lower than Yang’s [

14]. On the other hand, the mean write energy of this work is 348× lesser than Chang’s [

7], 149× lower than Yang’s [

14], 1.12× lesser than 8T [

10], and 2.4% lower than Feki’s [

8] at the TT_0.4V_27C corner with a column mux (CM) 4 in the worst case scenario. We report that the mean leakage current at the same corner is 1.28× lower than the 8T [

10] bitcell (

Table 1). However, our bitcell has 50% higher read time, and 7× higher write time compared to the conventional 6T at the same corner.

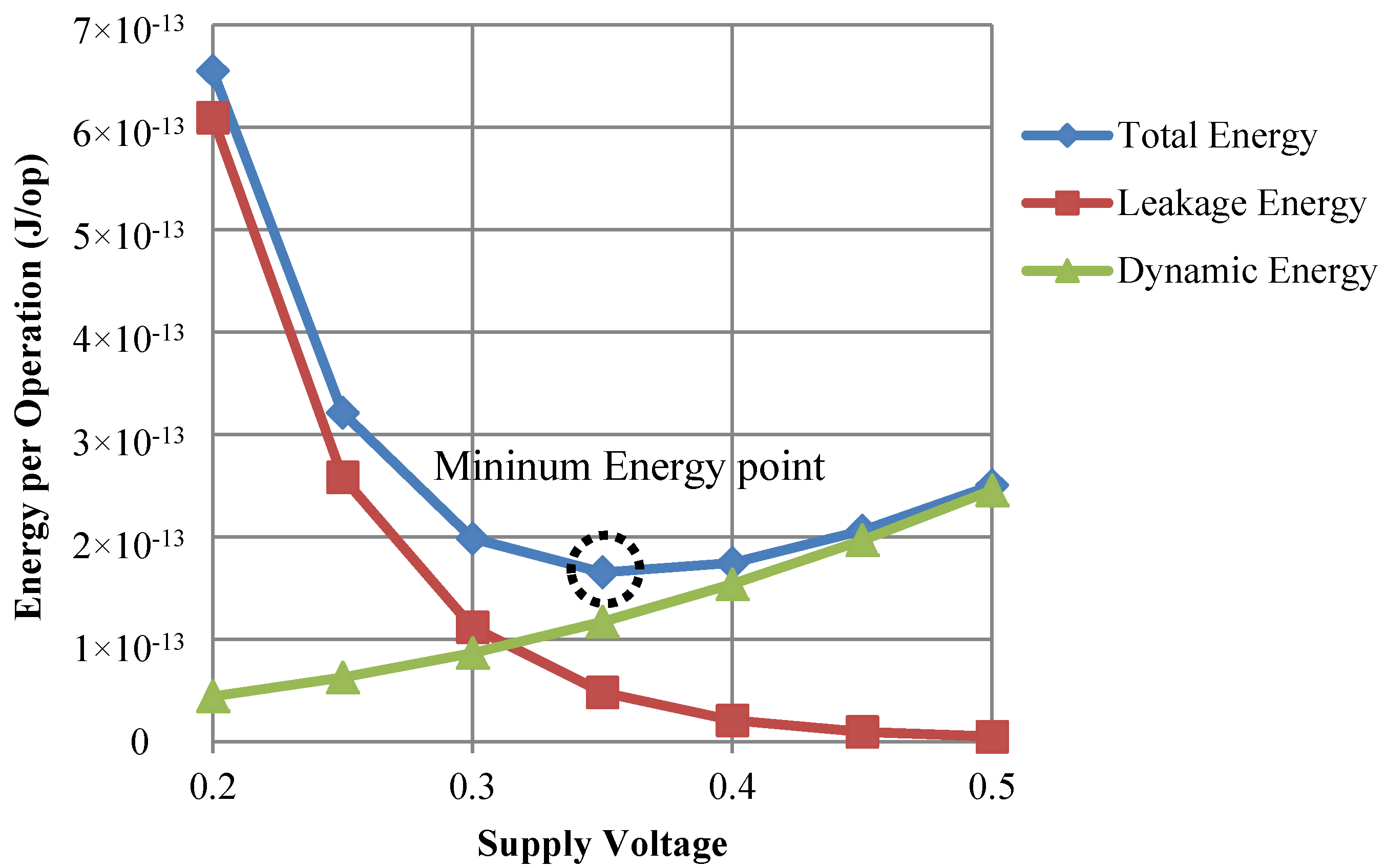

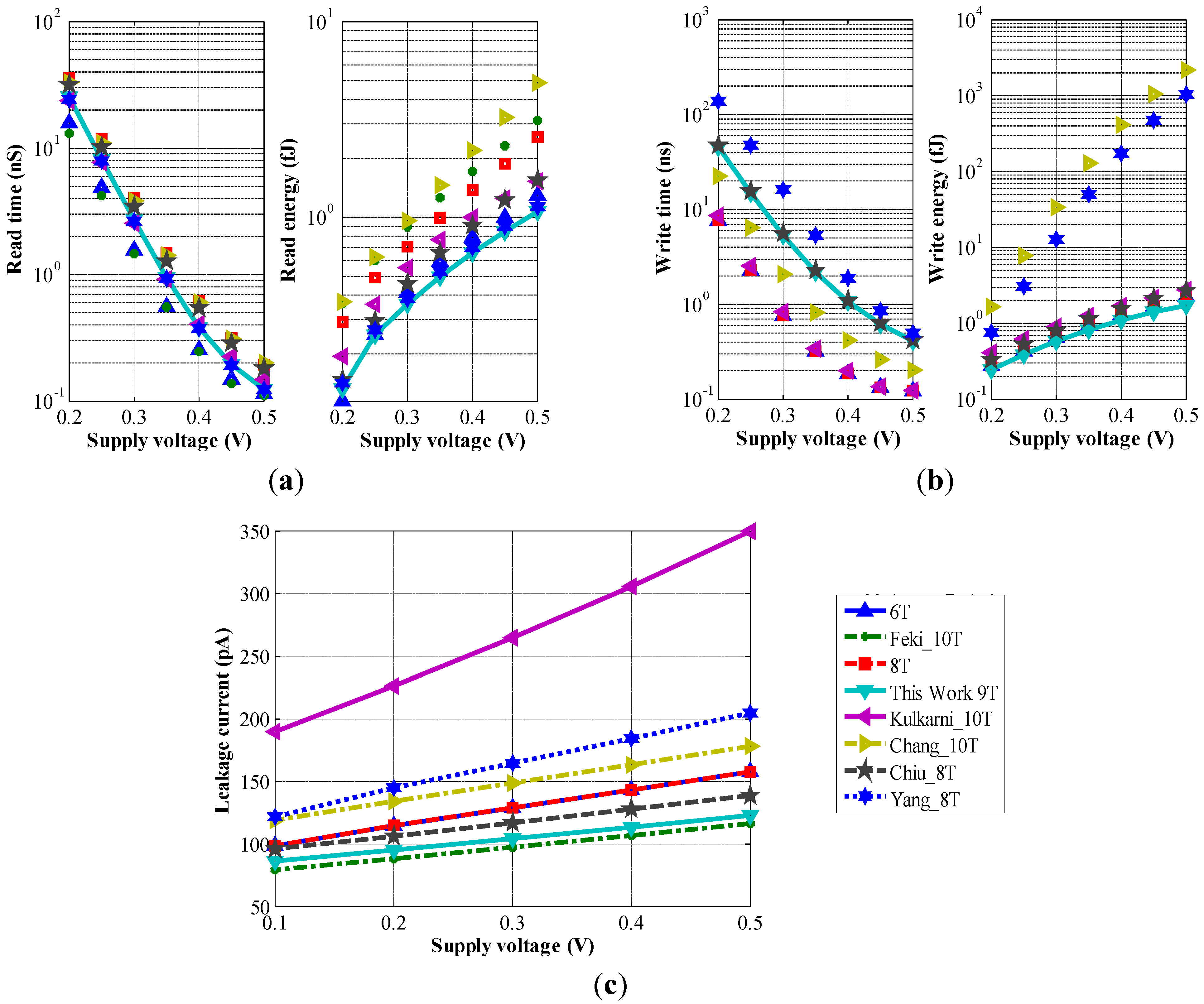

Figure 7a–c and

Table 1 show the comparison of the bitcells across voltages (0.2–0.5 V), and in the presence of statistical variations at the TT_0.4V_27C corner, respectively.

Figure 7.

(a) Bitcell read time and total read energy (semi-log scale) vs. supply voltage at TT_27C corner; (b) Bitcell write time and total write energy (semi-log scale) vs. supply voltage at TT_27C corner; (c) Bitcell standby leakage current vs. supply voltage at TT_27C corner.

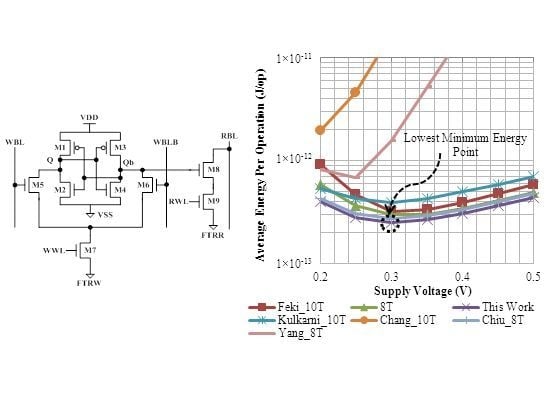

7.1. Comparison of Total Energy per Operation

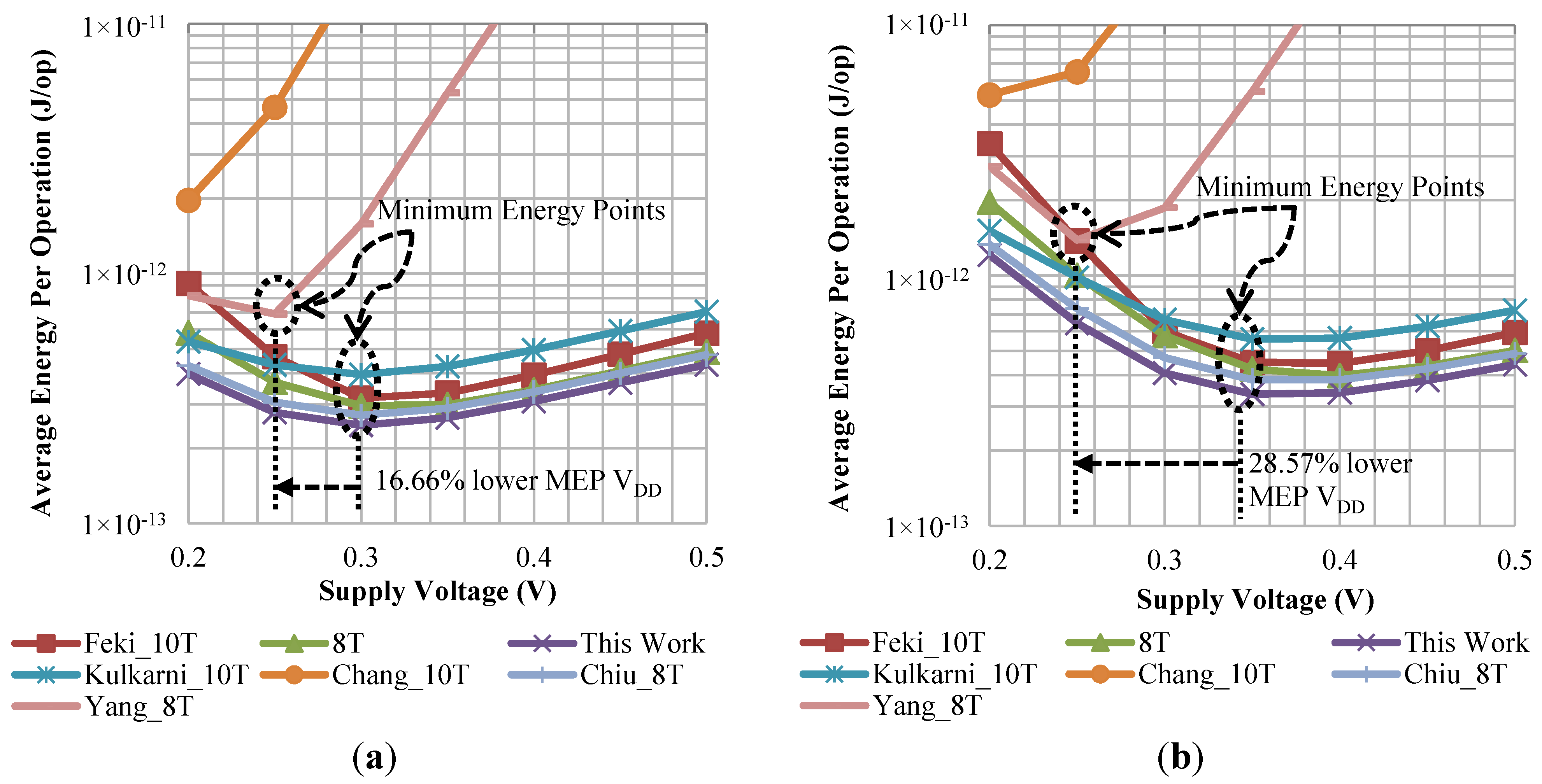

Figure 8a,b show total energy

vs. supply voltage plots and minimum energy points (MEP) for the bitcells with column mux (CM) = 4 and RPB = 16. We generate this plot using the assumption that per four read-write operations, we have three reads and one write, which means that our value of fraction of read and write (F

rdwr) is 0.75. We can see that for most of the 8 KB SRAMs, the MEP supply voltage is around 0.3 V, and for most of the 32 KB SRAMs, this MEP supply voltage is around 0.35 V. There are two exceptions to this fact: Chang’s bitcell does not have a minimum energy point within 0.2–0.5 V range in both the cases. This is because Chang’s bitcell has much higher dynamic energy per operation in the subthreshold region compare to the leakage energy per operation than other bitcells (

Figure 7a,b). We report 0.2 V as the MEP point for Chang’s bitcell for bigger SRAM macros since it does not have an MEP within the 0.2–0.5 V region. On the other hand, although, Yang’s bitcell has much higher MEP compare to other bitcells, its MEP supply voltage (V

DD) is around 0.25 V which is 16.66% lower than most of the bitcells’ MEP V

DD (

Figure 8a) in 8 KB SRAM and 28.57% lower than most of the bitcells’ MEP V

DD (

Figure 8b) in 32 KB SRAM.

Figure 8.

(a) Total energy vs. supply voltage of 8 KB SRAMs (CM = 4, RPB = 16); (b) Total energy vs. supply voltage of 32 KB SRAMs (CM = 4, RPB = 16).

Figure 8.

(a) Total energy vs. supply voltage of 8 KB SRAMs (CM = 4, RPB = 16); (b) Total energy vs. supply voltage of 32 KB SRAMs (CM = 4, RPB = 16).

7.2. MEP vs. Fraction of Read and Write and Comparison Results

In order to observe the effect of F

rdwr on minimum energy point, we vary the value of F

rdwr in Equation (1) and plot the MEP

vs. F

rdwr and MEP supply voltage

vs. F

rdwr in

Figure 9a,b with CM = 4. We can see that from

Figure 9a that increasing the F

rdwr results in a decrease in weighted minimum energy points in all bitcells for 32 KB SRAMs with 16 rows per bank (RPB). It is also noticeable that with the increase of F

rdwr the slope of the MEP

vs. F

rdwr changes more or less the same except for Chang’s bitcell, which has much slower slope changes than other bitcells. We report a 49.5% decrease in MEP for this work (

Figure 9a) as the F

rdwr increases from 0.5 to 0.9. This is because the read energy per operation of this work is much lower than the write energy per operation and weighing more in read energy per operation lowers the weighted MEP point. There is no clear trend observable from the MEP supply voltage

vs. F

rdwr plot among the bitcells (

Figure 9b). However, for Chiu’s and our bitcell, the MEP supply voltage remains constant from F

rdwr = 0.6–0.8 at 0.45 V. On the other hand, Yang’s and Chang’s bitcell also shows constant MEP supply voltages across F

rdwr = 0.6–0.9. On the contrary, Feki’s bitcell shows a linearly 20% decrease in MEP supply voltage from F

rdwr = 0.6–0.8. We also report that Chang’s bitcell has 16.66% lower MEP supply voltage than Yang’s bitcell from F

rdwr = 0.6–0.9. From

Figure 9a,b, we can say that although Chang’s and Yang’s bitcell has much higher MEP, due to lower MEP supply voltages, it is suitable for bigger subthreshold SoCs having comparable energy per operation with a higher number of logic cells.

Figure 9.

(a) Minimum energy point vs. fraction of read and write (Frdwr) for 32 KB SRAM (CM = 4, RPB = 16); (b) MEP supply voltage vs. fraction of read and write (Frdwr) for 32 KB SRAM (CM = 4, RPB = 16).

Figure 9.

(a) Minimum energy point vs. fraction of read and write (Frdwr) for 32 KB SRAM (CM = 4, RPB = 16); (b) MEP supply voltage vs. fraction of read and write (Frdwr) for 32 KB SRAM (CM = 4, RPB = 16).

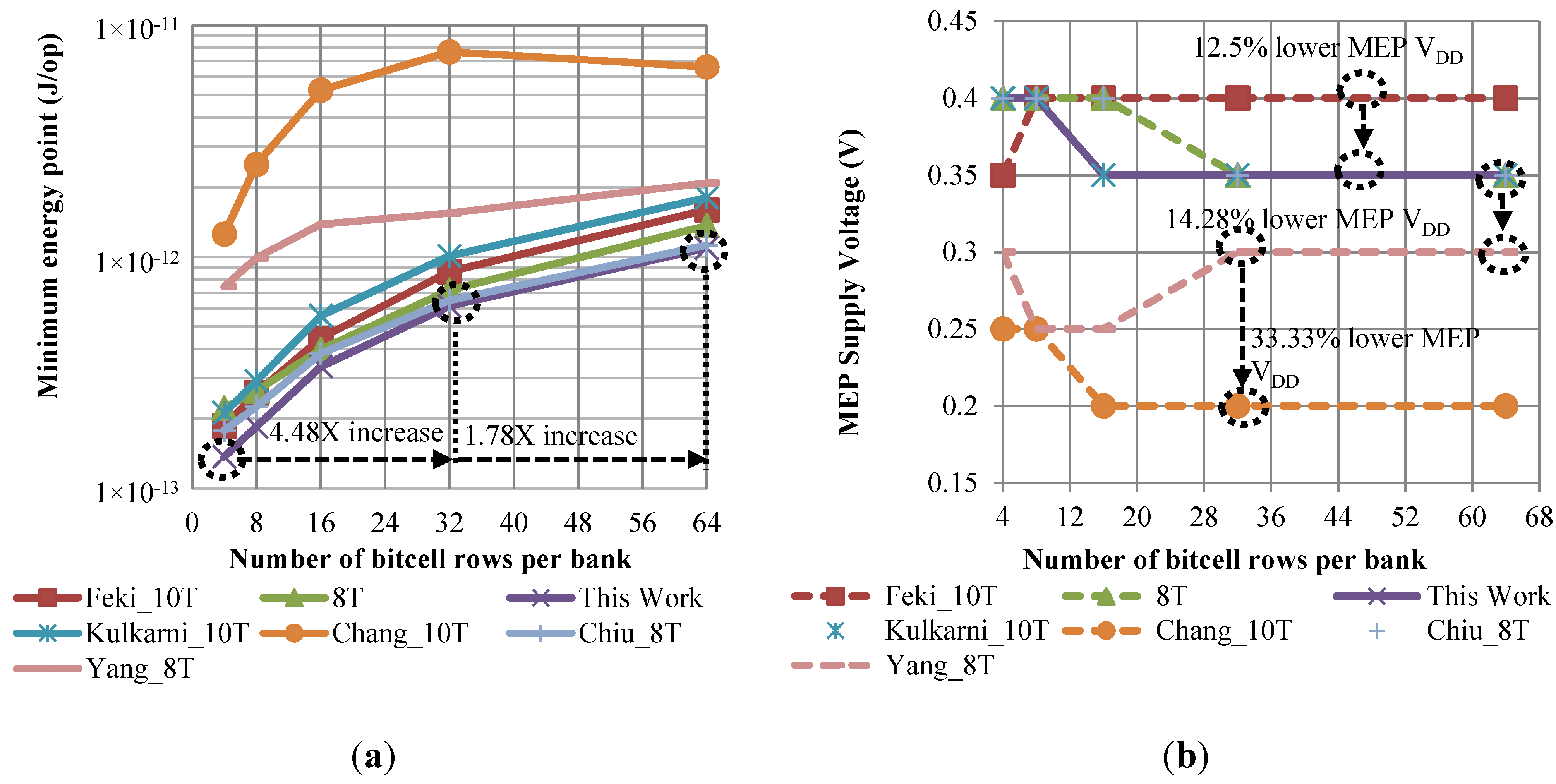

7.3. MEP vs. Number of Bitcell Rows per Bank Comparison Results

Figure 10a shows the variation of MEP with the number of bitcell rows per bank (RPB) for 32 KB SRAMs with CM = 4. This experiment uses a fixed SRAM macro size of 32 KB with word-width being fixed at word-width = 32 in a column mux 4 configuration. In order to keep the SRAM macro size fixed at 32 KB, the bank size and number of banks vary with RPB in this experiment. For the fixed size of 32 KB of SRAM macro size in this experiment, with the increase of RPB, the bank size increases and the number of banks decreases. We can see that all the modeled bitcell macros show a very similar trend of increasing MEP nonlinearly. This work shows minimum MEP variation across RPB = 4 to RPB = 64. However, from RPB = 32 to RPB = 64, Chiu’s bitcell MEP variation is comparable to this work. Within RPB = 16–32, conventional subthreshold 8T and Chiu’s bitcell MEPs are comparable too. We report Feki’s bitcell has 1.46×, 8T has 1.24×, Kulkarni’s bitcell has 1.65×, Chang’s bitcell has 6.05×, Chiu’s has 2.8%, and Yang’s bitcell has 1.9× higher MEP at RPB = 32 for 32 KB SRAM. The modeled macro with our bitcell shows 4.48× and 1.78× increase in MEP for increasing the RPB 8× from RPB = 4–32, and 2X from RPB = 32–64, respectively. We can see a trend in the MEP supply voltage

vs. RPB plot shown in

Figure 10b for 32 KB SRAM. All the bitcells show constant MEP supply voltage from RPB = 32–64. From RPB = 16–32, Feki’s, Kulkarni’s and Chang’s bitcell maintain their same constant MEP supply voltages as from RPB = 32–64. If we compare the MEP supply voltages of various bitcells above RPB = 32, we can see that Chang’s bitcell has 33.33% lower MEP supply voltage (V

DD) than Yang’s bitcell, Yang’s has 14.28% lower MEP V

DD than Kulkarni’s, this work and Chiu’s bitcell. On the other hand, our bitcell has 12.5% lower MEP V

DD than Feki’s bitcell.

Figure 10.

(a) Minimum energy point (MEP) vs. number of bitcell rows per bank (RPB) for 32 KB SRAMs (CM = 4); (b) MEP Supply voltage vs. RPB of 32 KB SRAMs (CM = 4).

Figure 10.

(a) Minimum energy point (MEP) vs. number of bitcell rows per bank (RPB) for 32 KB SRAMs (CM = 4); (b) MEP Supply voltage vs. RPB of 32 KB SRAMs (CM = 4).

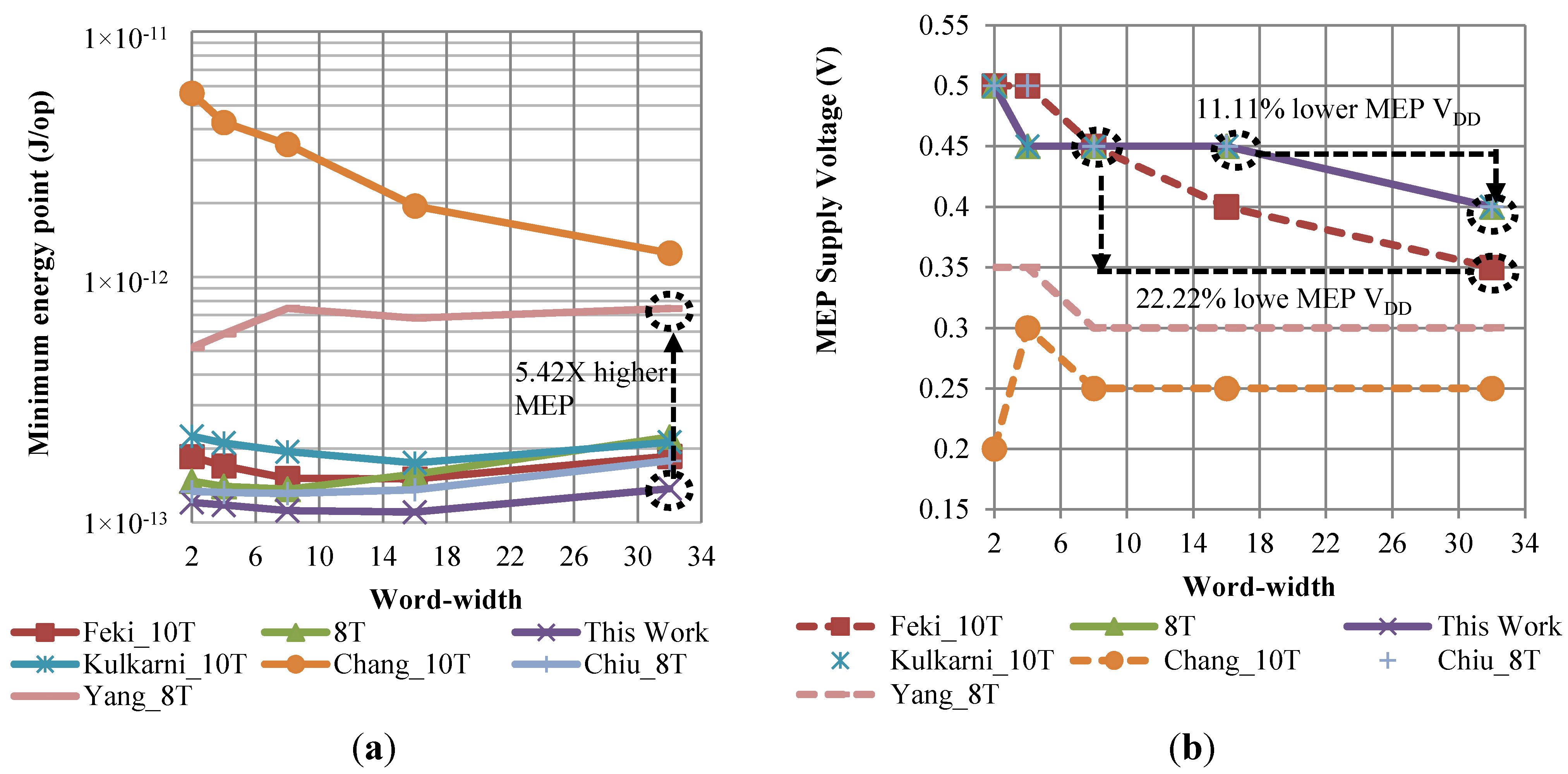

7.4. MEP vs. Word-Width Comparison Results

Figure 11a shows the plot for MEP

vs. number of SRAM bits in a word (word-width) for 32 KB SRAMs with CM = 4. We vary the word-width, and RPB at the same time, keeping the size of the banks fixed at 512 bits. Hence, the number of banks remains fixed at 512 for this experiment. In order to keep the bank size constant, the RPB decreases in a bank with the increase in word-width. As RPB and word-width both varies in this experiment with fixed bank size, we see a second order effect in MEP

vs. word-width plot (

Figure 11a): In almost all the bitcells (except Chang’s and Yang’s), the MEP first decreases and reaches a minimum point at some word-width then again it starts to increase. These minimum MEP points are at word-width = 8 for the 8T and Chiu’s bitcell, and at word-width = 16 for Kulkarni’s and Feki’s bitcells, and this work. It is also, noticeable that our bitcell MEP varies much less than the Chiu’s bitcell with increasing word-width. We report Feki’s bitcell has 1.35×, subthreshold 8T has 1.62×, Kulkarni’s bitcell has 1.55×, Chang’s bitcell has 9.14×, Chiu’s bitcell has 1.3×, and Yang’s bitcell has 5.42× higher MEP than this work for 32 KB SRAMs with word-width = 32 (

Figure 11a). Hence, with bigger memory macros, the combination of higher word-width and lower RPB is favorable for subthreshold SRAMs designed with our bitcell.

Figure 11b shows the variation of MEP supply voltage

vs. word-width. We can see a trend of decreasing MEP V

DD for all the bitcells except Chang’s and Yang’s bitcell. For the word-width increase of 4× from word-width = 8–32, Feki’s bitcell shows 22.22% reduction in MEP V

DD. On the other hand, Chiu’s and our bitcell show a 11.11% reduction in MEP V

DD for a 2× increase in word-width from word-width = 16–32.

Figure 11.

(a) Minimum energy point (MEP) vs. word-width (bank size and number of banks kept fixed) for 32 KB SRAMs; (b) MEP supply voltage vs. word-width for 32 KB SRAMs.

Figure 11.

(a) Minimum energy point (MEP) vs. word-width (bank size and number of banks kept fixed) for 32 KB SRAMs; (b) MEP supply voltage vs. word-width for 32 KB SRAMs.

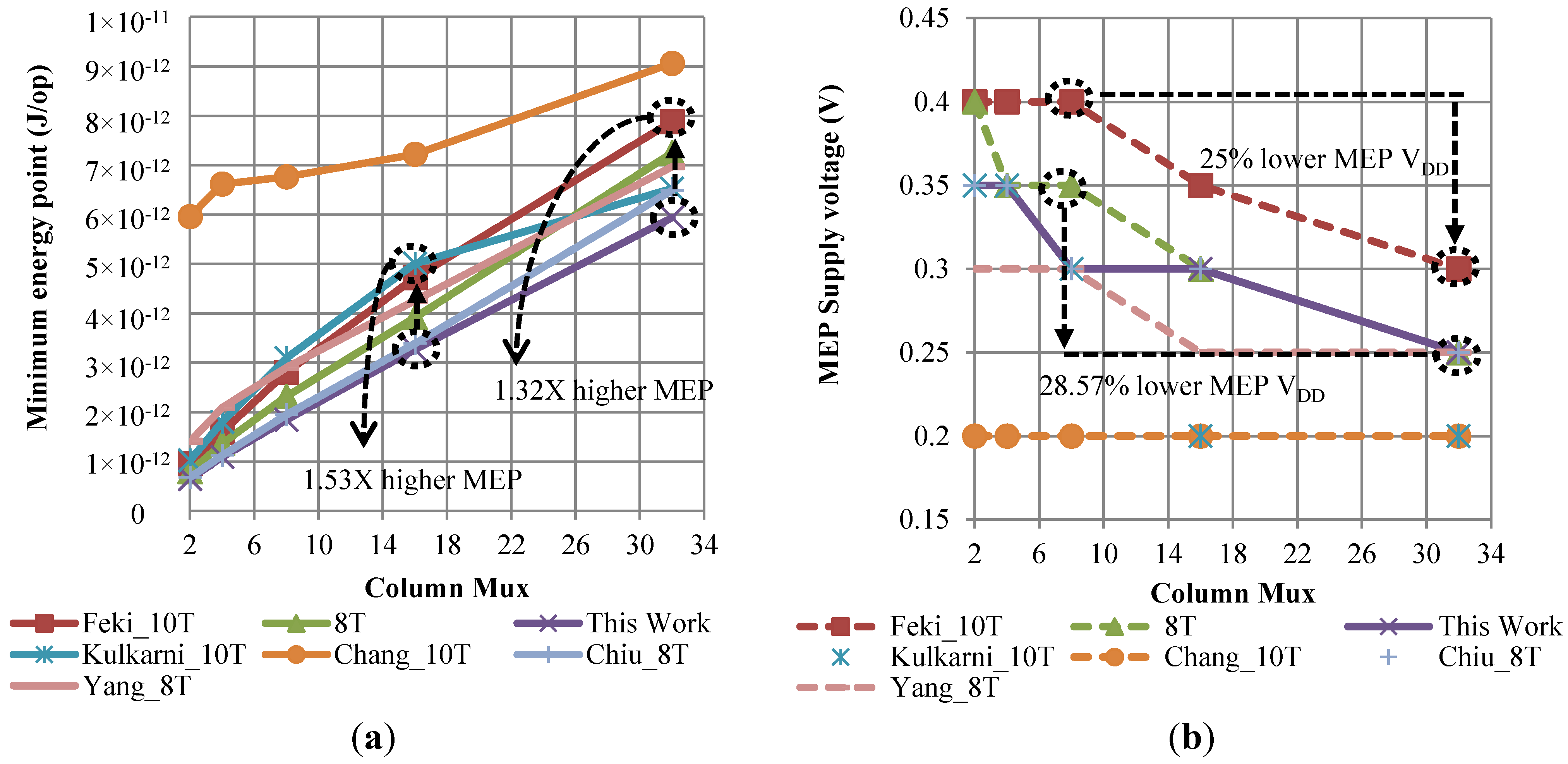

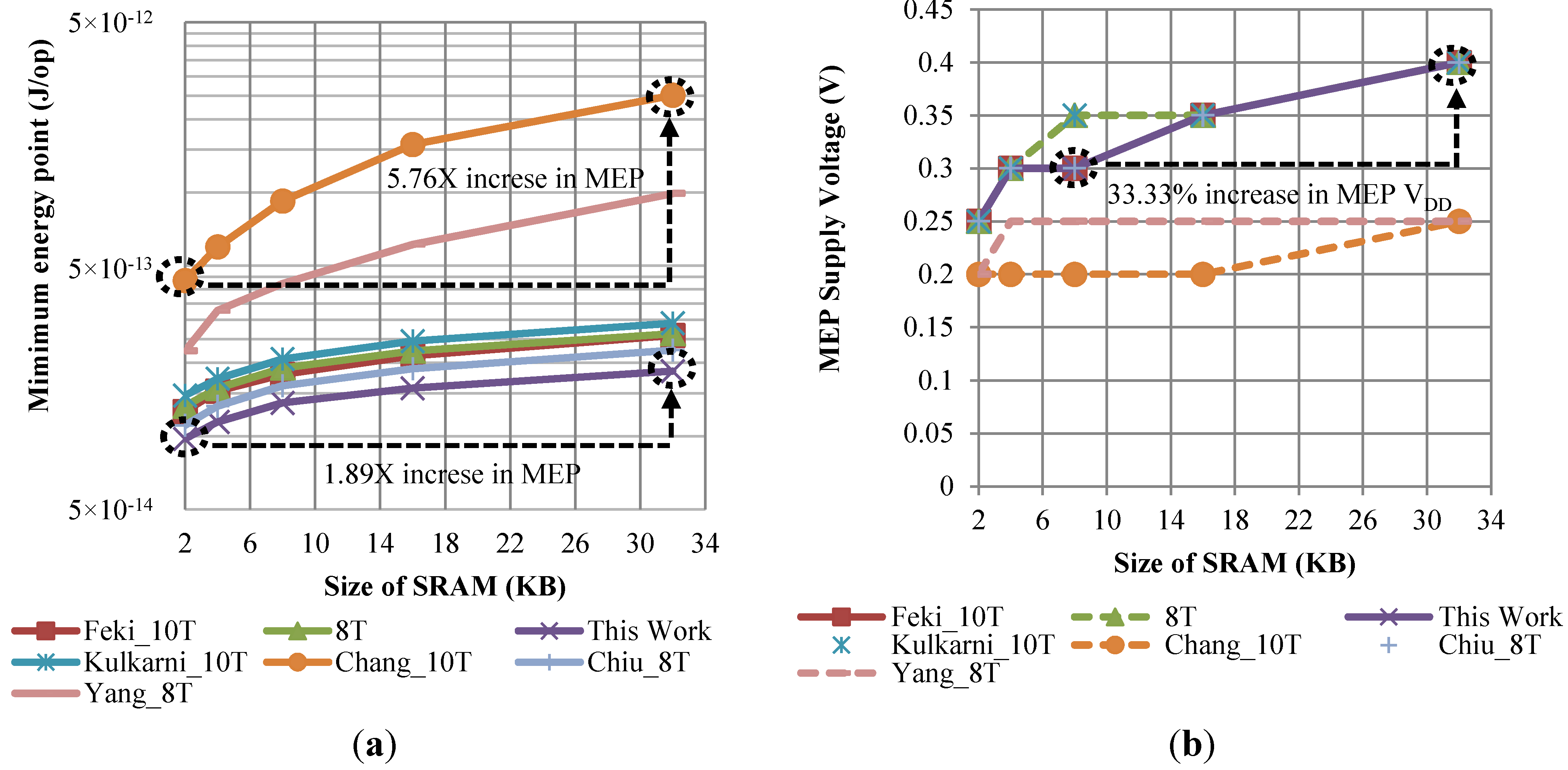

7.6. MEP vs. SRAM Size Comparison Results

Figure 13a shows the variation of MEP with increasing SRAM size with CM = 4. We conduct this experiment with the fixed bank size of 1024 bits per bank, RPB = 8 and word-width = 32 in a column mux 4 scenario. As the size of the SRAM banks remains fixed, the number of banks increases with the increase in memory size. We can see that the MEP of all bitcells increase with increasing SRAM memory size (

Figure 13a). This is an expected trend as for a fixed word-width, increasing the SRAM size increases the leakage energy per operation and hence, the MEP shifts to a higher value. However, for this work, it has the lowest MEP across 2–32 KB SRAM memory sizes with RPB = 8. This is consistent with the results of this work’s lower dynamic energy and leakage current data that keeps the MEP for this work lower compare to other bitcell macros. We report that for the SRAM size of 8 KB, Feki’s bitcell has 1.31×, 8T has 1.39×, Kulkarni’s bitcell has 1.51×, Chang’s bitcell has 6.75×, Chiu’s bitcell has 17.54%, and Yang’s bitcell has 3.08× higher MEP than this work. Increasing the SRAM memory size 16× from 2 to 32 KB increases the MEP by only 1.89× for this work, but the other bitcells’ MEP numbers increase by 2.04× for Feki’s bitcell, 1.98× for Kulkarni’s and 8T bitcell, 5.77× for Chang’s bitcell, 2.03× for Chiu’s bitcell, and 4.43× for Yang’s bitcell.

Figure 13b shows the variation of MEP supply voltage

vs. SRAM macro size. We observe that with the increase in SRAM size, the MEP supply voltage increases for almost all the bitcells. We report a 33.33% increase in MEP supply voltage for Feki’s, Chiu’s, 8T and our bitcell. On the contrary, it is interesting to can see that from 4–32 KB, Yang’s bitcell has a constant MEP supply voltage. Thus, even though Yang’s bitcell has much higher MEP across different SRAM sizes, it can be suitable for bigger subthreshold SoCs having comparable logic energy per operation. However, for smaller low energy biomedical SoCs, our SRAM bitcell shows promising MEP numbers.

Figure 13.

(a) Minimum energy point (MEP) vs. SRAM memory size (KB); (b) MEP supply voltage vs. SRAM memory size (KB).

Figure 13.

(a) Minimum energy point (MEP) vs. SRAM memory size (KB); (b) MEP supply voltage vs. SRAM memory size (KB).