MDPI

Communication

# A 0.6 V Bulk-Driven Class-AB Two-Stage OTA with Non-Tailed Differential Pair

Andrea Ballo 🗓, Alfio Dario Grasso \*🗓 and Salvatore Pennisi 👨

DIEEI (Dipartimento di Ingegneria Elettrica Elettronica e Informatica), University of Catania, I-95125 Catania, Italy

\* Correspondence: alfiodario.grasso@unict.it

**Abstract:** This work presents a two-stage operational transconductance amplifier suitable for sub-1 V operation. This characteristic is achieved thanks to the adoption of a bulk-driven non-tailed differential pair. Local positive feedback is exploited to boost the equivalent transconductance of the first stage and the quasi-floating gate approach enables the class AB operation of the second stage. Implemented in a standard 180 nm CMOS technology and supplied at 0.6 V, the amplifier exhibits a 350 kHz gain bandwidth product and a phase margin of 69° while driving a 150 pF load. Compared to other solutions in the literature, the proposed one exhibits a considerable performance improvement, especially for large signal operation.

Keywords: body-driven amplifier; low-power; low-voltage; positive feedback

#### 1. Introduction

In applications that require low power consumption, such as implantable biomedical devices, sensor nodes for the Internet of Things, and energy-harvesting battery-less devices, the design of analog circuits has become a challenging task. Indeed, while in these applications the digital part benefits from the technological scaling in terms of energy consumption reduction and performance enhancement, the performance of analog circuits decreases when technology is scaled down due to the reduced intrinsic gains of transistors and of the signal-to-noise ratios [1,2]. These disadvantages are exacerbated when the supply voltage is reduced below 1V, in which the design of the operational transconductance amplifier (OTA), representing the universal and fundamental building block of any analog front-end, is particularly difficult.

Below the 1V supply, the most widely used design approach is the sub-threshold bias (also known as the weak reverse bias) [3–10]. Inverter-based OTAs represent another viable alternative [11–13]. However, the main disadvantage of operating the digital inverter as an amplifier is the high variation of the dc gain and gain bandwidth (GBW), with temperature and process corners. Moreover, only pseudo-differential operation is achievable.

When input rail-to-rail capability is required, the bulk driving (body driving) technique is an effective solution, even in combination with sub-threshold operation [14–28]. However, when compared to conventional gate-driven circuits, body-driven counterparts exhibit a lower voltage gain due to the reduced value of the bulk transconductance, which accounts for only 10–20% of the gate transconductance [1]. Moreover, if the bulk of NMOS transistors must also be driven, the body-driven approach mandates for a triple-well process. However, since most of the modern CMOS technologies provide such feature, this point is not a real limitation

To overcome the low gain of bulk-driven OTAs, we exploit in this work local positive feedback to improve first-stage transconductance [26,29–31]. The class AB operation of the second stage is enabled by exploiting the quasi-floating gate approach [32]. Moreover, the tail bias current of the input gain stage is avoided while maintaining differential operation.

Citation: Ballo, A.; Grasso, A.D.; Pennisi, S. A 0.6 V Bulk-Driven Class-AB Two-Stage OTA with Non-Tailed Differential Pair. *J. Low Power Electron. Appl.* 2023, 13, 24. https://doi.org/10.3390/jlpea13020024

Academic Editors: Marcello De Matteis and Fabian Khateb

Received: 24 February 2023 Revised: 16 March 2023 Accepted: 24 March 2023 Published: 28 March 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

This paper is structured as follows. Section 2 discusses the circuit operation principle and analytical design equations are carried out. Section 3 describes the design and simulation of the OTA, while in Section 4 the experimental measurements and a comparison with other amplifiers in the literature are reported. Finally, concluding remarks are drawn in Section 5.

## 2. The Proposed Circuit

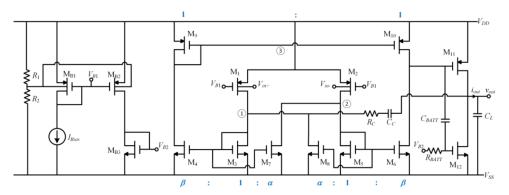

Figure 1 shows the schematic diagram of the designed amplifier. Where not represented, the transistor bulk terminal is considered to be connected to the corresponding source. The first OTA stage is a bulk-driven non-tailed differential pair  $M_1$ - $M_2$  loaded by the current mirror  $M_3$ - $M_4$  and  $M_5$ - $M_6$ . Differential to single-ended conversion is implemented by the additional current mirror  $M_9$ - $M_{10}$ . The diode-connected transistor  $M_{B1}$  generates the voltage  $V_{B1}$  to be applied to the gates of  $M_1$ - $M_2$ , thus setting their bias current. It is worth noting that the bulk terminal of  $M_{B1}$  is biased through the voltage divider  $R_1$ - $R_2$ , which sets the analog ground [26].

Figure 1. OTA schematic.

Due to the lack of the tail current generator, the couple  $M_1$ - $M_2$  works as a pseudo-differential pair; however, as detailed in [26], the overall OTA input stage exhibits a quasi-differential behavior due to the action of  $M_7$  and  $M_8$  that make voltages at node 1 and 2, as seen in in Figure 1, dependent on the difference of the inverting and noninverting input voltages.

Thanks to the action of the local positive feedback implemented by transistors  $M_7$  and  $M_8$ , the equivalent differential transconductance of the first stage is expressed by [26]:

$$G_m = \frac{\beta}{1 - \alpha} g_{mb1,2} \tag{1}$$

where

$$\alpha = \frac{(W/L)_7}{(W/L)_3} = \frac{(W/L)_8}{(W/L)_5} \tag{2}$$

$$\beta = \frac{(W/L)_4}{(W/L)_3} = \frac{(W/L)_6}{(W/L)_5},\tag{3}$$

and  $g_{mb1,2}$  is the bulk transconductance of  $M_1$  and  $M_2$  and it is assumed that  $(W/L)_9 = (W/L)_{10}$ . From (1), it is apparent that the first-stage transconductance can be boosted by appropriately choosing the aspect ratios  $\alpha$  and  $\beta$  from (2) and (3), respectively. In particular, to avoid the magnitude of the positive feedback being higher than one (and, consequently, the amplifier becoming a latch), parameter  $\alpha$  must be lower than 1. As a general rule of thumb, it is desirable to set  $\alpha$  less than 0.9 to guarantee an adequate margin against process mismatches [31].

The second stage is made up of the common source stage  $M_{11}$  and  $M_{12}$ . Class AB operation is enabled by adding resistor  $R_{BATT}$ , connected between the gate of the load

transistor  $M_{12}$  and the diode-connected transistor  $M_{B3}$ , and capacitor  $C_{BATT}$  which adds a path for the signal during dynamic operation [32]. Under quiescent conditions and considering that no DC current flows through  $R_{BATT}$ , the voltage at the gate of  $M_{12}$  is the same as at the gate of  $M_{B3}$ . Consequently, the quiescent current in  $M_{12}$  can be precisely set like in a conventional current mirror. During dynamic operation, the voltage at the output of the first stage is subject to a large variation. Capacitor  $C_{BATT}$ , which cannot discharge/charge rapidly through  $R_{BATT}$ , acts as a floating battery and transfers the voltage changes to the gate of  $M_{12}$ , thus providing class AB operation to the second stage.

The frequency compensation branch is implemented by the conventional Miller capacitor  $C_C$  in series with the resistor  $R_C$  connected across node 1 and the output node.

Neglecting the parasitic capacitance contribution at nodes 1, 2, and 3 in Figure 1, the open-loop transfer function of the OTA can be approximated as

$$A(s) \approx A_0 \frac{1 + \frac{s}{z}}{\left(1 + \frac{s}{p_D}\right)\left(1 + \frac{s}{p_2}\right)} \tag{4}$$

being  $A_0 = G_{mb}(g_{m11} + g_{m12})r_{o1}r_{o2}$  the DC gain, with  $r_{o1} = r_{d10}//r_{d6}$  and  $r_{o2} = r_{d11}//r_{d12}$ , and the zero and poles expressed by

$$z = \frac{\alpha + 2}{C_C \left(\frac{1}{g_{m3,5}} + 2R_C\right)} \tag{5}$$

$$p_D = \frac{1 - \alpha^2}{r_{o2}(C_L + (1 + \alpha)\beta(g_{m11} + g_{m12})r_{o1}C_C)} \approx \frac{(1 - \alpha)}{\beta(g_{m11} + g_{m12})r_{o1}r_{o2}C_C}$$

(6)

$$p_{2} = \frac{C_{L} + (1 + \alpha)\beta(g_{m11} + g_{m12})r_{o1}C_{C}}{C_{C}C_{L}\left(\frac{1}{g_{m3,5}} + R_{C}\right)} \approx \frac{(1 + \alpha)\beta(g_{m11} + g_{m12})r_{o1}}{C_{L}\left(\frac{1}{g_{m3,5}} + R_{C}\right)}$$

(7)

where the rightmost approximation in (6) and (7) holds if the following relation is satisfied:

$$C_L \ll (1+\alpha)\beta(g_{m11}+g_{m12})r_{o1}C_C$$

(8)

It is worth noting that, thanks to the adopted compensation strategy which exploits the embedded current buffer  $M_3$ - $M_4$ - $M_9$ - $M_{10}$ , the non-dominant pole  $p_2$  is moved at high frequency by a factor equal to  $(1 + \alpha)\beta$  as compared to a conventional two-stage Miller OTA.

The evaluation of the phase margin (PM) yields

$$PM \approx 90^{\circ} - \tan^{-1} \left( \frac{GBW}{p_2} \right) + \tan^{-1} \left( \frac{GBW}{z} \right)$$

(9)

where *GBW* is the gain bandwidth product equal to  $g_{mb1,2}/C_C$ .

The slew rate (SR) of an amplifier is determined by the maximum available charging/discharging currents of capacitors in the circuit. By inspection of Figure 1 and neglecting the effect of parasitic capacitors, the overall SR can be expressed as

$$SR \approx \min\left(\frac{I_1}{C_C}, \frac{I_{out}}{C_L}\right) \approx \frac{I_{out}}{C_L}$$

(10)

where  $I_1$  is the maximum current provided by  $M_1$  and  $I_{out}$  is the charging/discharging current of the class AB output stage. Being  $C_C \ll C_L$ , the rightmost approximation in (10) holds.

## 3. Design and Simulation Results

Using a standard 180 nm CMOS process supplied by STMicroelectronics, the amplifier shown in Figure 1 was designed using the transistor dimensions, bias conditions, passive

components values, and small-signal parameters reported in Tables 1–3 and assuming a nominal supply voltage equal to 0.6 V. The resistors were implemented using high-resistance polysilicon resistors with a square resistance of 3 k $\Omega$ .

Table 1. Transistor dimensions.

| Device                     | Value (μm/μm)        |

|----------------------------|----------------------|

| $M_{B1}, M_{B2}, M_1, M_2$ | 3/0.26 (×2)          |

| $M_{B1}, M_3, M_5$         | 6/0.26               |

| $M_4, M_6, M_{12}$         | $6/0.26 (\times 15)$ |

| $M_7, M_8$                 | 5/0.26               |

| $M_9, M_{10}$              | $6/0.26 (\times 4)$  |

| M11                        | 6/0.26 (×8)          |

Table 2. Component values.

| Device         | Value                   |

|----------------|-------------------------|

| $R_1, R_2$     | $300  \mathrm{k}\Omega$ |

| $R_{BATT}^{-}$ | $1\mathrm{M}\Omega$     |

| $R_C$          | $100~\mathrm{k}\Omega$  |

| $C_{BATT}$     | 800 fF                  |

| $C_{C}$        | 500 fF                  |

| $C_L$          | 150 pF                  |

| $I_{Bias}$     | 180 nA                  |

Table 3. Small-signal parameters.

| Param.        | Value           | Parameter      | Value                   |

|---------------|-----------------|----------------|-------------------------|

| <i>§</i> m1,2 | 3.98 µA/V       | <i>§m</i> 9,10 | 31.38 μA/V              |

| 8mb1,2        | 1.197 μA/V      | <i>Sm</i> 11   | 55.97 μA/V              |

| Şm3,5         | 2.71 μA/V       | <i>Şm</i> 12   | 62.89 μA/V              |

| 8m4,6         | $36.04~\mu A/V$ | $r_{o1}$       | $1.03~\mathrm{M}\Omega$ |

| <i>§</i> m7,8 | 1.848 μA/V      | $r_{o2}$       | 764 kΩ                  |

Considering the transistor dimensions reported in Table 1, parameters  $\alpha$  and  $\beta$  are equal to 0.83 and 15, respectively. Therefore, the bulk transconductance of  $M_1$  and  $M_2$ , equal to 3.98  $\mu$ A/V, is boosted by about 88 times.

Corner simulations and Monte Carlo analysis are executed to assess the robustness of the amplifier over process, temperature, and mismatch variations. The results are reported in Tables 4–6 for three different temperatures (i.e.,  $-10\,^{\circ}$ C, 27 °C, and 85 °C) for all transistor corners. The results show that the amplifier is stable in all conditions. Furthermore, Monte Carlo simulation results over 1000 runs show a relative standard deviation lower than 25% for all parameters.

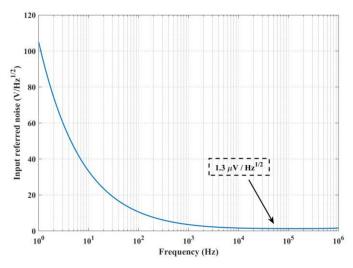

Figure 2 shows the simulated input referred noise versus frequency. The white noise level is equal to 1.3  $\mu V/\sqrt{Hz}$ .

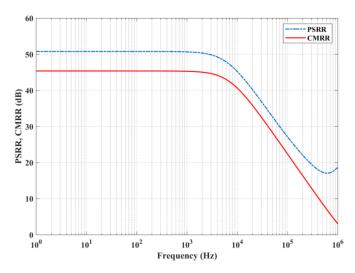

Figure 3 shows the magnitude of the power supply rejection ratio (PSRR) and the common mode rejection ratio (CMRR) versus frequency.

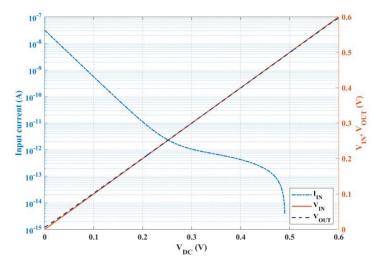

Figure 4 depicts the DC transfer characteristic of the amplifier in unity-gain configuration, showing a rail-to-rail input common mode range (*ICMR*). In the same figure, it can be also noted that the input current is lower than 13 nA.

| D.                    | aran. | SS    | GE.   | EC     | FF    | MC    |                      |  |

|-----------------------|-------|-------|-------|--------|-------|-------|----------------------|--|

| Param.                | TT    |       | SF    | FS     | FF    | μ     | σ                    |  |

| Power (μW)            | 3.29  | 3.11  | 3.19  | 3.31   | 3.44  | 3.27  | 0.24                 |  |

| DC Gain (dB)          | 64.8  | 59.6  | 67    | 56.7   | 67.1  | 67.4  | 0.8                  |  |

| GBW (kHz)             | 357   | 313.7 | 349.6 | 302.3  | 370.1 | 481.8 | 34.6                 |  |

| Phase Margin (deg)    | 67.6  | 67.5  | 67    | 69.6   | 68.8  | 67.6  | 2.1                  |  |

| Pos. Slew Rate (V/μs) | 0.17  | 0.09  | 0.34  | 0.08   | 0.3   | 0.17  | 0.04                 |  |

| Neg. Slew Rate (V/μs) | 6.61  | 5.98  | 5.47  | 6.7    | 6.62  | 6.58  | 0.57                 |  |

| $V_{OS}$ ( $\mu V$ )  | 18.6  | -7    | 56.6  | -108.5 | 30.3  | -78.1 | $13.5 \cdot 10^{-3}$ |  |

**Table 5.** Corner and Monte Carlo (1000 iterations) analysis results for T =  $27 \, ^{\circ}$ C.

| _                     |       |       | <b>67</b> | T.C   |       | MC    |                      |  |

|-----------------------|-------|-------|-----------|-------|-------|-------|----------------------|--|

| Param.                | TT    | SS    | SF        | FS    | FF    | μ     | Σ                    |  |

| Power (μW)            | 3.71  | 3.56  | 3.64      | 3.36  | 3.86  | 3.69  | 0.28                 |  |

| DC Gain (dB)          | 67.4  | 65.7  | 68.5      | 64.2  | 68.1  | 67.2  | 0.5                  |  |

| GBW (kHz)             | 341.6 | 333.1 | 332.9     | 337.2 | 343.6 | 471.9 | 24.2                 |  |

| Phase Margin (deg)    | 66.6  | 65.4  | 66.3      | 67.1  | 68    | 66.5  | 1.8                  |  |

| Pos. Slew Rate (V/µs) | 0.31  | 0.18  | 0.54      | 0.15  | 0.49  | 0.32  | 0.06                 |  |

| Neg. Slew Rate (V/μs) | 4.6   | 4.72  | 3.92      | 4.99  | 4.35  | 4.58  | 0.37                 |  |

| $V_{OS}(\mu V)$       | 53.8  | 50.6  | 67.8      | 37.2  | 58.8  | -30.5 | $13.4 \cdot 10^{-3}$ |  |

**Table 6.** Corner and Monte Carlo (1000 iterations) analysis results for T = 85 °C.

|                       | T.T.  | 66    | SF    | T.C   |      | MC    |                      |  |

|-----------------------|-------|-------|-------|-------|------|-------|----------------------|--|

| Param.                | TT    | SS    |       | FS    | FF   | μ     | Σ                    |  |

| Power (μW)            | 4.22  | 4.17  | 4.22  | 4.24  | 4.23 | 3.91  | 0.21                 |  |

| DC Gain (dB)          | 68.1  | 68    | 68.4  | 67.2  | 68   | 66.4  | 0.4                  |  |

| GBW (kHz)             | 304.3 | 304.6 | 295.9 | 310.3 | 303  | 423.7 | 18.1                 |  |

| Phase Margin (deg)    | 65.4  | 64    | 65.3  | 65.7  | 66.8 | 65.4  | 1.5                  |  |

| Pos. Slew Rate (V/µs) | 0.57  | 0.39  | 0.88  | 0.35  | 0.84 | 0.58  | 0.08                 |  |

| Neg. Slew Rate (V/μs) | 2.15  | 2.42  | 1.55  | 2.71  | 1.86 | 2.15  | 0.22                 |  |

| $V_{OS}$ ( $\mu V$ )  | 95.2  | 89    | 107.7 | 86    | 105  | 16.9  | $13.4 \cdot 10^{-3}$ |  |

Figure 2. Input referred noise versus frequency.

Figure 3. Magnitude of PSRR and CMRR versus frequency.

Figure 4. DC transfer characteristics in unity-gain configuration.

## 4. Measurement Results and Comparison

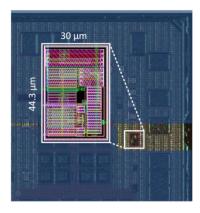

The OTA in Figure 1 has been fabricated and experimentally tested. The layout and the chip microphotograph of the circuit are shown in Figure 5. The occupied area is  $1329 \mu m^2$ .

Figure 5. Chip microphotograph and layout of the amplifier.

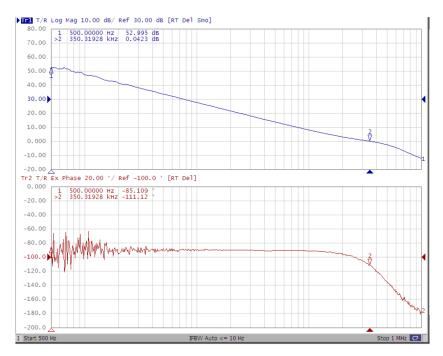

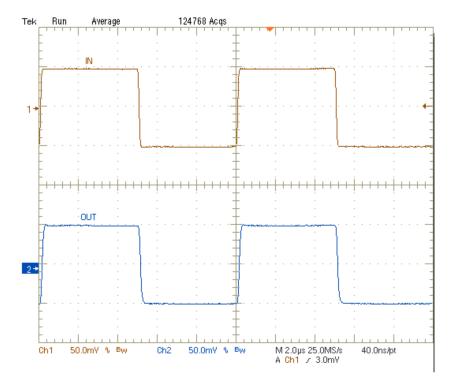

The circuit has been characterized at a 0.6 V supply and a 150 pF capacitive load. Figure 6 reports the measured Bode plot in open-loop configuration, showing a GBW equal to 350 kHz and a PM equal to 69°. The transient response to a 100 mV<sub>pp</sub> input step, with the OTA in unity gain, is shown in Figure 7.

Figure 6. Measured open-loop Bode plot.

Figure 7. Measured unity-gain step response.

Table 6 summarizes the OTA main performance parameters and a comparison with other sub-1 V amplifiers taken form the literature. To evaluate the performance trade-off between bandwidth, load capacitance, slew rate (SR), and total bias quiescent,  $I_T$ , we use in Table 6, the following conventional figures of merit:

$$IFOM_S = \frac{GBW}{I_T}C_L \tag{11a}$$

$$IFOM_L = \frac{SR}{I_T}C_L. \tag{11b}$$

Among the considered solutions, only the single-stage in [26] exhibits a higher value of  $IFOM_S$  but with a DC gain equal to 38 dB only. As compared to the remaining solutions, the increase in (11a) is equal to about 3.45. The proposed topology shows an increase in  $IFOM_L$  equal to  $4.36 \times$  against all the other solutions.

Two other traditional figures of merit, which take into account the silicon area, are included in Table 7:

$$IFOM_{AS} = \frac{\omega_{GBW}}{Area \cdot I_T} C_L \tag{12a}$$

$$IFOM_{AL} = \frac{SR}{Area \cdot I_T} C_L. \tag{12b}$$

Additionally, in this case the proposed solution outperforms the other amplifiers, except for the  $IFOM_{AS}$  of [26]. It is worth noting, however, that the tail-less structure does not offer a CMRR and PSRR as high as tailed ones, but the values are still acceptable and comparable with other solutions.

J. Low Power Electron. Appl. **2023**, 13, 24

**Table 7.** Comparison with others Sub-1 V experimentally tested OTAs.

| Ref.                                  | [5]   | [16]  | [15]   | [6]   | [18]   | [7]   | [19]    | [9]   | [20]   | [21]   | [22]    | [23]    | [24]    | [26]                 | [28]                | [27]                 | This Work            |

|---------------------------------------|-------|-------|--------|-------|--------|-------|---------|-------|--------|--------|---------|---------|---------|----------------------|---------------------|----------------------|----------------------|

| Year                                  | 2005  | 2007  | 2007   | 2012  | 2013   | 2014  | 2015    | 2016  | 2016   | 2018   | 2020    | 2020    | 2020    | 2022                 | 2022                | 2023                 | 2023                 |

| Technology (µm)                       | 0.18  | 0.35  | 0.35   | 0.18  | 0.35   | 0.18  | 0.065   | 0.18  | 0.18   | 0.18   | 0.18    | 0.18    | 0.065   | 0.18                 | 0.18                | 0.13                 | 0.18                 |

| Area (mm²)                            | 17    | 0.06  | 0.0532 | 0.057 | 0.1575 | 0.057 | 0.00495 | 0.036 | 0.0198 | 0.0082 | 0.0085  | 0.0098  | 0.002   | $8.66 \cdot 10^{-4}$ | $7.9 \cdot 10^{-3}$ | $2.34 \cdot 10^{-3}$ | $1.33 \cdot 10^{-3}$ |

| Supply (V)                            | 0.5   | 0.6   | 1      | 0.8   | 1      | 0.5   | 0.5     | 0.5   | 0.7    | 0.3    | 0.3     | 0.3     | 0.25    | 0.4                  | 0.4                 | 0.3                  | 0.6                  |

| $C_L$ (pF)                            | 20    | 15    | 17     | 8     | 15     | 30    | 3       | 40    | 20     | 20     | 30      | 30      | 15      | 150                  | 30                  | 35                   | 150                  |

| DC gain (dB)                          | 62    | 69    | 76.2   | 51    | 88     | 70    | 46      | 77    | 57     | 63     | 65      | 98.1    | 70      | 38                   | 60                  | 87                   | 67                   |

| $I_{bias}$ ( $\mu$ A)                 | 150   | 0.9   | 358    | 1.5   | 197    | 0.15  | 366     | 0.14  | 36     | 0.056  | 0.042   | 0.04333 | 0.10400 | 0.08135              | 0.0096              | 0.01019              | 6.17                 |

| Power (µW)                            | 75    | 0.54  | 358    | 1.2   | 197    | 0.075 | 183     | 0.07  | 25.2   | 0.0168 | 0.0126  | 0.013   | 0.026   | 0.03254              | 0.024               | 0.03373              | 3.70                 |

| GBW (MHz)                             | 10    | 0.011 | 8.1    | 0.057 | 11.67  | 0.018 | 38      | 0.004 | 3      | 0.0028 | 0.00296 | 0.0031  | 0.0095  | 0.00556              | 0.007               | 0.0103               | 0.3503               |

| <i>PM</i> (°)                         | 60    | 65    |        | 60    | 66     | 55    | 57      | 56    | 60     | 61     | 52      | 54      | 88      | 79                   | 60                  | 58                   | 69                   |

| SR (V/μs) <sup>a</sup>                | 2     | 0.015 | 3.88   | 0.14  | 1.95   | 0.003 | 43      | 0.002 | 2.8    | 0.0071 | 0.00415 | 0.0091  | 0.002   | 0.0074               | 0.079               | 0.00374              | 2.45                 |

| CMRR (dB)                             | 65    | 74.5  | 70.5   | 65    | 40     | -     | 35      | 55    | 19     | 72     | 110     | 60      | 62.5    | 36                   | 85                  | 58                   | 45.4                 |

| PSRR (dB)                             | 43    | _     | 45     | _     | 40     | _     | 37      | 52    | 52     | 62     | 56      | 61      | 38      | 30                   | 76                  | 47                   | 50.8                 |

| Op. mode <sup>b</sup>                 | GD    | BD    | BD     | GD    | BD     | GD    | BD      | GD    | BD     | BD     | BD      | BD      | BD      | BD                   | BD                  | BD                   | BD                   |

| Stage #                               | 2     | 2     | 1      | 1     | 2      | 2     | 3       | 2     | 3      | 2      | 2       | 3       | 3       | 1                    | 2                   | 3                    | 2                    |

| $IFOM_S$                              | 1.33  | 0.18  | 0.38   | 0.30  | 0.89   | 3.60  | 0.31    | 1.14  | 1.67   | 1.00   | 2.11    | 2.15    | 1.37    | 10.25                | 3.50                | 3.21                 | 7.42                 |

| $(MHz \cdot pF/\mu A)$                | 1.55  | 0.10  | 0.50   | 0.50  | 0.09   | 3.00  | 0.51    | 1.14  | 1.07   | 1.00   | 2.11    | 2.13    | 1.57    | 10.23                | 3.30                | 3.21                 | 7.42                 |

| $IFOM_L$                              | 0.27  | 0.25  | 0.18   | 0.75  | 0.15   | 0.60  | 0.35    | 0.57  | 1.56   | 2.54   | 2.96    | 6.30    | 0.29    | 13.64                | 39.50               | 1.16                 | 59.56                |

| ((V/μs)·pF/μA)                        | 0.27  | 0.23  | 0.10   | 0.75  | 0.13   | 0.00  | 0.55    | 0.57  | 1.50   | 2.54   | 2.70    | 0.50    | 0.27    | 13.04                | 37.30               | 1.10                 | 37.30                |

| $IFOM_{AS}$                           | 78.43 | 3.06  | 7.23   | 5.33  | 5.64   | 63.16 | 62.92   | 31.75 | 84.18  | 121.95 | 248.74  | 219.00  | 685.10  | 11,838.33            | 443.04              | 1372.89              | 5584.80              |

| $(MHz \cdot pF/\mu A \cdot mm^2)$     | 70.40 | 5.00  | 1.20   | 5.55  | J.UI   | 00.10 | 02.72   | 51.75 | 04.10  | 121.70 | 210.71  | 217.00  | 000.10  | 11,000.00            | 110.01              | 10, 2.0)             | 5504.00              |

| $IFOM_{AL}$                           | 15.69 | 4.17  | 3.46   | 13.10 | 0.94   | 10.53 | 71.20   | 15.87 | 78.56  | 309.23 | 348.74  | 642.86  | 144.23  | 15,745.41            | 5000.00             | 497.54               | 44,817.46            |

| $((V/\mu s)\cdot pF/\mu A\cdot mm^2)$ | 10.07 | 1.17  | 0.10   | 10.10 | 0.71   | 10.00 | , 1.20  | 10.07 | 75.50  | 307.20 | 010.74  | 012.00  | 111.20  | 10,, 10.11           | 2000.00             | 177.01               | 11,017.10            |

<sup>&</sup>lt;sup>a</sup> average value; <sup>b</sup> GD: gate drive, BD: bulk driven.

### 5. Conclusions

In this paper, a two-stage OTA exploiting local positive feedback, a non-tailed differential pair, and a class AB second stage are discussed, analyzed, and experimentally tested. A comparison with the state-of-the-art reveals that the proposed solution is suitable for area-constrained low-voltage low-power applications such as battery-less IoT nodes.

**Author Contributions:** Conceptualization, A.D.G.; methodology, A.D.G. and S.P.; data curation, A.B. and A.D.G.; writing—original draft preparation, A.D.G.; writing—review and editing, A.D.G. and S.P.; visualization, A.B.; supervision, A.D.G. and S.P. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work has been funded by European Union (NextGeneration EU), through the MUR-PNRR project SAMOTHRACE (ECS00000022).

Institutional Review Board Statement: Not applicable.

**Informed Consent Statement:** Not applicable.

**Data Availability Statement:** No new data were created or analyzed in this study. Data sharing is not applicable to this article.

**Conflicts of Interest:** The authors declare no conflict of interest.

### References

- 1. Grasso, A.D.; Pennisi, S. Ultra-Low Power Amplifiers for IoT Nodes. In Proceedings of the 2018 25th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018; pp. 497–500.

- 2. Sansen, W. 1.3 Analog CMOS from 5 Micrometer to 5 Nanometer. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–6.

- 3. Vittoz, E.; Fellrath, J. CMOS Analog Integrated Circuits Based on Weak Inversion Operations. *IEEE J. Solid-State Circuits* 1977, 12, 224–231. [CrossRef]

- 4. Comer, D.J.; Comer, D.T. Using the Weak Inversion Region to Optimize Input Stage Design of CMOS Op Amps. *IEEE Trans. Circuits Syst. II Express Briefs* **2004**, *51*, 8–14. [CrossRef]

- 5. Chatterjee, S.; Tsividis, Y.; Kinget, P. 0.5-V Analog Circuit Techniques and Their Application in OTA and Filter Design. *IEEE J. Solid-State Circuits* **2005**, *40*, 2373–2387. [CrossRef]

- 6. Valero Bernal, M.R.; Celma, S.; Medrano, N.; Calvo, B. An Ultralow-Power Low-Voltage Class-AB Fully Differential OpAmp for Long-Life Autonomous Portable Equipment. *IEEE Trans. Circuits Syst. II Express Briefs* **2012**, *59*, 643–647. [CrossRef]

- 7. Magnelli, L.; Amoroso, F.A.; Crupi, F.; Cappuccino, G.; Iannaccone, G. Design of a 75-NW, 0.5-V Subthreshold Complementary Metal–Oxide–Semiconductor Operational Amplifier. *Int. J. Circ. Theor. Appl.* **2014**, 42, 967–977. [CrossRef]

- 8. Grasso, A.D.; Marano, D.; Palumbo, G.; Pennisi, S. Design Methodology of Subthreshold Three-Stage CMOS OTAs Suitable for Ultra-Low-Power Low-Area and High Driving Capability. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2015**, 62, 1453–1462. [CrossRef]

- 9. Qin, Z.; Tanaka, A.; Takaya, N.; Yoshizawa, H. 0.5-V 70-NW Rail-to-Rail Operational Amplifier Using a Cross-Coupled Output Stage. *IEEE Trans. Circuits Syst. II Express Briefs* **2016**, *63*, 1009–1013. [CrossRef]

- 10. Beloso-Legarra, J.; Grasso, A.D.; Lopez-Martin, A.J.; Palumbo, G.; Pennisi, S. Two-Stage OTA With All Subthreshold MOSFETs and Optimum GBW to DC-Current Ratio. *IEEE Trans. Circuits Syst. II Express Briefs* **2022**, *69*, 3154–3158. [CrossRef]

- 11. Ng, K.A.; Xu, Y.P. A Low-Power, High CMRR Neural Amplifier System Employing CMOS Inverter-Based OTAs With CMFB Through Supply Rails. *IEEE J. Solid-State Circuits* **2016**, *51*, 724–737. [CrossRef]

- 12. Lv, L.; Zhou, X.; Qiao, Z.; Li, Q. Inverter-Based Subthreshold Amplifier Techniques and Their Application in 0.3-V DS -Modulators. *IEEE J. Solid-State Circuits* **2019**, *54*, 1436–1445. [CrossRef]

- Centurelli, F.; Della Sala, R.; Scotti, G. A Standard-Cell-Based CMFB for Fully Synthesizable OTAs. J. Low Power Electron. Appl. 2022, 12, 27. [CrossRef]

- 14. Blalock, B.J.; Allen, P.E.; Rincon-Mora, G. Designing 1-V Op Amps Using Standard Digital CMOS Technology. *IEEE Trans. Circuits Syst. II Analog Digit. Signal Process.* **1998**, 45, 769–780. [CrossRef]

- 15. Carrillo, J.M.; Torelli, G.; Perez-Aloe Valverde, R.; Duque-Carrillo, J.F. 1-V Rail-to-Rail CMOS OpAmp With Improved Bulk-Driven Input Stage. *IEEE J. Solid-State Circuits* **2007**, 42, 508–517. [CrossRef]

- 16. Ferreira, L.H.C.; Pimenta, T.C.; Moreno, R.L. An Ultra-Low-Voltage Ultra-Low-Power CMOS Miller OTA With Rail-to-Rail Input/Output Swing. *IEEE Trans. Circuits Syst. II Express Briefs* **2007**, *54*, 843–847. [CrossRef]

- 17. Ferreira, L.H.C.; Sonkusale, S.R. A 60-DB Gain OTA Operating at 0.25-V Power Supply in 130-nm Digital CMOS Process. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2014**, *61*, 1609–1617. [CrossRef]

- 18. Zuo, L.; Islam, S.K. Low-Voltage Bulk-Driven Operational Amplifier With Improved Transconductance. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2013**, *60*, 2084–2091. [CrossRef]

- 19. Abdelfattah, O.; Roberts, G.W.; Shih, I.; Shih, Y.C. An Ultra-Low-Voltage CMOS Process-Insensitive Self-Biased OTA With Rail-to-Rail Input Range. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2015**, *62*, 2380–2390. [CrossRef]

- 20. Cabrera-Bernal, E.; Pennisi, S.; Grasso, A.D.; Torralba, A.; Carvajal, R.G. 0.7-V Three-Stage Class-AB CMOS Operational Transconductance Amplifier. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2016**, *63*, 1807–1815. [CrossRef]

- 21. Kulej, T.; Khateb, F. Design and Implementation of Sub 0.5-V OTAs in 0.18-Mm CMOS. *Int. J. Circuit Theory Appl.* **2018**, 46, 1129–1143. [CrossRef]

- 22. Kulej, T.; Khateb, F. A Compact 0.3-V Class AB Bulk-Driven OTA. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 2020, 28, 224–232. [CrossRef]

- 23. Kulej, T.; Khateb, F. A 0.3-V 98-DB Rail-to-Rail OTA in 0.18 mm CMOS. IEEE Access 2020, 8, 27459–27467. [CrossRef]

- 24. Woo, K.-C.; Yang, B.-D. A 0.25-V Rail-to-Rail Three-Stage OTA With an Enhanced DC Gain. *IEEE Trans. Circuits Syst. II Express Briefs* 2020, 67, 1179–1183. [CrossRef]

- 25. Centurelli, F.; Della Sala, R.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A Tree-Based Architecture for High-Performance Ultra-Low-Voltage Amplifiers. *J. Low Power Electron. Appl.* **2022**, *12*, 12. [CrossRef]

- 26. Ballo, A.; Grasso, A.D.; Pennisi, S. 0.4-V, 81.3-NA Bulk-Driven Single-Stage CMOS OTA with Enhanced Transconductance. *Electronics* **2022**, *11*, 2704. [CrossRef]

- 27. Sala, R.D.; Centurelli, F.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A 0.3V Rail-to-Rail Three-Stage OTA With High DC Gain and Improved Robustness to PVT Variations. *IEEE Access* **2023**, *11*, 19635–19644. [CrossRef]

- 28. Akbari, M.; Hussein, S.M.; Hashim, Y.; Tang, K.-T. 0.4-V Tail-Less Quasi-Two-Stage OTA Using a Novel Self-Biasing Transconductance Cell. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2022**, *69*, 2805–2818. [CrossRef]

- 29. Roh, J.; Byun, S.; Choi, Y.; Roh, H.; Kim, Y.-G.; Kwon, J.-K. A 0.9-V 60-mW 1-Bit Fourth-Order Delta-Sigma Modulator With 83-DB Dynamic Range. *IEEE J. Solid-State Circuits* **2008**, 43, 361–370. [CrossRef]

- 30. Carrillo, J.M.; Torelli, G.; Duque-Carrillo, J.F. Transconductance Enhancement in Bulk-Driven Input Stages and Its Applications. *Analog. Integr. Circuits Signal Process.* **2011**, *68*, 207–217. [CrossRef]

- 31. Ballo, A.; Grasso, A.D.; Pennisi, S. Active Load with Cross-Coupled Bulk for High-Gain High-CMRR Nanometer CMOS Differential Stages. *Int. J. Circuit Theory Appl.* **2019**, 47, 1700–1704. [CrossRef]

- 32. Ramirez-Angulo, J.; Carvajal, R.G.; Galan, J.A.; Lopez-Martin, A. A Free but Efficient Low-Voltage Class-AB Two-Stage Operational Amplifier. *IEEE Trans. Circuits Syst. II Express Briefs* **2006**, *53*, 568–571. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.