Digital Controller Design Based on Active Damping Method of Capacitor Current Feedback for Auxiliary Resonant Snubber Inverter with LC Filter

Abstract

:1. Introduction

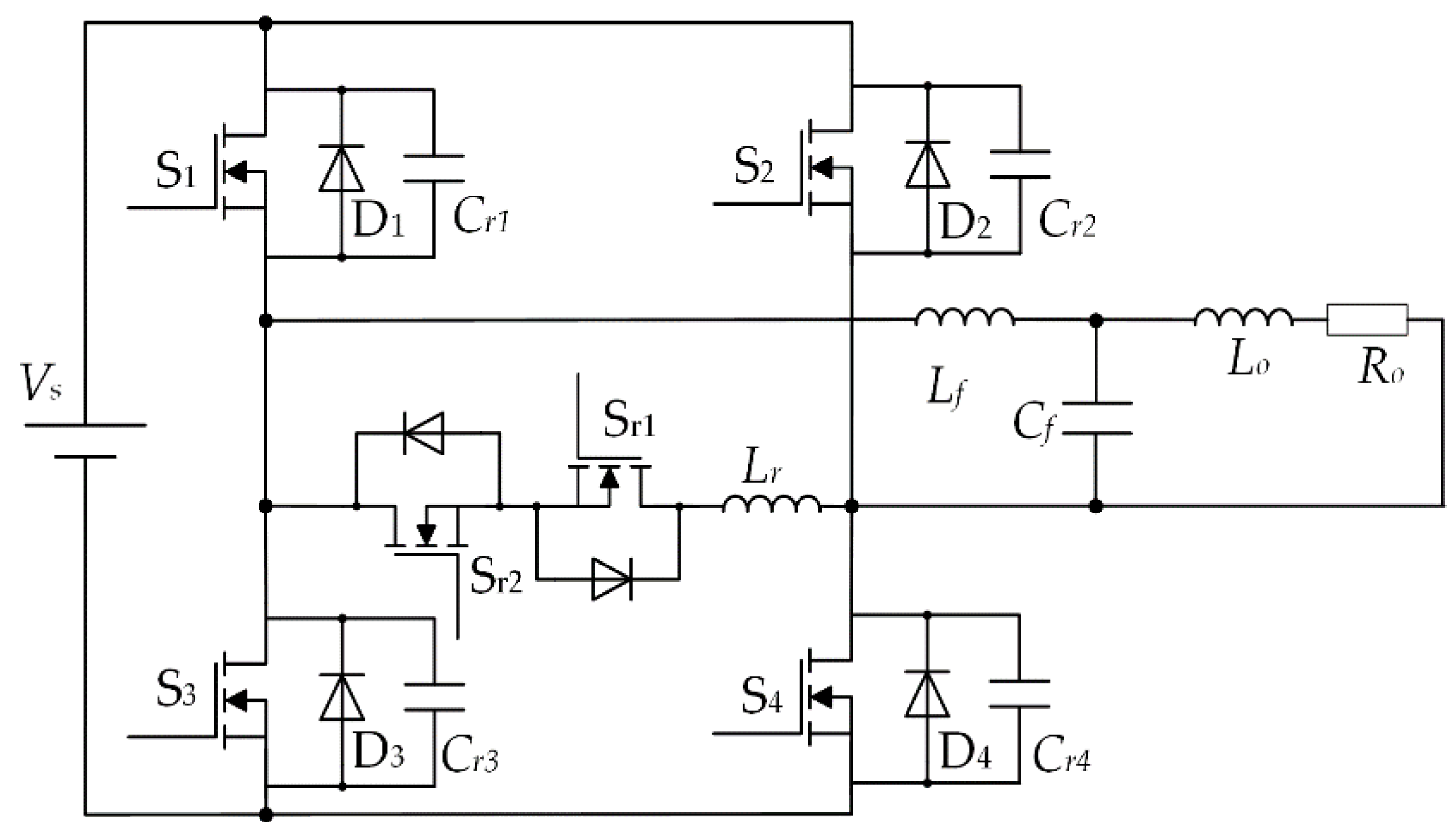

2. Control of the ARSI

3. The Load Adaptive Auxiliary Current Control

3.1. Principle

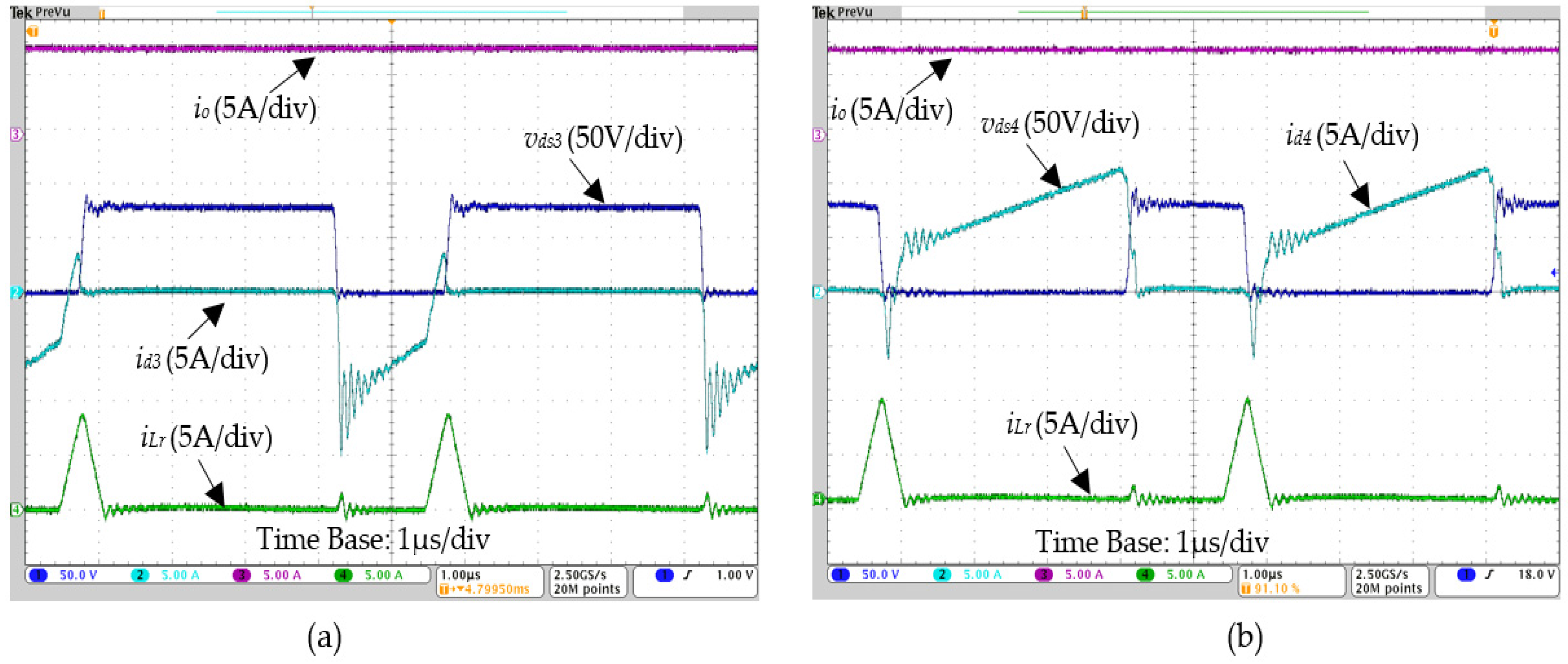

3.2. Limitation of the Duty Ratio

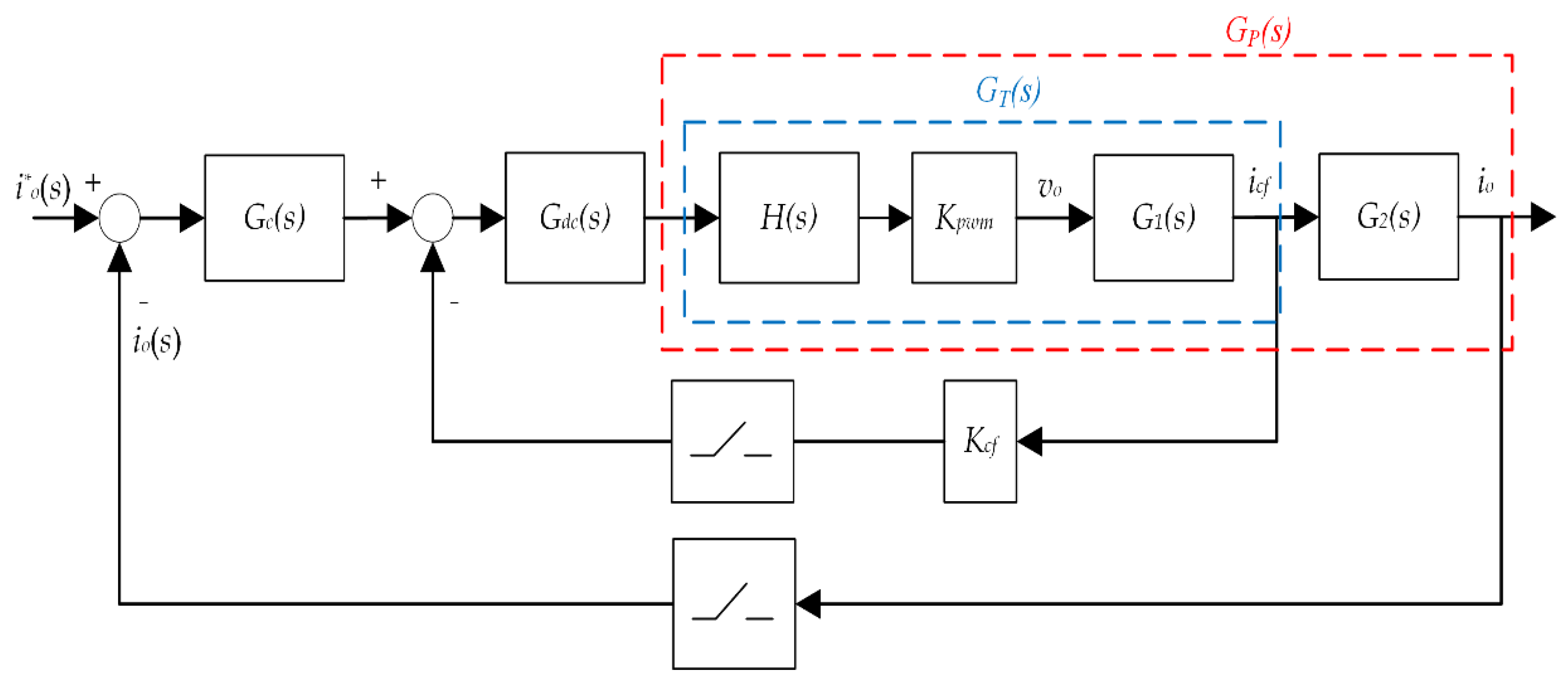

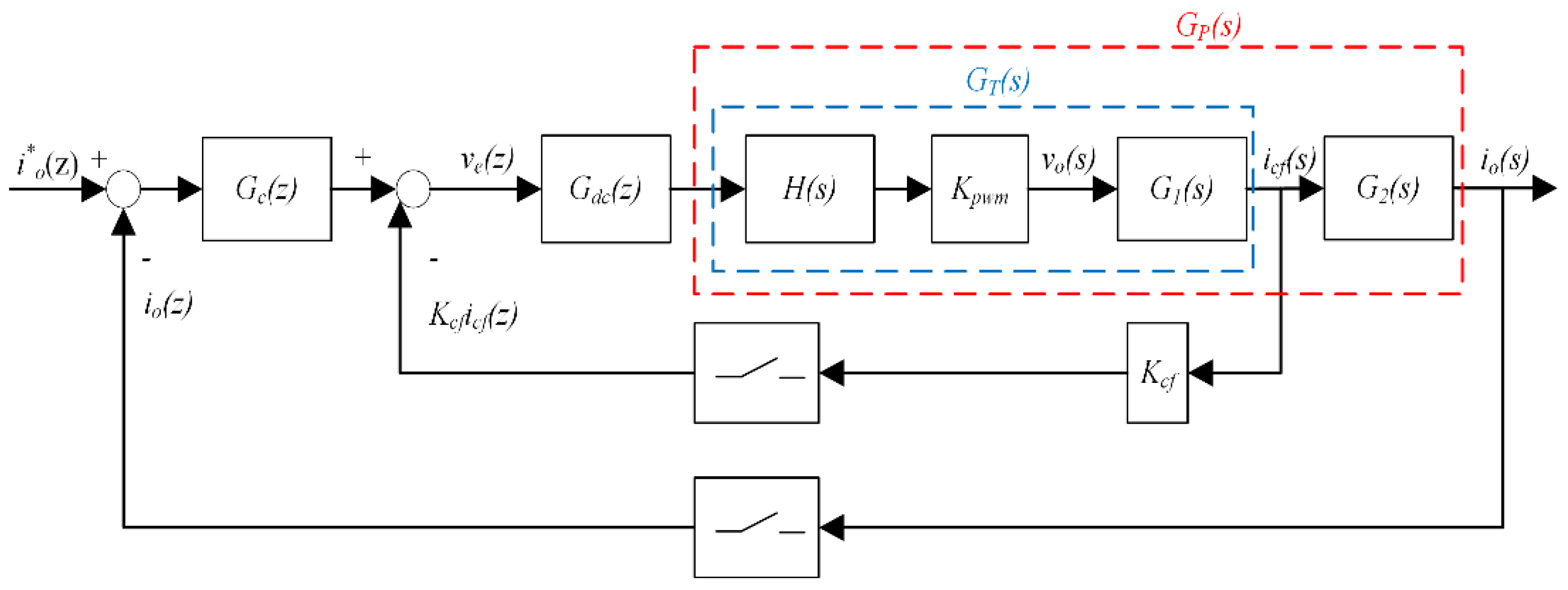

4. Output Current Control

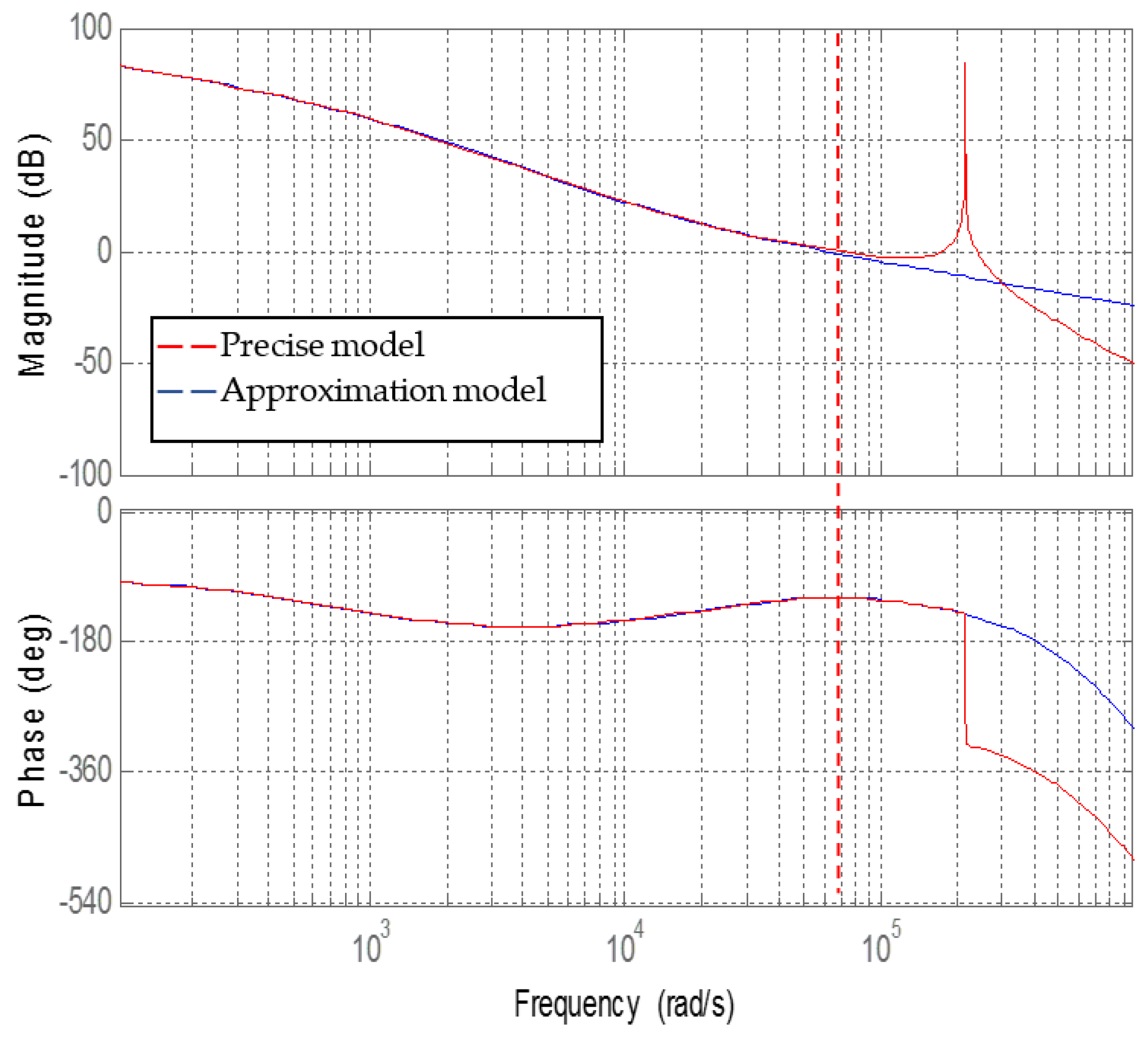

4.1. The Model of the ARSI

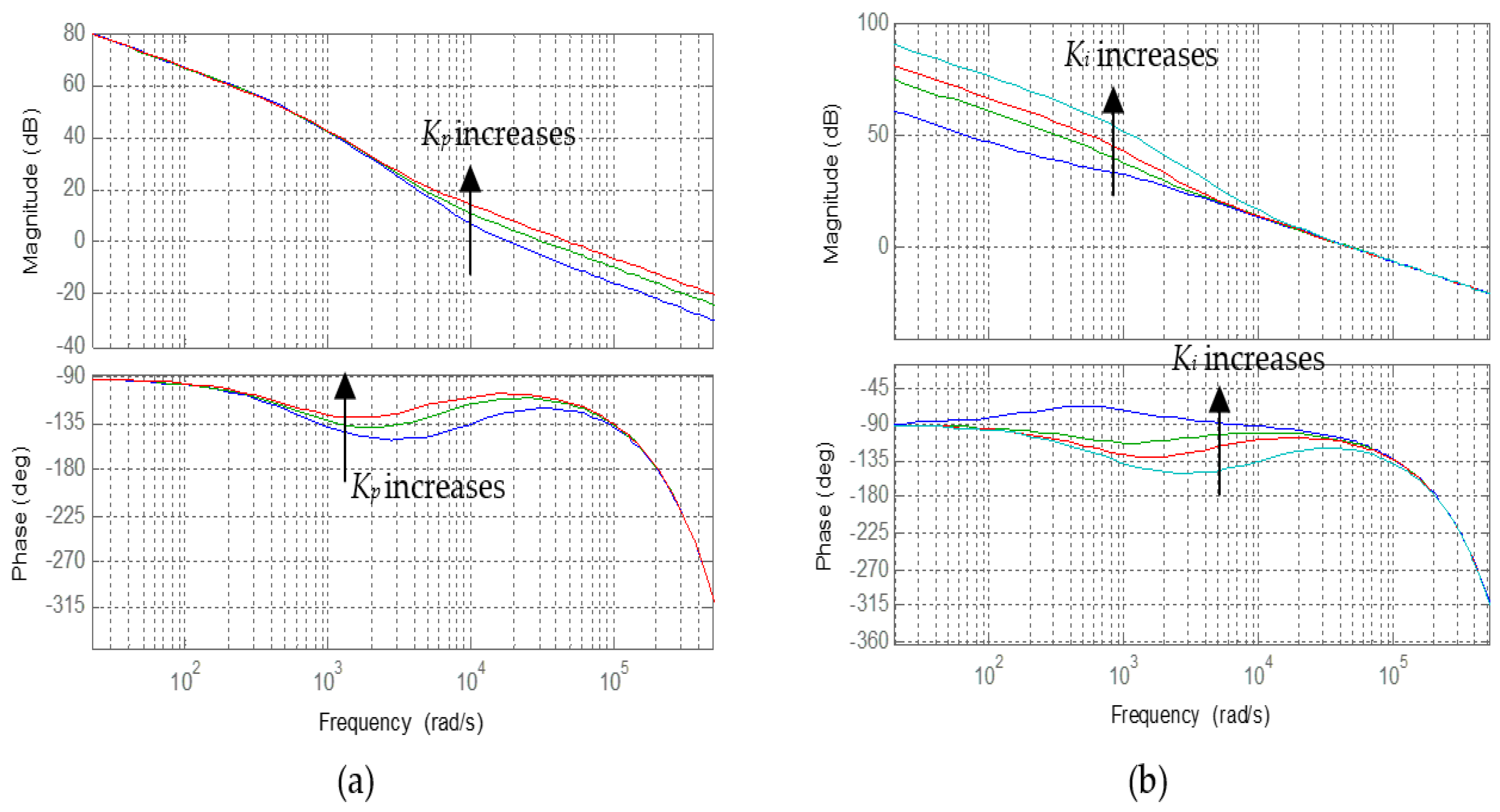

4.2. PI Controller Design

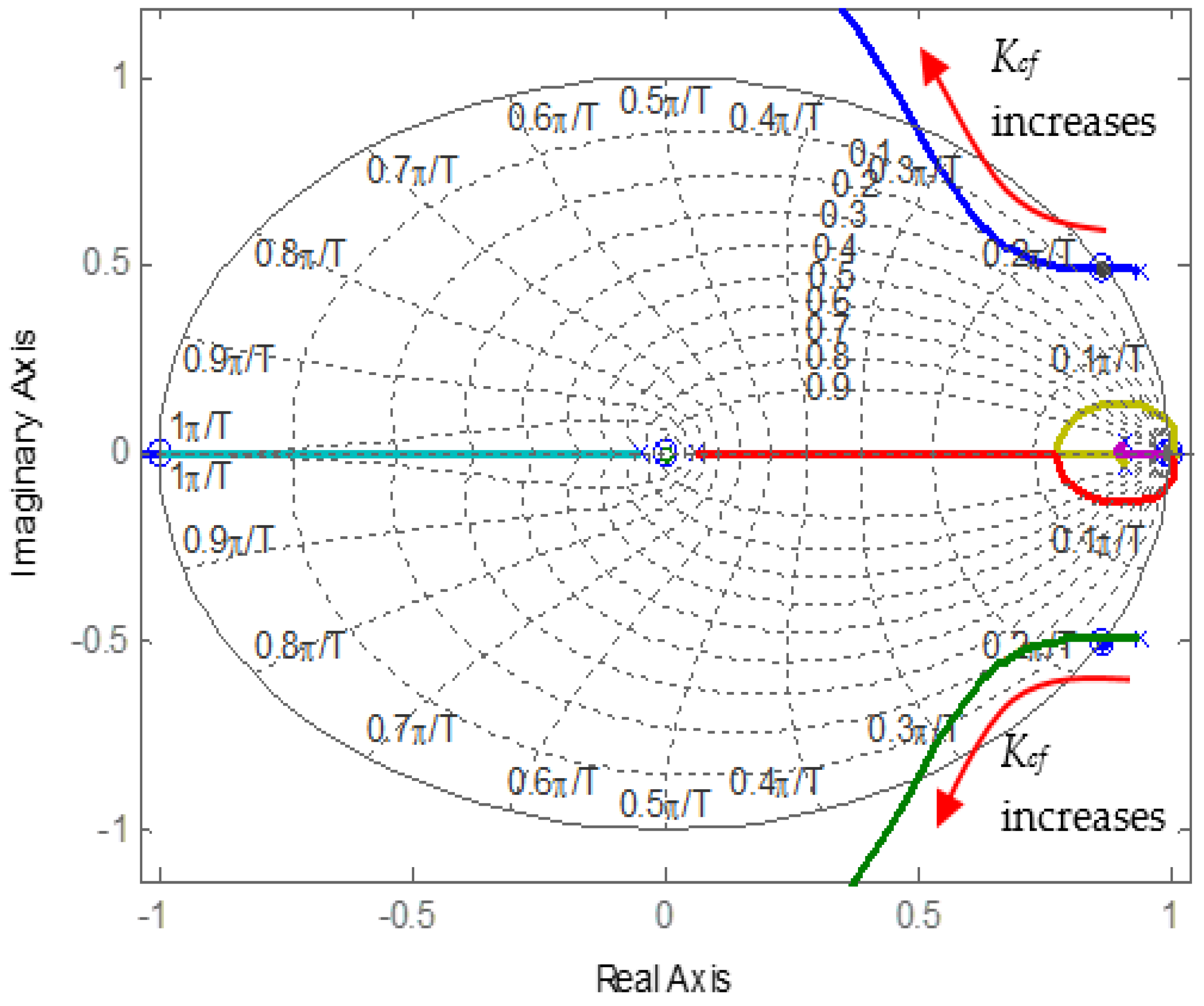

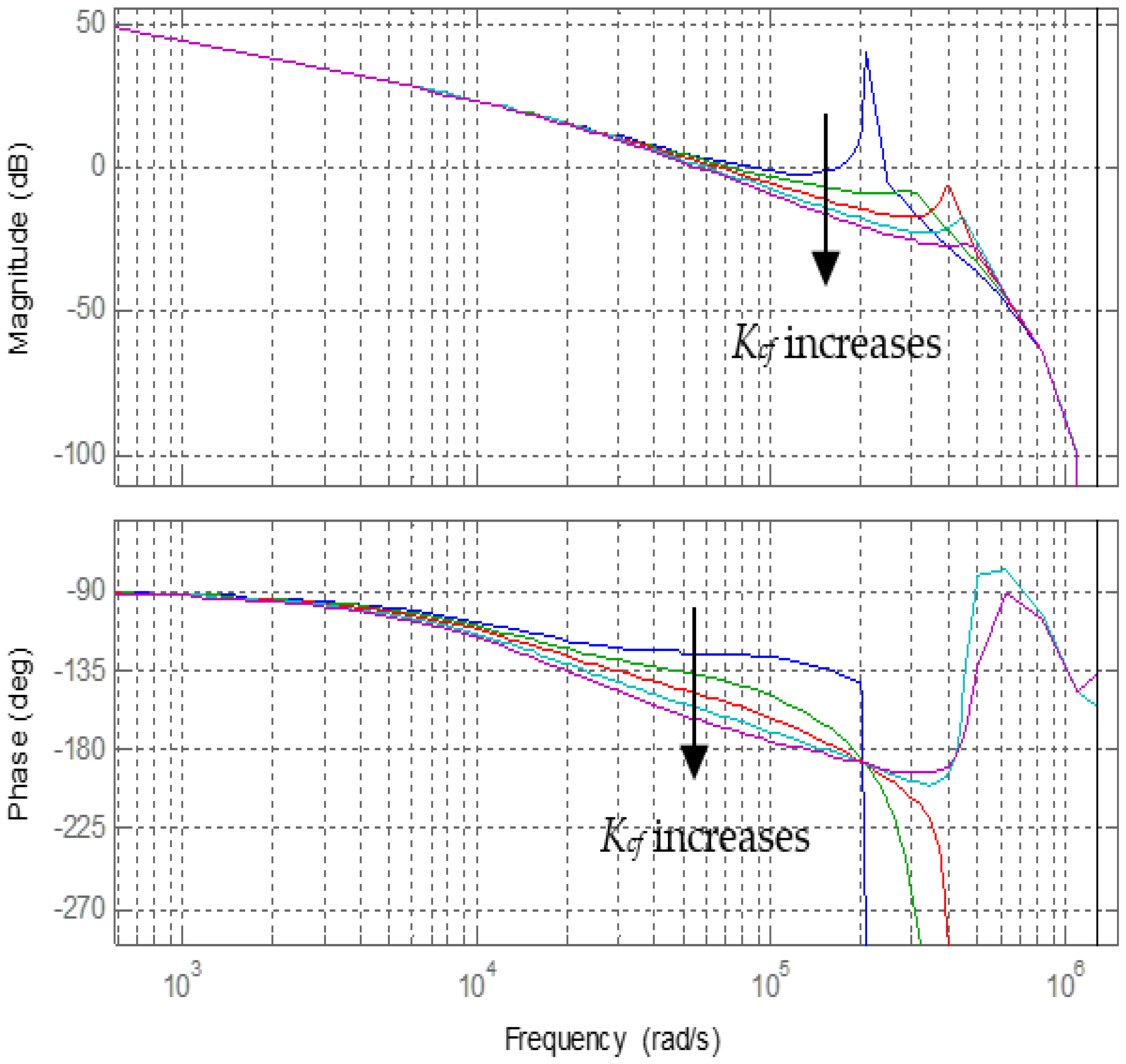

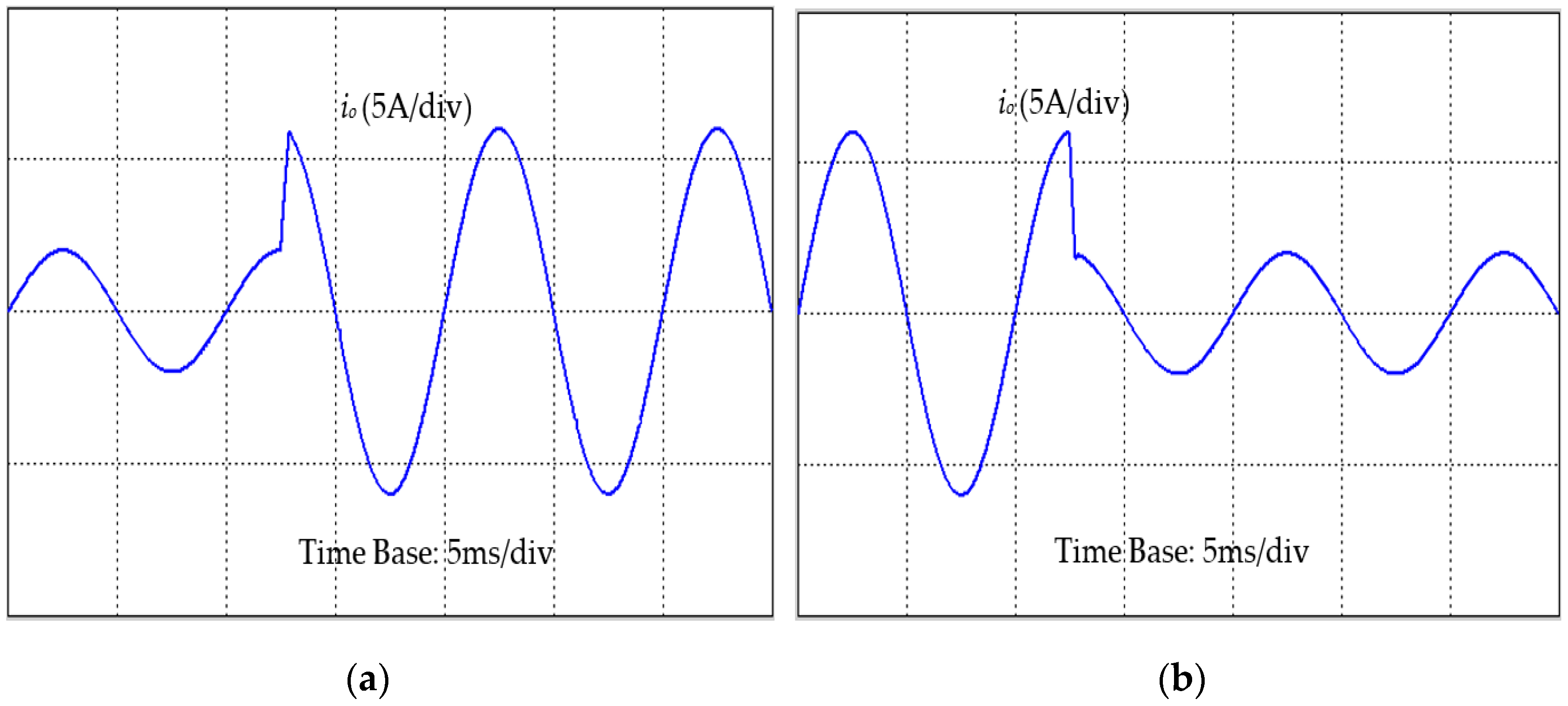

4.3. Capacitor Current Feedback Design

5. Design Example

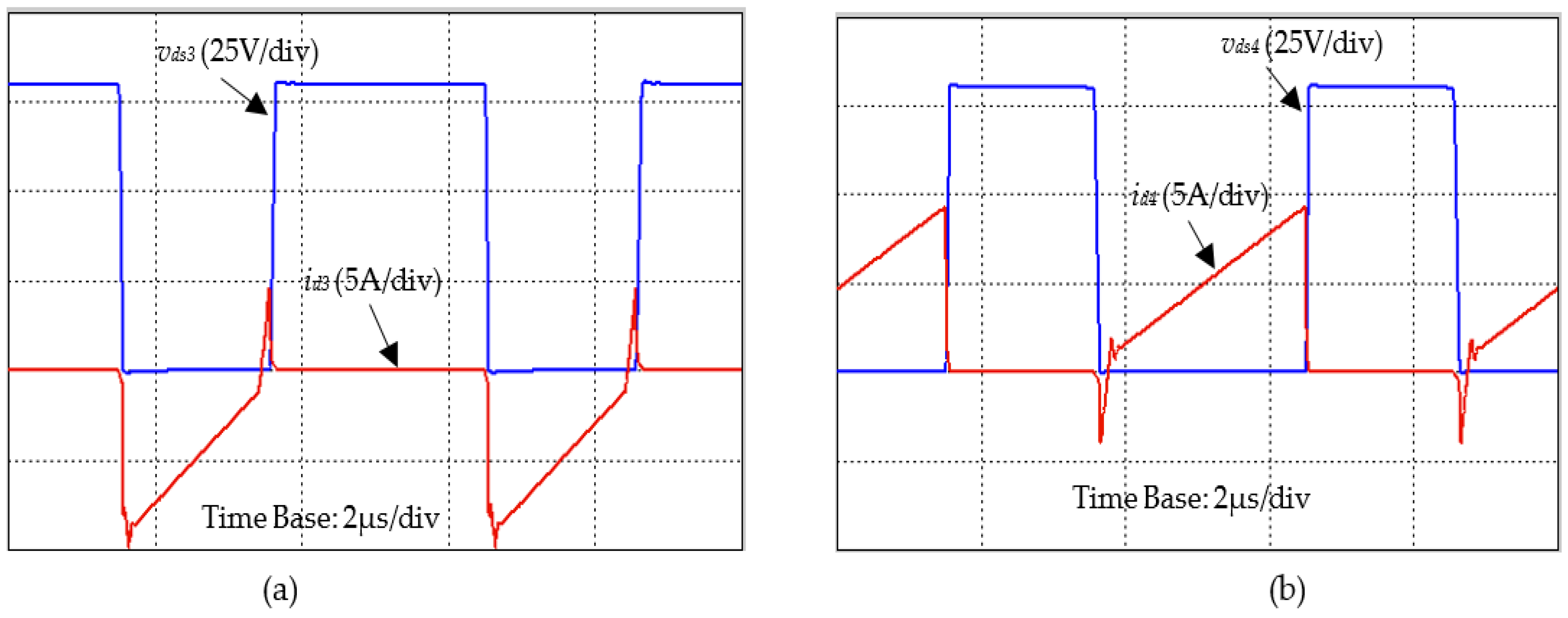

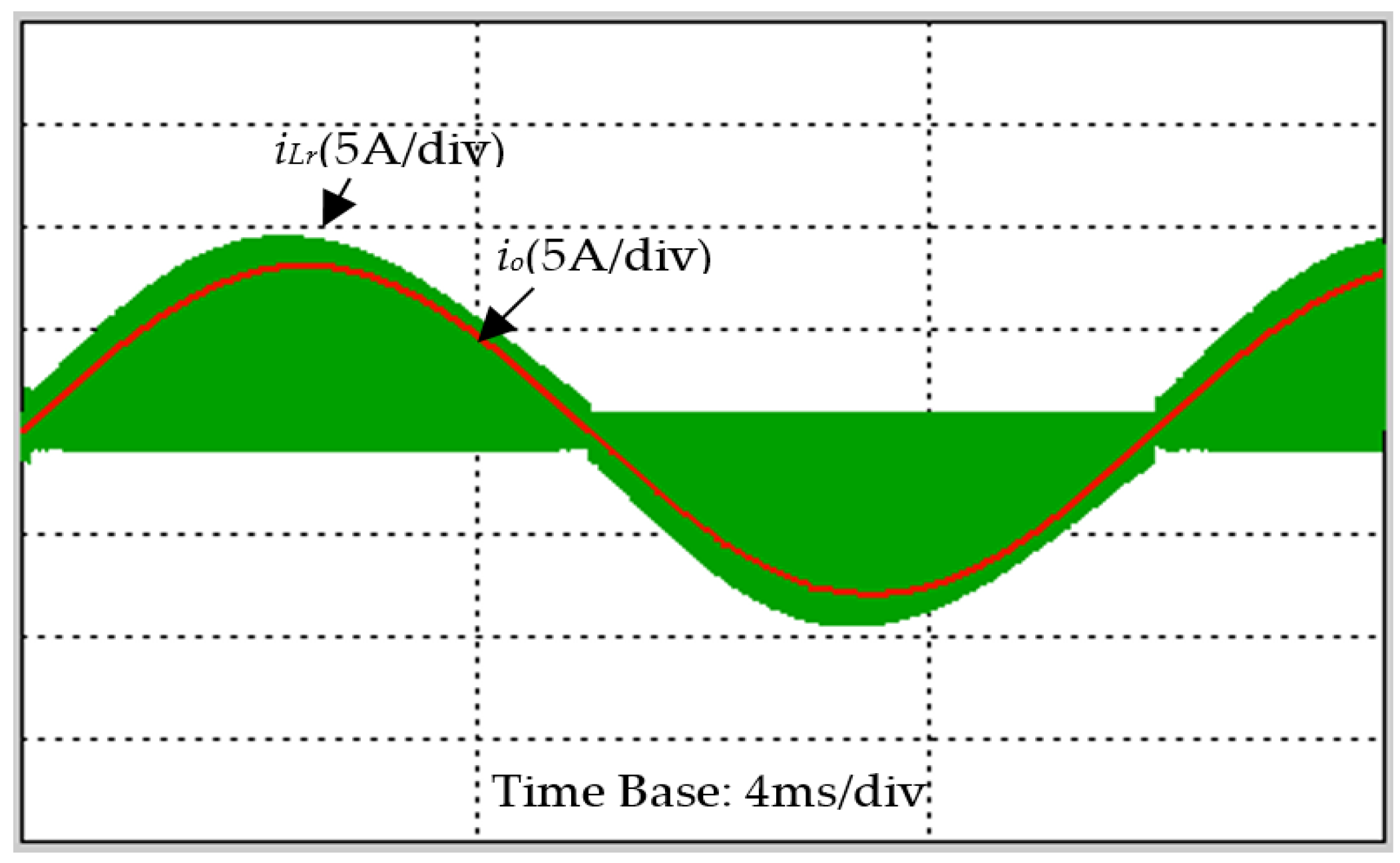

6. Simulations and Experiments

7. Conclusions

- (1)

- An improved loading scheme that the data is updating at the upper limit and lower limit of the carrier is proposed to improve the maximum duty ratio.

- (2)

- The filter capacitor current feedback is introduced to damp the resonance caused by the LC filter.

- (3)

- A step-by-step digital controller design method, including the auxiliary current controller and the output PI controller, is proposed, in which the computation and transport delay is considered.

Acknowledgments

Author Contributions

Conflicts of Interest

Appendix A

Appendix B

References

- Schmidt, R.M.; Schitter, G.; Eijk, J. The Design of High Performance Mechatronics; Delft University Press: Amsterdam, The Netherlands, 2011; pp. 438–444. [Google Scholar]

- Charalambous, A.; Yuan, X.; McNeill, N.; Yan, Q.Z. EMI reduction with a soft-switched auxiliary commutated pole inverter. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Montreal, QC, Canada, 20–24 Septemper 2015; pp. 2650–2657.

- Beltrame, R.C.; Rakoski Zientarski, J.R.; da Silva Martins, M.L.; Pinheiro, J.R.; Hey, H.L. Simplified zero-voltage-rransition circuits applied to bidirectional poles: Concept and synthesis methodology. IEEE Trans. Power Electron. 2011, 26, 1765–1776. [Google Scholar] [CrossRef]

- Russi, J.L.; da Silva Martins, M.L.; Schuch, L.; Pinheiro, J.R.; Hey, H.L. Synthesis methodology for multipole ZVT converters. IEEE Trans. Ind. Electron. 2007, 54, 1783–1795. [Google Scholar] [CrossRef]

- McMurray, W. Resonant snubbers with auxiliary switches. IEEE Trans. Ind. Appl. 1993, 29, 355–362. [Google Scholar] [CrossRef]

- DeDonker, R.W.; Lyons, J.P. The auxiliary resonant commutated pole converter. In Proceedings of the Industry Applications Society Annual Meeting, Seattle, WA, USA, 7–12 October 1990; pp. 1228–1235.

- Lai, J.S. Resonant snubber-based soft-switching inverters for electric propulsion drives. IEEE Trans. Ind. Electron. 1997, 44, 71–80. [Google Scholar]

- Lai, J.S.; Young, R.W.; Ott, G.W.; McKeever, J.W.; Peng, F.Z. A delta-configured auxiliary resonant snubber inverter. IEEE Trans. Ind. Appl. 1996, 32, 518–525. [Google Scholar]

- Yuan, X.; Barbi, I. Analysis, designing, and experimentation of a transformer-assisted PWM zero-voltage switching pole inverter. IEEE Trans. Power Electron. 2000, 15, 950–950. [Google Scholar]

- Russi, J.L.; da Silva Martins, M.L.; Hey, H.L. Coupled-filter-inductor soft-switching techniques: Principles and topologies. IEEE Trans. Ind. Electron. 2008, 55, 3361–3373. [Google Scholar] [CrossRef]

- Yu, W.; Lai, J.; Park, S. An improved zero-voltage switching inverter using two coupled magnetics in one resonant pole. IEEE Trans. Power Electron. 2010, 25, 952–961. [Google Scholar]

- Hanigovszki, N.; Poulsen, J.; Blaabjerg, F. A Novel Output Filter Topology to Reduce Motor Overvoltage. IEEE Trans. Ind. Appl. 2004, 40, 845–852. [Google Scholar] [CrossRef]

- Wu, W.; He, Y.; Tang, T.; Blaabjerg, F. A New Design Method for the Passive Damped LCL and LLCL Filter-Based Single-Phase Grid-Tied Inverter. IEEE Trans. Ind. Electron. 2013, 60, 4339–4350. [Google Scholar] [CrossRef]

- Balasubramanian, A.K.; John, V. Analysis and design of split-capacitor resistive-inductive passive damping for LCL filters in grid-connected inverters. IET Power Electron. 2013, 6, 1822–1832. [Google Scholar] [CrossRef]

- Xin, Z.; Loh, P.C.; Wang, X.; Blaabjerg, F.; Tang, Y. Highly Accurate Derivatives for LCL-Filtered Grid Converter with Capacitor Voltage Active Damping. IEEE Trans. Power Electron. 2016, 31, 3612–3625. [Google Scholar] [CrossRef]

- Dannehl, J.; Fuchs, F.W.; Hansen, S.; Thøgersen, P.B. Investigation of Active Damping Approaches for PI-Based Current Control of Grid-Connected Pulse Width Modulation Converters with LCL Filters. IEEE Trans. Ind. Appl. 2010, 46, 1509–1517. [Google Scholar] [CrossRef]

- Wagner, M.; Barth, T.; Alvarez, R.; Ditmanson, C.; Bernet, S. Discrete-Time Active Damping of LCL-Resonance by Proportional Capacitor Current Feedback. IEEE Trans. Ind. Appl. 2014, 50, 3911–3920. [Google Scholar] [CrossRef]

- Parker, S.G.; McGrath, B.P.; Holmes, D.G. Regions of Active Damping Control for LCL Filters. IEEE Trans. Ind. Appl. 2014, 50, 424–432. [Google Scholar] [CrossRef]

- Dong, W.; Yu, H.; Lee, F.C.; Lai, J. Generalized concept of load adaptive fixed timing control for zero-voltage-transition inverters. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 4–8 March 2001; pp. 179–185.

- Chan, C.C.; Chau, K.T.; Chan, D.T.W.; Yao, J.; Lai, J.S.; Li, Y. Switching characteristics and efficiency improvement with auxiliary resonant snubber based soft-switching inverters. In Proceedings of the IEEE Power Electronics Specialists Conference, Fukuoka, Japan, 17–22 May 1998; pp. 429–435.

- Kou, B.; Zhang, H.; Jin, Y.; Zhang, H. An Improved Control Scheme for Single-Phase Auxiliary Resonant Snubber Inverter. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference, Hefei, China, 22–26 May 2016; pp. 1259–1263.

- Holmes, D.G.; Lipo, T.A. Pulse Width Modulation for Power Converters: Principles and Practice; IEEE Press: New York, NY, USA, 2003; pp. 105–120. [Google Scholar]

- Kong, W.Y.; Holmes, D.G.; McGrath, B.P. Enhanced Three Phase AC Stationary Frame PI Current Regulators. In Proceedings of the IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 83–90.

- Agorreta, J.L.; Borrega, M.; López, J.; Marroyo, L. Modeling and control of N-paralleled grid-connected inverters with LCL filter coupled due to grid impedance in PV plants. IEEE Trans. Power Electron. 2011, 26, 770–785. [Google Scholar] [CrossRef]

- Buso, S.; Mattavelli, P. Digital Control in Power Electronics; Morgan & Claypool: Seattle, WA, USA, 2006; pp. 13–57. [Google Scholar]

| Switch | iLf_l < −Ir_min | iLf_l > −Ir_min | Switch | iLf_u < Ir_min | iLf_u > Ir_min |

|---|---|---|---|---|---|

| S1 & S4 | NZVS | AZVS (Sr1) | S2 & S3 | AZVS (Sr2) | NZVS |

| Parameter | Value |

|---|---|

| DC voltage Vs | 80 V |

| Switching frequency fs | 200 kHz |

| Dead time tdead | 0.2 μs |

| Load | 3.7 Ω, 4.87 mH |

| Resonant inductor Lr | 2.2 μH |

| Resonant capacitor Cr | 2.7 nF |

| Filter inductor Lf | 22 μH |

| Filter capacitor Cf | 1 μF |

| Maximum output current Io_max | 8 A |

| Parameter | Conventional Loading Scheme | Improved Loading Scheme |

|---|---|---|

| Maximum Duty Ratio Dmax | 0.857 | 0.867 |

| Minimum Duty Ratio Dmin | 0.143 | 0.133 |

| Upper Limit Vupperlimit | 257 | 266 |

| Lower Limit Vlowerlimit | 43 | 34 |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Kou, B.; Zhang, L.; Jin, Y. Digital Controller Design Based on Active Damping Method of Capacitor Current Feedback for Auxiliary Resonant Snubber Inverter with LC Filter. Appl. Sci. 2016, 6, 377. https://doi.org/10.3390/app6110377

Zhang H, Kou B, Zhang L, Jin Y. Digital Controller Design Based on Active Damping Method of Capacitor Current Feedback for Auxiliary Resonant Snubber Inverter with LC Filter. Applied Sciences. 2016; 6(11):377. https://doi.org/10.3390/app6110377

Chicago/Turabian StyleZhang, Hailin, Baoquan Kou, Lu Zhang, and Yinxi Jin. 2016. "Digital Controller Design Based on Active Damping Method of Capacitor Current Feedback for Auxiliary Resonant Snubber Inverter with LC Filter" Applied Sciences 6, no. 11: 377. https://doi.org/10.3390/app6110377