Stacked Integration of MEMS on LSI

Abstract

:1. Introduction

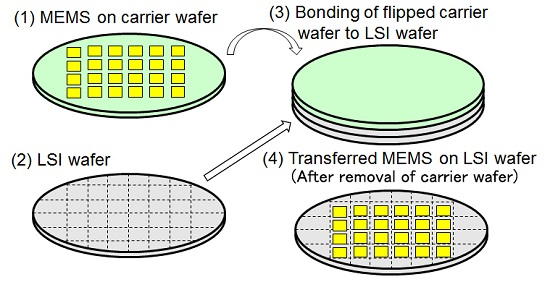

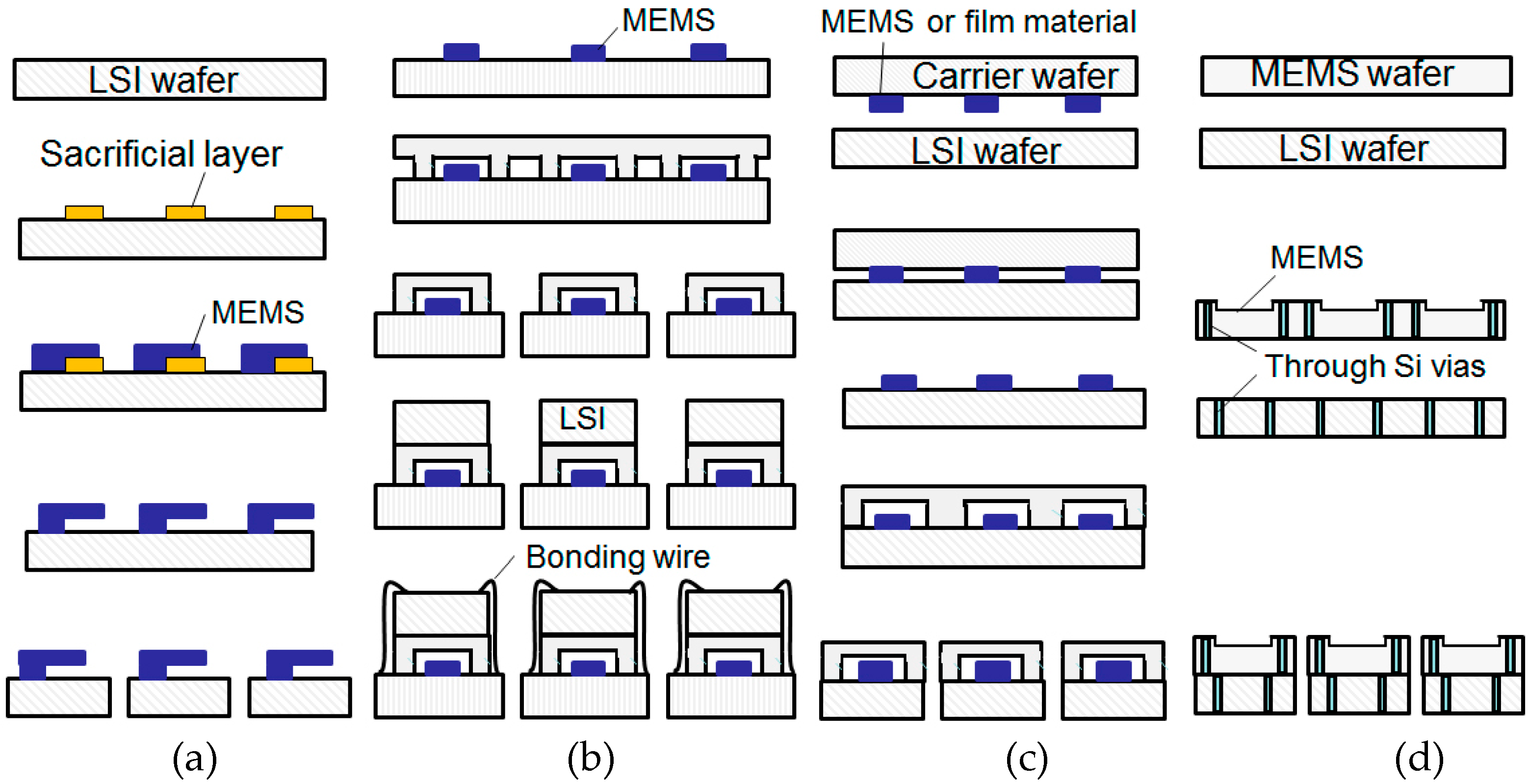

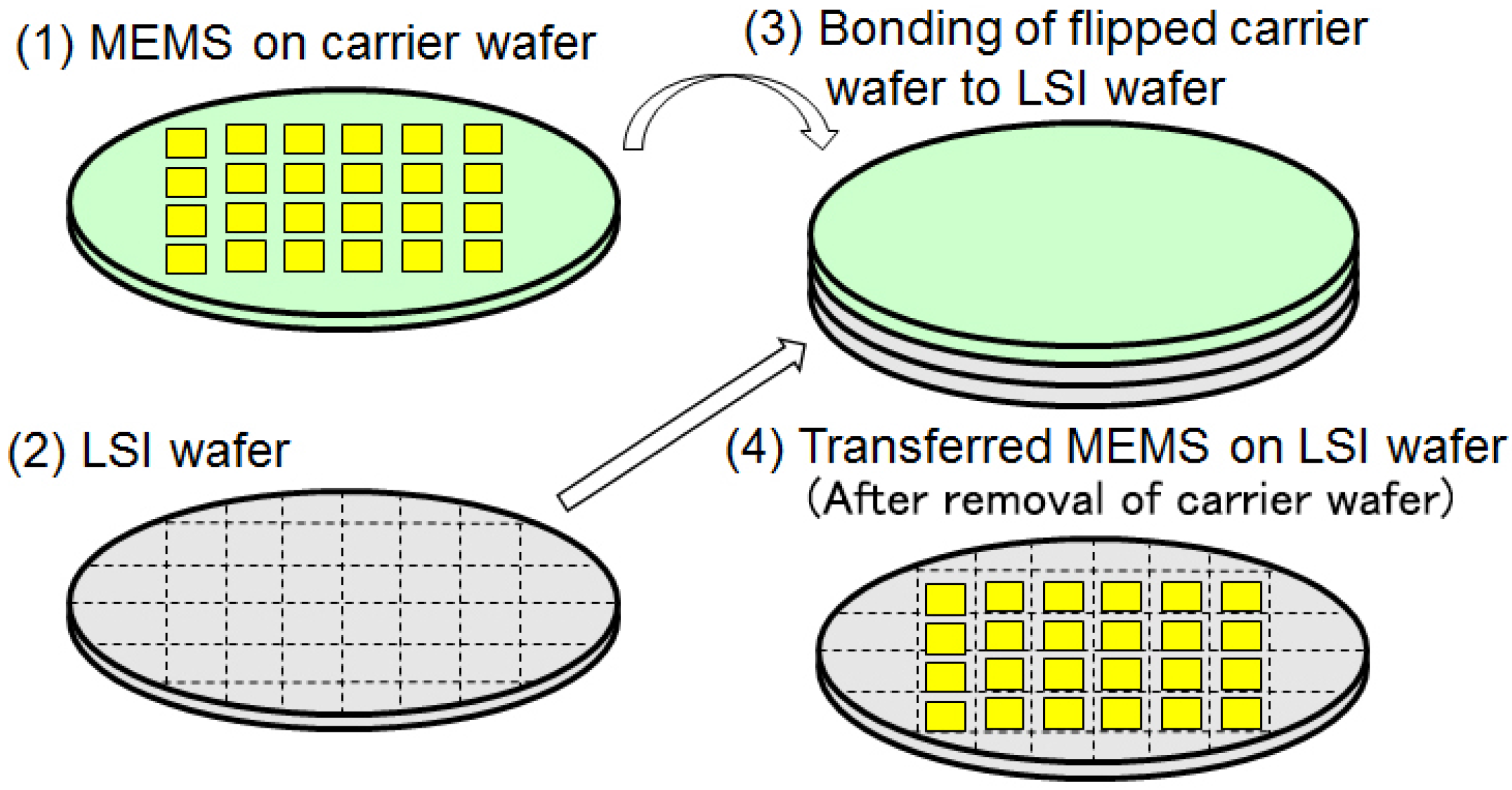

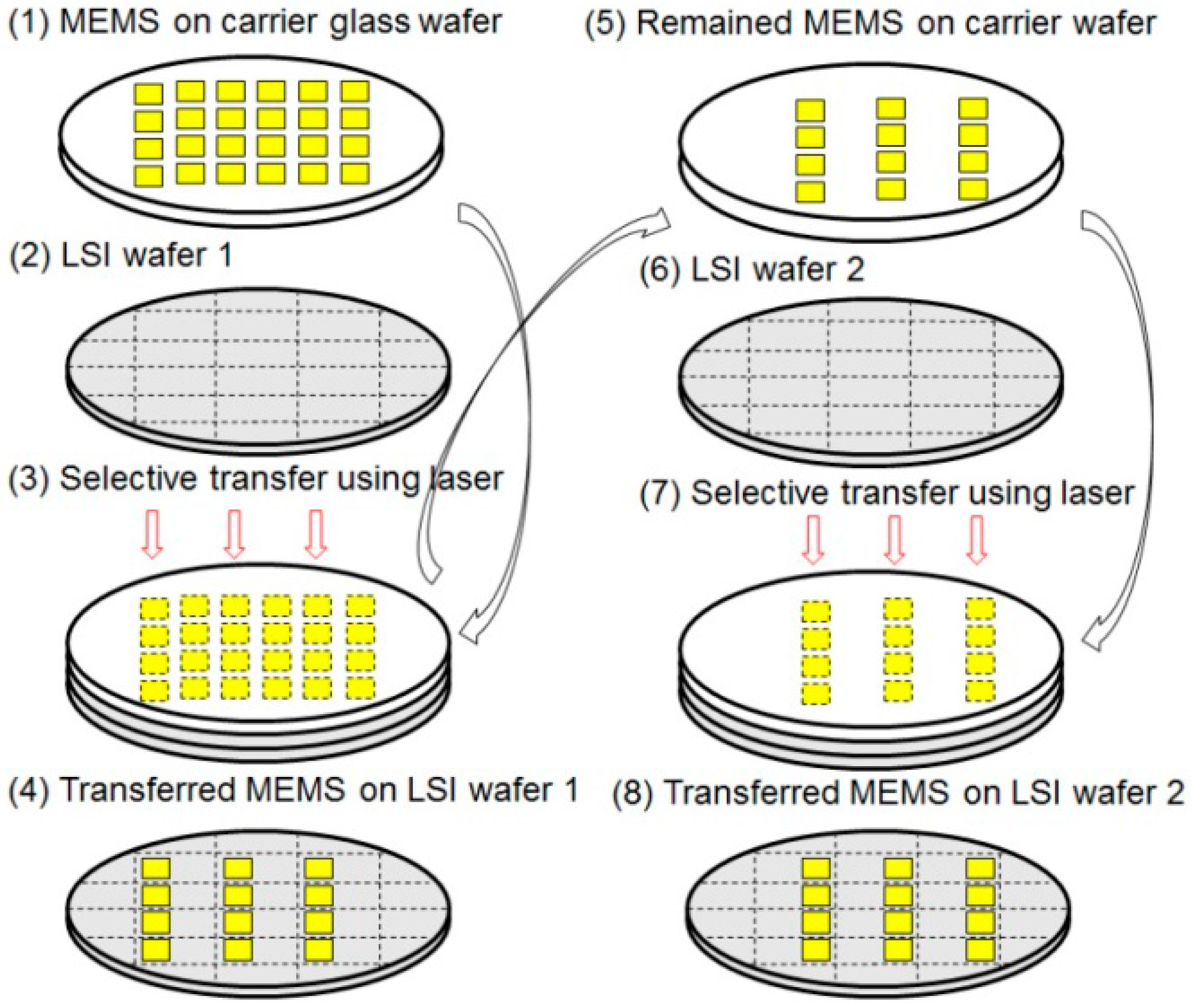

2. Wafer-Level Transfer of MEMS to LSI

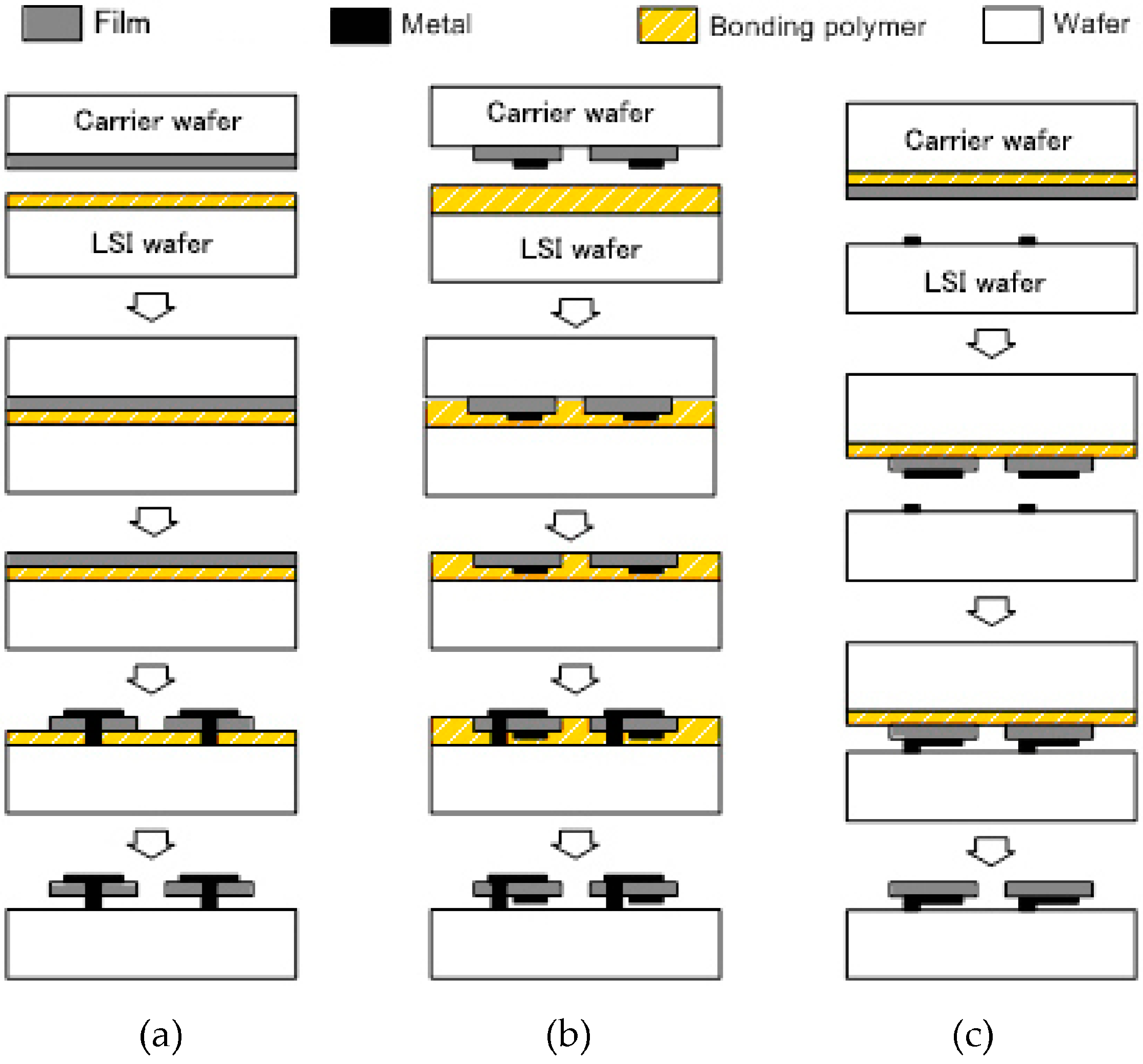

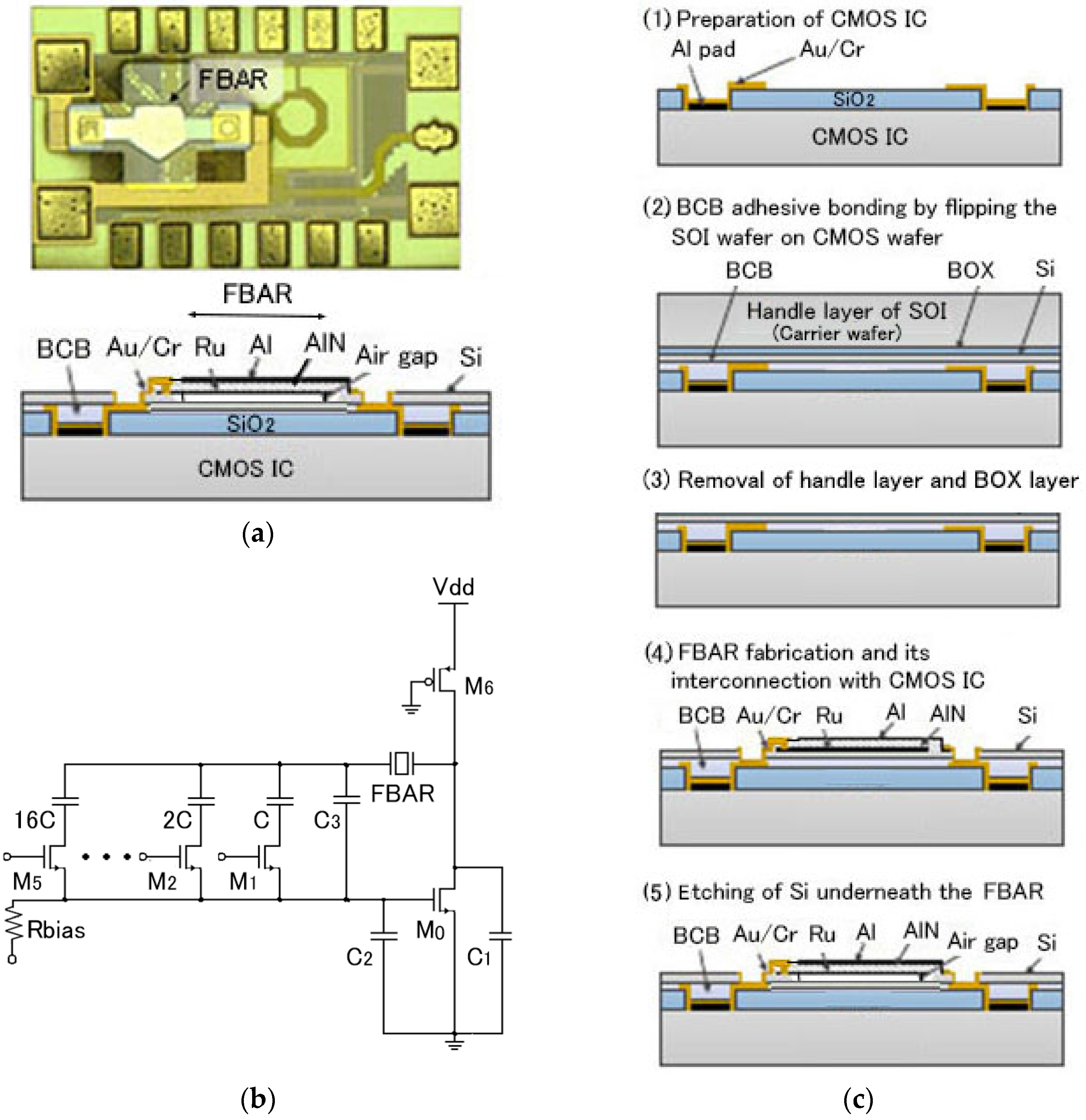

2.1. Film Transfer (Film Bulk Acoustic Resonator on LSI)

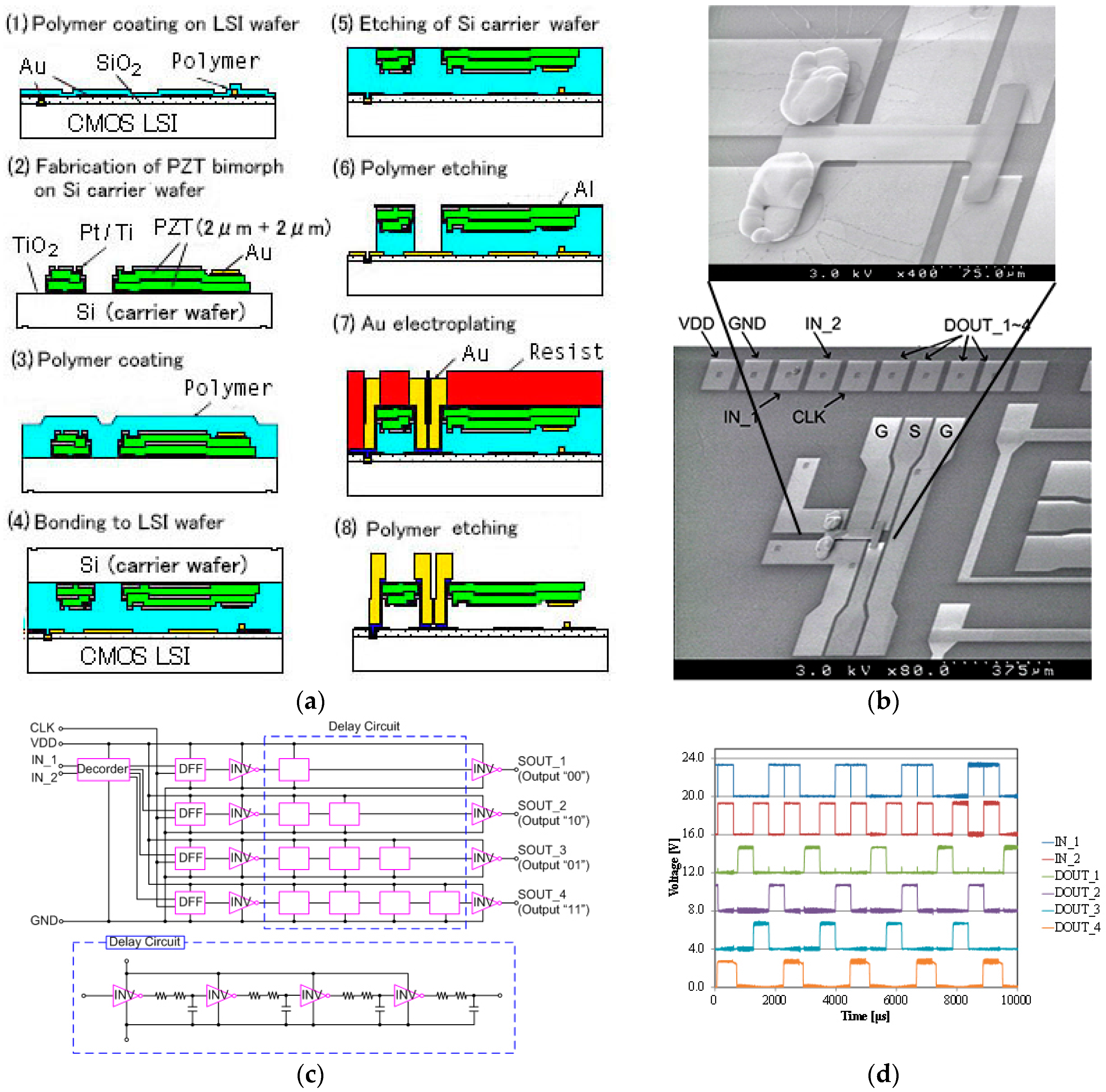

2.2. Device Transfer Connectivity Last (PZT MEMS Switch on LSI)

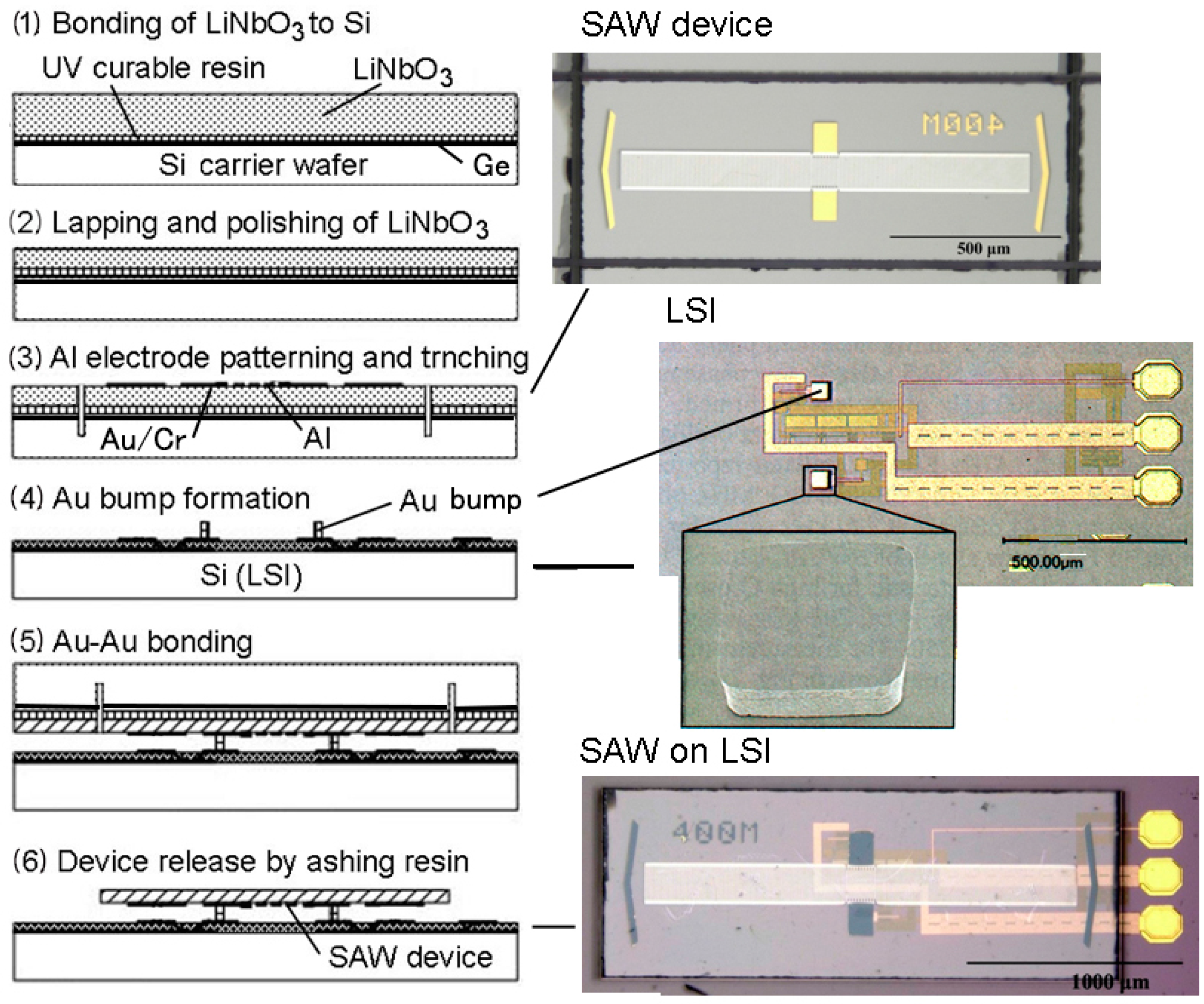

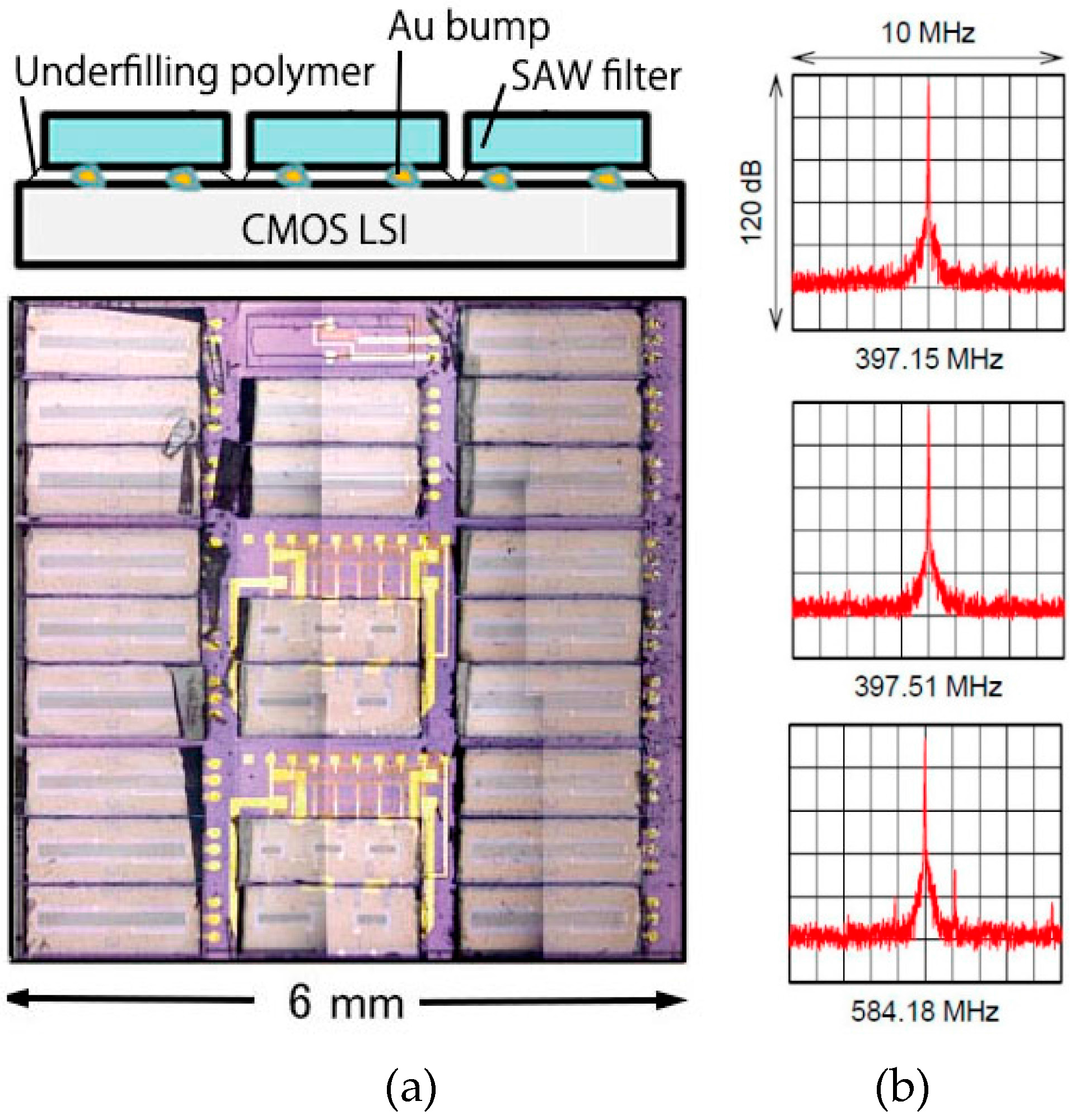

2.3. Immediate Connectivity at Device Transfer (Surface Acoustic Wave Resonator on LSI)

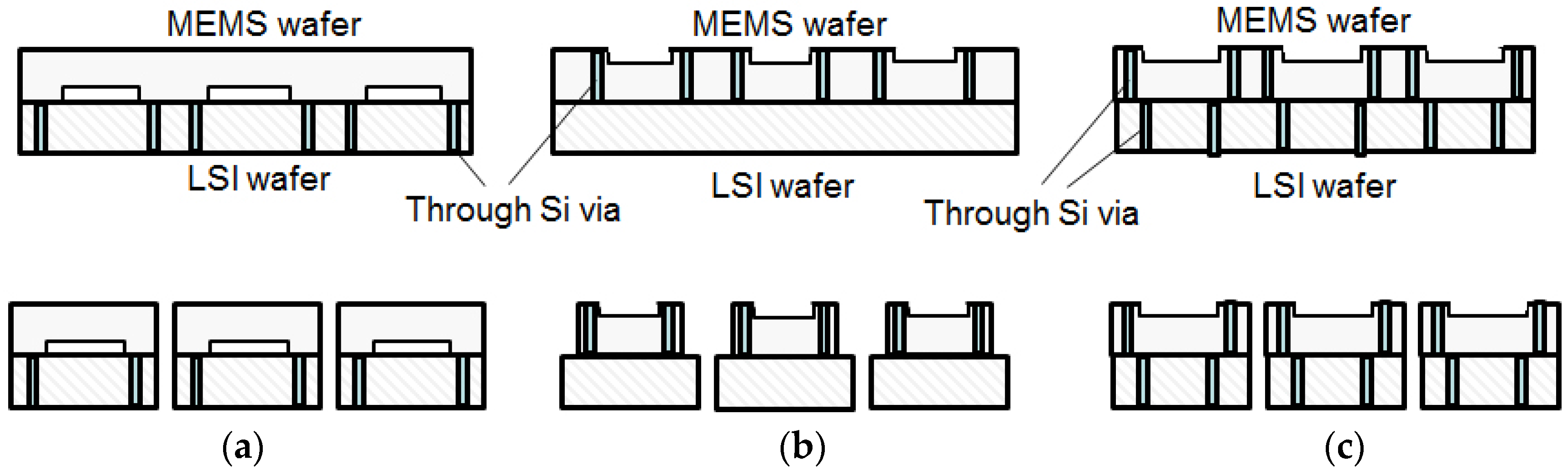

3. Stacked Integration Using through-Si Vias

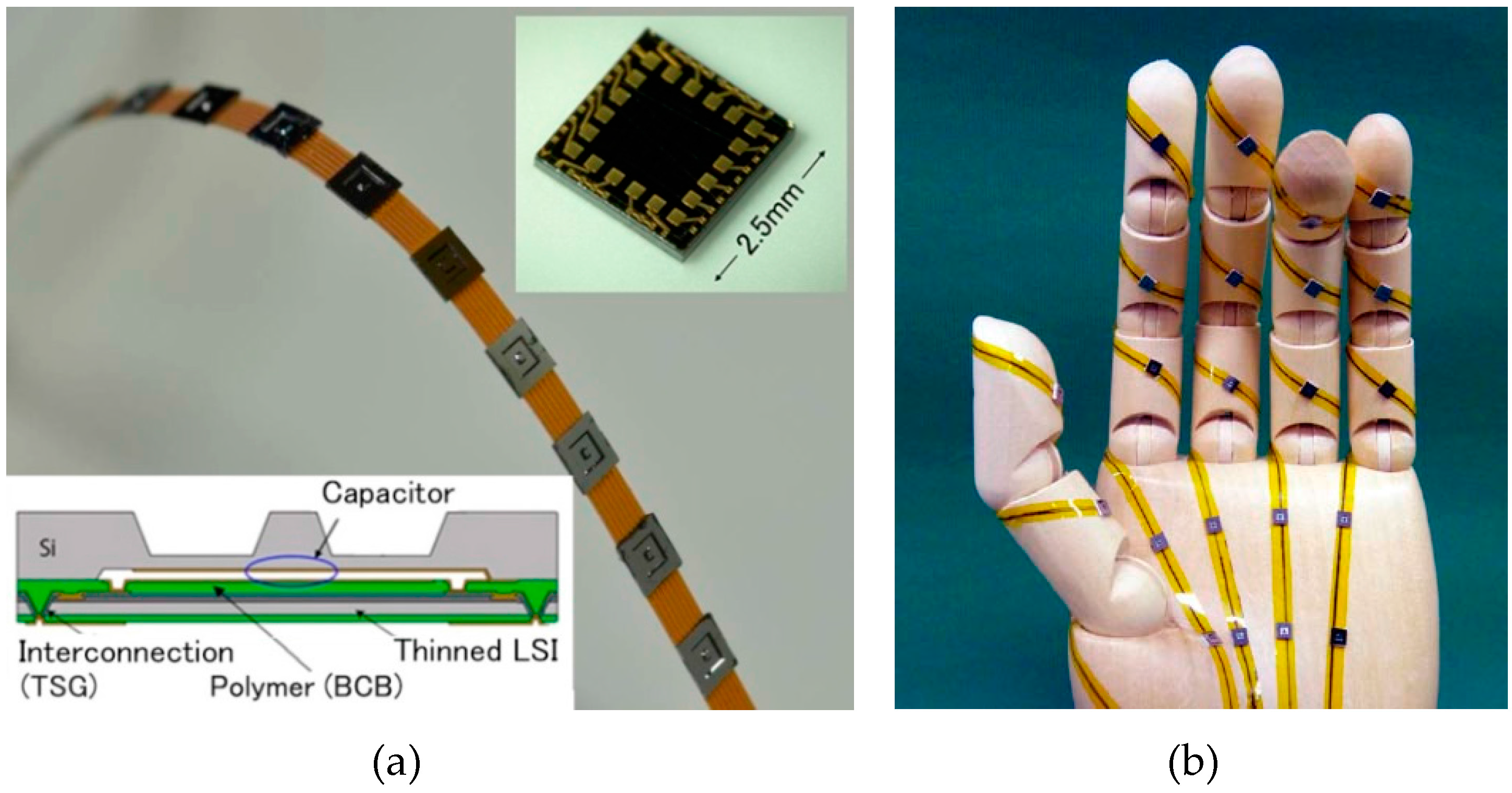

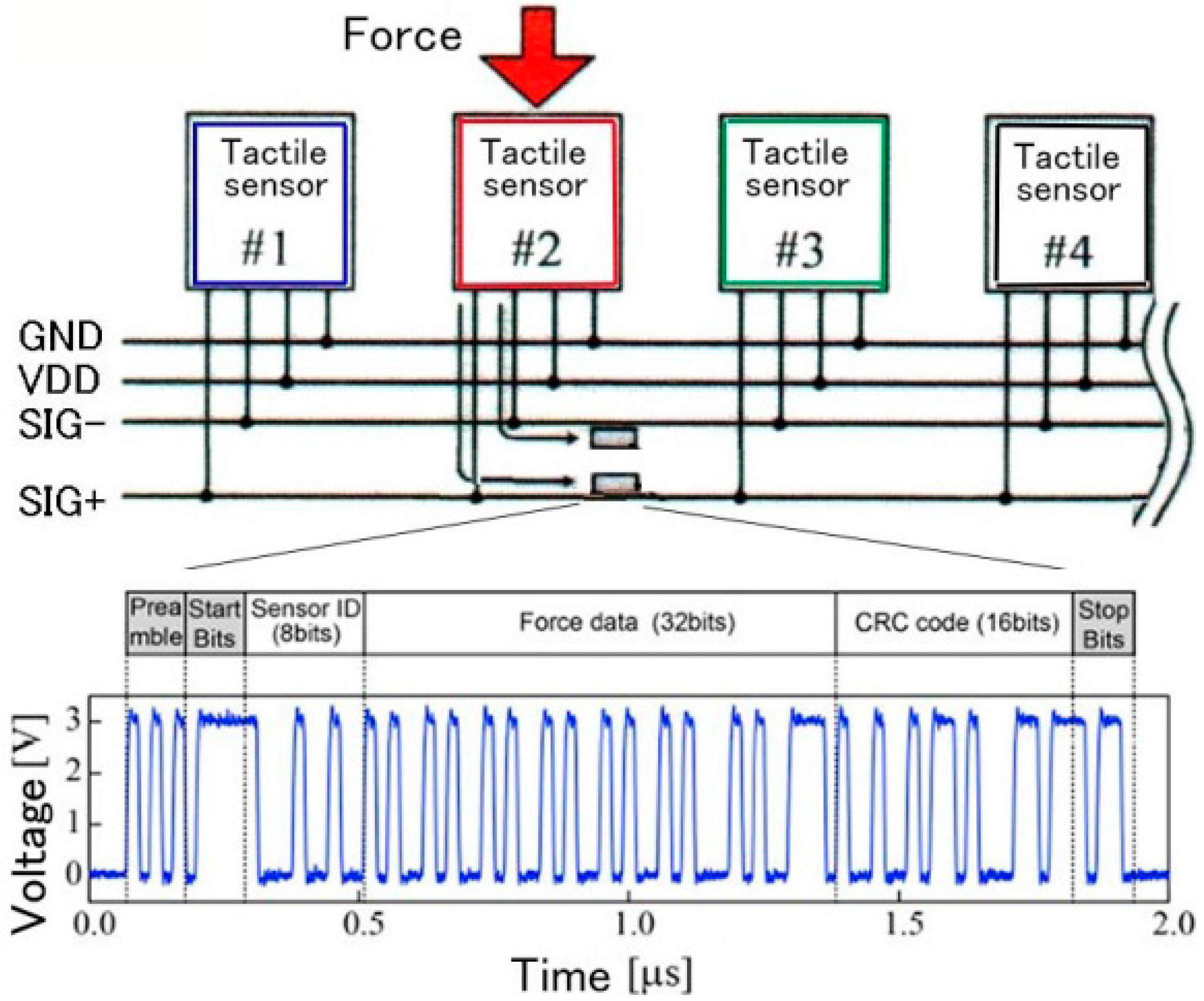

3.1. LSI Wafer Vias (Tactile Sensor Network)

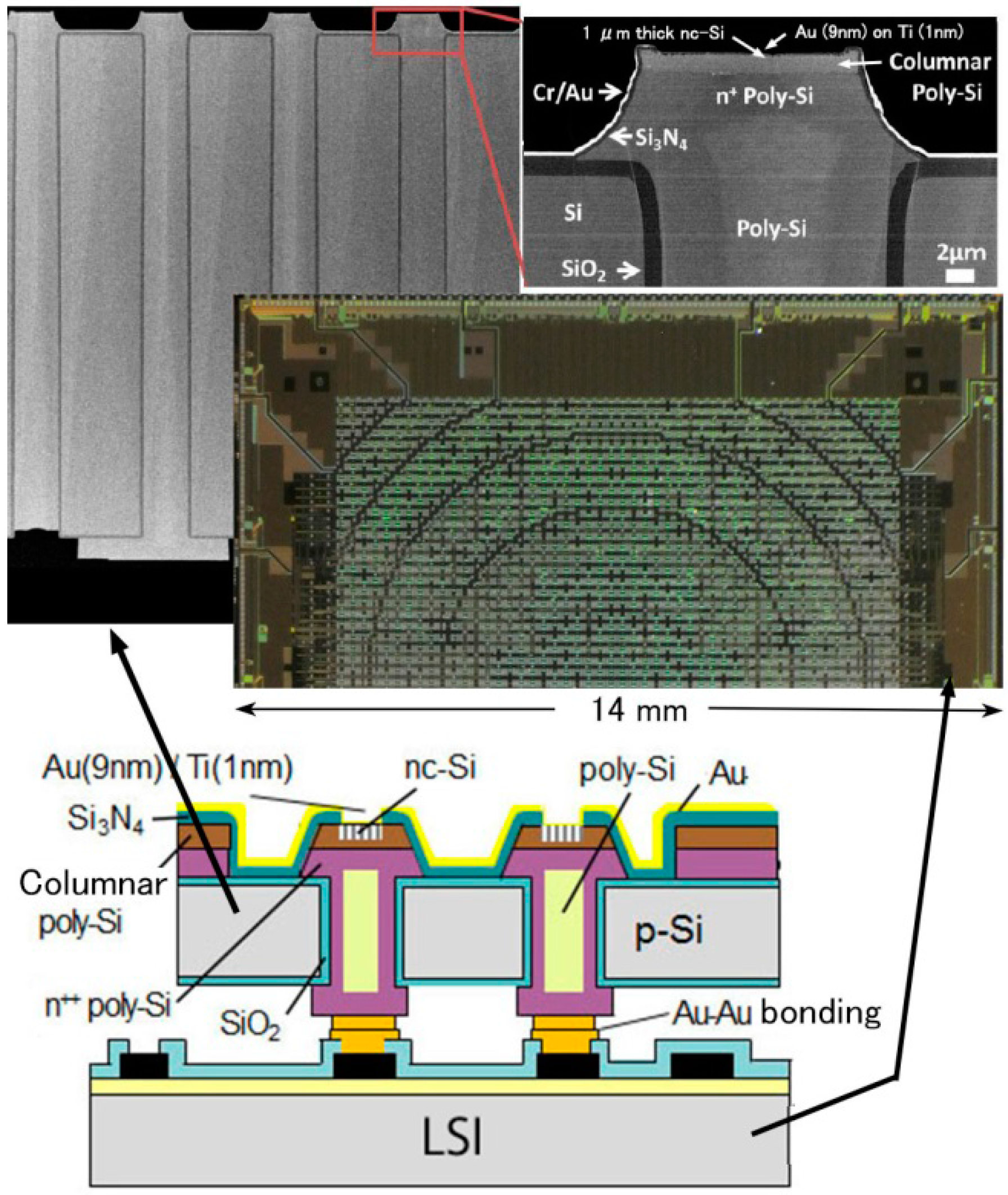

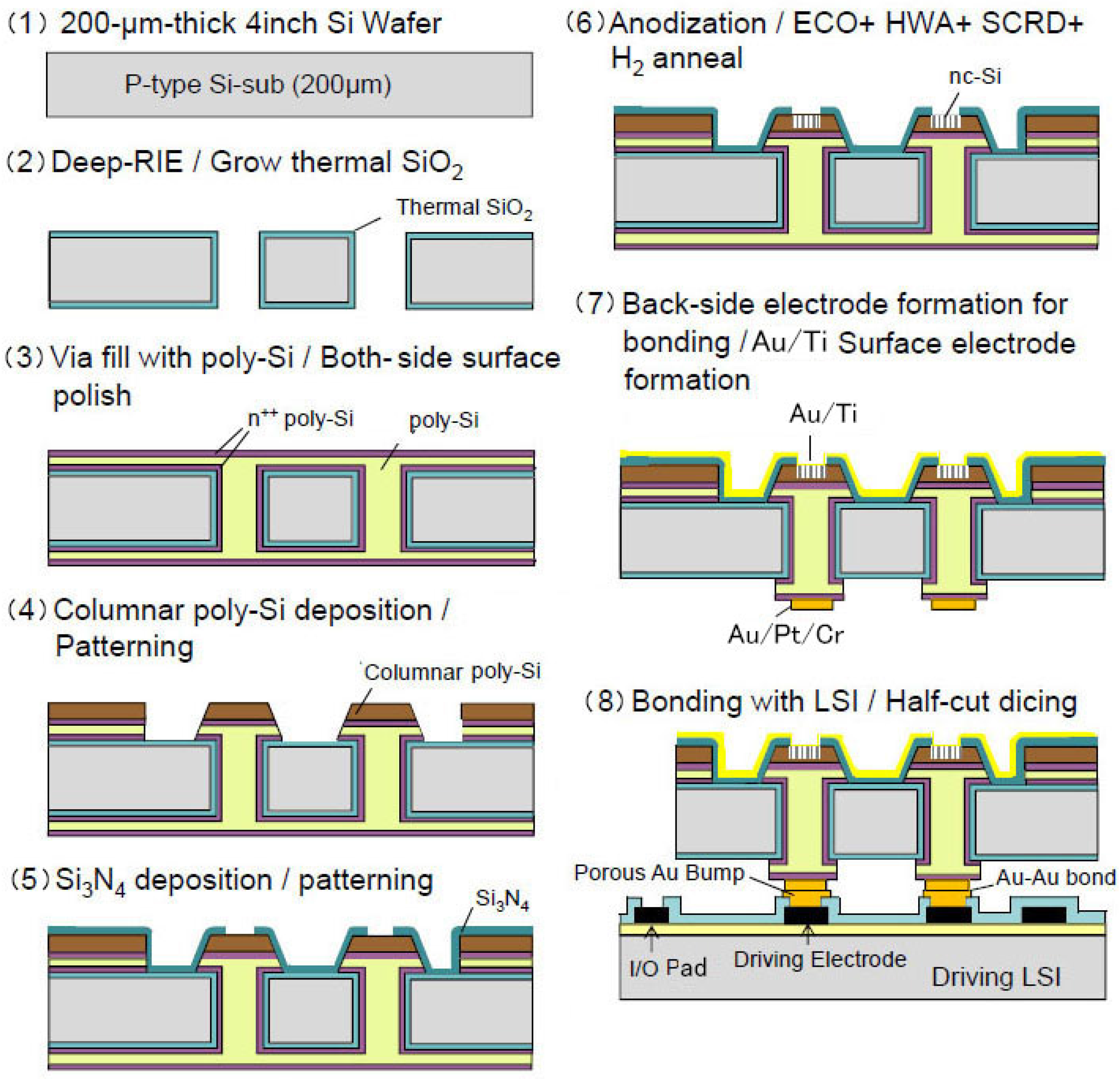

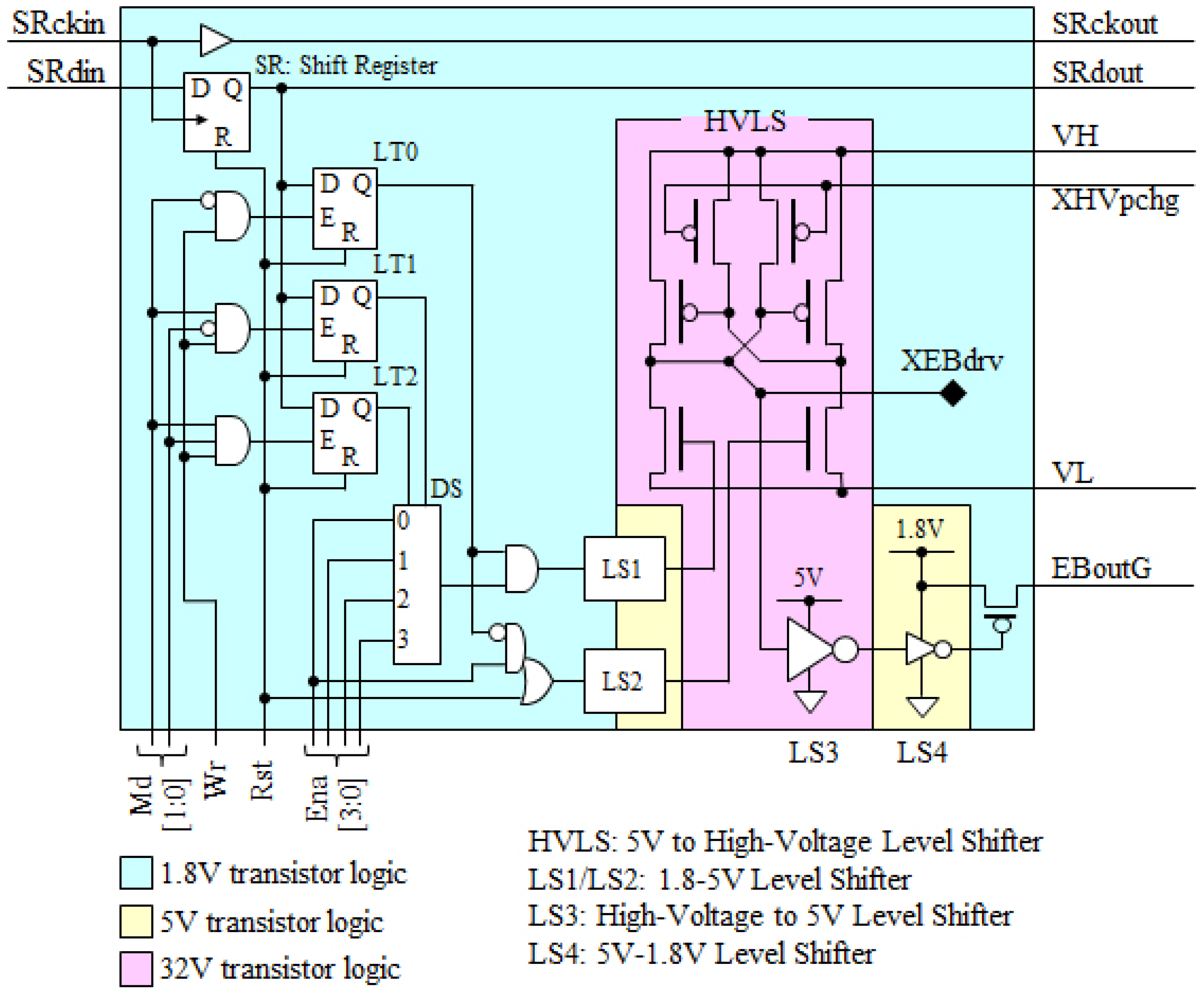

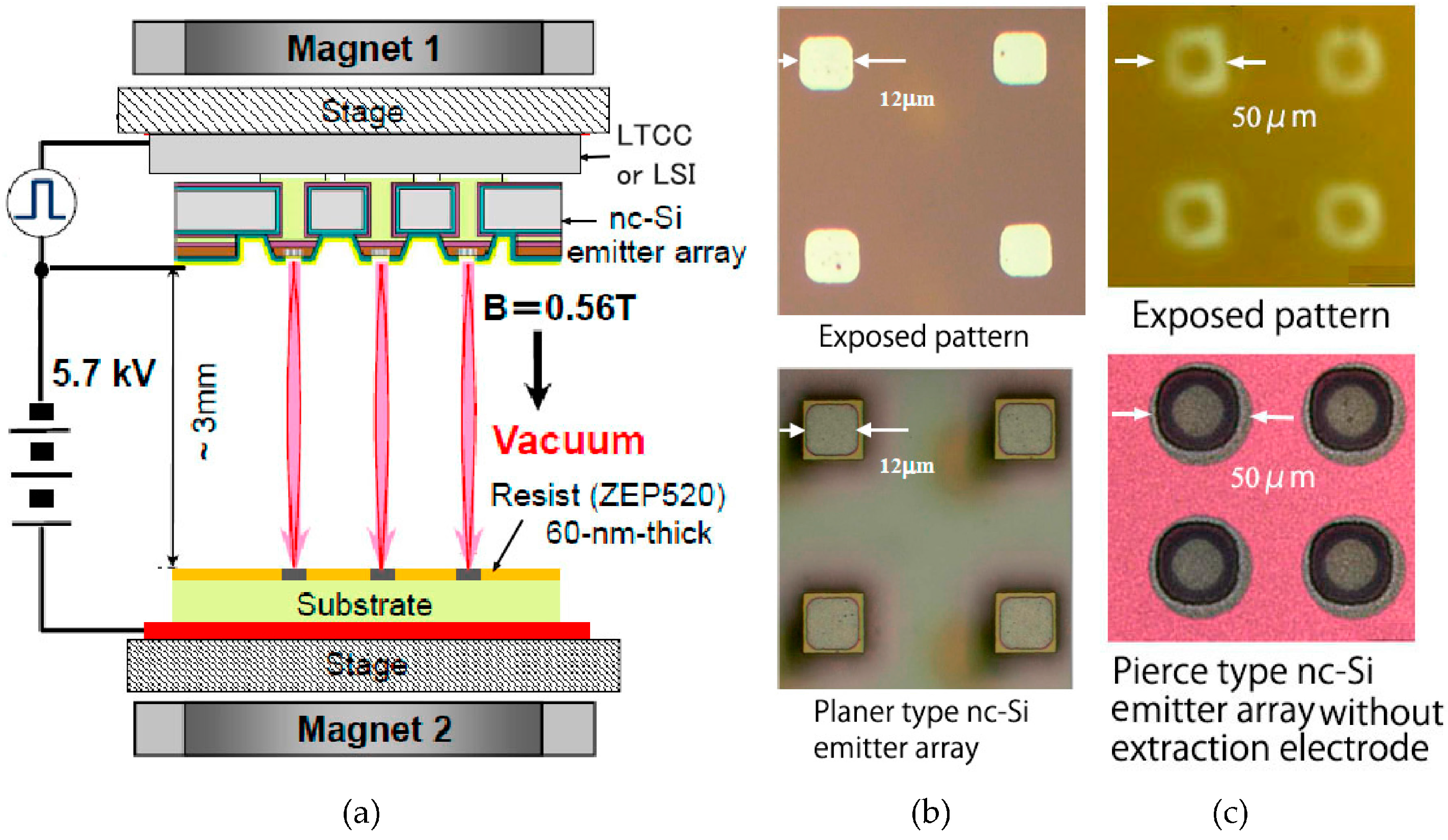

3.2. MEMS Wafer Vias (Active Matrix Planar-Type Electron Sources for Massive Parallel Electron Beam Lithography)

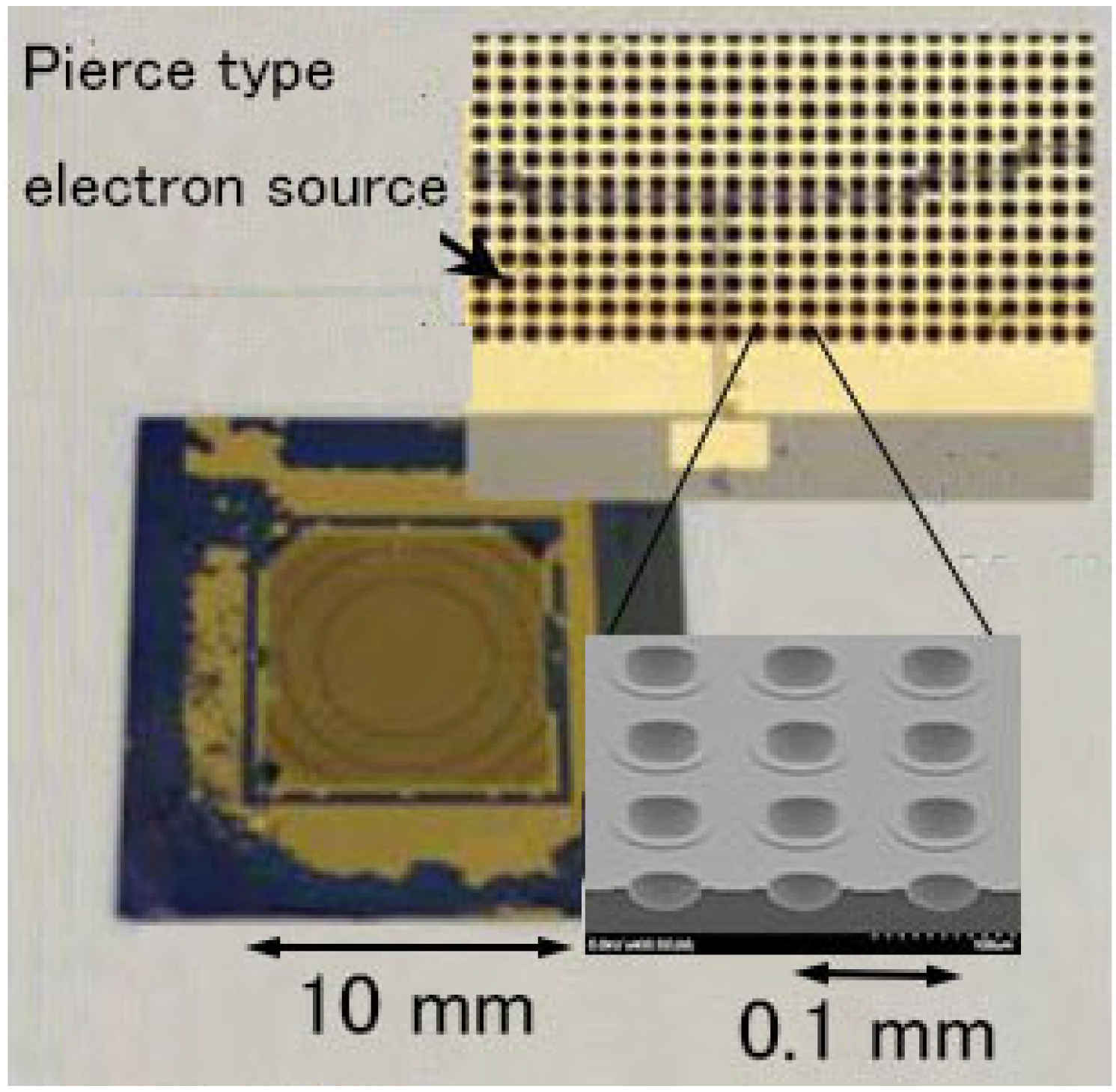

3.3. LSI Wafer Vias and MEMS Wafer Vias (Active Matrix Pierce-Type Electron Sources for Massive Parallel Electron Beam Lithography)

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Esashi, M.; Tanaka, S. Heterogeneous integration by adhesive bonding. Micro Nano Syst. Lett. 2013, 1, 3. [Google Scholar]

- Esashi, M. Wafer level packaging of MEMS. J. Micromech. Microeng. 2008, 18, 073001. [Google Scholar]

- Lapisa, A.; Stemme, G.; Niklaus, F. Wafer-level heterogeneous integration for MOEMS, MEMS and NEMS. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 629–644. [Google Scholar] [CrossRef]

- Lee, S.H.; Chen, K.-N.; Lu, J.J.-Q. Wafer-to-wafer alignment for three-dimensional integration: A review. J. Microelectromech. Syst. 2011, 20, 885–898. [Google Scholar] [CrossRef]

- Ogihara, M.; Fujiwara, H.; Mutoh, M.; Suzuki, T.; Igari, T.; Sugimori, T.; Kurokawa, H.; Kaneko, T.; Furuta, H.; Abiko, I.; et al. LED array integrated with Si driving circuits for LED-printer printhead. Electron. Lett. 2006, 42, 881–883. [Google Scholar] [CrossRef]

- Sukegawa, S.; Umebayashi, T.; Nakajima, T.; Kawanobe, H.; Koseki, K.; Hirota, I.; Haruta, T.; Kasai, M.; Fukumoto, K.; Wakano, T.; et al. A 1/4-inch 8Mpixel back-illuminated stacked CMOS image sensor. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2013; pp. 484–485.

- Despont, M.; Drechsler, U.; Yu, R.; Pogge, H.B.; Vettiger, P. Wafer-scale microdevice transfer/interconnect: Its application in an AFM-based data-storage system. J. Microelectromech. Syst. 2004, 13, 895–901. [Google Scholar] [CrossRef]

- Kochhar, A.; Matsumura, T.; Zhang, G.; Pokharel, R.; Hashimoto, K.; Esashi, M.; Tanaka, S. Monolithic fabrication of film bulk acoustic resonators above integrated circuit by adhesive-bonding-based film transfer. In Proceedings of the 2012 IEEE International Ultrasonics Symposium, Dresden, Germany, 7–10 October 2012; pp. 295–298.

- Hayasaka, T.; Yoshida, S.; Inoue, K.Y.; Nakano, M.; Matsue, T.; Esashi, M.; Tanaka, S. Integration of boron-doped diamond microelectrode on CMOS-based amperometric sensor array by film transfer technology. J. Microelectromech. Syst. 2015, 24, 958–967. [Google Scholar] [CrossRef]

- Matsuo, K.; Moriyama, M.; Esashi, M.; Tanaka, S. Low-voltage PZT-actuated MEMS switch monolithically integrated with CMOS circuit. In Proceedings of the 25th IEEE International Conference on Micro Electro Mechanical Systems (MEMS 2012), Paris, France, 29 January–2 February 2012; pp. 1153–1156.

- Tanaka, S.; Park, K.D.; Esashi, M. Lithium-niobate-based surface acoustic wave oscillator directly integrated with CMOS sustaining amplifier. IEEE Trans. Ultrason. Ferroelectr. Freq. Control 2012, 59, 1800–1805. [Google Scholar] [CrossRef] [PubMed]

- Guerre, R.; Drechsler, U.; Jubin, D.; Despont, M. Selective transfer technology for microdevice distribution. J. Microelectromech. Syst. 2008, 17, 157–165. [Google Scholar] [CrossRef]

- Hikichi, K.; Seiyama, K.; Ueda, M.; Taniguchi, S.; Hashimoto, K.; Esashi, M.; Tanaka, S. Wafer-level selective transfer method for FBAR-LSI integration. In Proceedings of the 2014 IEEE International Frequency Control Symposium, Taipei, Taiwan, 19–22 May 2014; pp. 246–249.

- Wang, Z. 3-D integration and through-silicon vias in MEMS and microsensors. J. Microelectromech. Syst. 2013, 24, 1211–1244. [Google Scholar] [CrossRef]

- Makihata, M.; Muroyama, M.; Nakano, Y.; Tanaka, S.; Nakayama, T.; Yamaguchi, U.; Yamada, H.; Nonomura, Y.; Funabashi, H.; Hata, Y.; et al. A 1.7 mm3 MEMS-on-CMOS tactile sensor using human-inspired autonomous common bus communication. In Proceedings of the 17th International Conference on Solid-State Sensors, actuators and Microsystems (Transducers2013 & Eurosensors XXVII), Balcerona, Spain, 16–20 June 2013; pp. 2729–2732.

- Makihata, M.; Tanaka, S.; Muroyama, M.; Matsuzaki, S.; Yamada, H.; Nakayama, T.; Yamaguchi, U.; Mima, K.; Nonomura, Y.; Fujiyoshi, M.; et al. Integration and packaging technology of MEMS-on-CMOS capacitive tactile sensor for robot application using thick BCB isolation layer and backside-grooved electrical connection. Sens. Actuators A 2012, 188, 103–110. [Google Scholar] [CrossRef]

- Koshida, N.; Kojima, A.; Ikegami, N.; Yoshida, T.; Suda, R.; Yagi, M.; Shirakashi, J.; Yoshida, T.; Miyaguchi, M.; Muroyama, H.; et al. Development of ballistic hot electron emitter and its applications to parallel processing; active-matrix massive direct-write lithography in vacuum and thin films deposition in solutions. J. Micro/Nanolithogr. MEMS MOEMS 2015, 14, 031215. [Google Scholar] [CrossRef]

- Esashi, M.; Kojima, A.; Ikegami, N.; Miyaguchi, H.; Koshida, N. Development of massively parallel electron beam direct write lithography using active-matrix nanocrystalline-silicon electron emitter arrays. Microsyst. Nanoeng. 2015, 1, 15029. [Google Scholar] [CrossRef]

- Tanaka, S.; Mohri, M.; Ogashiwa, T.; Fukushi, H.; Tanaka, K.; Nakamura, D.; Nishimori, T.; Esashi, M. Electrical interconnection in anodic bonding of silicon wafer to LTCC wafer using highly compliant porous bumps made from submicron gold particles. Sens. Actuators A 2012, 188, 198–202. [Google Scholar] [CrossRef]

- Nishino, H.; Yoshida, S.; Kojima, A.; Ikegami, N.; Tanaka, S.; Koshida, N.; Esashi, M. Fabrication of Pierce-type nanocrystalline Si electron-emitter array for massively parallel electron beam lithography. IEEJ Trans. Sens. Micromach. 2014, 134, 146–153. (In Japanese) [Google Scholar] [CrossRef]

© 2016 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Esashi, M.; Tanaka, S. Stacked Integration of MEMS on LSI. Micromachines 2016, 7, 137. https://doi.org/10.3390/mi7080137

Esashi M, Tanaka S. Stacked Integration of MEMS on LSI. Micromachines. 2016; 7(8):137. https://doi.org/10.3390/mi7080137

Chicago/Turabian StyleEsashi, Masayoshi, and Shuji Tanaka. 2016. "Stacked Integration of MEMS on LSI" Micromachines 7, no. 8: 137. https://doi.org/10.3390/mi7080137