Article

# Improvement of Dynamic On-Resistance in GaN-Based Devices with a High-Quality In Situ SiN Passivation Layer

Jeong-Gil Kim<sup>1,†</sup>, Jun-Hyeok Lee<sup>2,†</sup>, Dong-Min Kang<sup>1</sup> and Jung-Hee Lee<sup>3,\*</sup>

- <sup>1</sup> Terrestrial & Non-Terrestrial Integrated Telecommunications Research Laboratory, Electronics and Telecommunications Research Institute, Daejeon 34129, Republic of Korea; jeonggil.kim@etri.re.kr (J.-G.K.); kdm1597@etri.re.kr (D.-M.K.)

- <sup>2</sup> GaN Part, DB-Hitek, Eumseong 27605, Republic of Korea; junhyeok.lee@dbhitek.com

- <sup>3</sup> L&D Inc., Daegu 34138, Republic of Korea

- \* Correspondence: jlee@ee.knu.ac.kr

- + These authors contributed equally to this work.

Abstract: In this paper, we compared the characteristics of normally-on/off AlGaN/GaN MISHEMTs passivated by an in situ/ex situ SiN layer. The devices passivated by the in situ SiN layer revealed enhanced DC characteristics, such as the drain current of 595 mA/mm (normally-on) and 175 mA/mm (normally-off) with the high on/off current ratio of ~10<sup>7</sup>, respectively, compared with those of the devices passivated by the ex situ SiN layer. The MISHEMTs passivated by the in situ SiN layer also exhibited a much lower increase of dynamic on-resistance ( $R_{ON}$ ) of 4.1% for the normally-on device and 12.8% for the normally-off device, respectively. Furthermore, the breakdown characteristics are greatly improved by employing the in situ SiN passivation layer, suggesting that the in situ SiN passivation layer can remarkably not only suppress the surface-trapping effects, but also decrease the off-state leakage current in the GaN-based power devices.

Keywords: AlGaN/GaN; MISHEMT; in situ SiN; dynamic on-resistance; breakdown voltage

Citation: Kim, J.-G.; Lee, J.-H.; Kang, D.-M.; Lee, J.-H. Improvement of Dynamic On-Resistance in GaN-Based Devices with a High-Quality In Situ SiN Passivation Layer. *Micromachines* **2023**, *14*, 1227. https://doi.org/10.3390/ mi14061227

Academic Editor: Yu-Shyan Lin

Received: 9 May 2023 Revised: 30 May 2023 Accepted: 8 June 2023 Published: 10 June 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

## 1. Introduction

Recently, there has been enormous progress in the field-effect transistors (FET) with the wide band-gap semiconductors. GaN-based devices have demonstrated excellent performances for high-power/frequency applications due to their high breakdown electric field, high saturation velocity, and high thermal stability [1,2]. Especially, GaNbased metal-insulator-semiconductor high-electron-mobility transistors (MISHEMTs) have demonstrated a high performance of the devices in the power-switching applications [3–5]. MISHEMTs can reduce the gate leakage dramatically and enlarge gate voltage swing. In addition, the GaN-based normally-off devices are also attractive candidates for the power-switching applications [6–8]. However, GaN-based devices still have the demand of reducing the trapping effects from the surface and buffer layers, which results in the current dispersion and higher dynamic on-resistance. In particular, the traps on the surface can capture the electrons and then act as a virtual gate, which depletes 2-DEG (2-dimensional electron gas) channel electrons and increase on-resistance simultaneously [9]. There have been many efforts to reduce the surface-trapping effect and passivate the surface with SiN, SiO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> deposited by low-pressure chemical vapor deposition (LPCVD), plasmaenhanced chemical vapor deposition (PECVD), and atomic layer deposition (ALD), respectively [10–14]. Moreover, new studies of improving the interface have been introduced such as the insertion of graphene, an AINO layer deposited by plasma-enhanced atomic layer deposition (PEALD), and a SiON layer deposited by the PECVD, respectively [15–17]. However, a high density of interface trap states (D<sub>it</sub>) in the order of  $\sim 10^{13}$ - $10^{14}$  cm<sup>-2</sup> eV<sup>-1</sup> are still usually present at the dielectric/AlGaN barrier interface with these ex situ passivation layer [18-21].

Compared with these ex situ deposited passivation layers, a high-quality in situ SiN passivation layer can be grown at a much higher temperature in a metal-organic chemical vapor deposition (MOCVD) chamber immediately after the growth of the AlGaN barrier, without exposing the barrier to the ambient air to eliminate the process-induced surface contamination and/or damage which results in less formation of the interface trap states [22–24]. In addition, the in situ SiN layer is grown at the relatively high growth temperature and low growth rate, resulting in a much better dielectric quality [25–27].

In this work, we present the effects of an in situ SiN passivation layer on the device performance, including DC characteristics, pulsed I-V characteristics, and breakdown characteristics. We fabricated two different AlGaN/GaN-MISHEMTs with the in situ SiN passivation layers; one for the normally-on HEMT utilizing the in situ SiN layer as the gate insulator, and the other for the gate recessed normally-off HEMT with removing the in situ SiN layer in the recessed gate region. The dynamic on-resistances (R<sub>ON</sub>) of the fabricated devices were remarkably improved due to the effective suppression of the trapping effects.

#### 2. Materials and Methods

### 2.1. Epitaxial Structure

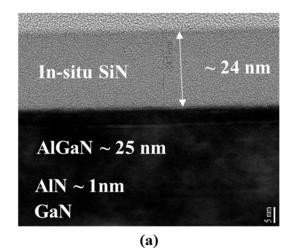

In situ SiN/AlGaN/GaN heterostructures were grown on 2 inch SiC substrates. Trimethylgallium (TMGa), trimethylaluminum (TMAl), ammonia (NH3), and silane (SiH<sub>4</sub>) were used as the sources of Ga, Al, N, and Si, respectively. Firstly, a 50 nm-thick initial GaN nucleation layer was grown at a low temperature of 525 °C, and then a 2 µm-thick C-doped semi-insulating GaN buffer layer was grown at 1060 °C, which consists of the 1st GaN layer grown with a pressure of 50 Torr and the 2nd GaN layer with 300 Torr. Sequentially, an AlGaN/GaN heterostructure consisting of a 50 nm-thick unintentionally doped GaN channel layer, and a 25 nm-thick Al<sub>0.25</sub>Ga<sub>0.75</sub>N barrier were grown in the same growth temperature of 1060 °C. To improve the 2-DEG property, a 1 nm-thick AlN layer was inserted between the barrier and the GaN channel layer. Finally, an in situ SiN layer was grown at 1000 °C. The cross-sectional TEM image and the energy-dispersive X-ray spectroscopy (EDX) analysis shown in Figure 1, indicate that the thickness of the in situ SiN layer being 24 nm, and the interface between the in situ SiN layer and AlGaN barrier being abrupt in nature.

Prior to device fabrication, the two-dimensional electron gas (2-DEG) property was evaluated by Hall measurements using the Van der Pauw method, such as the sheet concentration of  $8.9 \times 10^{12}$  cm<sup>-2</sup>, electron mobility of 1950 cm<sup>2</sup>/V·s, and sheet resistance of 357 ohm/sq, respectively.

Figure 1. Cont.

**Figure 1.** (a) Cross-sectional TEM image of the AlGaN/GaN heterostructure with the in situ SiN and EDX analysis of (b) Al, (c) Ga, (d) N, and (e) Si, respectively.

## 2.2. Device Fabrication

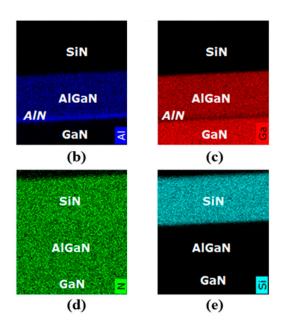

As shown in Figure 2, normally-on and normally-off devices were fabricated to assess the effect of the in situ SiN passivation layer. For the fabrication of normally-on devices of MISHEMTs shown in Figure 2a, the mesa isolation, which is one of the most widely used techniques for device isolation was first performed using  $Cl_2$  gas in an inductively coupled-plasma reactive ion etcher (ICP-RIE). For the protection of the epitaxial layer and preventing the increase of sheet resistance during the rapid thermal annealing (RTA) process, a 30 nm-thick SiN protection layer was deposited by PECVD. An ohmic metal stack consisting of Si/Ti/Al/Ni/Au (1/25/160/40/100 nm) was then deposited by an e-beam evaporator, followed by 2-step rapid thermal annealing at 500 °C for 20 s and 850 °C for 30 s in N<sub>2</sub> ambient to form the source/drain ohmic contact. The contact resistance was evaluated as 0.6 ohm-mm measured by the transfer length method (TLM). Finally, Ni/Au (50/150 nm) was deposited for the gate electrode.

**Figure 2.** Schematic representation of (**a**) normally-on and (**b**) normally-off AlGaN/GaN MISHEMTs passivated with in situ/ex situ SiN layer.

For the fabrication of normally-off MISHEMTs shown in Figure 2b, the in situ SiN layer and the AlGaN barrier was sequentially recess-etched in the gate region using dry etching in CF<sub>4</sub> and Cl<sub>2</sub> gas by ICP-RIE, respectively. Then, a 15 nm-thick ALD Al<sub>2</sub>O<sub>3</sub> layer was deposited as a gate insulator. The gate length (L<sub>G</sub>), the gate width (W<sub>G</sub>), and the gate–drain distance (L<sub>GD</sub>) of the fabricated devices were 3, 100, and 5 u  $\mu$  m, respectively. For comparison of the device characteristics, ex situ SiN/AlGaN/GaN normally-on/off MISHEMTs were also fabricated. The thickness of the ex situ SiN layer was approximately 25 nm.

#### 3. Results and Discussion

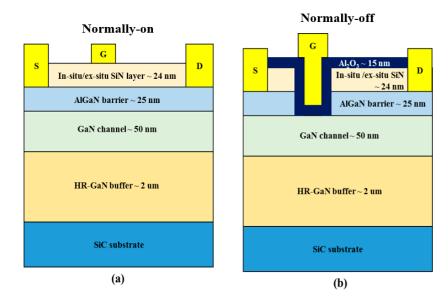

Figure 3a shows the C–V characteristics measured from the metal/in situ SiN/AlGaN/ GaN stack capacitor with varying frequencies from 10 kHz to 1 MHz at room temperature. The C–V curves revealed a sharp transition and negligible frequency dispersion, indicating that the in situ SiN layer deposited on the AlGaN barrier forms a very high-quality interface.

Figure 3. (a) Multi-frequency C–V characteristics. (b) XPS analysis of the in situ SiN passivation layer.

The extracted  $D_{it}$  at  $E_c - E_T = 0.3$  eV was calculated as  $3.66 \times 10^{11}$  eV<sup>-1</sup> cm<sup>-2</sup> Equation (1) below, indicating that the In situ SiN layer effectively passivates the AlGaN surface, and reduces the interface trap density at the dielectric/barrier compared to that with the ex situ SiN layer [28,29].

$$D_{it} = \frac{C_{ox}}{q} \left( \frac{dV_G}{d\psi_s} - 1 \right) - \frac{C_s}{q} = \frac{C_{ox}}{q} \frac{dV_G}{d\psi_s}$$

(1)

X-ray photoelectron spectroscopy (XPS) was performed to compare the density of the Ga-O bonds, which are believed to be main origin of the surface trap. In Figure 3b, black line shows the XPS analysis of the in situ SiN passivation layer and it consists of three components with binding energies of 20.8, 19.6, and 18.7 eV were extracted, which corresponded to Ga-O, Ga-N, and the Ga element, respectively. The intensity of the Ga-O bond decreased when the AlGaN surface was covered with the in situ SiN passivation layer, as shown in Figure 3b. Consequently, it was expected that the in situ SiN passivation layer effectively suppressed the oxygen incorporation at the AlGaN surface to reduce the trapping effects at the device surface as the in situ SiN layer grew immediately after the AlGaN barrier was grown in the MOCVD chamber.

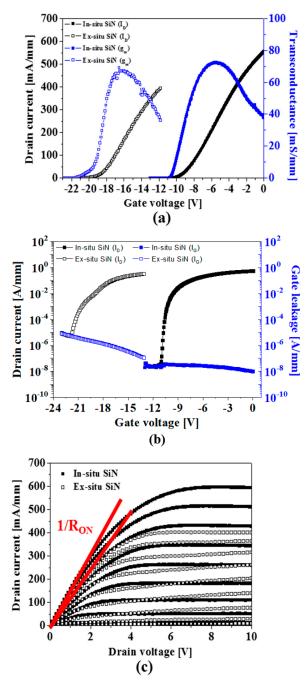

The transfer I–V and DC output characteristics of both AlGaN/GaN MISHEMTs with an in situ/ex situ SiN layer were evaluated. Figure 4a shows the transfer characteristics of the normally-on AlGaN/GaN MISHEMTs with an in situ/ex situ SiN layer at the saturation region ( $V_{DS} = 10$  V). The MISHEMTs passivated with an ex situ SiN layer showed the threshold voltage of -18.5 V, the drain current of 401 mA/mm at VG = -12 V, and the peak transconductance of 67 mS/mm, respectively. The MISHEMTs passivated with the in situ SiN layer showed improved device characteristics, such as the drain current of 595 mA/mm at  $V_G = 0$  V, the threshold voltage of -9.2 V, and the peak transconductance of 76 mS/mm, respectively. The large negative threshold voltage for the device with the ex situ SiN passivation layer was believed to be due to the high density of the positive fixed charges in the ex situ SiN layer, which also increased the 2DEG density to satisfy the charge neutrality.

Moreover, the device passivated by the in situ SiN showed a very low off-state leakage current of  $\sim 2 \times 10^{-8}$  A/mm and a high on/off current ratio of  $\sim 10^7$  compared to those of the device passivated with the ex situ SiN layer as shown in Figure 4b. It is believed that in situ SiN effectively prevents the generation of the Ga-O bond at the AlGaN surface, and hence suppresses the surface-trapping effects and the surface leakage current, resulting in the low off-state leakage current.

**Figure 4.** Comparison of the normally-on AlGaN/GaN MISHEMTs in transfer characteristics, including (**a**) linear scale, (**b**) log scale, and (**c**) output characteristics.

Figure 4c compares the output characteristics of the AlGaN/GaN MISHEMTs passivated by the in situ/ex situ SiN layer. The device passivated with the in situ SiN layer showed a relatively low  $R_{ON}$  of 5.6 ohm-mm extracted in the linear region and at  $V_G$  where the maximum drain current flows. Meanwhile, the device passivated with the ex situ SiN layer showed a higher  $R_{on}$  of 8.4 ohm-mm. This was believed to be due to the gate lag caused by the surface trapping [30].

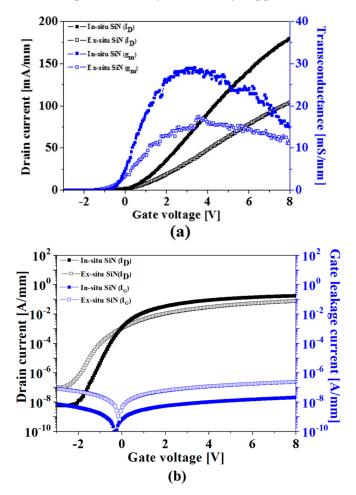

The merit of the in situ SiN layer was also proven in the normally-off MISHEMTs as shown in Figure 5. The device passivated with the in situ SiN layer showed a higher drain current of 175 mA/mm at  $V_G = 8$  V and a peak transconductance of 29 mS/mm, compared to that of the drain current of 104 mA/mm and the peak transconductance of 17 mS/mm for the device containing the ex situ SiN layer, respectively. Furthermore, the device with the in situ SiN layer exhibited a much improved off-state leakage current of  $6 \times 10^{-9}$  A/mm with a high on/off current ratio of ~ $10^7$  and R<sub>ON</sub> of 25 ohm-mm compared to the values of the off-state leakage current of  $1 \times 10^{-7}$  A/mm and R<sub>ON</sub> of 41 ohm-mm for the devices passivated with the ex situ SiN layer, respectively.

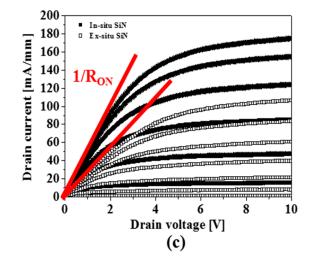

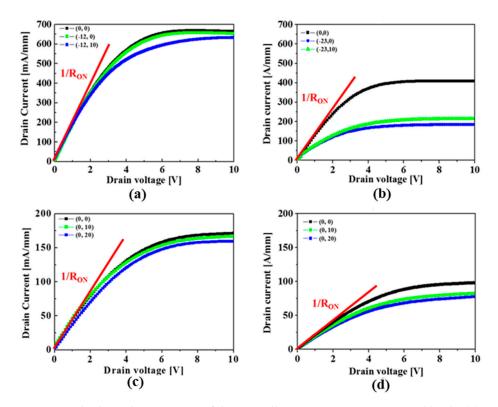

The pulsed I–V characteristics were measured under the condition of a pulse width of 50  $\mu$ s and period of 1 mS, respectively, as shown in Figure 6. The devices passivated with the in situ SiN layer showed a much lower percentage increase of dynamic R<sub>on</sub> of 4.1% for the normally-on device, and 12.8% for the normally-off device, respectively, while the devices with passivated with the ex situ SiN layer revealed a corresponding percentage increase of dynamic R<sub>on</sub> of 50 and 16.9%, respectively. Therefore, it was concluded that the in situ SiN passivation layer effectively suppressed the surface-trapping effects.

Figure 5. Cont.

**Figure 5.** Comparison of the normally-off AlGaN/GaN MISHEMTs in transfer characteristics, including the (**a**) linear scale, (**b**) log scale, and (**c**) output characteristics.

**Figure 6.** Pulsed I-V characteristics of the normally-on MISHEMTs passivated by the (**a**) in situ and (**b**) ex situ SiN layers, and of the normally-off MISHEMTs passivated by the (**c**) in situ and (**d**) ex situ SiN layers.

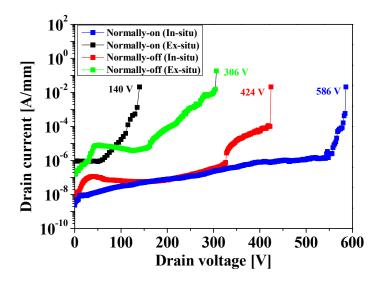

The breakdown characteristics of the devices with a  $L_{GD}$  of 5 um were measured using the Keithley model 248 high voltage supply and a Keithly 6485 picoammeter, as shown in Figure 7. The normally-on/off MISHEMTs passivated with the in situ SiN layer exhibited a much higher breakdown voltage of 586 and 424 V, respectively, while the devices passivated with ex situ SiN layer exhibited a relatively poor breakdown voltage of 140 and 306 V, respectively, indicating that the in situ SiN passivation layer can remarkably suppress the surface-trapping effects in the GaN-based devices.

**Figure 7.** Comparison of the off-state breakdown characteristics in the normally-on/off MISHEMTs passivated by the in situ/ex situ SiN layer.

### 4. Conclusions

The characteristics of the normally-on/off AlGaN/GaN MISHEMTs passivated with an in situ/ex situ SiN layer were investigated. The devices passivated with the in situ SiN layer showed much improved DC characteristics, such as the drain current of 595 mA/mm (normally-on) and 175 mA/mm (normally-off) with the high on/off current ratio of ~10<sup>9</sup>, respectively, compared to those of the devices passivated with the ex situ SiN layer. The devices passivated with the in situ SiN layer showed a much lower percentage increase of dynamic R<sub>on</sub> of 4.1% for the normally-on device and 12.8% for the normally-off device, respectively.

It was also found that the in situ SiN passivation layer greatly improved the breakdown characteristics for the device of 586 and 424 V for normally-on and normally-off, respectively, indicating that the passivation with the high-quality in situ SiN layer devices can withstand much higher voltages, thereby improving its robustness.

In conclusion, employing an in situ SiN passivation layer in AlGaN/GaN MISHEMTs leads to improved DC characteristics, including higher drain currents, increased on/off current ratios, lower dynamic R<sub>on</sub>, and enhanced breakdown characteristics. These findings have implications for the design and optimization of high-performance GaN-based transistors.

**Author Contributions:** Writing—original draft, J.-G.K. and J.-H.L. (Jun-Hyeok Lee); Writing—review & editing, J.-H.L. (Jung-Hee Lee); Supervision, D.-M.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the Institute of Information & communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) (2021-0-00760, Development of GaN-based process technology and RF components for 28 GHz 5G base stations).

Data Availability Statement: Data available in a publicly accessible repository.

Conflicts of Interest: The authors declare no conflict.

#### References

- Lee, H.S.; Piedra, D.; Sun, M.; Gao, X.; Guo, S.; Palacios, T. 3000-V 4.3-mΩ·cm2 InAlN/GaN MOSHEMTs With AlGaN Back Barrier. *IEEE Electron Device Lett.* 2012, 33, 982–984. [CrossRef]

- Shinohara, K.; Regan, D.; Corrion, A.; Brown, D.; Burnham, S.; Willadsen, P.; AlvaradoRodriguez, I.; Cunningham, M.; Butler, C.; Schmitz, A.; et al. Deeply-scaled self-aligned-gate GaN DH-HEMTs with ultrahigh cutoff frequency. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 453–456.

- Wong, K.Y.R.; Kwan, M.H.; Yao, F.W.; Tsai, M.W.; Lin, Y.S.; Chang, Y.C.; Chen, P.C.; Su, R.Y.; Yu, J.; Yang, F.J.; et al. A next generation CMOS-compatible GaN-on-Si transistors for high efficiency energy systems. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 9.5.1–9.5.4.

- Kikkawa, T.; Hosoda, T.; Imanishi, K.; Shono, K.; Itabashi, K.; Maeda, T.; Asai, Y.; Shen, L.; Clement, H.; Honea, J.; et al. 600 V JEDEC-qualified highly reliable GaN HEMTs on Si substrates. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 2.6.1–2.6.4.

- 5. Saito, W.; Nitta, T.; Kakiuchi, Y.; Saito, Y.; Tsuda, K.; Omura, I.; Yamaguchi, M. A 120-W Boost Converter Operation Using a High-Voltage GaN-HEMT. *IEEE Electron Device Lett.* 2008, 29, 8–10. [CrossRef]

- Jones, E.A.; Wang, F.; Ozpineci, B. Application-based review of GaN HFETs. In Proceedings of the 2014 IEEE Workshop on Wide Bandgap Power Devices and Applications, Knoxville, TN, USA, 13–15 October 2014; pp. 24–29.

- Jones, E.A.; Wang, F.; Costinett, D. Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 707–719. [CrossRef]

- Heuken, L.; Kortemeyer, M.; Ottaviani, A.; Schroder, M.; Alomari, M.; Fahle, D.; Marx, M.; Heuken, M.; Kalisch, H.; Vescan, A.; et al. Analysis of an AlGaN/AlN Super-Lattice Buffer Concept for 650-V Low-Dispersion and High-Reliability GaN HEMTs. *IEEE Trans. Electron Devices* 2020, 67, 1113–1119. [CrossRef]

- Tzou, A.-J.; Chu, K.-H.; Lin, I.-F.; Østreng, E.; Fang, Y.-S.; Wu, X.-P.; Wu, B.-W.; Shen, C.-H.; Shieh, J.-M.; Yeh, W.-K.; et al. AlN surface passivation of GaN-based high electron mobility transistors by plasma-enhanced atomic layer deposition. *Nano Express* 2017, 12, 1–6. [CrossRef]

- Freedsman, J.J.; Egawa, T.; Yamaoka, Y.; Yano, Y.; Ubukata, A.; Tabuchi, T.; Matsumoto, K. Normally-OFF Al<sub>2</sub>O<sub>3</sub>/AlGaN/GaN MOS-HEMT on 8 in. Si with Low Leakage Current and High Breakdown Voltage (825 V). *Appl. Phys. Exp.* 2014, 7, 041003. [CrossRef]

- 11. Huang, T.; Zhu, X.; Wong, K.M.; Lau, K.M. Low-Leakage-Current AlN/GaN MOSHFETs Using Al<sub>2</sub>O<sub>3</sub> for Increased 2DEG. *IEEE Electron Device Lett.* **2012**, *33*, 212–214. [CrossRef]

- Wu, T.-L.; Marcon, D.; Jaeger, B.D.; Hove, M.V.; Bakeroot, B.; Stoffels, S.; Groeseneken, G.; Decoutere, S.; Roelofs, R. The impact of the gate dielectric quality in developing Au-free D-mode and E-mode recessed gate AlGaN/GaN transistors on a 200mm Si substrate. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 6C.4.1–6C.4.6.

- Choi, W.; Seok, O.; Ryu, H.; Cha, H.-Y.; Seo, K.-S. High-Voltage and Low-Leakage-Current Gate Recessed Normally-Off GaN MIS-HEMTs With Dual Gate Insulator Employing PEALD-SiNx/RF-Sputtered-HfO<sub>2</sub>. *IEEE Electron Device Lett.* 2014, 35, 175–177. [CrossRef]

- 14. Zhang, Z.; Yu, G.; Zhang, X.; Deng, X.; Li, S.; Fan, Y.; Sun, S.; Song, L.; Tan, S.; Wu, D.; et al. Studies on high-voltage GaN-on-Si MIS-HEMTs using LPCVD Si<sub>3</sub>N<sub>4</sub> as gate dielectric and passivation layer. *IEEE Trans. Electron Devices* **2016**, *63*, 731–738. [CrossRef]

- 15. Liu, X.; Zheng, L.; Cheng, X.; Shen, L.; Liu, S.; Wang, D.; You, J.; Yu, Y. Graphene-induced positive shift of the flat band voltage in recessed gate AlGaN/GaN structures. *Appl. Phy. Lett.* **2021**, *118*, 173504. [CrossRef]

- 16. Wang, Q.; Cheng, X.; Zheng, L.; Ye, P.; Li, M.; Shen, L.; Li, J.; Zhang, D.; Gu, Z.; Yu, Y. Band alignment between PEALD-AlNO and AlGaN/GaN determined by angle-resolved X-ray photoelectron spectroscopy. *Appl. Surface Sci.* **2017**, *423*, 675–679. [CrossRef]

- 17. Geng, K.; Chen, D.; Zhou, Q.; Wang, H. AlGaN/GaN MIS-HEMT with PECVD SiNx, SiON, SiO<sub>2</sub> as Gate Dielectric and Passivation layer. *Electronics* **2018**, *7*, 416. [CrossRef]

- 18. Liao, W.C.; Chen, Y.L.; Chen, Z.X.; Chyi, J.I.; Hsin, Y.M. Gate leakage current induced trapping in AlGaN/GaN Schottky-gate HFETs and MISHFETs. *Nanoscale Res. Lett.* **2014**, *9*, 474. [CrossRef]

- 19. Kim, H.; Thompson, R.M.; Tilak, V.; Prunty, T.R.; Shealy, J.R.; Eastman, L.F. Effects of SiN passivation and high-electric field on AlGaN-GaN HFET degradation. *IEEE Electron Device Lett.* **2003**, *24*, 421–423.

- Xu, D.; Chu, K.; Diaz, J.; Zhu, W.; Roy, R.; Pleasant, L.M.; Nichols, K.; Chao, P.C.; Xu, M.; Ye, P.D. 0.2-μm AlGaN/GaN High Electron-Mobility Transistors with Atomic Layer Deposition Al<sub>2</sub>O<sub>3</sub> Passivation. *IEEE Electron Device Lett.* 2013, 34, 744–746. [CrossRef]

- 21. Huang, S.; Jiang, Q.; Yang, S.; Zhou, C.; Chen, K.J. Effective Passivation of AlGaN/GaN HEMTs by ALD-Grown AlN Thin Film. *IEEE Electron Device Lett.* **2012**, *33*, 516–518. [CrossRef]

- Derluyn, J.; Boeykens, S.; Cheng, K.; Vandersmissen, R.; Das, J.; Ruythooren, W.; Degroote, S.; Leys, M.R.; Germain, M.; Borghs, G. Improvement of AlGaN/GaN high electron mobility transistor structures by in situ deposition of a Si3N4 surface layer. *J. Appl. Phys.* 2005, *98*, 054501-1–054501-6. [CrossRef]

- 23. Lu, X.; Ma, J.; Jiang, H.; Liu, C.; Lau, K.M. Low trap states in in situ SiN<sub>x</sub>/AlN/GaN metal-insulator-semiconductor structures grown by metal-organic chemical vapor deposition. *Appl. Phys. Lett.* **2014**, *105*, 102911-1–102911-4. [CrossRef]

- 24. Ma, J.; Lu, X.; Jiang, H.; Liu, C.; Lau, K.M. In situ growth of SiN<sub>x</sub> as gate dielectric and surface passivation for AlN/GaN heterostructures by metalorganic chemical vapor deposition. *Appl. Phys. Exp.* **2014**, *7*, 091002-1–091002-4. [CrossRef]

- Van Hove, M.; Kang, X.; Stoffels, S.; Wellekens, D.; Ronchi, N.; Vanagas, R.; Geens, K.; Decoutere, S. Fabrication and performance of au-free AlGaN/GaN-on-silicon power devices with Al<sub>2</sub>O<sub>3</sub> and Si<sub>3</sub>N<sub>4</sub>/Al<sub>2</sub>O<sub>3</sub> gate dielectrics. *IEEE Trans. Electron Devices* 2013, 60, 3071–3078. [CrossRef]

- 26. Moens, P.; Liu, C.; Banerjee, A.; Vanmeerbeek, P.; Coppens, P.; Ziad, H.; Constant, A.; Li, Z.; De Veleeschouwer, H.; Roig-Guitart, J.; et al. An industrial process for 650V rated GaN-on-Si power devices using in-situ SiN as a gate dielectric. In Proceedings of the 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 374–377.

- 27. Lu, X.; Ma, J.; Jiang, H.; Liu, C.; Xu, P.; Lau, K.M. Fabrication and characterization of gate-last self-aligned AlN/GaN MISHEMTs with in situ SiNx gate dielectric. *IEEE Trans. Electron Devices* **2015**, *62*, 1862–1869.

- Lu, X.; Yu, K.; Jiang, H.; Zhang, A.; Lau, K.M. Study of Interface Traps in AlGaN/GaN MISHEMTs Using LPCVD SiNx as Gate Dielectric. *IEEE Trans. Electron Device* 2017, 64, 824–831. [CrossRef]

- Yang, S.; Tang, Z.; Hua, M.; Xhang, Z.; Wei, J.; Lu, Y.; Chen, K. Investigation of SiNx and AlN passivation for AlGaN/GaN High-Electron-Mobility Transistors: Role of Interface Traps and Polarization Charges. *IEEE J. Electron Device Soc.* 2008, *8*, 358–364. [CrossRef]

- Menozzi, R. Reliability of GaN-Based HEMT devices. In Proceedings of the Conference on Optoelectronic and microelectronic Materials and Devices, Sydney, NSW, Australia, 28 July–1 August 2008; pp. 44–50.

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.