# Article Reliability Assessment of On-Wafer AlGaN/GaN HEMTs: The Impact of Electric Field Stress on the Mean Time to Failure

Surajit Chakraborty <sup>1</sup> and Tae-Woo Kim <sup>1,2,\*</sup>

<sup>2</sup> Department of Electrical and Computer Engineering, Texas Tech University, Lubbock, TX 79409, USA

\* Correspondence: twkim78@ulsan.ac.kr

**Abstract:** We present the mean time to failure (MTTF) of on-wafer AlGaN/GaN HEMTs under two distinct electric field stress conditions. The channel temperature ( $T_{ch}$ ) of the devices exhibits variability contingent upon the stress voltage and power dissipation, thereby influencing the longterm reliability of the devices. The accuracy of the channel temperature assumes a pivotal role in MTTF determination, a parameter measured and simulated through TCAD Silvaco device simulation. Under low electric field stress, a gradual degradation of  $I_{DSS}$  is noted, accompanied by a negative shift in threshold voltage ( $\Delta V_T$ ) and a substantial increase in gate leakage current ( $I_G$ ). Conversely, the high electric field stress condition induces a sudden decrease in  $I_{DSS}$  without any observed shift in threshold voltage. For the low and high electric field conditions, MTTF values of 360 h and 160 h, respectively, were determined for on-wafer AlGaN/GaN HEMTS.

Keywords: AlGaN/GaN HEMTs; electric field; stress voltage; mean time to failure; channel temperature

## 1. Introduction

The AlGaN/GaN transistors exhibit favorable attributes for high-frequency power applications owing to their substantial band gap of 3.4 eV, exceptional breakdown field around 3.5 MV/cm, low on-state resistance, and effective heat dissipation capabilities [1–5]. In the absence of doping, the AlGaN/GaN heterostructure demonstrates a significant conduction band discontinuity. This, when coupled with the influences of piezoelectric polarization and spontaneous polarization, gives rise to the creation of a high-density two-dimensional electron gas (2-DEG) [6–8]. These features make AlGaN/GaN HEMTs uniquely suited for demanding applications that require high-power handling, high-frequency operation, and robust performance even in extreme conditions [9-14]. These advanced devices have emerged as key components in the field of electronics and power electronics, offering a wide range of benefits that make them indispensable in numerous cutting-edge applications [15–18]. AlGaN/GaN HEMTs have revolutionized power electronics. Their ability to handle high voltages and currents efficiently, along with their high-speed switching capabilities, has made them ideal for applications like power amplifiers, DC–DC converters, and power supplies [19–22]. They enable the development of compact and energy-efficient power electronic systems [23]. In the realm of radio frequency (RF) and microwave electronics, AlGaN/GaN HEMTs offer exceptional high-frequency performance, low noise characteristics, and high-power output [24–27]. These transistors are critical components in radar systems, wireless communication infrastructure, and satellite communications [28,29].

The wide bandgap confers substantial robustness against diverse manifestations of electrical overstress, encompassing direct current (DC), electrostatic discharge (ESD), and radio frequency (RF) stressors [30–33]. Hence, ensuring reliability emerges as a pivotal concern necessitating meticulous consideration throughout the developmental or material growth phases [34]. The mean time to failure (MTTF) serves as a critical parameter in

Citation: Chakraborty, S.; Kim, T.-W. Reliability Assessment of On-Wafer AlGaN/GaN HEMTs: The Impact of Electric Field Stress on the Mean Time to Failure. *Micromachines* 2023, 14, 1833. https://doi.org/10.3390/ mi14101833

Academic Editor: Yu-Shyan Lin

Received: 31 August 2023 Revised: 15 September 2023 Accepted: 21 September 2023 Published: 26 September 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

assessing the longevity of devices within the context of long-term reliability. Subsequently, the mean time to failure (MTTF) can be extrapolated from the heightened test temperature to the standard operational temperature, typically hovering around 150 °C for gallium nitride (GaN) devices [7,35]. In terms of reliability categories, long-term reliability (around 1000 h according to JEDEC standard) at a three-temperature DC test is most used to determine device reliability [36]. Conducting measurements across various junction temperatures (at least three temperatures) facilitates the determination of activation energies ( $E_a$ ) through the application of the Arrhenius equation. Long-term high-power 50 V DC stress was induced on  $L_g = 0.5 \,\mu\text{m}$  devices with an output current of 150 mA/mm (7.5 W/mm) for a duration of 816 h at channel temperature  $T_{ch}$  = 280 °C, 300 °C, and 330 °C [37]. The initial drop in output drain current was observed at 24 h, and the period of stability was around 100–200 h. Beyond this point, the output current relative to time significantly decreased. After a comprehensive physical failure analysis, the emergence of crystallographic defects was ascertained within the entirety of the gate width in the AlGaN layer. This occurrence can be attributed to the manifestation of the inverse piezoelectric effect [38,39]. However, the analysis did not yield an estimation of the mean time to failure (MTTF).

The failure mechanism analysis of GaN-based HEMTs involves short-term reliability studies (<24 h), as conducted by various research groups [30,40]. Notably, hot-electron degradation has been well established in GaAs-based HEMTs, and similarly, the hot-electron effect remains a predominant degradation mechanism in GaN HEMTs. The aforementioned study investigated the hot-electron effect through DC short-term tests (<150 h) across diverse HEMT structures. The electroluminescence (EL) intensity exhibited a non-monotonic 'bell-shaped' trend when correlated with  $V_{GS}$  while maintaining the  $V_{DS}$  constant. Furthermore, a long-term accelerated test was conducted, spanning up to 3000 h, on a specific device at distinct bias points ( $V_{GS} = 0$  V,  $V_{DS} = 6$  V, (on state);  $V_{GS} = -9$  V,  $V_{DS} = 32$  V (off state);  $V_{GS} = -4$  V,  $V_{DS} = 25$  V (semi-on state)). Notably, under the semi-on state condition, a substantial degradation in transconductance ( $g_m$ ) was observed compared with the other conditions, indicating the presence of the hot-electron effect within the channel. In spite of a thorough examination of the degradation mechanism, the evaluation did not result in the computation of the mean time to failure (MTTF).

Numerous additional research groups have undertaken investigations involving threetemperature DC accelerated Arrhenius test aging, from which activation energies have been deduced [31,41,42]. High-temperature operating (HTO) tests were conducted by subjecting the devices to a consistent power dissipation of 6 W/mm. These tests were performed at varying channel temperatures of 204 °C, 232 °C, and 260 °C, all maintained under the same voltage condition ( $V_{DS}$  = 25 V), over an approximate duration of 3000 h [43]. However, a comprehensive analysis of activation energy and MTTF was notably absent from the study.

Under a consistent voltage condition of  $V_{DS} = 30$  V, a high-temperature operating life (HTOL) test was executed for approximately 2000 h. This test encompassed three distinct channel temperatures: 210 °C, 225 °C, and 250 °C. The outcomes revealed a mean time to failure (MTTF) of  $1.87 \times 10^6$  h at a temperature of 200 °C, along with activation energy ( $E_a$ ) of 1.8 eV [44]. An accurate estimation of the channel temperature is of paramount importance for determining the precise mean time to failure (MTTF) values in GaN HEMTs. Employing a constant bias of  $V_{DS} = 50$  V and a power dissipation rate of 4 W/mm, devices were subjected to stress testing at three distinct base temperatures:  $T_b = 160$  °C, 175 °C, and 190 °C. However, the resulting MTTF values diverged based on the peak channel temperature (measured through Raman thermography) and the average temperature (measured via IR thermography). Specifically, two distinct MTTF values emerged:  $10^9$  h and  $10^6$  h [45].

Given the array of proposed stressors, degradation mechanisms, and associated degradation signatures, it is important to distinguish the precise stressors responsible for inducing particular effects. All prior investigations were carried out on packaged GaN HEMT devices. Limited long-term reliability studies exist on GaN epitaxial wafers or on-wafer devices [46]. In the current study, we investigated the extraction of activation energy and MTTF values under two distinct stress conditions, denoted as high and low electric field stress in on-wafer devices.

Assessing the reliability of gallium nitride high-electron-mobility transistors (GaN HEMTs) under various electric field stress conditions is crucial for several reasons: Understanding how GaN HEMTs behave under different electric field stress conditions allows for the optimization of their performance and operational lifetime [47,48]. By identifying stress conditions that may lead to degradation, manufacturers can develop strategies to mitigate these effects and design devices that operate more reliably and durably. As we mentioned previously, GaN HEMTs are often used in high-power, high-frequency, and critical applications such as aerospace, defense, telecommunications, and power electronics. In these applications, device failures can have serious consequences, including system downtime, mission failures, or costly repairs. Assessing reliability helps prevent unexpected failures and ensures the uninterrupted operation of these systems [49,50]. In some applications, GaN HEMTs are used in safety-critical systems, where their failure could pose significant risks to human safety or the environment [51–56]. Reliability assessments under different stress conditions help identify potential failure modes and enable the implementation of safety measures and redundancies to mitigate these risks.

The paper is structured as follows: Section 2 presents the materials and methods employed, Section 3 encompasses the results and subsequent discussion, and Section 4 encapsulates the concluding remarks.

## 2. Materials and Methods

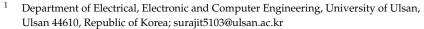

The epitaxial layer structures were synthesized utilizing a low-pressure metal–organic chemical vapor deposition (MOCVD) technique on 3-inch sapphire wafers measuring 430  $\mu$ m in thickness. This epitaxial configuration comprised an Al<sub>0.25</sub>Ga<sub>0.75</sub>N barrier layer (20 nm), a Ga-polarity GaN channel layer (150 nm), and a high-resistance GaN layer (2.4  $\mu$ m) positioned atop the sapphire substrate. The schematic and process flow can be observed in Figure 1a,b, respectively. The device fabrication encompassed mesa isolation etching, the establishment of source–drain ohmic contacts, and gate patterning. Mesa isolation etching was executed employing a reactive ion etching (RIE) system. Following this, standard Ti/Al/Ni/Au (25/160/40/100 nm) metallization was applied to the source and drain regions to form ohmic contacts. These contacts were then subjected to rapid thermal annealing (RTA) at 830 °C for 30 s within an N<sub>2</sub> environment, facilitating the formation of contacts on the AlGaN/GaN epi-structure. Metallization was achieved through the lift-off technique. Subsequently, photolithography was employed to pattern the Schottky gate contacts, composed of Ni/Au (20/300 nm), were fabricated using e-beam evaporation. For surface passivation, an Al<sub>2</sub>O<sub>3</sub> layer (3 nm) was deposited.

Figure 1. (a) Fabrication process flow; (b) schematic of AlGaN/GaN HEMTs.

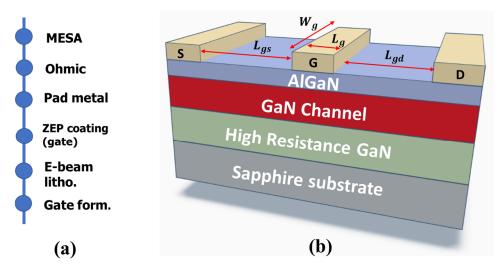

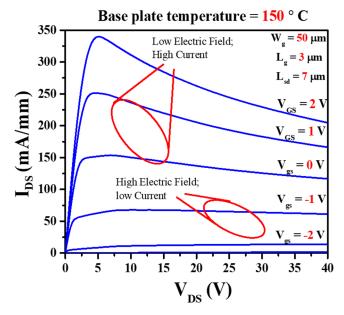

Figure 2 represents output characteristics of GaN HEMTs device of gate length,  $L_g = 3 \ \mu m$ , source to drain distance,  $L_{sd} = 7 \ \mu m$  and gate width,  $W_g = 50 \ \mu m$ . The output characteristics show that at very high drain voltage ( $V_{DS} > 20 \ V$ ) with an increase of gate voltage from  $V_{GS} = -1 \ V$  to 2 V leads to a decrease in output drain current ( $I_{DSS}$ ) because of self-heating effects [57]. To gain insights into the influence of temperature and characteristics on stress performance and electrical behavior, we conducted evaluations using a BA1500 and a 4155C semiconductor parameter analyzer (Keysight Technologies, Santa Rosa, CA, USA). These instruments were linked to a probe station (MS TECH 5500) (MSTECH, Gyeonggi, Republic of Korea) equipped with a temperature-controlled (Temptronic TP03000) (inTEST Thermal Solutions GmbH, Deutschland, Germany) heating plate, ensuring precise temperature control during the I–V (current–voltage) characteristic measurements. The experimental setup and characterization procedures of the devices are displayed in Figure 3.

**Figure 2.** Output characteristics at base plate temperature 150 °C represent the stress zones of low electric field and high electric field.

Figure 3. Experimental setup details and characterization procedures.

#### MTTF Determination Method

Given the fact that many applications demand device lifetimes spanning several years, accelerated-life tests serve as essential tools for efficiently gathering reliability data within

a practical timeframe. Among the myriad factors used for accelerating degradation in electronic devices, temperature emerges as one of the foremost contributors, as substantiated by extensive historical evidence within the semiconductor industry. One common approach to modeling semiconductor device reliability is to use the Arrhenius model. This model is based on the assumption that the rate of device failures is exponentially related to temperature and can be expressed as follows:

$$\lambda = Ae^{\left(\frac{E_a}{kT}\right)} \tag{1}$$

where  $\lambda$  is the failure rate, A is a material constant,  $E_a$  is the activation energy (a measure of the energy barrier for failure mechanisms), k is the Boltzmann constant, and T is the absolute temperature (in Kelvin).

This equation outlines the connection between temperature and the rate at which the device degrades due to a specific failure mechanism. The semiconductor industry has widely embraced this equation as a guiding principle for overseeing device operation under diverse temperature conditions. The Arrhenius model allows for the determination of an acceleration factor (*AF*), which relates the failure rate at elevated stress conditions ( $T_{stress}$ ) to the failure rate at normal operating conditions ( $T_{normal}$ ):

$$AF = e^{\left(\frac{E_a}{kT}\right)\left(\frac{1}{T_{normal}} - \frac{1}{T_{Stress}}\right)}$$

(2)

One crucial assumption in this methodology is that failure mechanisms are thermally activated, and the Arrhenius model accurately describes the relationship between temperature and failure rate. The accuracy of MTTF calculations relies on the validity of the acceleration factor and the assumption that failure mechanisms under accelerated testing conditions are representative of those under normal operating conditions. The channel temperature ( $T_{ch}$ ) of the device plays a vital role in determining the activation energy and acceleration factor. Temperature variations can significantly influence device reliability, so precise temperature measurements and control are essential during accelerated testing. Accurate measurement and control of channel temperature are critical, as temperature variations directly impact device reliability and influence the activation energy used in the model. The methodology also assumes that failure mechanisms are thermally activated and can be accelerated under stress conditions, making the calculated MTTF values relevant to real-world device performance.

In this study, we delineate two distinct stress zones, each characterized by specific combinations of high current and low electric field, as well as low current and high electric field. To comprehensively investigate these zones, we carefully selected specific bias conditions. Specifically, we opted for two distinct bias zones: one at a low voltage ( $V_{DS} = 10$  V) and another at a higher voltage ( $V_{DS} = 25$  V), each accompanied by power dissipation rates of 2 W/mm and 1.25 W/mm, respectively. These selected bias parameters are concisely summarized in Table 1. Additionally, we conducted experiments at three varying base temperatures:  $T_b = 150$  °C, 170 °C, and 190 °C. The determination of channel temperature for each bias condition is discussed in detail within the Results and Discussion section of this study.

Table 1. Selected test condition for determination of MTTF values.

| Sample<br>Quantity | Stress Voltage,<br>(V <sub>DS</sub> (V)) | Current,<br>(I <sub>DS</sub> (mA/mm)) | Power,<br>(P (W/mm)) |

|--------------------|------------------------------------------|---------------------------------------|----------------------|

| 5                  | 10                                       | 200                                   | 2                    |

| 5                  | 25                                       | 50                                    | 1.25                 |

## 3. Results

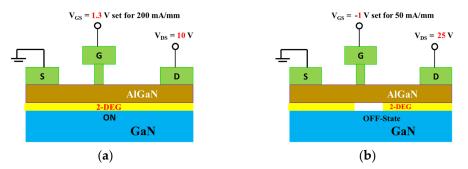

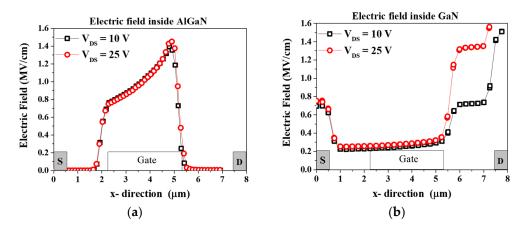

Figure 4a,b represent the bias stress condition of low electric field ( $V_{DS}$  = 10 V and  $V_{GS}$  = 1.3 V set for 200 mA/mm, power dissipation, P = 2 W/mm) and high electric field  $(V_{DS} = 25 \text{ V} \text{ and } V_{GS} = -1 \text{ V} \text{ set for 50 mA/mm, power dissipation, P} = 1.25 \text{ W/mm}).$ Under the low electric field stress condition, the device operates in a fully on-state condition, and a conspicuous self-heating effect is evident in the output characteristics (Figure 2). Consequently, this scenario closely resembles a high-power state condition. Conversely, during the high electric field stress condition, the device is in an off state, resulting in a minimal self-heating effect. This aligns with a high-voltage state in the off-state mode. Figure 5a shows the electric field simulation of stress voltage  $V_{DS}$  = 10 V and 25 V. A negligible electric field variation is evident inside the AlGaN barrier. Figure 5b illustrates the electric field simulation inside the GaN channel. At the gate edge to the drain side, the electric field increased 1.2 times higher at  $V_{DS} = 25$  V than at  $V_{DS} = 10$  V. As we mentioned above, stress condition  $V_{DS}$  = 25 V,  $V_{GS}$  = -1 V is in the off-state mode. Therefore, a negative voltage is applied to the gate of the GaN HEMT. This negative voltage creates a strong electric field that pushes electrons away from the channel region. The high electric field in the off state extends through the GaN material and depletes the 2DEG, preventing the flow of electrons in the channel. In the on-state condition ( $V_{DS} = 10$  V,  $V_{GS} = 1.3$  V), a less negative (or even positive) voltage is applied to the gate of the GaN HEMT. This reduces the electric field across the device. The reduced electric field allows the 2DEG to accumulate or populate near the interface between the GaN and AlGaN layers.

Figure 4. (a) Bias condition for low electric field and (b) high electric field region.

**Figure 5.** (a) Electric field simulation using Silvaco TCAD inside AlGaN barrier and (b) inside GaN channel.

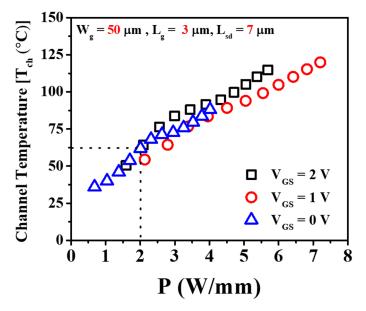

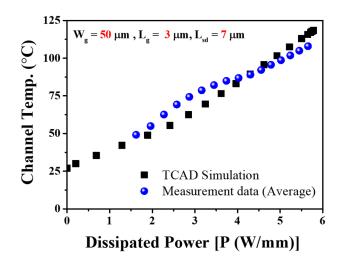

The channel temperatures were computed using the DC or electrical method as outlined in Reference [58] and are illustrated in Figure 6 for the device characterized by a gate length,  $L_g = 3 \mu m$ ; source-to-drain distance,  $L_{sd} = 7 \mu m$ ; and gate width,  $W_g = 50 \mu m$ . Across a range of gate voltages, specifically from  $V_{GS} = 0$  V to 2 V, the disparity in channel temperature ( $T_{ch}$ ) remained negligible. For 2 W/mm and 1.25 W/mm power dissipation,

Figure 6. Channel temperature variation relative to the power dissipation of GaN HEMTs.

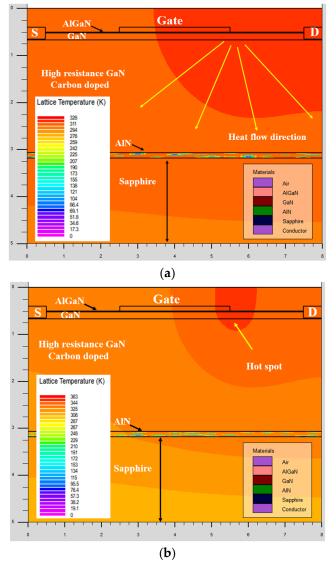

TCAD simulations were conducted to verify the channel temperature against the measurement data, as presented in Figure 7.

In the context of TCAD (technology computer-aided design) simulation, specific mesh settings were defined for precise modeling. The mesh width was established at 50 microns, with the primary spacing in the x-plane set at 0.25 µm for the source and drain metal regions. Similarly, the mesh spacing for the source-to-gate  $(L_{sg})$  and gate-to-drain  $(L_{od})$  regions was set at 0.25  $\mu$ m. In the y-plane, the meshing ranged from 0 to 0.50  $\mu$ m, with a spacing of 0.1 µm. This area covered the "air" region (region number 1). Beyond that, the AlGaN barrier (region number 2) extended from 0.50 to 0.520 μm, with an aluminum composition of 0.25% and a mesh spacing of 0.01  $\mu$ m. The GaN channel (region number 3) spanned from 0.520 to 0.670  $\mu$ m, also with a mesh spacing of 0.01  $\mu$ m. The buffer region (region number 4) ranged from 0.670 to 3.070 µm and was uniformly doped with carbon (p-type), maintaining a mesh spacing of 0.01 µm. The AlN nucleation layer (region number 5) was extremely thin, from 3.070 to  $3.018 \,\mu\text{m}$ . Finally, the sapphire substrate (region number 6) was in the range from  $3.180 \,\mu\text{m}$  to the end of the device. Three electrodes were defined as source (y·min = 0.40  $\mu$ m, y·max = 0.65  $\mu$ m), drain (y·min = 0.40  $\mu$ m, y·max = 0.65  $\mu$ m), and gate (y·min = 0.40  $\mu$ m, y·max = 0.50  $\mu$ m). The work functions for these electrodes were specified as 5.20 eV, 4.0 eV, and 4.0 eV for gate, source, and drain, respectively.

In the simulation process, the high-field mobility was computed utilizing the Farahmand modified Caughey–Thomas (FMCT) and GANSAT models, while the low-field mobility was determined using the Albrecht model. Various physical models, including Schottky–Read–Hall (SRH), Fermi–Dirac statistics (FLDMOB), CONMOB, Fermi, and KP, were considered in the model definition. The polarization parameter was set to 0.952.

To account for self-heating effects, a lattice temperature model (lat. temp) was incorporated for channel temperature estimation in TCAD modeling, where the substrate is stated as "thermalcontact num = 1", with the specific region defined as region number 5, external temperature (ext.temp) set as 300 K, and adjusted thermal resistance ( $R_{th} = 1/\alpha$ ).

Additionally, the Selberherr impact ionization model (Impact selb) parameters, namely an1, an2, bn1, bn2, ap1, ap2, bp1, and bp2, were set to specific values, namely  $2.9 \times 10^8$ ,  $2.9 \times 10^8$ ,  $3.4 \times 10^7$ ,  $3.4 \times 10^7$ ,  $2.9 \times 10^8$ ,  $2.9 \times 10^8$ ,  $3.4 \times 10^7$ , and  $3.4 \times 10^7$ , respectively. These parameters are essential for accurately modeling the device's behavior and performance in the simulation environment.

Figure 7. (a) TCAD simulation of the device at  $V_{DS}$  = 10 V and (b)  $V_{DS}$  = 25 V.

Figure 7a depicts the simulation results for a device under  $V_{GS} = 0$  V and  $V_{DS} = 10$  V conditions while maintaining a base plate temperature of  $T_b = 300$  K (27 °C). Notably, the highest channel temperature recorded was 327 K (54 °C) in close proximity to the gate edge.

Similarly, when the device was biased at  $V_{DS} = 25$  V with the same gate voltage,  $V_{GS} = 0$  V, the corresponding channel temperature escalated to 360 K (87 °C), as illustrated in Figure 7b. This change corresponds to an approximate temperature increase of 33 °C. Consequently, the temperature variation within the channel is contingent upon the stress voltage conditions. To determine the changes in channel temperature ( $T_{ch}$ ) resulting from fluctuations in drain currents, we conducted experiments to observe the behavior of drain currents under different temperature conditions. Our findings indicated a consistent linear decrease in drain current across various temperature settings [29]. Additionally, we computed power levels ( $I_{DS} \times V_{DS}$ ) from the output characteristics of the device. Subsequently, we normalized the drain current data relative to different temperatures and power levels. These normalized values were used to construct graphs in Figure 8 (measurement data), representing the relationship between channel temperatures and power levels.

**Figure 8.** Measurement data (averaged from all three-gate voltages and TCAD simulation) show very close agreement to determine channel temperature.

Notably, this exhibits a remarkable congruence between the TCAD simulation outcomes and our measurement data.

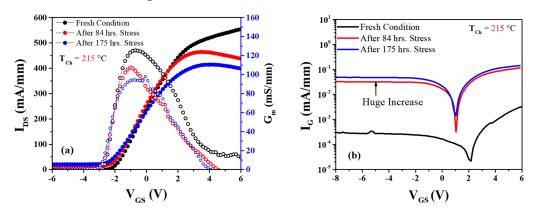

#### 3.1. Low Electric Field with High Current Stress Experiment

Figure 9a presents the transfer characteristics (characterization at  $V_{DS} = 10$  V) at low electric field stress condition at  $V_{DS} = 10$  V and output current level maintained to  $I_{DS} = 200$  mA/mm for power dissipation of P = 2 W/mm. At a constant base plate temperature of  $T_b = 150$  °C the channel temperature was estimated as  $T_{ch} = 215$  °C. After 84 h of stress,  $I_{DS}$  and  $g_m$  dropped around 30 mA/mm and 18 mS/mm, respectively. At the same time, gate leakage current  $I_G$  (defined at  $V_{GS} = -10$  V,  $V_{DS} = 10$  V) increased from  $3.3 \times 10^{-4}$  to 0.034 mA/mm, as shown in Figure 8b. The threshold voltage negatively shifted around  $\Delta V_T = -0.16$  V. After 175 h of stress,  $I_{DS}$  and  $g_m$  decreased more around 38 mA/mm and 31 mS/mm, respectively, from the initial value (Figure 8). At the same point, the leakage current increased from the initial value of  $3.3 \times 10^{-4}$  to 0.051 mA/mm, and the threshold voltage shift was around  $\Delta V_T = -0.31$  V from the initial value.

**Figure 9.** (a) Transfer characteristics after and before stress voltage  $V_{DS} = 10$  V; (b) Schottky characteristics depict gate leakage current after stress at the channel temperature,  $T_{ch} = 215$  °C.

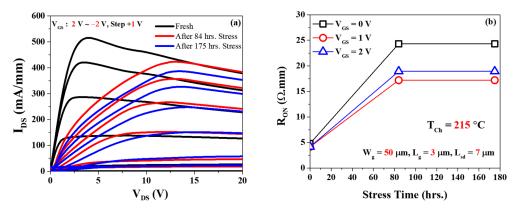

Figure 10a shows the output characteristics before and after stress of 84 h and 175 h. On-resistance (Ron) increased around  $\Delta \text{Ron} = 20 \ \Omega \cdot \text{mm}$  at  $V_{GS} = 0 \text{ V}$  after 84 h of stress, and no change was observed until 175 h. The failure time is defined at  $I_{DSS}$  degradation up to 15%. All the degradation in the other two base plate temperatures ( $T_b = 170 \ ^\circ\text{C}$  and 190  $^\circ\text{C}$ ) are depicted in Table 2.

**Figure 10.** (a) Output characteristics after and before the stress of  $V_{DS} = 10$  V; (b) on-resistance characteristics after and before stress voltage at  $V_{DS} = 10$  V.

| Base Plate<br>Temperature $(T_b)$ °C | Corresponding<br>Channel Temperature<br>(T <sub>ch</sub> ) °C | Condition      | Lifetime (h)<br>(15% Degradation) |

|--------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|

| 150                                  | 215                                                           | VDS = 10 V,    | 175                               |

| 170                                  | 230                                                           | ID = 200 mA/mm | 147                               |

| 190                                  | 240                                                           | P = 2 W/mm     | 120                               |

Table 2. Lifetime calculation at different base plate temperatures for low electric field stress.

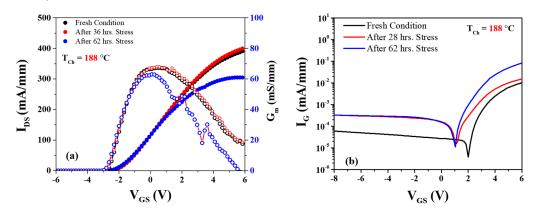

## 3.2. High Electric Field with Low Current Stress Experiment

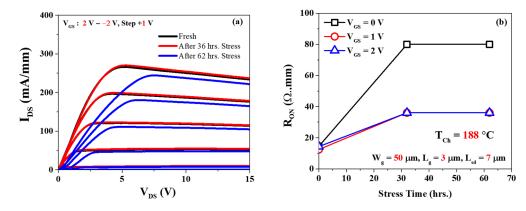

Figure 11a shows the transfer characteristics at high electric field stress  $V_{DS} = 25$  V,  $I_{DS} = 50$  mA/mm, and the power dissipation set at 1.25 W/mm. After 36 h of stress, there seemed a slight increase in the output current from 387 mA/mm to 401 mA/mm at the base plate temperature of  $T_b = 150$  °C. The maximum transconductance (g<sub>max</sub>) also showed negligible change. But at the same time, the leakage current I<sub>G</sub> increased from  $9.12 \times 10^{-5}$  mA/mm to 3.86 mA/mm, whereas no shift was observed in the threshold voltage ( $\Delta V_T$ ), as shown in Figure 11b. After 62 h of stress, the output current ( $I_{DS}$ ) decreased around 84 mA/mm from its initial value, and  $g_m$  also decreased from 337 mS/mm to 313 mS/mm (almost 24 mS/mm). However, no change was observed in the leakage current. Table 3 illustrates the degradation observed at the other two base plate temperatures, namely  $T_b = 170$  °C and 190 °C.

**Figure 11.** (a) Transfer characteristics after and before stress voltage  $V_{DS}$  = 25 V; (b) Schottky characteristics depict gate leakage current after stress at the channel temperature 188 °C.

| Base Plate<br>Temperature ( $T_b$ ) °C | Corresponding<br>Channel Temperature<br>(T <sub>ch</sub> ) °C | Condition                | Lifetime (h)<br>(15% Degradation) |

|----------------------------------------|---------------------------------------------------------------|--------------------------|-----------------------------------|

| 150                                    | 188                                                           | V <sub>DS</sub> = 25 V,  | 62                                |

| 170                                    | 208                                                           | $I_D = 50 \text{ mA/mm}$ | 36                                |

| 190                                    | 228                                                           | P = 1.25 W/mm            | 15                                |

Table 3. Lifetime calculation at different base plate temperatures for high electric field stress.

Figure 12a illustrates the output characteristics prior to and following stress periods of 36 h and 62 h. After 32 h of stress,  $I_{DSS}$  exhibited an increase, but this trend reversed after 62 h of stress. Notably, the on-state resistance ( $R_{on}$ ) demonstrated an increase of approximately  $\Delta R_{on} = 60 \ \Omega \cdot mm$  at  $V_{GS} = 0 \ V$  after 32 h of stress, with no noticeable alteration observed until the 62 h stress point. The degradation observed at the other two base plate temperatures, i.e.,  $T_b = 208 \ ^{\circ}C$  and 228  $^{\circ}C$ , is depicted in Table 3.

**Figure 12.** (a) Output characteristics before and after the stress of  $V_{DS} = 25$  V; (b) on-resistance characteristics before and after stress voltage at  $V_{DS} = 25$  V.

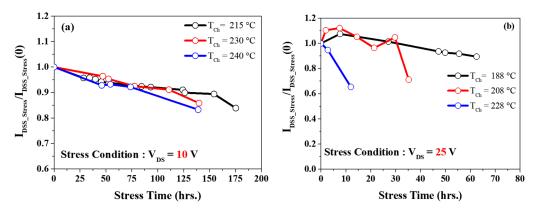

Figure 13a demonstrates the degradation of  $I_{dss}$  (which is defined at  $V_{DS} = 5$  V and  $V_{GS} = 2$  V) in three different channel temperatures calculated for the  $V_{DS} = 10$  V bias condition. No abrupt degradation behavior of  $I_{dss}$  was observed in high temperatures. However, under high-stress voltage conditions ( $V_{DS} = 25$  V), the device's stability was compromised, lasting no more than 15 h at  $T_{ch} = 228$  °C, as depicted in Figure 13b.

**Figure 13.** (a)  $I_{DSS}$  degradation at low electric field stress voltage  $V_{DS} = 10$  V and (b) high electric stress voltage  $V_{DS} = 25$  V.

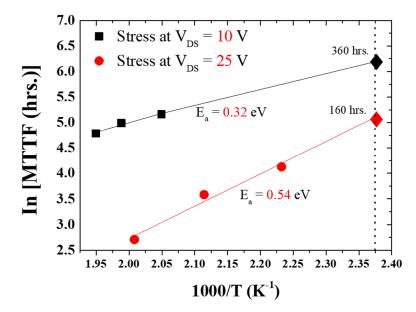

Figure 14 illustrates the *MTTF* values calculated for three different channel temperatures under specific voltage stress conditions. To calculate the activation energy, the well-known Arrhenius equation of mean time to failure (*MTTF*) can be expressed as follows [26]:

$$MTTF = e^{-\left(\frac{Ea}{KT}\right)}$$

$$\ln[MTTF] = -\frac{E_a}{kT}$$

(3)

Here, MTTF = mean time to failure; k = Boltzmann constant, 8.6173 × 10<sup>-5</sup> eV K<sup>-1</sup>; and  $E_a$  = activation energy (eV). From the slope of Equation (3), activation energy ( $E_a$ ) can be calculated.

Figure 14. Mean time to failure (*MTTF*) analysis of two different electric field conditions.

Under the low electric field stress condition ( $V_{DS}$  = 10 V), the calculated activation energy was  $E_a = 0.32$  eV, yielding an extrapolated lifetime MTTF = 360 h. Conversely, under the high electric field stress condition ( $V_{DS} = 25$  V), the estimated activation energy was  $E_a = 0.54$  eV, resulting in MTTF = 160 h. The possible degradation or failure at low electric field and high current stress is related to the diffusion process ( $E_a = 0.32 \text{ eV}$ ). This diffusion can lead to the formation of conductive paths or short circuits within the device, increasing leakage current and reducing the breakdown voltage. For the high electric field and low current stress, this degradation is related to the hot-electron effect or electron trapping ( $E_a = 0.54 \text{ eV}$ ) [59]. The obtained mean time to failure (MTTF) values for GaN highelectron-mobility transistors (HEMTs) are significant indicators of device reliability and can provide insights into their performance under different electric field stress conditions. In general, MTTF represents the expected time for a device to fail under specified conditions. It is a critical parameter for assessing device reliability. We calculated MTTF values for on-wafer GaN HEMTs under both low ( $V_{DS} = 10$  V) and high ( $V_{DS} = 25$  V) electric field stress conditions. These values indicate how long, on average, the devices can be expected to operate before a significant number of them fail. The lower MTTF under high electric field stress (160 h) suggests that the devices are more prone to failure when subjected to higher voltage stress, which is consistent with accelerated aging in high-stress conditions.

Our MTTF values were validated only for on-wafer/bare-wafer devices. The MTTF for on-wafer devices typically represents the reliability of the semiconductor material itself, without considering packaging and external factors. On the other hand, the MTTF for packaged devices takes into account not only the intrinsic reliability of the semiconductor material but also the effects of packaging, assembly, and the device's operational environment. Packaged devices typically have a longer MTTF than bare wafers because their packaging contributes to their robustness and resilience. In summary, comparing the MTTF of a bare-wafer device with a packaged device is not a straightforward apples-toapples comparison.

#### 4. Conclusions

The presentation of MTTF data for on-wafer devices was contingent upon specific electric field conditions. The accurate determination of channel temperature assumes a critical role in the precise estimation of MTTF values. Furthermore, degradation parameters exhibited variations based on the specific stress voltage or electric field conditions. Moreover, when calculating MTTF for on-wafer devices, distinct electric field conditions yielded different values. These intricate details merit thorough consideration as they hold the potential to significantly enhance the long-term reliability of AlGaN/GaN HEMTs.

**Author Contributions:** Conceptualization, T.-W.K. and S.C.; resources, S.C.; data curation, S.C.; writing—original draft preparation, T.-W.K.; review and editing, S.C.; visualization, T.-W.K.; supervision. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT under Grant NRF-2022M3I8A108544912.

Data Availability Statement: Data are available upon request from the corresponding author.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- Chakraborty, S.; Kim, T.-W. Comprehensive Schottky Barrier Height Behavior and Reliability Instability with Ni/Au and Pt/Ti/Pt/Au on AlGaN/GaN High-Electron-Mobility Transistors. *Micromachines* 2022, 13, 84. [CrossRef] [PubMed]

- Zagni, N.; Gao, V.Z.; Verzellesi, G.; Chini, A.; Pantellini, A.; Natali, M.; Lucibello, A.; Latessa, L.; Lanzieri, C.; De Santi, C.; et al. Mechanisms of Step-Stress Degradation In Carbon-Doped 0.15 µm Algan/Gan Hemts for Power RF Applications. *IEEE Trans. Electron Devices* 2023. [CrossRef]

- Zanoni, E.; Rampazzo, F.; De Santi, C.; Gao, Z.; Sharma, C.; Modolo, N.; Verzellesi, G.; Chini, A.; Meneghesso, G.; Meneghini, M. Failure Physics and Reliability of GaN-Based HEMTs for Microwave and Millimeter-Wave Applications: A Review of Consolidated Data and Recent Results. *Phys. Status Solidi. A* 2022, 219, 2100722. [CrossRef]

- Bisi, D.; Meneghini, M.; de Santi, C.; Chini, A.; Dammann, M.; Brückner, P.; Mikulla, M.; Meneghesso, G.; Zanoni, E. Deep-Level Characterization in GaN HEMTs-Part I: Advantages and Limitations of Drain Current Transient Measurements. *IEEE Trans. Electron. Devices* 2013, 60, 3166–3175. [CrossRef]

- Meneghini, M.; De Santi, C.; Abid, I.; Buffolo, M.; Cioni, M.; Khadar, R.A.; Nela, L.; Zagni, N.; Chini, A.; Medjdoub, F.; et al. GaN-based power devices: Physics, reliability, and perspectives. *J. Appl. Phys.* 2021, 130, 181101. [CrossRef]

- Amir, W.; Shin, J.-W.; Shin, K.-Y.; Chakraborty, S.; Cho, C.-Y.; Kim, J.-M.; Lee, S.-T.; Hoshi, T.; Tsutsumi, T.; Sugiyama, H.; et al. Performance Enhancement of AlGaN/GaN HEMT via Trap-State Improvement Using O2 Plasma Treatment. *IEEE Trans. Electron.* Devices 2013, 70, 2988–2993. [CrossRef]

- Chakraborty, S.; Kim, T.-W. Investigation of Mean-Time-to-Failure Measurements from AlGaN/GaN High-Electron-Mobility Transistors Using Eyring Model. *Electronics* 2021, 10, 3052. [CrossRef]

- 8. Chakraborty, S.; Amir, W.; Kwon, H.-M.; Kim, T.-W. New Methodology for Parasitic Resistance Extraction and Capacitance Correction in RF AlGaN/GaN High Electron Mobility Transistors. *Electronics* **2023**, *12*, 3044. [CrossRef]

- Haziq, M.; Falina, S.; Manaf, A.A.; Kawarada, H.; Syamsul, M. Challenges and Opportunities for High-Power and High-Frequency AlGaN/GaN High-Electron-Mobility Transistor (HEMT) Applications: A Review. *Micromachines* 2022, 13, 2133. [CrossRef]

- Teo, K.H.; Zhang, Y.; Chowdhury, N.; Rakheja, S.; Ma, R.; Xie, Q.; Yagyu, E.; Yamanaka, K.; Li, K.; Palacios, T. Emerging GaN technologies for power, RF, digital, and quantum computing applications: Recent advances and prospects. *J. Appl. Phys.* 2021, 130, 160902. [CrossRef]

- 11. Harrouche, K.; Kabouche, R.; Okada, E.; Medjdoub, F. High Performance and Highly Robust AlN/GaN HEMTs for Millimeter-Wave Operation. *IEEE J. Electron Devices* 2019, 7, 1145–1150. [CrossRef]

- 12. Raman, A.; Chattopadhyay, S.P.; Ranjan, R.; Kumar, N.; Kakkar, D.; Sharma, R. Design and Investigation of Dual Dielectric Recessed-Gate AlGaN/GaN HEMT as Gas sensor Application. *Trans. Electr. Electron. Mater.* **2022**, *23*, 618–623. [CrossRef]

- 13. Ranjan, R.; Kashyap, N.; Raman, A. High-performance dual-gate-charge-plasma-AlGaN/GaN MIS-HEMT. *Appl. Phys. A* 2020, 126, 169. [CrossRef]

- 14. Shivangi, S.; Ashish, R.; Sarabdeep, S.; Naveen, K. Design and Analysis of Source Engineered with High Electron Mobility Material Triple Gate Junctionless Field Effect Transistor. *J. Nanoelectron. Optoelectron.* **2019**, *14*, 825–832. [CrossRef]

- Li, H.; Yao, C.; Fu, L.; Zhang, X.; Wang, J. Evaluations and applications of GaN HEMTs for power electronics. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 563–569. [CrossRef]

- 16. Zhong, Y.; Zhang, J.; Wu, S.; Jia, L.; Yang, X.; Liu, Y.; Zhang, Y.; Sun, Q. A review on the GaN-on-Si power electronic devices. *Fundam. Res.* **2022**, *2*, 462–475. [CrossRef]

- 17. Musumeci, S.; Barba, V. Gallium Nitride Power Devices in Power Electronics Applications: State of Art and Perspectives. *Energies* **2023**, *16*, 3894. [CrossRef]

- De Santi, C.; Buffolo, M.; Rossetto, I.; Bordignon, T.; Brusaterra, E.; Caria, A.; Chiocchetta, F.; Favero, D.; Fregolent, M.; Masin, F.; et al. Review on the degradation of GaN-based lateral power transistors. *E-Prime Adv. Electr. Eng. Electron. Energy* 2021, 1, 100018. [CrossRef]

- Gao, Y.; Huang, A.Q. Feasibility Study of AlGaN/GaN HEMT for Multi-megahertz DC/DC Converter Applications. In Proceedings of the 2006 CES/IEEE 5th International Power Electronics and Motion Control Conference, Shanghai, China, 14–16 August 2006; pp. 1–3. [CrossRef]

- 20. Kozak, J.P.; Zhang, R.; Song, Q.; Liu, J.; Saito, W.; Zhang, Y. True Breakdown Voltage and Overvoltage Margin of GaN Power HEMTs in Hard Switching. *IEEE Electron. Device Lett.* **2021**, *42*, 505–508. [CrossRef]

- 21. Imada, T.; Kanamura, M.; Kikkawa, T. Enhancement-mode GaN MIS-HEMTs for power supplies. In Proceedings of the 2010 International Power Electronics Conference—ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 1027–1033. [CrossRef]

- 22. Ma, C.-T.; Gu, Z.-H. Review of GaN HEMT Applications in Power Converters over 500 W. Electronics 2019, 8, 1401. [CrossRef]

- Zhang, K.; Chen, X.; Peng, Z.; Chen, Y.; Wei, G.; Ze, S. High-Efficiency, High-Power Density and Wide-Range Power Supply Design Based on GaN HEMT. In Proceedings of the 2022 International Conference on Power Energy Systems and Applications (ICoPESA), Singapore, 25–27 February 2022; pp. 101–108. [CrossRef]

- Micovic, M.; Brown, D.F.; Regan, D.; Wong, J.; Tang, Y.; Herrault, F.; Santos, D.; Burnham, S.D.; Tai, J.; Prophet, E.; et al. High frequency GaN HEMTs for RF MMIC applications. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; IEEE: New York, NY, USA, 2016.

- 25. Ahn, H.; Ji, H.; Kang, D.; Son, S.-M.; Lee, S.; Han, J. A 26–30 GHz GaN HEMT Low-Noise Amplifier Employing a Series Inductor-Based Stability Enhancement Technique. *Electronics* **2022**, *11*, 2716. [CrossRef]

- 26. Jarndal, A.; Arivazhagan, L.; Almajali, E.; Majzoub, S.; Bonny, T. Impact of AlGaN Barrier Thickness and Substrate Material on the Noise Characteristics of GaN HEMT. *IEEE J. Electron Devices Soc.* **2022**, *10*, 696–705. [CrossRef]

- Niida, Y.; Kamada, Y.; Ohki, T.; Ozaki, S.; Makiyama, K.; Minoura, Y.; Okamoto, N.; Sato, M.; Joshin, K.; Watanabe, K. 3.6 W/mm high power density W-band InAlGaN/GaN HEMT MMIC power amplifier. In Proceedings of the 2016 IEEE Topical Conference on Power Amplifiers for Wireless and Radio Applications (PAWR), Austin, TX, USA, 24–27 January 2016; pp. 24–26. [CrossRef]

- 28. Sano, S.; Ebihara, K.; Yamamoto, T.; Sato, T.; Miyazawa, N. GaN HEMTs for wireless communication. SEI Tech. Rev. 2018, 85, 65.

- Cidronali, A.; Pagnini, L.; Collodi, G.; Passafiume, M. A Highly Linear Ka-Band GaN-on-Si Active Balanced Mixer for Radar Applications. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2022, 69, 4453–4464. [CrossRef]

- 30. Meneghesso, G.; Verzellesi, G.; Danesin, F.; Rampazzo, F.; Zanon, F.; Tazzoli, A.; Meneghini, M.; Zanoni, E. Reliability of GaN High-Electron-Mobility Transistors: State of the Art and Perspectives. *IEEE Trans. Electron. Devices* **2008**, *8*, 332–343. [CrossRef]

- Zanoni, E.; Meneghini, M.; Chini, A.; Marcon, D. AlGaN/GaN-Based HEMTs Failure Physics and Reliability: Mechanisms Affecting Gate Edge and Schottky Junction. *IEEE Trans. Electron. Devices* 2013, 60, 3119–3131. [CrossRef]

- 32. Faqir, M.; Verzellesi, G.; Meneghesso, G.; Zanoni, E.; Fantini, F. Investigation of High-Electric-Field Degradation Effects in AlGaN/GaN HEMTs. *IEEE Trans. Electron. Devices* 2008, *55*, 1592–1602. [CrossRef]

- 33. Sozza, A.; Dua, C.; Morvan, E.; diForte-Poisson, M.A.; Delage, S.; Rampazzo, F.; Tazzoli, A.; Danesin, F.; Meneghesso, G.; Zanoni, E.; et al. Evidence of traps creation in GaN/AlGaN/GaN HEMTs after a 3000 hour on-state and off-state hot-electron stress. In Proceedings of the IEEE InternationalElectron Devices Meeting 2005, IEDM Technical Digest, Washington, DC, USA, 5 December 2005. [CrossRef]

- 34. Amano, H.; Baines, Y.; Beam, E.; Borga, M.; Bouchet, T.; Chalker, P.R.; Charles, M.; Chen, K.J.; Chowdhury, N.; Chu, R.; et al. The 2018 GaN power electronics roadmap. *J. Phys. D Appl. Phys.* **2018**, *51*, 163001. [CrossRef]

- Lee, S.; Vetury, R.; Brown, J.D.; Gibb, S.R.; Cai, W.Z.; Sun, J.; Green, D.S.; Shealy, J. Reliability assessment of AlGaN/GaN HEMT technology on SiC for 48V applications. In Proceedings of the 2008 IEEE International Reliability Physics Symposium, Phoenix, AZ, USA, 27 April–1 May 2008; pp. 446–449. [CrossRef]

- Burnham, S.D.; Paine, B.M. Towards and RF GaN Reliability Standard. In Proceedings of the JEDEC Reliability of Compound Semiconductors Workshop, Indian Wells, CA, USA, 22 May 2017.

- 37. Marcon, D.; Viaene, J.; Favia, P.; Bender, H.; Kang, X.; Lenci, S.; Stoffels, S.; Decoutere, S. Reliability of AlGaN/GaN HEMTs: Permanent leakage current increase and output current drop. In Proceedings of the 20th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Suzhou, China, 15–19 July 2013; pp. 249–254. [CrossRef]

- Joh, J.; Gao, F.; Palacios, T.; del Alamo, J.A. A model for the critical voltage for electrical degradation of GaN high electron mobility transistors. *Microelectron. Reliab.* 2010, 50, 6. [CrossRef]

- 39. Zhang, Y.; Zhou, L.; Mao, J.-F. Inverse Piezoelectric and Trap Effects with Temperature Dependence in AlGaN/GaN HEMTs Under Narrowband Microwave Pulses. *IEEE Trans. Electromagn. Compat.* **2023**, *65*, 794–803. [CrossRef]

- 40. Meneghesso, G.; Meneghini, M.; Stocco, A.; Bisi, D.; de Santi, C.; Rossetto, I.; Zanandrea, A.; Rampazzo, F.; Zanoni, E. Degradation of AlGaN/GaN HEMT devices: Role of reverse-bias and hot electron stress. *Microelectron. Eng.* **2013**, *109*, 257–261. [CrossRef]

- 41. Meneghesso, G.; Meneghini, M.; Tazzoli, A.; Ronchi, N.; Stocco, A.; Chini, A.; Zanoni, E. Reliability issues of Gallium Nitride High Electron Mobility Transistors. *Int. J. Microw. Wirel. Technol.* **2010**, *2*, 39–50. [CrossRef]

- 42. Del Alamo, J.A.; Joh, J. GaN HEMT reliability. Microelectron. Reliab. 2009, 49, 1200–1206. [CrossRef]

- 43. Sozza, A.; Dua, C.; Morvan, E.; Grimber, B.; Delage, S.L. A 3000 hours DC Life Test on AlGaN/GaN HEMT for RF and microwave applications. *Microelectron. Reliab.* 2005, 45, 9–11. [CrossRef]

- 44. Gao, Z.; Chiocchetta, F.; Rampazzo, F.; De Santi, C.; Fornasier, M.; Meneghesso, G.; Meneghini, M.; Zanoni, E. Thermally-activated failure mechanisms of 0.25 μm RF AlGaN/GaN HEMTs submitted to long-term life tests. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–5. [CrossRef]

- Miccoli, C.; Gervasi, L.; Cerantonio, V.; Pomeroy, J.; Kuball, M. Peak channel temperature determination for an AlGaN/GaN HEMT with Raman Thermography and MTTF extraction for long term reliability. In Proceedings of the 2022 IEEE 9th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Redondo Beach, CA, USA, 7–9 November 2022; pp. 35–39. [CrossRef]

- 46. Kurpas, P.; Selvanathan, I.; Schulz, M.; Würfl, J. Performance Benchmarking of European GaN Epitaxial Wafer Suppliers in Comparison with Vendors from USA and Japan; ESA/ESTEC Contract 20328/06/NL/IA; European Space Agency: Paris, France, 2022. Available online: https://escies.org/download/webDocumentFile?id=62230 (accessed on 30 August 2023).

- Raja, P.V.; Nallatamby, J.-C.; Bouslama, M.; Jacquet, J.C.; Sommet, R.; Chang, C.; Lambert, B. HTRB Stress Effects on 0.15 μm AlGaN/GaN HEMT Performance. In Proceedings of the 2022 IEEE MTT-S International Conference on Numerical Electromagnetic and Multiphysics Modeling and Optimization (NEMO), Limoges, France, 6–8 July 2022; pp. 1–4. [CrossRef]

- Bergsten, J.; Chen, J.-T.; Gustafsson, S.; Malmros, A.; Forsberg, U.; Thorsell, M.; Janzén, E.; Rorsman, N. Performance Enhancement of Microwave GaN HEMTs Without an AlN-Exclusion Layer Using an Optimized AlGaN/GaN Interface Growth Process. *IEEE Trans. Electron. Devices* 2016, 63, 333–338. [CrossRef]

- Alemdar, O.S.; Karakaya, F.; Keysan, O. PCB Layout Based Short-Circuit Protection Scheme for GaN HEMTs. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 2212–2218. [CrossRef]

- Lyu, X.; Li, H.; Abdullah, Y.; Wang, K.; Hu, B.; Yang, Z.; Wang, J.; Liu, L.; Bala, S. A Reliable Ultra-Fast Three Step Short Circuit Protection Method for E-mode GaN HEMTs. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 437–440. [CrossRef]

- 51. Shankar, B.; Raghavan, S.; Shrivastava, M. ESD Reliability of AlGaN/GaN HEMT Technology. *IEEE Trans. Electron. Devices* 2019, 66, 3756–3763. [CrossRef]

- 52. Shankar, B.; Shrivastava, M. Unique ESD behavior and failure modes of AlGaN/GaN HEMTs. In Proceedings of the 2016 IEEE International Reliability Physics Symposium (IRPS), Pasadena, CA, USA, 17–21 April 2016; pp. EL-7-1–EL-7-5. [CrossRef]

- 53. Shankar, B.; Raghavan, S.; Shrivastava, M. Distinct Failure Modes of AlGaN/GaN HEMTs Under ESD Conditions. *IEEE Trans. Electron. Devices* 2020, 67, 1567–1574. [CrossRef]

- 54. Shankar, B.; Shrivastava, M. Safe Operating Area of Polarization Super-junction GaN HEMTs and Diodes. *IEEE Trans. Electron. Devices* **2019**, *66*, 4140–4147. [CrossRef]

- Shankar, B.; Sengupta, R.; Gupta, S.D.; Soni, A.; Mohan, N.; Bhat, N.; Raghavan, S.; Shrivastava, M. On the ESD behavior of Al-GaN/GaN schottky diodes and trap assisted failure mechanism. In Proceedings of the 2017 39th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Tucson, AZ, USA, 10–14 September 2017; pp. 1–6. [CrossRef]

- Shankar, B.; Soni, A.; Gupta, S.D.; Shrivastava, M. Safe Operating Area (SOA) reliability of Polarization Super Junction (PSJ) GaN FETs. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 4E.3-1–4E.3-4. [CrossRef]

- 57. Qin, Y.; Chai, C.; Li, F.; Liang, Q.; Wu, H.; Yang, Y. Study of Self-Heating and High-Power Microwave Effects for Enhancement-Mode p-Gate GaN HEMT. *Micromachines* **2022**, *13*, 106. [CrossRef]

- Chakraborty, S.; Amir, W.; Shin, J.-W.; Shin, K.-Y.; Cho, C.-Y.; Kim, J.-M.; Hoshi, T.; Tsutsumi, T.; Sugiyama, H.; Matsuzaki, H.; et al. Explicit Thermal Resistance Model of Self-Heating Effects of AlGaN/GaN HEMTs with Linear and Non-Linear Thermal Conductivity. *Materials* 2022, 15, 8415. [CrossRef]

- 59. Kuball, M.; Ťapajna, M.; Simms, R.J.T.; Faqir, M.; Mishra, U.K. AlGaN/GaN HEMT device reliability and degradation evolution: Importance of diffusion processes. *Microelectron. Reliab.* **2011**, *1*, 2. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.