Article

# Teflon/SiO<sub>2</sub> Bilayer Passivation for Improving the Electrical Reliability of Oxide TFTs Fabricated Using a New Two-Photomask Self-Alignment Process

Ching-Lin Fan  $^{1,2,*}$ , Ming-Chi Shang  $^1$ , Bo-Jyun Li  $^1$ , Yu-Zuo Lin  $^2$ , Shea-Jue Wang  $^3$ , Win-Der Lee  $^4$  and Bohr-Ran Hung  $^1$

- Graduate Institute of Electro-Optical Engineering,

National Taiwan University of Science and Technology, 43 Section 4,

Keelung Road, Taipei 106, Taiwan; E-Mails: d10019004@mail.ntust.edu.tw (M.-C.S.);

m10019004@mail.ntust.edu.tw (B.-J.L.); huangbr@mail.ntust.edu.tw (B.-R.H.)

- Department of Electronic Engineering, National Taiwan University of Science and Technology,

43 Section 4, Keelung Road, Taipei 106, Taiwan; E-Mail: yzlin.ntust@gmail.com

- Institute of Materials Science and Engineering, National Taipei University of Technology, Taipei 106, Taiwan; E-Mail: sjwang@ntut.edu.tw

- <sup>4</sup> Department of Electrical Engineering, Lee-Ming Institute of Technology, New Taipei City 243, Taiwan; E-Mail: leewd@mail.lit.edu.tw

- \* Author to whom correspondence should be addressed; E-Mail: clfan@mail.ntust.edu.tw; Tel.: +886-2-2737-6374; Fax: +886-2-2737-6424.

Academic Editor: Martin Frank

Received: 7 January 2015 / Accepted: 26 March 2015 / Published: 13 April 2015

**Abstract:** This study proposes a two-photomask process for fabricating amorphous indium—gallium—zinc oxide (a-IGZO) thin-film transistors (TFTs) that exhibit a self-aligned structure. The fabricated TFTs, which lack etching-stop (ES) layers, have undamaged a-IGZO active layers that facilitate superior performance. In addition, we demonstrate a bilayer passivation method that uses a polytetrafluoroethylene (Teflon) and SiO<sub>2</sub> combination layer for improving the electrical reliability of the fabricated TFTs. Teflon was deposited as a buffer layer through thermal evaporation. The Teflon layer exhibited favorable compatibility with the underlying IGZO channel layer and effectively protected the a-IGZO TFTs from plasma damage during SiO<sub>2</sub> deposition, resulting in a negligible initial performance drop in the a-IGZO TFTs. Compared with passivation-free a-IGZO TFTs,

passivated TFTs exhibited superior stability even after 168 h of aging under ambient air at 95% relative humidity.

**Keywords:** indium gallium zinc oxide (IGZO); thin film transistors (TFTs); passivation layer; Teflon; SiO<sub>2</sub>

# 1. Introduction

Numerous recent studies have focused on metal–oxide semiconductors, such as amorphous indium–gallium–zinc oxide (a-IGZO), because of their high mobility and transparency; these semiconductors have been applied as active channel layers in thin-film transistors (TFTs) [1–3]. Regarding conventional silicon-based TFTs, amorphous silicon exhibits low carrier mobility (0.5–1 cm²/V·s), whereas polycrystalline silicon requires high-temperature fabrication and has problems associated with its nonuniform grain size [4,5]. By contrast, a-IGZO TFTs can be fabricated on plastic substrates at low temperatures and exhibit excellent and uniform electrical characteristics [6,7].

In general, a-IGZO TFTs applied in active-matrix liquid-crystal displays and active-matrix organic light-emitting diodes are typically fabricated using a back-channel-etching structure and five photomasks. To reduce the fabrication cost, Uhm *et al.* proposed a two-photomask scheme in which a gray-tone photomask was used to fabricate TFT devices [8]; however, the lack of an etching-stop (ES) layer damages the a-IGZO active island when source/drain (S/D) electrodes are etched. In a typical process, an additional photomask step is required for creating an ES pattern, presenting a trade-off between fabrication cost and device stability. Therefore, Geng *et al.* [9] proposed using backside-ultraviolet (BUV) exposure through a metal gate electrode to define the ES area; this process reduces the misalignment margin and fabrication cost. However, during ES deposition, the process gas of hydrogen-based materials affects the a-IGZO active layer, thereby increasing the leakage current [10]. To promote device stability, [11] proposed a two-photomask scheme that combines BUV exposure and liftoff schemes for fabricating self-aligned TFT devices. S/D electrode etching is replaced by a liftoff technique, and a low-damage device can thus be obtained.

The a-IGZO TFTs must be passivated to elongate their lifetimes by protecting the metal-oxide semiconductors from ambient air. SiO<sub>2</sub> is a widely used passivation material in solid-state electronic and optoelectronic devices because of its excellent oxygen and moisture barrier performance [12]. Moreover, SiO<sub>2</sub> deposition is compatible with conventional large-area deposition processes, such as plasma-enhanced chemical vapor deposition (PECVD) and radio-frequency (RF) sputtering. However, the deposition techniques are based on a plasma process harmful to the metal-oxide materials [13]. Therefore, an appropriate buffer layer must be embedded between the metal-oxide semiconductor and the SiO<sub>2</sub> passivation layer to protect the a-IGZO TFTs from plasma damage during the deposition. In our previous study [14], noncharged polytetrafluoroethylene (Teflon) was used as the buffer layer and combined with a SiO<sub>2</sub> barrier layer to provide bilayer passivation for organic TFTs (OTFTs). Teflon is a nonpolar polymer with numerous excellent properties, such as gas and moisture barrier properties, chemical resistance, thermal resistance, and electric insulation. Teflon can be readily deposited through thermal evaporation at low evaporation temperatures, thus preventing thermal stresses

from damaging the underlying organic semiconductor during evaporation [15,16]. No initial performance drop in the OTFTs was evident after Teflon/SiO<sub>2</sub> passivation, and Teflon effectively protects the OTFTs from plasma damage during SiO<sub>2</sub> deposition.

In the current study, bilayer passivation using Teflon and SiO<sub>2</sub> is proposed for improving the reliability of a-IGZO TFTs fabricated through a two-photomask self-alignment process. Teflon was deposited as the buffer layer through thermal evaporation; this layer exhibited favorable compatibility with the underlying IGZO channel layer. Furthermore, the effect of moisture on the reliability of the a-IGZO TFTs was substantially reduced after the Teflon/SiO<sub>2</sub> passivation. The proposed bilayer Teflon/SiO<sub>2</sub> passivation can be applied to low-cost a-IGZO TFTs fabricated using a two-photomask self-alignment process for improving the reliability of the TFTs.

#### 2. Device Fabrication

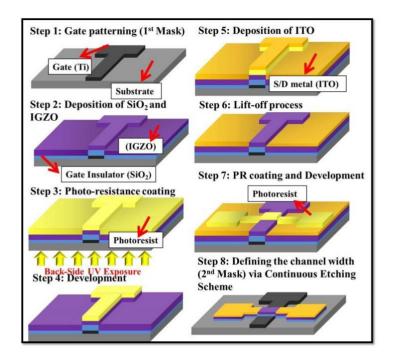

Figure 1 illustrates the proposed two-photomask process for fabricating a-IGZO TFTs. A 160-nm-thick Ti layer was first deposited onto a glass substrate through thermal evaporation, and the layer was patterned to create the gate electrode by using the first photomask. A 200-nm-thick SiO<sub>2</sub> layer was subsequently deposited using PECVD at 300 °C to create the gate insulator. Next, a 20-nm-thick a-IGZO layer (In<sub>2</sub>O<sub>3</sub>:Ga<sub>2</sub>O<sub>3</sub>:ZnO = 1:1:1 mol%) was deposited through RF sputtering at 200 °C, as follows. First, a photoresist was spin-coated onto an IGZO layer and subjected to BUV exposure by using the Ti gate as a photomask (Figure 1). Second, a 350-nm-thick indium-tin oxide (ITO) layer was deposited through RF sputtering. The backside-liftoff scheme was subsequently used to define the channel length of the self-aligned structure, and the second photomasks were used to define the channel width. Furthermore, reactive-ion etching with CF<sub>4</sub> gas was employed to continuously etch ITO, IGZO, and SiO₂ under 80 mTorr, and the etched TFTs were annealed at 200 ℃ for 30 min in a vacuum chamber. Third, the passivation layer, composed of Teflon and SiO<sub>2</sub>, was deposited over the TFTs. Teflon (400 nm) was deposited using a thermal evaporator (base pressure  $2 \times 10^{-6}$  Torr) with the substrate maintained at room temperature (RT). SiO<sub>2</sub> (100 nm) was subsequently deposited through RF magnetron sputtering by using a SiO<sub>2</sub> target at 50 W, 5 mTorr, and RT. The electrical parameters of all TFTs were measured in ambient and 95% relative humidity (RH) environments in a glovebox by using a semiconductor parameter analyzer (HP 4145B).

All devices were measured under ambient environments and 95% relative humidity (RH) environments

**Figure 1.** Two-photomask process flow of amorphous indium–gallium–zinc oxide (a-IGZO) thin-film transistors (TFTs) subjected to Teflon/SiO<sub>2</sub> passivation.

# 3. Results and Discussion

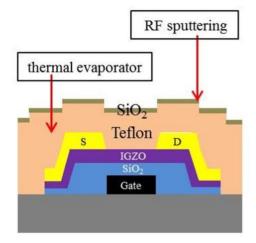

Figure 2a shows the transfer characteristic of the device with the SiO<sub>2</sub> passivation layer only. It is found that the plasma severely damage the device performance after the SiO<sub>2</sub> deposition. Therefore, the Teflon layer was considered as a buffer layer to suffer the plasma damage from SiO<sub>2</sub> deposition. Figure 2b illustrates the transfer curves (I<sub>DS</sub>-V<sub>GS</sub>) of the oxide TFTs before and after the Teflon/SiO<sub>2</sub> bilayer deposition. No change was observed in the transfer curve of the TFTs after the deposition. Crucial electrical characteristics are evident in the transfer curves at an S/D voltage of 10.5 V. The threshold voltages were calculated in the saturation regime by fitting the  $|I_{DS}|^{1/2}$  versus  $V_{GS}$  curve of the square law:  $I_{DS} = \mu_{FE}C_{OX} (W/2L)(V_{GS} - V_{TH})^2$ , where  $\mu_{FE}$  is the field-effect mobility,  $C_{OX}$  is the capacitance density of the gate insulator, V<sub>TH</sub> is the threshold voltage. The maximum and minimum values of drain current (IDS) at a drain voltage (VDS) of 10.5 V are designated as Ion (on-current) and  $I_{off}$  (off-current), respectively [17–19]. And the shift of threshold voltage  $\Delta V_{TH}$  is defined  $\Delta V_{TH} = [(V_{TH} \text{ after stress} - V_{TH} \text{ before stress})/V_{TH} \text{ before stress}]$ . Before passivation, the field-effect mobility (µFE) was 8.28 cm<sup>2</sup>/V·s in the saturation region, the threshold voltage (V<sub>TH</sub>) was 4.81 V, and the on/off current ratio (I<sub>ON</sub>/I<sub>OFF</sub>) was approximately 10<sup>6</sup>. After passivation, the values of µ<sub>FE</sub>, V<sub>TH</sub>, and I<sub>ON</sub>/I<sub>OFF</sub> were 8.67 cm<sup>2</sup>/V·s, 5.08 V, and approximately 10<sup>6</sup>, respectively as shown in Table 1. These results show that the thermally evaporated Teflon did not physically or chemically damage the underlying IGZO channel layer because of its low evaporation temperature and chemical inertness, and the Teflon layer can effectively protect the a-IGZO TFTs from plasma damage during the SiO<sub>2</sub> deposition. Therefore, Teflon can be used as the buffer layer for suppressing the in situ degradation of a-IGZO TFTs during SiO<sub>2</sub> passivation.

**Figure 2.** (a) Transfer curves (I<sub>DS</sub>-V<sub>GS</sub>) of a-IGZO TFTs without teflon buffer layer; (b) Transfer curves (I<sub>DS</sub>-V<sub>GS</sub>) of a-IGZO TFTs before and after Teflon/SiO<sub>2</sub> bilayer deposition.

Table 1. The electrical characteristics of devices before and after Teflon/SiO<sub>2</sub> bilayer deposition.

| Electrical parameters | $V_{TH}$ | μге  | S.S. | $I_{on}/I_{off}$    |

|-----------------------|----------|------|------|---------------------|

| Before-passivation    | 4.81     | 8.28 | 0.39 | $2.9 \times 10^{6}$ |

| After-passivation     | 5.08     | 8.67 | 0.40 | $2.7 \times 10^{6}$ |

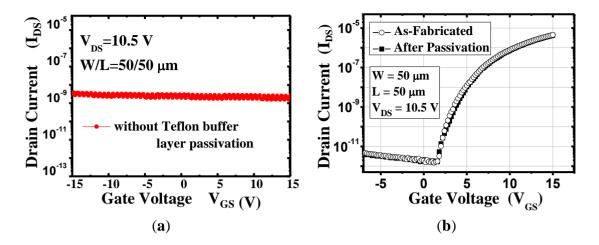

Figure 3 depicts the electrical parameters of the a-IGZO TFTs that were and were not subjected to Teflon/SiO<sub>2</sub> bilayer passivation in an ambient environment for 30 days. The electrical reliability of the TFTs subjected to Teflon/SiO<sub>2</sub> passivation was superior to that of the TFTs not subjected to passivation. The markedly negative V<sub>TH</sub> shift and the increased leakage current (I<sub>off</sub>) in the TFTs not subjected to passivation are attributed to free electrons generated in the IGZO layer during the prolonged stress durations. This result suggests that, as reported previously [20], adsorbed H<sub>2</sub>O donates a partial negative charge to the a-IGZO surface in either molecular or hydroxyl forms. Similarly, the formation of extra electron carriers has been attributed to the donation of electrons (i.e., the donor effect) [20] from chemically adsorbed H<sub>2</sub>O molecules to the surfaces of IGZO. The V<sub>TH</sub> of TFTs can be expressed as  $V_{TH} = \{ [(q \times D_{bt} \times (E_F - E_i))/C_i] - (Q_f/C_i) + [(q \times D_{it} \times (E_F - E_i))/C_i] - (Q_m/C_i) - [(q \times D_D - D_A)/C_i] + \Delta_{MS} \}$ where C<sub>i</sub> is the insulator capacitance; Q<sub>f</sub> is the oxide charge density; D<sub>bt</sub> and D<sub>it</sub> are the bulk trap density and the interface trap density, respectively, and  $\Delta_{MS}$  is the work function difference between metal/semiconductor. D<sub>D</sub> and D<sub>A</sub> are the donor and acceptor concentrations, respectively [21]. It is described that the carrier concentration in the channel layer influences V<sub>TH</sub>. The extra electrons induced by the H<sub>2</sub>O molecules may form a back channel layer with a high electron concentration, thus producing a more negative voltage that depletes the channel layer.

**Figure 3.** Time-dependent changes in the (a)  $I_{ON}$ ; (b)  $I_{OFF}$ ; (c)  $\mu_{FE}$ ; and (d)  $V_{TH}$  of a-IGZO TFTs with and without Teflon/SiO<sub>2</sub> passivation in an ambient environment, respectively.

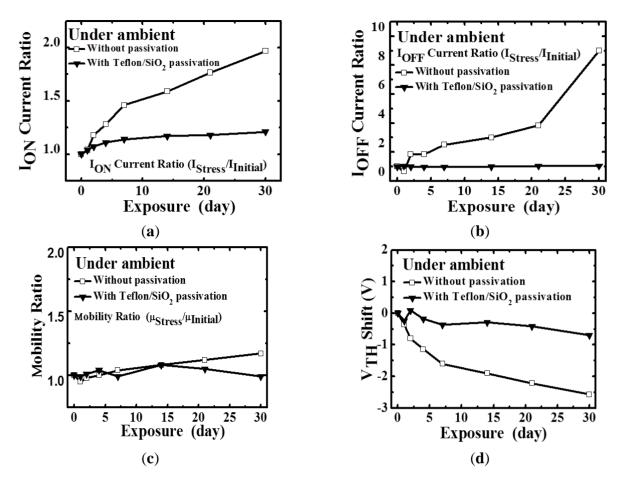

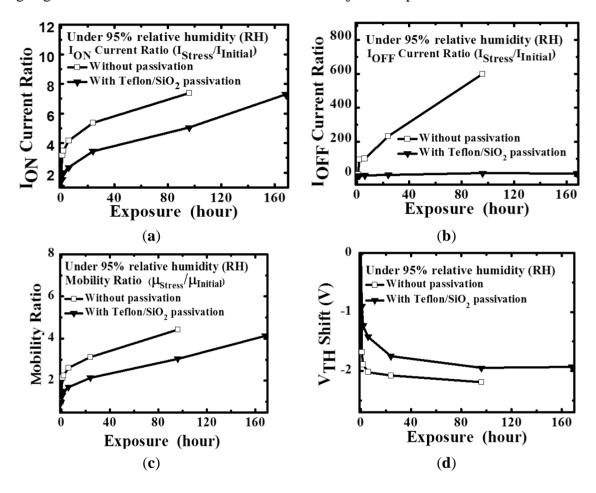

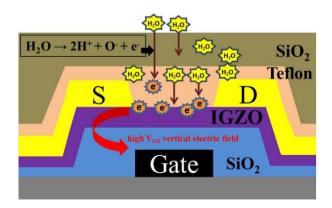

Further investigation was required to clarify the effect of moisture on the TFTs. Therefore, the TFTs were placed in a 95% RH environment to induce the effect of moisture. Figure 4 depicts the electrical parameters of a-IGZO TFTs that were and were not subjected to Teflon/SiO<sub>2</sub> bilayer passivation at 95% RH for 168 h. Both a-IGZO TFTs exhibited increased mobility and  $I_{on}$  current ratios. The TFTs not subjected to Teflon/SiO<sub>2</sub> passivation exhibited considerably more degradation than did those subjected to it. In addition, the device without bilayer passivation had been not the transfer characteristics after the stress in the period of 168 h. Previous studies [20,22] have reported that the extra electron carriers cause a high electron concentration in the back channel, reducing  $V_{TH}$ ; this process can be described as  $H_2O \rightarrow 2H^+ + O^- + e^-$ . Therefore, when the TFTs subjected to bilayer passivation were placed in a 95% RH environment, a small amount of  $H_2O$  molecules diffused through  $SiO_2$  (*i.e.*, the passivation layer) and piled onto the Teflon layer because of the high concentration of  $H_2O$ . The piled  $H_2O$  molecules induce extra electron carriers because of the high vertical electric field ( $V_{GS}$ ), thus causing the negative  $V_{TH}$  shift of the TFTs subjected to bilayer passivation. Figure 5 depicts a schematic of an  $H_2O$ -molecule-induced extra electron carrier model for a-IGZO TFTs.

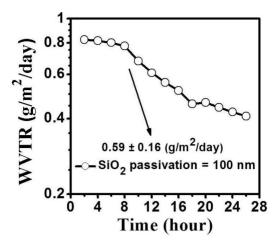

To confirm the moisture-barrier property of the RF sputtered SiO<sub>2</sub> film, the water vapor transmission rate (WVTR) of the 100-nm-thick SiO<sub>2</sub> layer deposited on one side of a polycarbonate (PC) substrate was investigated. The WVTR measurement was conducted at 38 °C and 100% RH by using a water vapor permeation measurement system (MOCON Aquatran Model 1). As shown in Figure 6, the WVTR

mean value of the SiO<sub>2</sub>-coated PC substrate was approximately  $0.59 \pm 0.16$  g/m²/day. And for commercially available polymers, such as Polylmide (PI), PolyTetraFlouro Ethylene (Teflon), PolyEthylene Terephthalate (PET) and PolyEthylene Naphthalate (PEN), the permeation rates are typically >1  $\times$  103 g/m²/day for oxygen and >1 g/m² day for water at last [23]. In this study, the moisture-blocking layer was SiO<sub>2</sub> because of its excellent oxygen and moisture barrier performance. The Teflon layer was considered to be a buffer layer suffer the plasma damage from the SiO<sub>2</sub> layer depositing. In summary, the Teflon/SiO<sub>2</sub> bilayer passivation effectively blocked moisture diffusion, reducing degradation relative to that of the a-IGZO not subjected to passivation.

**Figure 4.** Time-dependent changes in the (**a**) IoN; (**b**) IoFF; (**c**) μFE; and (**d**) V<sub>TH</sub> of a-IGZO TFTs with and without Teflon/SiO<sub>2</sub> passivation in a 95% relative humidity environment, respectively.

**Figure 5.** Schematic of H<sub>2</sub>O-molecule-induced extra electron carrier model for a-IGZO TFTs.

**Figure 6.** Water vapor transmission rate of polycarbonate substrates with a 100-nm-thick SiO<sub>2</sub> layer.

#### 4. Conclusions

This study demonstrated a bilayer passivation method that involves using a Teflon and SiO<sub>2</sub> combination layer for considerably improving the reliability of a-IGZO TFTs—Which exhibit a self-aligned structure—Fabricated using a novel two-photomask process. The results show that the electrical performance of the fabricated a-IGZO TFTs subjected to Teflon/SiO<sub>2</sub> passivation was comparable to that of pristine a-IGZO TFTs. Depositing a Teflon buffer layer did not damage the underlying channel layer; this buffer layer effectively protected the a-IGZO TFTs from plasma damage during SiO<sub>2</sub> passivation. This study concludes that the proposed bilayer Teflon/SiO<sub>2</sub> passivation effectively blocks the moisture diffusion, thus yielding superior reliability even after 168 h of aging under ambient air at 95% RH.

# **Acknowledgments**

The authors would like to acknowledge the financial support of the National Science Council of Taiwan under contract No. NSC 102-2221-E-011-112-MY2, and of the Taiwan Building Technology Center (TBTC) of National Taiwan University of Science and Technology (NTUST).

# **Author Contributions**

Ching-Lin Fan advise the study and work; Ching-Lin Fan and Bo-Jyun Li designed the research; Bo-Jyun Li and Ming-Chi Shang performed the experimental work; Ming-Chi Shang wrote the manuscript. All authors discussed, edited and approved the final version.

# **Conflicts of Interest**

The authors declare no conflict of interest.

# References

1. Hirao, T.; Furuta, M.; Hiramatsu, T.; Matsuda, T.; Li, C.; Furuta, H.; Hokari, H.; Yoshida, M.; Ishii, H.; Kakegawa, M. Bottom-gate zinc oxide thin film transistors (ZnO TFTs) for AM-LCDs. *IEEE Trans. Electron Devices* **2008**, *55*, 3136–3142.

- 2. Paine, D.; Yaglioglu, B.; Beiley, Z.; Lee, S.H. Amorphous IZO based transparent thin film transistors. *Thin Solid Films* **2008**, *516*, 5894–5898.

- 3. Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. Amorphous oxide channel TFTs. *Thin Solid Films* **2008**. *516*. 1516–1522.

- 4. Ukai, Y. TFT-LCD manufacturing technology current status and future prospect. In Proceedings of the International Workshop on Physics of Semiconductor Devices, Mumbai, India, 16–20 December 2007; pp. 29–34.

- 5. Choi, Y.W.; Lee, J.N.; Jang, T.W. Thin-film transistors fabricated with Poly-Si films crystallized at low temperature by microwave annealing. *IEEE Electron Device Lett.* **1999**, *20*, 2–4.

- 6. Nomura, K.; Ohta, H.; Ueda, K.; Kamiya, T.; Hirano, M.; Hosono, H. Thin-film transistor fabricated in single-crystalline transparent oxide emiconductor. *Science* **2003**, *300*, 1269–1272.

- 7. Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-temperature fabrication of transparent flexible thin-film transistorsusing amorphous oxide semiconductor. *Nature* **2004**, *432*, 488–492.

- 8. Uhm, H.; Lee, S.; Kim, W.; Park, J. A two-mask process for fabrication of bottom-gate IGZO-based TFTs. *IEEE Electron Device Lett.* **2012**, *33*, 543–545.

- 9. Geng, D.; Kang, D.H.; Jang, J. High-performance amorphous Indium-Gallium-Zinc-Oxide thin-film transistor with a self-aligned etch stopper patterned by back-side UV exposure. *IEEE Electron Device Lett.* **2011**, *32*, 758–760.

- 10. Park, J.; Kim, S.; Kim, C. High-performance amorphous gallium indium zinc oxide thin-film transistors through N<sub>2</sub>O plasma passivation. *Appl. Phys. Lett.* **2008**, *93*, 053505:1–053505:3.

- 11. Fan, C.L.; Shang, M.C.; Li, B.J.; Lin, Y.Z.; Wang, S.J.; Lee, W.D. A self-aligned a-IGZO thin-film transistor using a new two-photo-mask process with a continuous etching scheme. *Materials* **2014**, *7*, 5761–5768.

- 12. Tropsha, Y.G.; Harvey, N.G. Activated rate theory treatment of oxygen and water transport through silicon oxide/poly(ethylene terephthalate) composite barrier structures. *J. Phys. Chem. B* **1997**, *101*, 2259–2266.

- 13. Lin, W.K.; Liu, K.C.; Chen, J.N.; Hu, S.C.; Chang, S.T. The influence of fabrication process on top-gate thin-film transistors *Thin Solid Films* **2011**, *519*, 5126–5130.

- 14. Fan, C.L.; Lin, Y.Z.; Chiu, P.C.; Wang, S.J.; Lee, W.D. Teflon/SiO<sub>2</sub> bilayer passivation for improving the electrical reliability of pentacene-based organic thin-film transistors. *Org. Electronics* **2013**, *14*, 2228–2232.

- 15. Fan, C.L.; Yang, T.H.; Chiu, P.C. Performance improvement of bottom-contact pentacene-based organic thin-film transistors by inserting a thin polytetrafluoroethylene buffer layer. *Appl. Phys. Lett.* **2010**, *97*, 143306:1–143306:3.

- 16. Rapisarda, M.; Simeone, D.; Fortunato, G.; Valletta, A.; Mariucci, L. Pentacene thin film transistors with (polytetrafluoroethylene) PTFE-like encapsulation layer. *Org. Electronics* **2011**, *12*, 119–124.

17. Chen, T.L.; Hsu, T.Y.; Lin, H.Y.; Chou, C.H.; Lin, H.H.; Liu, C.W. Enhanced current drive of double-gate α-IGZO thin-film transistors. *IEEE Electron Device Lett.* **2013**, *34*, 417–419.

- 18. Kamiya, T.; Nomura, K.; Hosono, H. Present status of amorphous In–Ga–Zn–O thin-film transistors. *Sci Technol. Adv. Mater.* **2010**, *11*, 044305:1–044305:23.

- 19. Seok, M.J.; Choi, M.H.; Mativenga, M.; Kim, D.Y.; Jang, J. A full-swing a-IGZO TFT-based inverter with a top-gate-bias-induced depletion load. *IEEE Electron Device Lett.* **2011**, *32*, 1089–1091.

- 20. Park, J.S.; Jeong, J.K.; Chung, H.J.; Mo, Y.G.; Kim, H.D. Electronic transport properties of amorphous indium-gallium-zinc oxide semiconductor upon exposure to water. *Appl. Phys. Lett.* **2008**, *92*, 072104:1–072104:3.

- 21. Kim, S.J.; Lee, S.Y.; Lee, Y.W.; Lee, W.G.; Yoon, K.S.; Kwon, J.Y.; Han, M.K. Effect of channel layer thickness on characteristics and stability of amorphous hafnium–indium–zinc oxide thin film transistors. *Jpn. J. Appl. Phys.* **2011**, *50*, 024104:1–024104:3.

- 22. Chen, F.H.; Pan, T.M.; Chen, C.H.; Liu, J.H.; Lin, W.H.; Chen, P.H. Two-step electrical degradation behavior in a-InGaZnO thin-film transistor under gate-bias stress. *IEEE Electron Device Lett.* **2013**, *34*, 635–637.

- 23. Groner, M.D.; George, S.M.; McLean, R.S.; Carcia, P.F. Gas diffusion barriers on polymers using Al<sub>2</sub>O<sub>3</sub> atomic layer deposition. *Appl. Phys. Lett.* **2006**, 88, 051907:1–051907:3.

- © 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).