Article

# Promise and Challenges of High-Voltage SiC Bipolar Power Devices

#### Tsunenobu Kimoto \*, Kyosuke Yamada, Hiroki Niwa and Jun Suda

Department of Electronic Science and Engineering, Kyoto University, Kyoto 615 8510, Japan; yamada@semicon.kuee.kyoto-u.ac.jp (K.Y.); niwa@semicon.kyoto-u.ac.jp (H.N.); suda@kuee.kyoto-u.ac.jp (J.S.) \* Correspondence: kimoto@kuee.kyoto-u.ac.jp; Tel.: +81-75-383-2300

Academic Editors: Alberto Castellazzi and Andrea Irace Received: 11 October 2016; Accepted: 28 October 2016; Published: 3 November 2016

**Abstract:** Although various silicon carbide (SiC) power devices with very high blocking voltages over 10 kV have been demonstrated, basic issues associated with the device operation are still not well understood. In this paper, the promise and limitations of high-voltage SiC bipolar devices are presented, taking account of the injection-level dependence of carrier lifetimes. It is shown that the major limitation of SiC bipolar devices originates from band-to-band recombination, which becomes significant at a high-injection level. A trial of unipolar/bipolar hybrid operation to reduce power loss is introduced, and an 11 kV SiC hybrid (merged pin-Schottky) diodes is experimentally demonstrated. The fabricated diodes with an epitaxial anode exhibit much better forward characteristics than diodes with an implanted anode. The temperature dependence of forward characteristics is discussed.

**Keywords:** silicon carbide; power device; carrier lifetime; conductivity modulation; merged pin-Schottky (MPS) diodes

### 1. Introduction

Silicon carbide (SiC) has received increasing attention as a wide bandgap semiconductor well suited for high-voltage power devices. The promise of SiC power devices stems from its superior physical properties and rapid progress in growth and device technologies [1–5]. SiC (4H polytype) unipolar devices such as metal-oxide-semiconductor field effect transistors (MOSFETs) and Schottky barrier diodes (SBDs) with blocking voltages of 600-1700 V have been commercialized, demonstrating substantial reduction of power loss in various power conversion systems. Higher-voltage (3.3–6.5 kV) SiC power MOSFETs have currently been developed [6–8], and 15 kV SiC MOSFETs have also been demonstrated [8]. These very high-voltage SiC MOSFETs can be fabricated with process technology similar to that used for 1 kV-class SiC MOSFETs, though some modifications are required in the cell design and termination structure. However, the specific on-resistance  $(R_{on})$  of power MOSFETs significantly increases with increasing the blocking voltage (V<sub>B</sub>), following the relationship of  $R_{\rm on} \sim V_{\rm B}^{2.2-2.5}$ . The on-resistance further increases at elevated temperature due to the mobility drop. For ultrahigh-voltage (>10 kV) power devices, SiC bipolar devices are promising, because the resistance of the thick voltage-blocking layer can remarkably be reduced by the conductivity modulation effect, and the on-resistance exhibits a very small temperature dependence [9]. A drawback of bipolar devices is, of course, the slower switching speed and thereby the increased switching loss. Thus, the choice of unipolar/bipolar devices must be carefully determined taking account of the operation condition required for individual applications [10]. Another weak point of SiC bipolar devices is the large built-in potential caused by the wide bandgap of SiC (3.26 eV). Thus, a forward voltage drop of about 2.8 V is required before significant current flows in SiC bipolar devices except for bipolar junction transistors. This large built-in voltage (knee voltage) naturally results in a relatively high forward voltage drop at low current density.

In recent years, ultrahigh-voltage SiC pin diodes [11–13], thyristors [14], bipolar junction transistors [15], and insulated-gate bipolar transistors (IGBTs) [16–18] have been reported. Using 10 kV SiC MOSFETs or 15 kV SiC IGBTs, several power converters such as boost converters and modular-leg converters have been fabricated, demonstrating good power efficiencies [19–22]. The major technological challenges for development of ultrahigh-voltage SiC bipolar devices include fast epitaxial growth, reduction of extended defects, control of carrier lifetimes, surface passivation, and packages. The most critical concern about the reliability of SiC bipolar devices is degradation caused by expansion of single-Shockley stacking faults, which nucleate from basal plane dislocations when excess carriers are injected and recombine [23,24]. Elimination of basal plane dislocations in SiC wafers is one of the most important challenges for commercialization of SiC bipolar power devices. Furthermore, development of ultrahigh-voltage packages is another challenge. Although some packages and modules with special insulating materials have been reported for such high-voltage devices [25,26], the ultrahigh-voltage package technology is still not mature.

Though the performances of these devices and converters reported are promising, the ideal characteristics limited by the intrinsic material properties of SiC have not been well studied. In the first part of this paper, the forward characteristics of SiC pin diodes having different thickness of i-layer (voltage-blocking layer) are simulated, and the major intrinsic limitations are discussed. Although 10–30 kV-class SiC pin diodes exhibit good characteristics when the carrier lifetime is long, the forward voltage drop significantly increases when the breakdown voltage exceeds 50–60 kV. It is shown that this limitation originates from the band-to-band recombination in SiC, being an inherent limitation of SiC. In the second part, a trial of unipolar/bipolar hybrid operation with SiC pin diodes is described. The characteristics of merged pin-Schottky (MPS) diodes having epitaxial junction and implanted junction are compared. The epitaxial MPS diodes show good hybrid operation as expected and a high breakdown voltage of 11.3 kV is demonstrated by adopting an appropriate junction termination.

#### 2. Results

## 2.1. Simulation of Forward Characteristics of Ultrahigh-Voltage SiC Pin Diodes

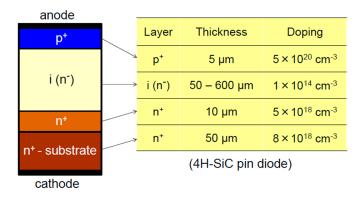

Figure 1 shows the structure of a SiC pin diode simulated in this study. The anode is 5 μm-thick, doped to  $5 \times 10^{20}$  cm<sup>-3</sup>, and the cathode (n<sup>+</sup>-layer beneath the i-layer) is 10  $\mu$ m-thick, doped to  $5 \times 10^{18} \, \mathrm{cm}^{-3}$ . These structures were optimized to achieve highest carrier-injection efficiencies (for example, see Figure S1). Although a higher doping concentration is generally desirable to enhance the injection efficiency, one should consider bandgap narrowing [27]. When the doping concentration becomes too high, a bandgap narrowing phenomenon occurs for the anode or cathode, which remarkably decreases the injection efficiency. Furthermore, when the thickness of the anode or cathode is not enough, the carrier recombination at the anode/cathode contact becomes significant and this recombination increases the minority-carrier current inside the anode/cathode, leading to the decreased injection efficiency [28]. Therefore, the anode and cathode structures were fixed and the thickness of i-layer was varied in this study. The i-layer was a lightly-doped n-type epilayer with a donor concentration of  $1 \times 10^{14}$  cm<sup>-3</sup>, which is technically achievable with the current technology. Since the switching frequency in ultrahigh-voltage power converters is usually low, the major component of power loss in semiconductor devices is the on-state loss. Thus, the forward characteristics of SiC pin diodes were mainly investigated in this study. In recent years, elimination of carrier-lifetime killers has been reported [29,30] and the carrier lifetime of n-type SiC has substantially been improved from about 1–2 µs (as-grown) to 30 µs or even longer [31,32]. In this study, the forward characteristics were simulated by changing the carrier lifetime in a wide range.

Energies 2016, 9, 908 3 of 15

Figure 1. Schematic structure of a SiC pin diode simulated in this study.

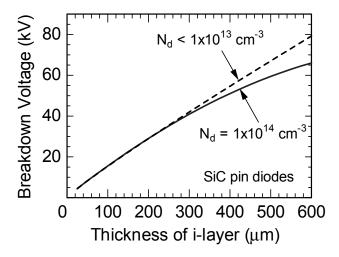

Figure 2 depicts the i-layer thickness dependence of breakdown voltage for SiC pin diodes having the structure shown in Figure 1. The breakdown voltage almost linearly increases with the i-layer thickness, because the doping concentration of the i-layer is low and the diodes are of complete punchthrough structure. However, the breakdown voltage shows a slight saturation trend when the thickness exceeds 300  $\mu$ m, where the electric field strength at the end of the i-layer (space charge region) becomes significantly lower than that at the junction interface. Roughly speaking, the diodes with an i-layer thickness of 100, 300, and 500  $\mu$ m are 15, 40, and 58 kV-class, respectively.

**Figure 2.** Dependence of breakdown voltage for SiC pin diodes on i-layer thickness. The solid and dashed lines denote the results for the i-layer doping concentration of  $1 \times 10^{14}$  cm<sup>-3</sup> and  $<1 \times 10^{13}$  cm<sup>-3</sup>, respectively.

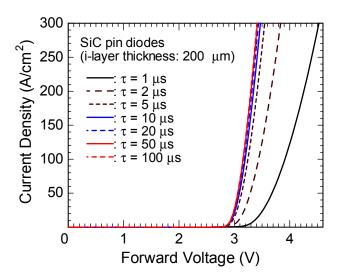

As a typical example, the forward characteristics of SiC pin diodes having an i-layer thickness of 200  $\mu$ m (28 kV class) are presented in Figure 3, where the carrier lifetime in the i-layer was changed from 1  $\mu$ s to 100  $\mu$ s (an analytical expression for the characteristics of a pin diode and brief discussion are given in Note S1). As expected, the characteristics are remarkably improved by increasing the carrier lifetime, which is consistent with the studies on lower-voltage SiC pin diodes reported in literature [33,34]. Note that the carrier lifetimes longer than 10  $\mu$ s do not contribute very much to reduction of the forward voltage drop. For example, the forward voltage drop at a current density of 100 A/cm² is reduced from 3.93 V to 3.20 V by increasing the carrier lifetime from 1  $\mu$ s to 10  $\mu$ s. However, improvement of the forward voltage drop is marginal when the lifetime is further increased to 20  $\mu$ s or longer.

Energies 2016, 9, 908 4 of 15

**Figure 3.** Forward characteristics of SiC pin diodes having an i-layer thickness of 200  $\mu$ m (28 kV class). The carrier lifetime in the i-layer was changed from 1  $\mu$ s to 100  $\mu$ s.

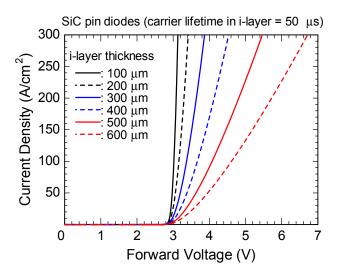

Figure 4 shows the forward characteristics of SiC pin diodes having different i-layer thicknesses from 100  $\mu$ m (15 kV class) to 600  $\mu$ m (65 kV class). Here the carrier lifetime was fixed at 50  $\mu$ s. The diode with an i-layer thickness of 100  $\mu$ m exhibits nearly ideal characteristics; The differential on-resistance is as low as 0.76 m $\Omega$ cm $^2$  and the forward voltage drop is 3.02 V at 100 A/cm $^2$ . Since the on-resistance include a substrate resistance of 0.08 m $\Omega$ cm $^2$ , the actual differential on-resistance of the thick i-layer is estimated to be about 0.68 m $\Omega$ cm $^2$ . However, the on-resistance and forward voltage drop considerably increase to 12.2 m $\Omega$ cm $^2$  and 4.62 V, respectively, for the diode having a 600  $\mu$ m-thick i-layer, even though the lifetime is as long as 50  $\mu$ s.

**Figure 4.** Forward characteristics of SiC pin diodes having different i-layer thicknesses from 100  $\mu$ m (15 kV class) to 600  $\mu$ m (65 kV class). Here the carrier lifetime was fixed at 50  $\mu$ s.

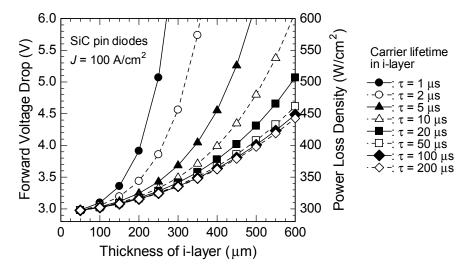

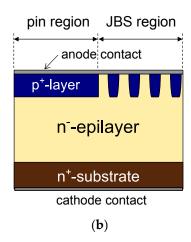

Figure 5 demonstrates the i-layer thickness dependence of the forward voltage drop at a current density of  $100 \text{ A/cm}^2$  for SiC pin diodes, where the carrier lifetime in the i-layer was varied from 1  $\mu$ s to  $200 \mu$ s (the lifetime dependence of the forward voltage drop can be seen in Figure S2). The right axis indicates the density of on-state loss at  $100 \text{ A/cm}^2$ . For a given carrier lifetime, the forward voltage drop monotonically increases with increasing the i-layer thickness. As in the case of Figure 3, reduction of forward voltage drop is not very significant when the carrier lifetime becomes very

Energies 2016, 9, 908 5 of 15

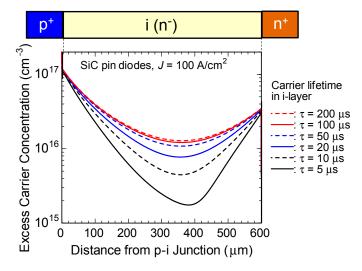

long (>50  $\mu$ s). To clarify the conductivity modulation of high-voltage SiC pin diodes, the profiles of excess carrier concentration inside the i-layer at a current density of 100 A/cm² are plotted in Figure 6. Here the diode with a 600  $\mu$ m-thick i-layer was considered and the carrier lifetime was varied from 5  $\mu$ s to 200  $\mu$ s. The excess carrier concentration is significantly higher than the background carrier concentration in the i-layer (1  $\times$  10<sup>14</sup> cm<sup>-3</sup>) even for the case of a relatively short lifetime (5  $\mu$ s), and it increases with increasing the carrier lifetime. However, the excess carrier concentration does not show further increase very much when the carrier lifetime exceeds 50  $\mu$ s, which is the main reason why improvement of the forward characteristics is almost saturated for very long carrier lifetime as shown in Figure 5. This result identifies the major limitation of SiC pin diodes (and other bipolar devices) in terms of the on-state loss and its origin is discussed in Section 3.

**Figure 5.** Dependence of the forward voltage drop at a current density of  $100 \text{ A/cm}^2$  for SiC pin diodes on the i-layer thickness. Here the carrier lifetime in the i-layer was varied from 1  $\mu$ s to 200  $\mu$ s. The right axis indicates the density of on-state loss at  $100 \text{ A/cm}^2$ .

**Figure 6.** Profiles of excess carrier concentration inside the i-layer at a current density of  $100 \text{ A/cm}^2$  for a SiC pin diode. The i-layer thickness is  $600 \mu m$  and the carrier lifetime was varied from 5  $\mu s$  to  $200 \mu s$ .

## 2.2. Characteristics of Ultrahigh-Voltage SiC Merged Pin-Schottky (MPS) Diodes

As shown in Figure 4, a relatively large knee voltage of about 2.8 V is a major drawback of SiC pin diodes (and other bipolar devices except bipolar junction transistors). The high knee voltage originates

Energies **2016**, 9, 908 6 of 15

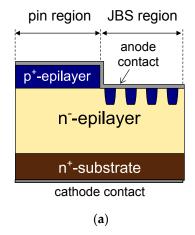

from the large built-in potential of a pn junction in SiC and is an inherent characteristic, which is caused by the wide bandgap (3.26 eV). Since the forward voltage drop of SiC pin diodes is never smaller than 2.8 V at room temperature, the on-state loss of SiC pin diodes can be larger than that of SiC Schottky barrier diodes in the case of partial load (relatively low current density). To overcome this issue, merged pin-Schottky (MPS) diodes have been proposed in Si [35] and then this device concept has been employed to reduce the leakage current caused by tunneling as well as to enhance the surge current capability of SiC Schottky barrier diodes (SBD) [36,37]. In this study, high-voltage SiC MPS diodes, the junction of which was fabricated by either epitaxial growth or ion implantation, were fabricated and tested to reduce the forward voltage drop at relatively low current density. Figure 7 illustrates the schematic structures of SiC MPS diodes fabricated in this study. The main junction was formed by either (a) epitaxial growth or (b) Al<sup>+</sup> ion implantation. Due to the difference in junction formation, the "epitaxial" MPS diode has a mesa structure (Figure 7a), while the "implanted" MPS diode does a planar structure (Figure 7b). The details of fabrication process are described in Section 4.

**Figure 7.** Schematic structures of SiC MPS diodes fabricated in this study. The main junction was formed by either (a) epitaxial growth or (b) Al<sup>+</sup> ion implantation. The widths of the pin and JBS (Junction-Barrier Schottky) regions were both 150  $\mu$ m and of a stripe-like geometry. The active area was  $3.6 \times 10^{-3}$  cm<sup>2</sup>.

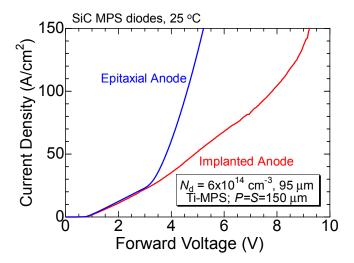

Figure 8 depicts the forward characteristics for two types of SiC MPS diodes (epitaxial or implanted anode) fabricated in this study. In both diodes, the current starts to flow at a forward voltage of 0.9 V, which corresponds to the knee voltage of Ti/SiC Schottky barrier diodes. From the semilogarithmic plots of forward characteristics, the barrier height of Ti Schottky was estimated as 1.12 eV, which is consistent with a previous report [38]. The differential on-resistance in this unipolar operation was approximately 85–100 m $\Omega$ cm<sup>2</sup> irrespective of the formation process of the main junction (anode). This on-resistance is slightly higher than but reasonably agrees with the drift resistance calculated from the structure of a lightly-doped n-type epilayer. The epitaxial MPS diode exhibited the second knee voltage at about 3.2 V, which means the onset of bipolar operation caused by minority-carrier injection. Above this second knee voltage, the differential on-resistance was remarkably reduced by the conductivity modulation effect and it reaches 14.9 m $\Omega$ cm<sup>2</sup> at a current density of 100 A/cm<sup>2</sup>. On the other hand, the implanted MPS diode did not show a clear "second knee voltage" and the current density gradually increased and the differential on-resistance slowly decreased with the current. As a result, the forward voltage drop at 100 A/cm<sup>2</sup> was much smaller for the epitaxial MPS diode (4.65 V) than for the implanted MPS diode (7.81 V). Therefore, SiC epitaxial MPS diodes are promising because the forward voltage drop can be remarkably reduced at relatively low current density ("partial load" condition) compared with SiC pin diodes and the voltage drop at high current density is much lower than that of a SiC Schottky barrier diode with the same breakdown

Energies **2016**, 9, 908 7 of 15

voltage, though the forward voltage at high current density is slightly higher than that of a pure SiC pin diode (For comparison, see Figure S3).

**Figure 8.** Forward characteristics for two types (epitaxial or implanted anode) of SiC MPS diodes fabricated in this study. The widths of the pin-region (*P*) and JBS region (*S*) were both 150 μm.

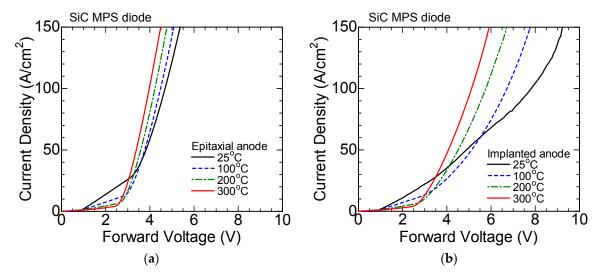

Figure 9 shows the forward characteristics of (a) epitaxial and (b) implanted MPS diodes at different temperatures from 25 to 300 °C. In both diodes, the current density in the unipolar operation at a given forward voltage (below 2.5 V) decreased at elevated temperature, which is similar to the characteristics of Schottky barrier diodes. In the bipolar operation, the knee voltage gradually decreased with elevating the temperature, leading to higher current density at high temperature. This phenomenon is naturally expected because the built-in potential of a pn junction declines when the temperature is elevated. The increase of current density in the bipolar operation by increasing the temperature is more significant for the implanted MPS diode compared with the epitaxial MPS diode, and the characteristics of the implanted MPS diode gradually approach those of the epitaxial MPS diode at high temperature. However, the epitaxial MPS diode showed better performance even at 300 °C. More quantitative analyses are described in the next section.

**Figure 9.** Forward characteristics of (a) epitaxial and (b) implanted SiC MPS diodes at different temperatures from 25 to 300  $^{\circ}$ C.

Energies **2016**, 9, 908 8 of 15

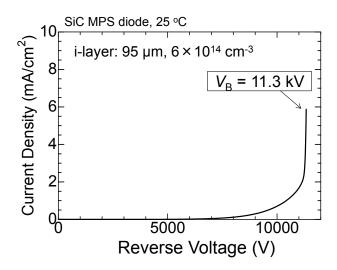

The reverse characteristic of a fabricated SiC MPS diode is shown in Figure 10, where the current-voltage curve of an epitaxial MPS diode was measured by a high-voltage DC sweep. The diode exhibited a very high breakdown voltage of 11.3 kV, which is about 90% of the ideal parallel-plane breakdown voltage determined by the epilayer structure. As far as the blocking performance is concerned, there is not a significant difference between the epitaxial and implanted MPS diodes, because the breakdown occurs in the JTE region for the diodes fabricated in this study (The i-layer structure and the JTE region are almost identical for both the diodes).

Figure 10. Reverse characteristic of a SiC epitaxial MPS diode fabricated in this study.

#### 3. Discussion

## 3.1. Limitation of Ultrahigh-Voltage SiC Bipolar Devices

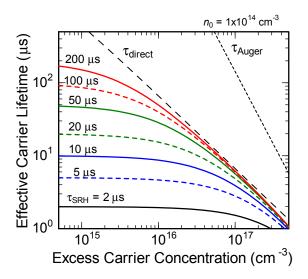

As shown in Figures 5 and 6, the major limitation of ultrahigh-voltage SiC pin diodes is the large forward voltage drop and high differential on-resistance when the i-layer thickness becomes very thick (for example, 600  $\mu$ m (65 kV class)). The forward characteristics are not improved even if an extremely long carrier lifetime over 100  $\mu$ s is assumed. Therefore, recombination paths of excess carriers are analyzed and discussed in this subsection. It should be noted that the carrier lifetime employed in the simulation is so-called Shockley-Read-Hall (SRH) lifetime ( $\tau_{SRH}$ ) determined by indirect recombination via deep levels. In a semiconductor, band-to-band (direct) and Auger recombinations also take place, and these recombination processes must be taken into account especially when the excess carrier concentration is high [39]. Thus, the decay of excess carrier concentration in SiC was theoretically analyzed.

Recombination of excess carriers in n-type semiconductor can be expressed by the following differential equation [39]:

$$\frac{d\Delta n}{dt} = -\frac{\Delta n}{\tau_{SRH}} - B(n_0 + p_0 + \Delta n)\Delta n - C_n(n_0^2 + 2n_0\Delta n + \Delta n^2)\Delta n - C_p(p_0^2 + 2p_0\Delta n + \Delta n^2)\Delta n$$

(1)

here,  $\Delta n$ ,  $n_0$ , and  $p_0$  are the excess carrier concentration, the equilibrium electron concentration (1  $\times$  10<sup>14</sup> cm<sup>-3</sup> in the present case), and the equilibrium hole concentration, respectively. Regarding the carrier recombination, SRH recombination ( $\tau_{SRH}$ ), band-to-band (direct) recombination (coefficient: B), and Auger recombination (coefficients:  $C_n$ ,  $C_p$ ) were considered. The SRH lifetime was assumed to be independent of the excess carrier concentration. Table 1 summarizes these parameters employed in this analysis [40]. Both the SRH lifetime and the initial excess carrier concentration were varied in wide ranges, and the time decay of the excess carrier concentration was calculated.

Energies **2016**, 9, 908 9 of 15

| Parameter | Value                 | Unit               |

|-----------|-----------------------|--------------------|

| В         | $1.5 \times 10^{-12}$ | cm <sup>3</sup> /s |

| $C_{n}$   | $5.0 \times 10^{-31}$ | cm <sup>6</sup> /s |

| $C_{p}$   | $2.0 \times 10^{-31}$ | cm <sup>6</sup> /s |

**Table 1.** Carrier recombination coefficients used in the calculation [40].

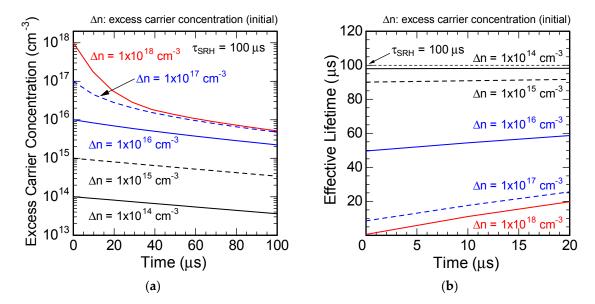

Figure 11a shows the decay curves of the excess carrier concentration in n-type SiC having a long SRH lifetime of 100  $\mu$ s. A relatively fast decay is observed when the initial excess carrier concentration is high. For each decay curve, the differential slope was calculated and defined as the effective carrier lifetime ( $\tau_{eff}$ ). Figure 11b depicts the effective carrier lifetime as a function of time for several different initial excess carrier concentrations from  $1 \times 10^{14}$  cm<sup>-3</sup> to  $1 \times 10^{18}$  cm<sup>-3</sup>.

**Figure 11.** (a) Decay curves of the excess carrier concentration in n-type SiC having a long SRH lifetime of 100  $\mu$ s for several different initial excess carrier concentrations from 1  $\times$  10<sup>14</sup> cm<sup>-3</sup> to 1  $\times$  10<sup>18</sup> cm<sup>-3</sup>; (b) Effective carrier lifetime as a function of time for several different initial excess carrier concentrations.

When the excess carrier concentration is relatively low,  $1\times10^{15}$  cm $^{-3}$ , the effective lifetime is 90–92 µs, close to the SRH lifetime (100 µs). However, the effective lifetime at the initial decay drops drastically with increasing the excess carrier concentration and it reaches 8.5 µs at  $1\times10^{17}$  cm $^{-3}$  and 0.6 µs at  $1\times10^{18}$  cm $^{-3}$ . Figure 12 plots the effective carrier lifetime as a function of the excess carrier concentration calculated in this study.

Results for different SRH lifetimes from 2  $\mu$ s to 200  $\mu$ s are shown, and the lifetimes limited purely by band-to-band (direct) recombination and Auger recombination are indicated by dashed and dotted lines, respectively. It is well known that direct and Auger recombinations become significant when the carrier concentration is very high. As shown in Figure 12, however, the direct recombination severely affects the effective carrier lifetime even at a relatively low excess carrier concentration of  $1 \times 10^{16}$  cm<sup>-3</sup> when the SRH lifetime is very long (>50  $\mu$ s). In such a case, the effective carrier lifetime is mainly limited not by SRH recombination but by direct recombination. This situation is more pronounced as the SRH lifetime becomes longer. The ambipolar diffusion constant ( $D_a$ ) and ambipolar diffusion length ( $L_a$ ) of excess carriers are given by the following equations:

$$D_{\rm a} = \frac{n+p}{n/D_{\rm n} + p/D_{\rm p}},\tag{2}$$

$$L_{\rm a} = \sqrt{D_{\rm a} \tau_{\rm eff}}.$$

(3)

where n and p are the electron concentration ( $n = n_0 + \Delta n$ ) and hole concentration ( $p = p_0 + \Delta n$ ), respectively.  $D_n$  and  $D_p$  are the diffusion constants of electrons and holes, respectively. Based on Figures 11 and 12, the ambipolar diffusion length can be estimated to be 210  $\mu$ m at an excess carrier concentration of  $1 \times 10^{15}$  cm<sup>-3</sup>, 140  $\mu$ m at  $1 \times 10^{16}$  cm<sup>-3</sup>, and decreased to 45  $\mu$ m at  $1 \times 10^{17}$  cm<sup>-3</sup> for a SRH lifetime of 100  $\mu$ s. Since the excess carrier concentration inside the i-layer of a pin diode is in the  $10^{16}$ – $10^{17}$  cm<sup>-3</sup> range at high current density (Figure 6), the ambipolar diffusion length at such current density is almost saturated at about 50–150  $\mu$ m, even if all the defects can be eliminated. The estimated ambipolar diffusion length (about 100  $\mu$ m) is sufficiently long to highly modulate a 200  $\mu$ m-thick i-layer [35] but not enough for a 600  $\mu$ m-thick i-layer. As discussed above, this limitation originates from band-to-band (direct) recombination in SiC, which is an intrinsic property of the material. Thus, band-to-band recombination is the major factor which inherently limits the performance of ultrahigh-voltage SiC pin diodes and possibly other bipolar devices.

Figure 12. Effective carrier lifetime in SiC as a function of the excess carrier concentration.

As a future work, it is important to predict the limitation of SiC pin diodes in the wide temperature range, especially at high temperature. To this end, basic studies on the temperature dependence of carrier recombination coefficients (both band-to-band and Auger recombinations) are essential.

# 3.2. Comparison of SiC MPS Diodes Formed by Epitaxial Growth and Ion Implantation

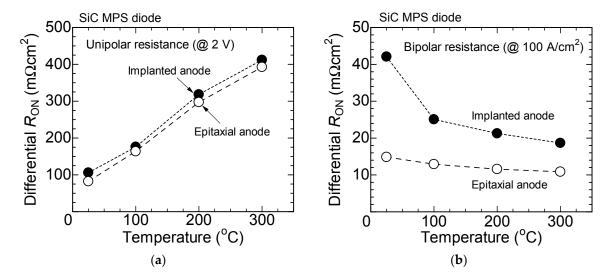

Based on the results shown in Figure 9, the differential on-resistances in the (a) unipolar and (b) bipolar operations were determined at each temperature and are plotted in Figure 13. Here the differential on-resistance was defined at a forward voltage of 2 V for the unipolar operation and at a current density of  $100~\text{A/cm}^2$  for the bipolar operation. As shown in Figure 13a, the unipolar on-resistance is almost independent of the type of MPS diodes, namely epitaxial or implanted junctions, though the epitaxial MPS diode exhibited slightly lower on-resistance. Since the i-layer (lightly-doped n-type epilayer) is very thick (95  $\mu$ m), the impact of implantation-induced damage, which is created inside the implanted p-type anode as well as near the implantation tail [41], is very small, as far as the majority carrier conduction is concerned. Thus, the differential on-resistance in the unipolar operation should be determined simply by the bulk resistance of the very thick n-type epilayer. This is the reason why the difference in the unipolar on-resistance between epitaxial and implanted MPS diodes was very small. The increase of the unipolar on-resistance at elevated temperature is ascribed to the decrease of electron mobility due to enhanced phonon scattering. The temperature dependence of the unipolar

on-resistance shown in Figure 13a is consistent with the temperature dependence of electron mobility in lightly-doped n-type SiC [4].

**Figure 13.** Differential on-resistances of fabricated SiC MPS diodes in the **(a)** unipolar and **(b)** bipolar operations at different temperatures. The results for epitaxial and implanted MPS diodes are shown.

In contrast, a definite difference was observed for the differential on-resistance in the bipolar operation. As shown in Figure 13b, the bipolar on-resistance is reduced at high temperature, which can be attributed to the increased carrier lifetime and the enhanced injection efficiency of holes from the p-type anode to the lightly-doped n-type epilayer. The latter is naturally expected owing to the increased ionization of Al acceptors at elevated temperature, which are energetically deep in SiC. Since a high density of deep levels and extended defects are generated inside the p-type anode and near the main junction by ion implantation and subsequent annealing, the carrier lifetime is substantially shortened in these regions. The short charrier lifetime near the main junction kills the injection efficiency, leading to considerable decrease of the conductivity modulation effect and thereby to the increased differential on-resistance of the implanted MPS diode. This result is consistent with a report on 4.5 kV SiC pin diodes formed by implantation [42]. When the carrier lifetime in the i-layer is long enough, the differential on-resistance of a pin diode is low and its temperature dependence is small [9], which is the major reason why the bipolar on-resistance of the epitaxial MPS diode in this study was much lower and showed the small temperature dependence. However, the increase of carrier lifetime at elevated temperature significantly contributes to the conductivity modulation and to decrease of the differential on-resistance when the carrier lifetime is short, because the conductivity of more and more region inside the i-layer is modulated with increasing the temperature. This trend is more significant for the bipolar on-resistance of the implanted MPS diodes as shown in Figure 13b.

Since a potential of unipolar/bipolar hybrid operation could be demonstrated with high-voltage SiC diodes in this study, monolithic integration of SiC vertical power MOSFET and IGBT is an attractive challenge. Since MOSFETs exhibit no knee voltage in the on-state characteristics, remarkable reduction of on-state loss can be expected by the hybrid operation of MOSFET and IGBT. However, the unipolar on-resistance becomes unacceptably high for extremely high-voltage devices and at high temperature. Thus, such hybrid devices must have severe limitations when the breakdown voltage is higher than 20 kV or the operation temperature exceeds 200 °C. The proposed hybrid MOSFET-IGBT devices will be promising for 8–15 kV switching devices.

#### 4. Materials and Methods

For simulation of SiC pin diodes, a commercial device simulator, a Synopsis TCAD-Sentaurs device [43], was used. The standard set of physical properties of 4H-SiC embedded in the simulator was employed. In the simulation, incomplete ionization of dopants (nitrogen donors and aluminum acceptors) and a bandgap narrowing effect for heavily-doped materials were taken into account. In simulation of SiC pin diodes, accurate models for the carrier statistics and basic transport properties of SiC are included. However, the injection-level dependence of SRH carrier lifetime and carrier-carrier scattering are not known in SiC. Therefore, we assumed an injection-level independent SRH lifetime and neglected carrier-carrier scattering. These assumptions induce certain inaccuracy in the present simulation. Establishment of these physical models is an important subject of study in the future.

In the simulation, a heavily-doped n-type SiC substrate was assumed beneath the active pin diode. The thickness and resistivity of the substrate were 50  $\mu$ m and 0.016  $\Omega$ cm, respectively, where the substrate thinning was considered because the active region (mainly i-layer) is very thick. The contact resistivity for the anode and cathode was neglected for simplicity. For calculating the ideal breakdown voltage, a latest set of impact ionization coefficients [44] was employed. The diode temperature was fixed at room temperature (300 K) in all the simulations.

In fabrication of SiC MPS diodes, a 95 μm-thick n-type epilayer grown on a heavily doped n-type substrate was used as a starting material. The n-type epilayer was intentionally doped with nitrogen to  $6 \times 10^{14} \ cm^{-3}$ . Before formation of the p-type anode, thermal oxidation at 1400 °C for 48 h was performed to enhance the carrier lifetime [30,32]. The low-injection carrier lifetime can be increased from 2 µs to about 30 µs by this process. After removal of the formed oxide, the anode region was formed by either epitaxial growth or Al<sup>+</sup> implantation. In the case of epitaxial growth, the anode consists of two p-type layers, 2.0  $\mu$ m-thick layer doped to  $1 \times 10^{19}$  cm<sup>-3</sup> and 0.2  $\mu$ m-thick layer doped to  $1 \times 10^{20} \ \text{cm}^{-3}$  (top). After epitaxial growth of the p-type anode, sloped mesas were formed for device isolation by fluorine-based reactive ion etching using  $SiO_2$  as an etching mask [45]. In the case of implanted junctions, a 0.8  $\mu$ m-deep box profile with the dopant concentration of 2  $\times$  10<sup>18</sup> cm<sup>-3</sup> was formed by Al<sup>+</sup> implantation (implant energy: 270–700 keV). Higher-dose Al<sup>+</sup> implantation was carried out to form a 0.2  $\mu$ m-thick heavily-doped surface layer (dopant concentration:  $2 \times 10^{20}$  cm<sup>-3</sup>) for improving the contact resistivity. Along the periphery of a diode, a 500 µm-long space-modulated junction termination extension (JTE) structure was formed by Al<sup>+</sup> implantation [13]. All the implanted dopants were activated by annealing at 1650 °C for 20 min with a carbon cap [46]. The Ohmic and Schottky contacts on the anode were Ti/Al sintered at 1000 °C and Ti sintered at 300 °C, respectively. The specific contact resistance of the Ti/Al ohmic contact was determined from a transfer length method. The contact resistance was  $1.4 \times 10^{-5} \ \Omega \text{cm}^2$  on the epitaxial anode and  $2.2 \times 10^{-4} \ \Omega \text{cm}^2$  on the implanted anode. The cathode contact was Ni sintered at 1000 °C. Note that the Schottky area was actually of junction-barrier Schottky (JBS) structure, which was formed by Al+ implantation (stripe geometry), to reduce the leakage current. The surface was passivated with a thermally grown oxide and a 7 µm-thick polyimide. The widths of the pin-diode and Schottky-areas were both 150 µm, and the active area excluding the JTE region was  $3.6 \times 10^{-3}$  cm<sup>2</sup>. This anode geometry and widths were optimized to suppress a "snapback" phenomenon [47], which is often observed in unipolar/bipolar hybrid operation.

The forward characteristics of fabricated diodes were tested with a semiconductor parameter analyzer (4200, Keithley, Solon, OH, USA) without packaging. The high-voltage reverse characteristics were measured with a custom-made high-voltage DC tester (Keithley, Solon, OH, USA) by immersing a diode in Fluorinart to avoid air sparking. The diode temperature was changed by using a heating stage.

#### 5. Conclusions

Performance and potential limitation of SiC bipolar diodes were investigated by simulation and experiments. SiC pin diodes and other bipolar devices are especially attractive in the blocking voltage range of 10–30~kV, owing to the conductivity modulation effect. When the i-layer becomes

very thick to further increase the blocking voltage, however, the conductivity of such a thick i-layer is not fully modulated because of a limited carrier lifetime, leading to higher differential on-resistance. The intrinsic limitation of effective carrier lifetime in SiC originates from band-to-band recombination at the high-injection level. This limitation especially affects the device performance when the blocking voltage exceeds 50–60 kV.

One weak point of SiC pin diodes and other bipolar devices except bipolar junction transistors is the high knee voltage in the on-state. To overcome this issue, unipolar/bipolar hybrid operation is promising, because unipolar devices can carry the current at lower voltage drop when the current density is relatively low. As the first step, an 11 kV SiC MPS diode with an epitaxial anode was experimentally demonstrated. The proposed hybrid devices are attractive in the blocking voltage range of 8–15 kV. However, the advantage of these hybrid devices is almost lost when the blocking voltage is higher than 20 kV especially in the high-temperature operation, where the unipolar on-resistance becomes unacceptably high.

Supplementary Materials: The following are available online at www.mdpi.com/1996-1073/9/11/908/s1, Figure S1: Forward voltage drop at  $100~A/cm^2~vs$ . doping concentration in the p-anode simulated with and without the bandgap narrowing effect in SiC pin diodes. The i-layer thickness is  $200~\mu m$ . The optimum doping concentration can be determined as  $5 \times 10^{20}~cm^{-3}$ , taking account of the bandgap narrowing effect, Figure S2: Forward voltage drop at  $100~A/cm^2~vs$ . carrier lifetime in the i-layer simulated for SiC pin diodes having different i-layer thicknesses. In each case, the forward voltage drop shows saturation when the carrier lifetime is long enough. The saturated voltage drop significantly increases with increasing the i-layer thickness, Figure S3: Forward characteristics of the epitaxial MPS diode, pure pin diode, and pure JBS diode fabricated in this study. The proposed MPS diode exhibited a lower voltage drop than the pin diode at low current density and did than the JBS diode at high current density, Figure S4: Forward characteristics of SiC pin diodes having an i-layer thickness of  $200~\mu m$  (28~kV class). The carrier lifetime in the i-layer was changed from  $1~\mu s$  to  $100~\mu s$ .

**Acknowledgments:** This work was supported by Council for Science, Technology and Innovation (CSTI), Cross-ministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics/Consistent R&D of next-generation SiC power electronics" (funding agency: NEDO).

**Author Contributions:** T.K. conceived and designed the simulation and experiments. K.Y. performed the simulation and analyzed the data. H.N. carried out the simulation, fabrication of diodes, and measurements. J.S. extensively supported the simulation and contributed to the data analyses. T.K. wrote the paper.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Bhatnagar, M.; Baliga, B.J. Comparison of 6H-SiC, 3C-SiC, and Si for power devices. *IEEE Trans. Electron Devices* **1993**, 40, 645–655. [CrossRef]

- 2. Cooper, J.A.; Agarwal, A. SiC power-switching devices-the second electronics revolution? *Proc. IEEE* **2002**, 90, 956–968. [CrossRef]

- 3. Friedrichs, P.; Kimoto, T.; Ley, L.; Pensl, G. Volume 2: Power Devices and Sensors. In *Silicon Carbide*; Wiley-VCH Verlag: Weinheim, Germany, 2010.

- 4. Kimoto, T.; Cooper, J.A. Fundamentals of Silicon Carbide Technology; John Wiley & Sons: Singapore, 2014.

- 5. Kimoto, T. Material science and device physics in SiC technology for high-voltage power devices. *Jpn. J. Appl. Phys.* **2015**, *54*, 040103. [CrossRef]

- 6. Imaizumi, M.; Miura, N. Characteristics of 600, 1200, and 3300 V planar SiC-MOSFETs for energy conversion applications. *IEEE Trans. Electron Devices* **2015**, 62, 390–395. [CrossRef]

- 7. Harada, S.; Kobayashi, Y.; Ariyoshi, K.; Kojima, T.; Senzaki, J.; Tanaka, Y.; Okumura, H. 3.3-kV-class 4H-SiC MeV-implanted UMOSFET with reduced gate oxide field. *IEEE Electron Device Lett.* **2016**, *37*, 314–316. [CrossRef]

- 8. Palmour, J.W. Silicon carbide power device development for industrial markets. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014.

- 9. Kaji, N.; Suda, J.; Kimoto, T. Temperature dependence of forward characteristics for ultrahigh-voltage SiC p-i-n diodes with a long carrier lifetime. *Jpn. J. Appl. Phys.* **2015**, *54*, 098004. [CrossRef]

- 10. Morisette, D.T.; Cooper, J.A. Theoretical comparison of SiC PiN and Schottky diodes based on power dissipation considerations. *IEEE Trans. Electron Devices* **2002**, *49*, 1657–1664. [CrossRef]

Energies 2016, 9, 908 14 of 15

11. Sugawara, Y.; Takayama, D.; Asano, K.; Singh, R.; Palmour, J.; Hayashi, T. 12–19 kV 4H-SiC pin diodes with low power loss. In Proceedings of the 2001 International Symposium Power Semiconductor Devices and IC's, Osaka, Japan, 4–7 June 2001; pp. 27–30.

- 12. Cheng, L.; Palmour, J.W.; Agarwal, A.K.; Allen, S.T.; Brunt, E.V.; Wang, G.Y.; Pala, V.; Sung, W.J.; Huang, A.Q.; O'Loughlin, M.J.; et al. Strategic overview of high-voltage SiC power device development aiming at global energy savings. *Mater. Sci. Forum* **2014**, 778–780, 1089–1095. [CrossRef]

- 13. Kaji, N.; Niwa, H.; Suda, J.; Kimoto, T. Ultrahigh-voltage SiC p-i-n diodes with improved forward characteristics. *IEEE Trans. Electron Devices* **2015**, *62*, 374–381. [CrossRef]

- 14. Zhang, Q.J.; Agarwal, A.; Capell, C.; Cheng, L.; O'Loughlin, M.; Burk, A.; Palmour, J.W.; Rumyantsev, S.; Saxena, T.; Levinshtein, M.; et al. 12 kV, 1 cm<sup>2</sup> SiC gate turn-off thyristors with negative bevel termination. *Mater. Sci. Forum* **2012**, 717–720, 1151–1154. [CrossRef]

- 15. Miyake, H.; Okuda, T.; Niwa, H.; Kimoto, T.; Suda, J. 21-kV SiC BJTs with space-modulated junction termination extension. *IEEE Electron Device Lett.* **2012**, *33*, 1598–1600. [CrossRef]

- 16. Ryu, S.H.; Cheng, L.; Dhar, S.; Capell, C.; Jonas, C.; Clayton, J.; Donofrio, M.; O'Loughlin, M.; Burk, A.; Agarwal, A.; et al. Development of 15 kV 4H-SiC IGBTs. *Mater. Sci. Forum* **2012**, 717–720, 1135–1138. [CrossRef]

- 17. Brunt, E.V.; Cheng, L.; O'Loughlin, M.; Capell, C.; Jonas, C.; Lam, K.; Richmond, J.; Pala, V.; Ryu, S.; Allen, S.T.; et al. 22 kV, 1 cm<sup>2</sup>, 4H-SiC n-IGBTs with improved conductivity modulation. In Proceedings of the 2014 International Symposium on Power Semiconductor Devices & IC's, Waikoloa, HI, USA, 15–19 June 2014; pp. 358–361.

- 18. Fukuda, K.; Okamoto, D.; Okamoto, M.; Deguchi, T.; Mizushima, T.; Takenaka, K.; Fujisawa, S.; Harada, S.; Tanaka, Y.; Yonezawa, Y.; et al. Development of ultrahigh-voltage SiC devices. *IEEE Trans. Electron Devices* **2015**, *62*, 396–404. [CrossRef]

- 19. Yang, L.; Zhao, T.; Wang, J.; Huang, A. Design and analysis of a 270 kW five-level DC/DC converter for solid state transformer using 10 kV SiC power devices. In Proceedings of the IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; pp. 245–251.

- 20. Wang, J.; Zhou, X.; Li, J.; Zhao, T.; Huang, A.Q.; Callanan, R.; Husna, F.; Agarwal, A. 10 kV SiC MOSFET-based boost converter. *IEEE Trans. Ind. Appl.* **2009**, 45, 2056–2063. [CrossRef]

- 21. Patel, D.C.; Kadavelugu, A.; Madhusoodhanan, S.; Bhattacharya, S.; Hatua, K.; Leslie, S.; Ryu, S.-H.; Grinder, D.; Agarwal, A. 15 kV SiC IGBT based three-phase three-level modular-leg power converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Denver, CO, USA, 15–19 September 2013; pp. 3291–3298.

- 22. Madhusoodhanan, S.; Tripathi, A.; Patel, D.; Mainali, K.; Kadavelugu, A.; Hazra, S.; Bhattacharya, S.; Hatua, K. Solid-state transformer and MV grid tie applications enabled by 15 kV SiC IGBTs and 10 kV SiC MOSFETs based multilevel converters. *IEEE Trans. Ind. Appl.* **2015**, *51*, 3343–3360. [CrossRef]

- 23. Bergman, P.; Lendenmann, H.; Nilsson, P.Å.; Lindefelt, U.; Skytt, P. Crystal defects as source of anomalous forward voltage increase of 4H-SiC diodes. *Mater. Sci. Forum* **2001**, *353–356*, 299–302. [CrossRef]

- 24. Skowronski, M.; Ha, S. Degradation of hexagonal silicon-carbide-based bipolar devices. *J. Appl. Phys.* **2006**. [CrossRef]

- 25. Hayashi, T.; Izumi, T.; Hemmi, T.; Asano, K. Insulating properties of package for ultrahigh-voltage, high-temperature devices. *Mater. Sci. Forum* **2013**, 740–742, 1036–1039. [CrossRef]

- 26. Schirmer, K.C.; Rowden, B.; Mantooth, H.A.; Ang, S.S.; Balda, J.C. Packaging and Modeling of SiC Power Modules. *ECS Trans.* **2011**, *41*, 183–188.

- 27. Persson, C.; Lindefelt, U.; Sernelius, B.E. Band gap narrowing in n-type and p-type 3C-, 2H-, 4H-, 6H-SiC, and Si. *J. Appl. Phys.* **1999**, *86*, 4419–4427. [CrossRef]

- 28. Luts, J.; Schlangenotto, H.; Scheuermann, U.; Doncker, R.D. Semiconductor Power Devices; Springer: Berlin/Heidelberg, Germany, 2011.

- 29. Storasta, L.; Tsuchida, H. Reduction of traps and improvement of carrier lifetime in 4H-SiC epilayers by ion implantation. *Appl. Phys. Lett.* **2007**, *90*, 062116. [CrossRef]

- 30. Hiyoshi, T.; Kimoto, T. Reduction of deep levels and improvement of carrier lifetime in n-type 4H-SiC by thermal oxidation. *Appl. Phys. Express* **2009**, *2*, 041101. [CrossRef]

- 31. Miyazawa, T.; Ito, M.; Tsuchida, H. Evaluation of long carrier lifetimes in thick 4H silicon carbide epitaxial layers. *Appl. Phys. Lett.* **2010**, *97*, 202106. [CrossRef]

32. Ichikawa, S.; Kawahara, K.; Suda, J.; Kimoto, T. Carrier recombination in n-type 4H-SiC epilayers with long carrier lifetimes. *Appl. Phys. Express* **2012**, *5*, 101301. [CrossRef]

- 33. Singh, R.; Irvine, H.G.; Capell, D.C.; Richmond, J.T.; Berning, D.; Hefner, A.R.; Palmour, J.W. Large area, ultra-high voltage 4H-SiC p-i-n rectifiers. *IEEE Trans. Electron Devices* **2002**, *49*, 2308–2316. [CrossRef]

- 34. Bhalla, A.; Chow, T.P. Bipolar power device performance: Dependence on materials, lifetime and device ratings. In Proceedings of the 6th International Symposium Power Semiconductor Devices and IC's, Davos, Switzerland, 31 May–2 June 1994; pp. 287–292.

- 35. Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer: Berlin, Germany, 2008.

- 36. Peters, D.; Friedrichs, P.; Schörner, R.; Stephani, D. Comparison of 4H-SiC pn, pinch and Schottky diodes for the 3 kV range. *Mater. Sci. Forum* **2002**, *389*–*393*, 1125–1128. [CrossRef]

- 37. Rupp, R.; Treu, M.; Voss, S.; Björk, F.; Reimann, T. 2nd generation SiC Schottky diodes: A new benchmark in SiC device ruggedness. In Proceedings of the 2006 International Symposium Power Semiconductor Devices and IC's, Naples, Italy, 4–8 June 2006; pp. 269–272.

- 38. Itoh, A.; Kimoto, T.; Matsunami, H. High performance of high-voltage 4H-SiC Schottky barrier diodes. *IEEE Electron Device Lett.* **1995**, *16*, 280–282. [CrossRef]

- 39. Schroder, D.K. Semiconductor Material and Device Characterization, 3rd ed.; Wiley-IEEE: New York, NY, USA, 2006.

- 40. Galeckas, A.; Linnros, J.; Grivickas, V.; Lindefelt, U.; Hallin, C. Auger recombination in 4H-SiC: Unusual temperature behavior. *Appl. Phys. Lett.* **1997**, *71*, 3269–3271. [CrossRef]

- 41. Kawahara, K.; Alfieri, G.; Kimoto, T. Detection and depth analyses of deep levels generated by ion implantation in n- and p-type 4H-SiC. *J. Appl. Phys.* **2009**, *106*, 013719. [CrossRef]

- 42. Lendenmann, H.; Mukhitdinov, A.; Dahlquist, F.; Bleichner, H.; Irwin, M.; Söderholm, R.; Skytt, P. 4.5 kV 4H-SiC diodes with ideal forward characteristic. In Proceedings of the 2001 International Symposium Power Semiconductor Devices and IC's, Osaka, Japan, 4–7 June 2001; pp. 31–34.

- 43. Synopsys Website: Tools. Available online: https://www.synopsys.com/Tools/silicon/tcad/device-simulation/Pages/ (accessed on 1 November 2016).

- 44. Niwa, H.; Suda, J.; Kimoto, T. Impact ionization coefficients in 4H-SiC toward ultrahigh-voltage power devices. *IEEE Trans. Electron Devices* **2015**, *62*, 3326–3333. [CrossRef]

- 45. Hiyoshi, T.; Hori, T.; Suda, J.; Kimoto, T. Simulation and experimental study on the junction termination structure for high-voltage 4H-SiC PiN diodes. *IEEE Trans. Electron Devices* **2008**, *55*, 1841–1846. [CrossRef]

- 46. Negoro, Y.; Katsumoto, K.; Kimoto, T.; Matsunami, H. Electronic behaviors of high-dose phosphorus-ion implanted 4H-SiC (0001). *J. Appl. Phys.* **2004**, *96*, 224–228. [CrossRef]

- 47. Niwa, H.; Suda, J.; Kimoto, T. Demonstration of 10 kV SiC hybrid unipolar/bipolar operating diodes. In Proceedings of the Extended Abstracts European Conference Silicon Carbide and Related Materials 2016, Halkidiki, Greece, 25–29 September 2016.

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).