A Varied VSVM Strategy for Balancing the Neutral-Point Voltage of DC-Link Capacitors in Three-Level NPC Converters

Abstract

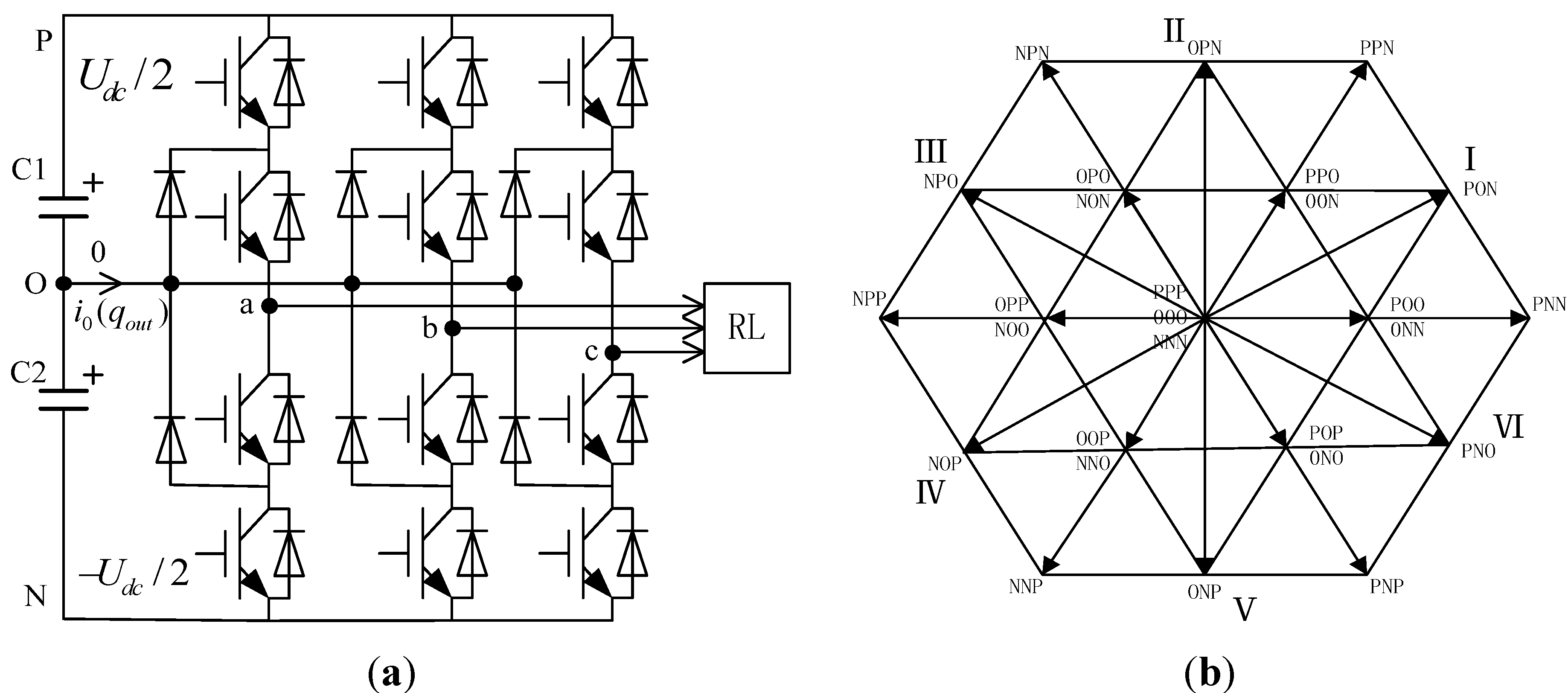

:1. Introduction

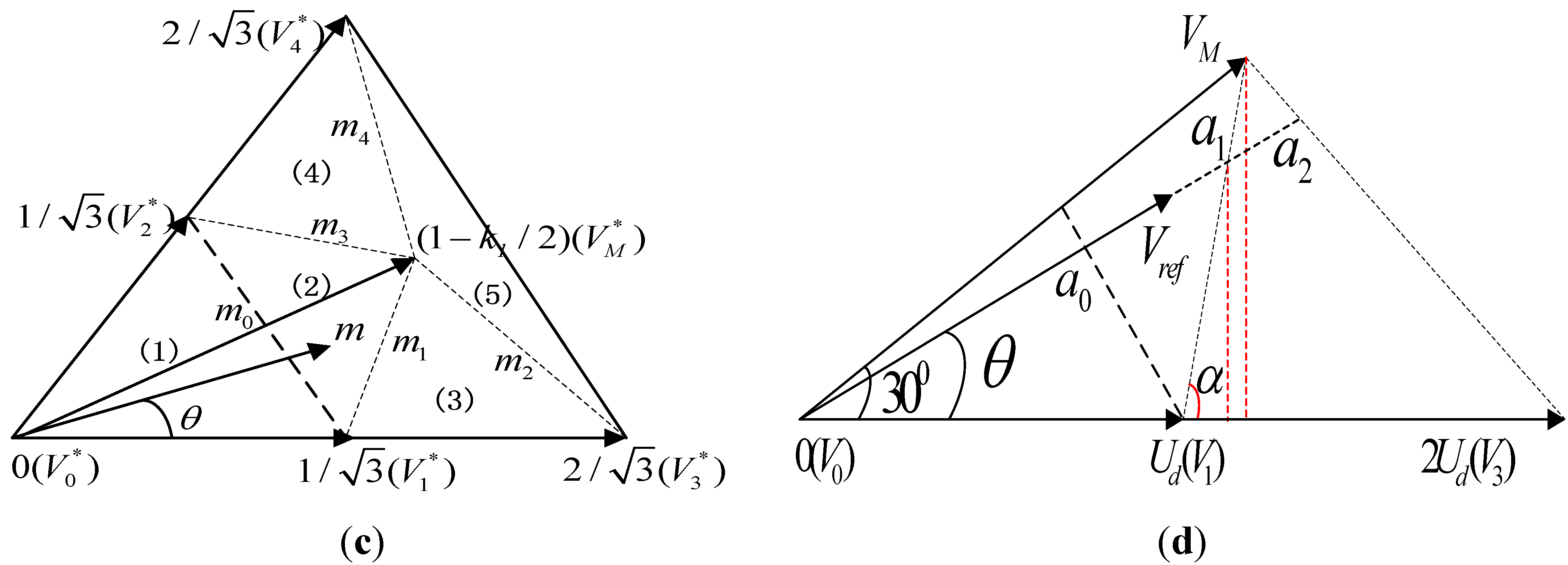

2. Varied Virtual Space Vector Modulation

2.1. The Definition of Varied Virtual Space Vectors

- (1)

- When k1 = 2/3, the virtual medium vector locates at the point b, and the charge qTm flowing out from the neutral-point O is zero. This virtual medium vector will not cause a fluctuation of the neutral-point voltage, which is the same as the neutral-point voltage in the traditional VSVM (modulation index m = 0.667). Because the length of the virtual medium vector stays steady in the process of synthesizing the voltage space vector Vref, the traditional VSVM can’t use the virtual medium vector to balance the neutral-point voltage of DC-link capacitors.

- (2)

- When 1 > k1 > 2/3, the virtual medium vector locates between a and b.

- If ib > 0, the charge flowing out from the neutral-point O: qTm < 0, and UC1 gets smaller; UC2 get larger.

- If ib < 0, the charge flowing from the neutral-point O: qTm > 0, and UC1 gets larger; UC2 get smaller.

- (3)

- When 2/3 > k1 > 0, the virtual medium vector locates between b and c.

- If ib > 0, the charge flowing from the neutral-point O: qTm > 0, and UC1 gets larger; UC2 get smaller.

- If ib < 0, the charge flowing out from the neutral-point O: qTm < 0, and UC1 gets smaller; UC2 get larger.

2.2. Judgment of Small Regions in 60° Sextant

| Small region | Condition 1 | Condition 2 |

|---|---|---|

| (1) | - | |

| (2) | ||

| (3) | ||

| (4) | ||

| (5) | Other | - |

2.3. Synthesis of Vectors

| Small region | Duty cycle 1 | Duty cycle 2 | Duty cycle 3 |

|---|---|---|---|

2.4. The Amplitude of the NP Voltage Oscillations

3. Neutral-Point Balancing Strategy

3.1. Neutral-Point Balancing Algorithm in Small Region (1)

3.2. Balancing Strategy for Neutral-Point Voltage in Small Regions (2)–(5)

4. Simulation and Experimental Verification

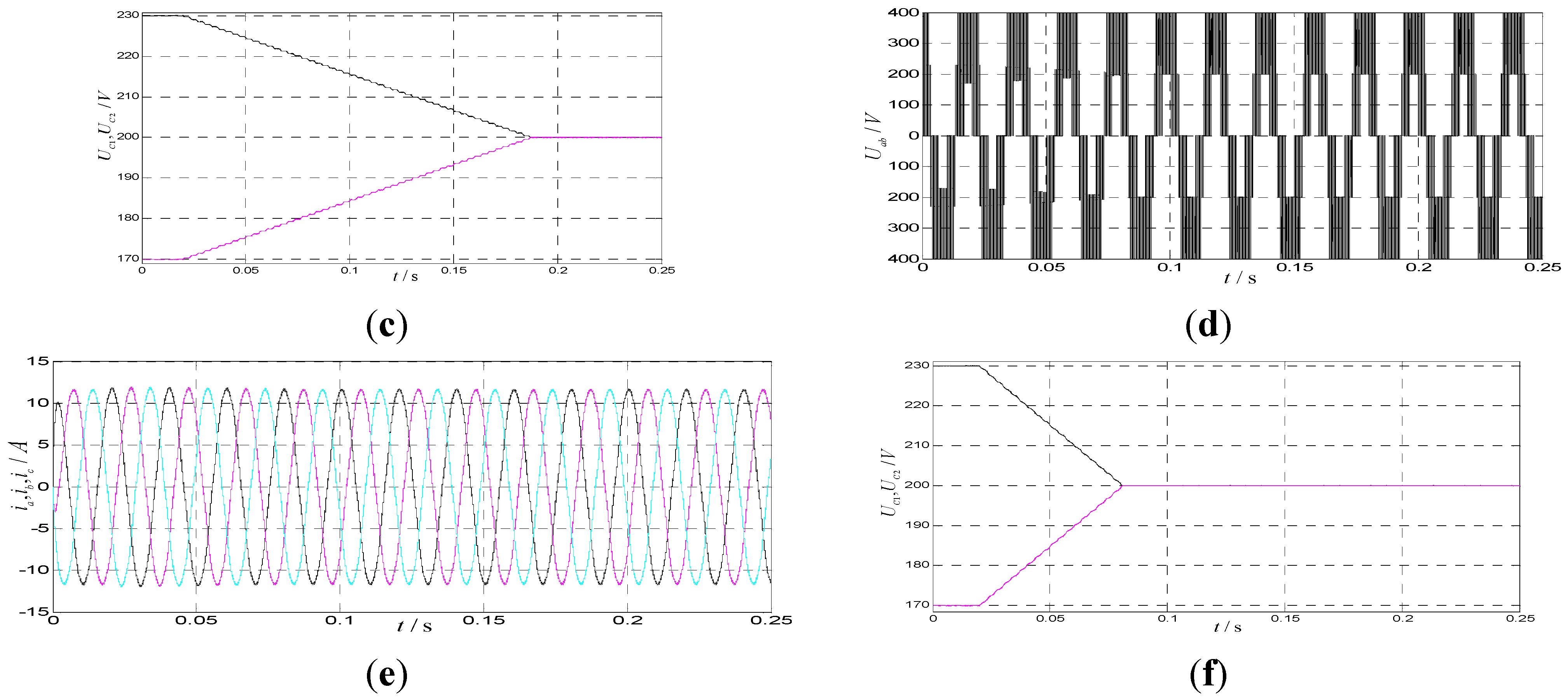

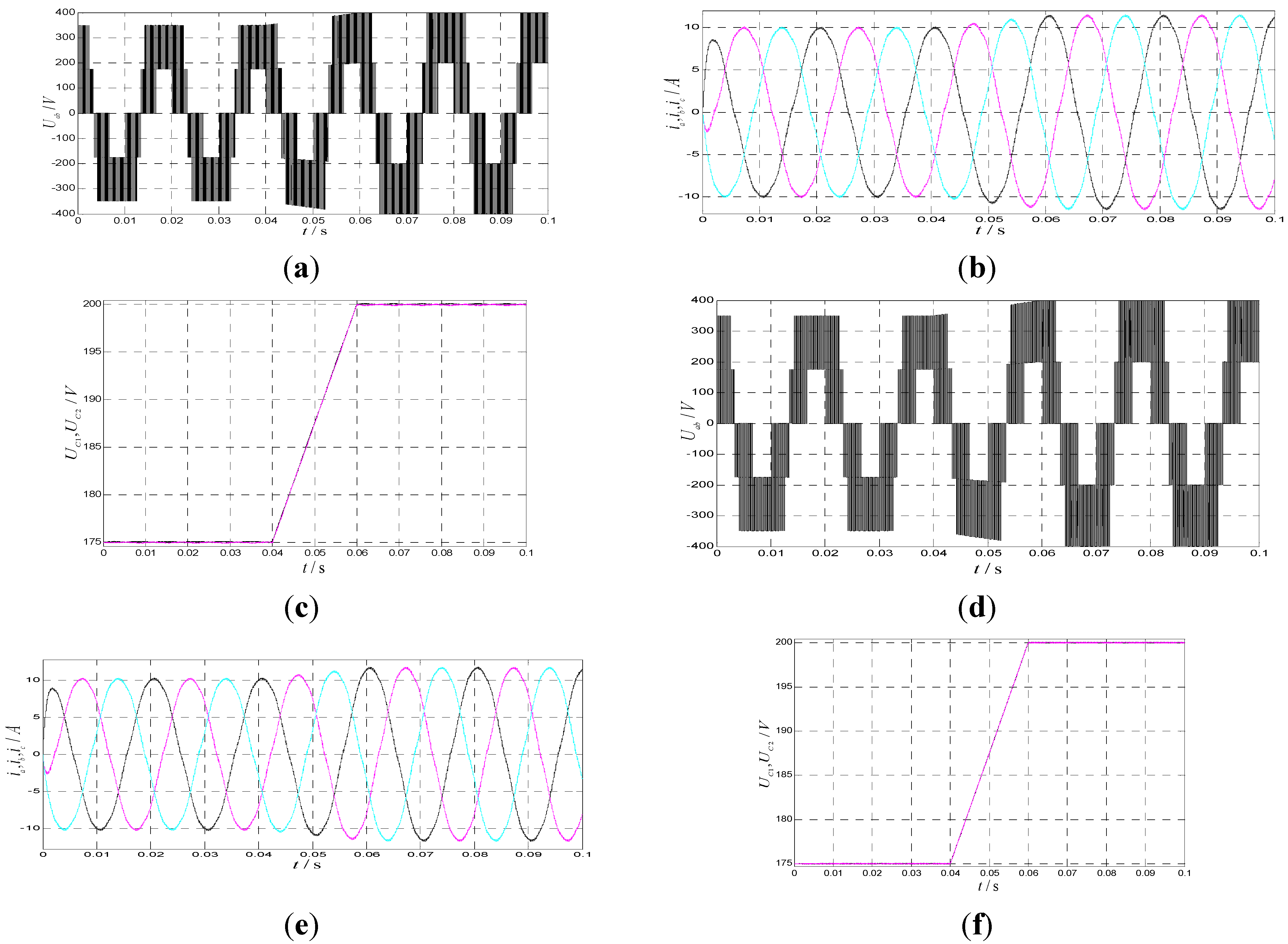

4.1. Simulation Results

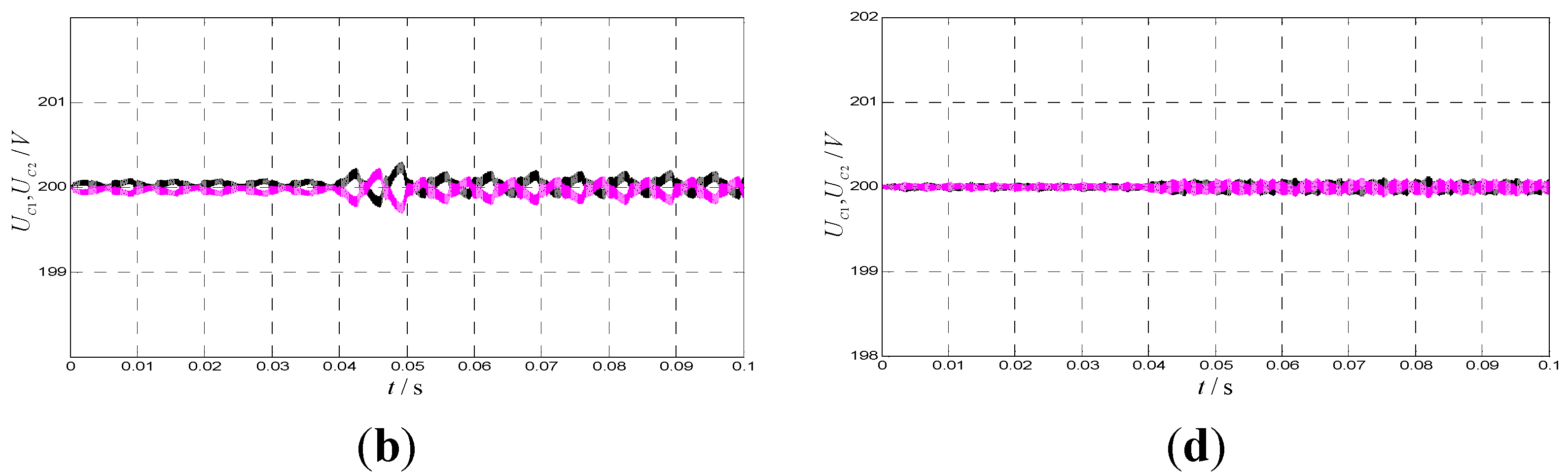

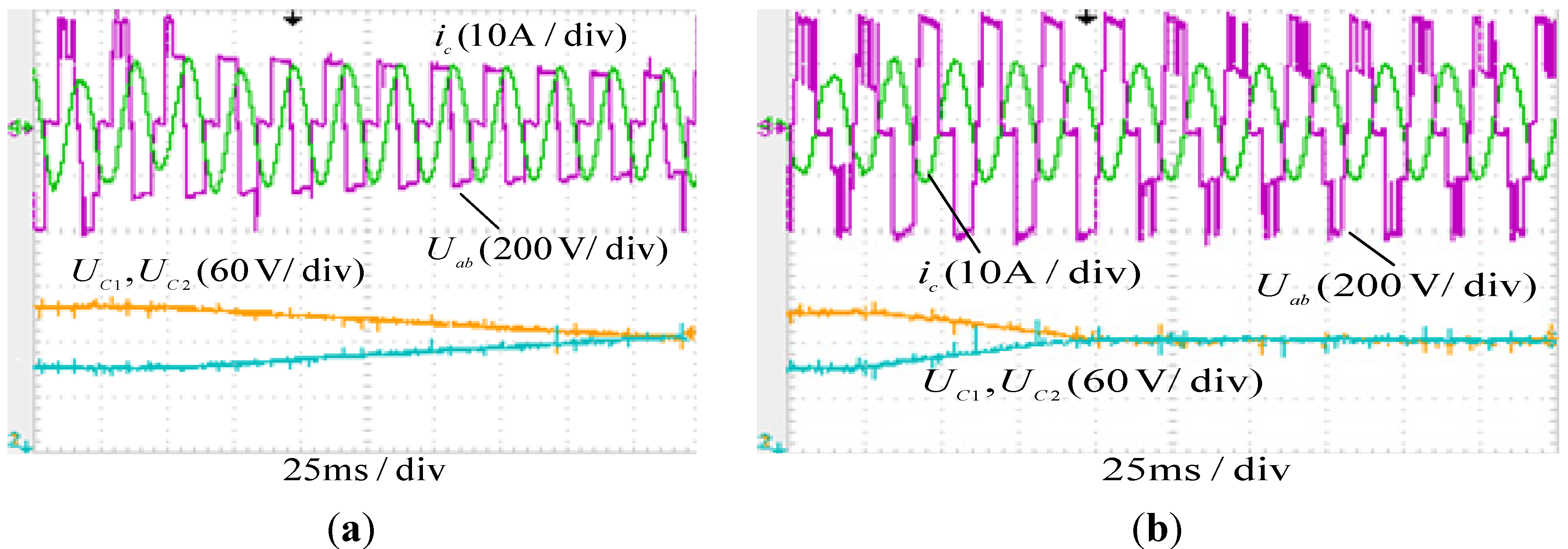

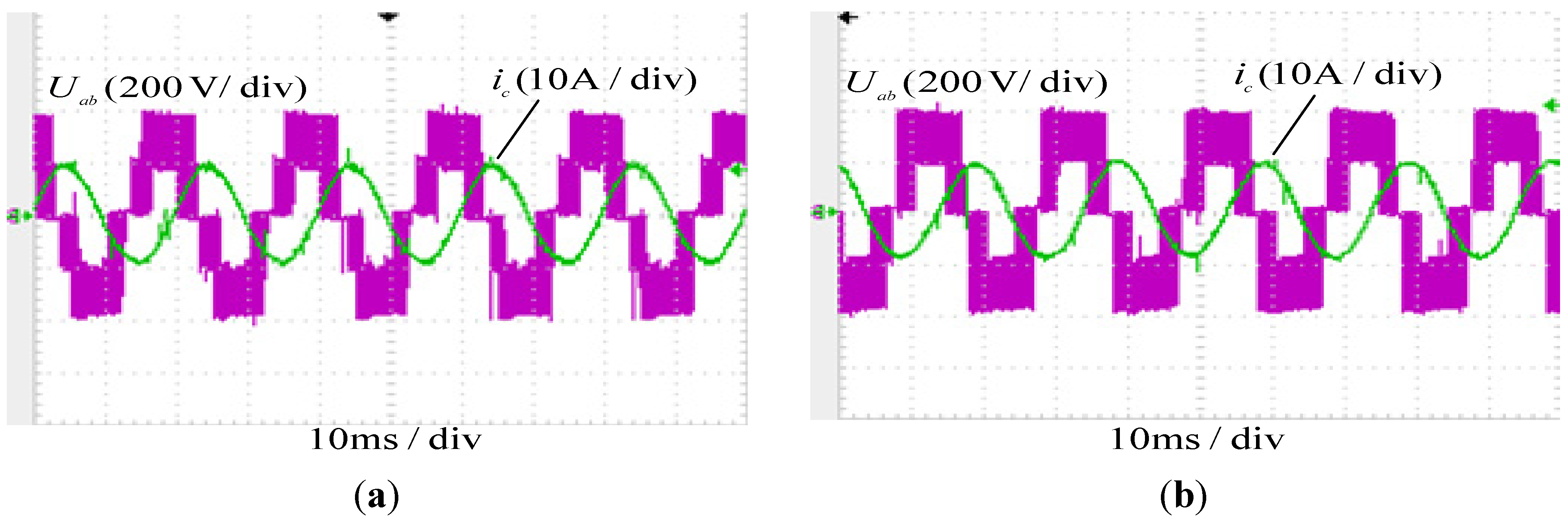

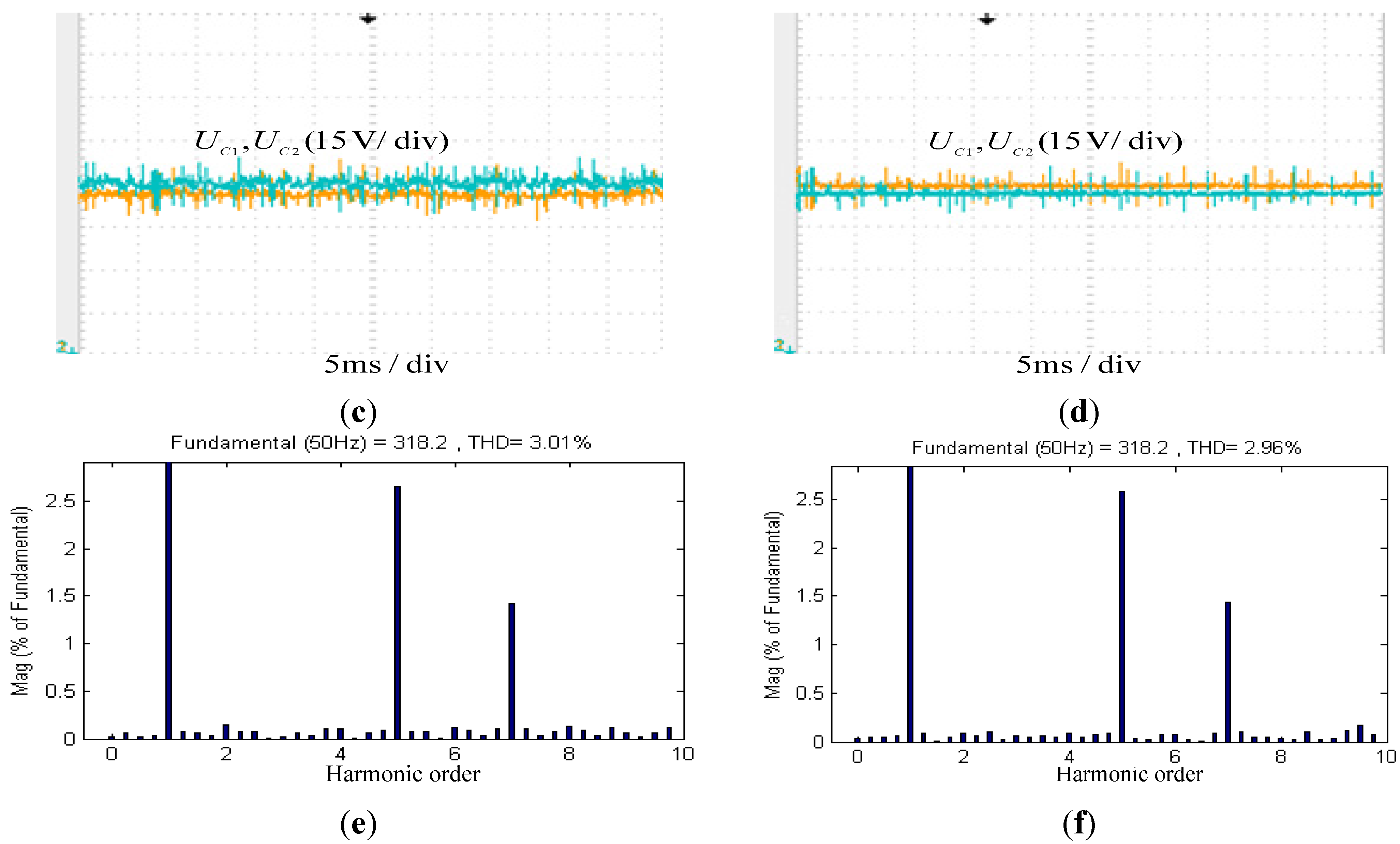

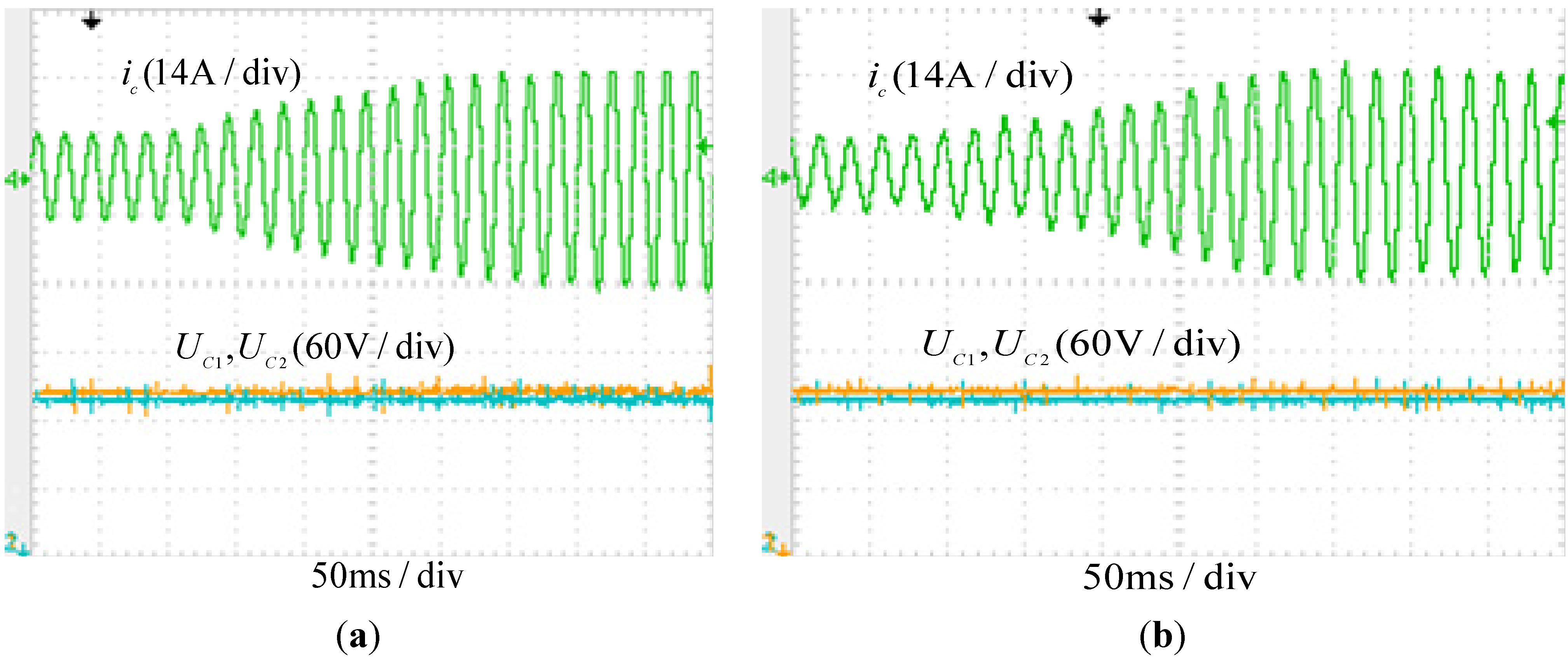

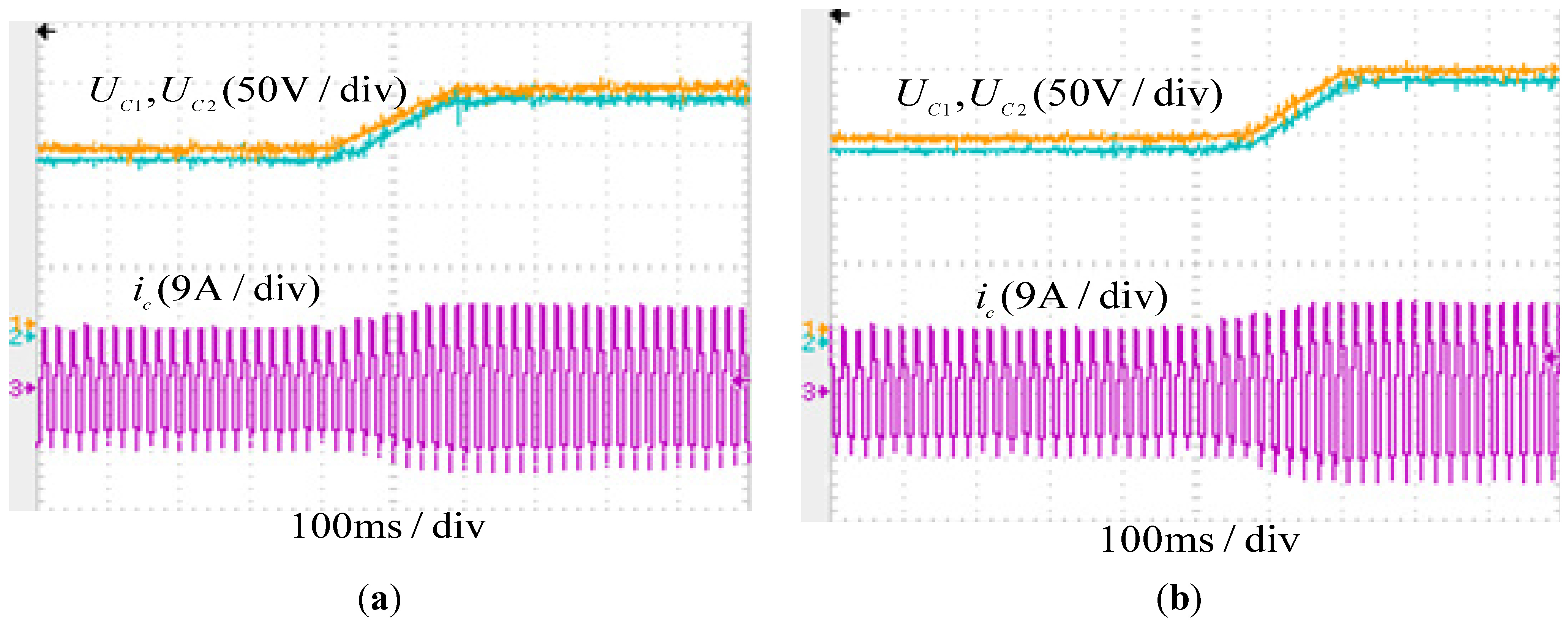

4.2. Experiment Results

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Rodriguez, J.; Bernet, S.; Bin, W.; Pontt, J.O.; Kour, S. Multilevel voltage source converter for industrial medium voltage drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Chaves, M.; Margato, E.; Silva, J.F.; Pinto, S.F. New approach in back-to-back m-level diode-clamped multilevel converter modeling and direct current bus voltages balancing. IEEE Trans. Power Electron. 2010, 3, 578–589. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, 5, 518–523. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverter. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Ke, M.; Frede, B. The impact of power switching devices on the thermal performance of a 10 MW wind power NPC converter. Energies 2012, 5, 2559–2577. [Google Scholar] [CrossRef]

- Bendre, A.; Venkataramanan, G.; Rosene, D.; Srinivasan, V. Modeling and design of a neutral-point voltage regulator for a three-level diode-clamped inverter using multiple-carrier modulation. IEEE Trans. Ind. Electron. 2006, 53, 718–726. [Google Scholar] [CrossRef]

- Pou, J.; Zaragoza, J.; Ceballos, S.; Saeedifard, M.; Boroyevich, D. A carrier-based PWM strategy with zero-sequence voltage injection for a three-level neutral-point-clamped converter. IEEE Trans. Power Electron. 2012, 27, 642–651. [Google Scholar] [CrossRef]

- Seo, J.H.; Choi, C.H.; Hyun, D.S. A new simplified space-vector PWM method for three-level inverters. IEEE Trans. Power Electron. 2001, 16, 545–550. [Google Scholar]

- Chaturvedi, P.K.; Jain, S.; Agarwal, P. Reduced switching loss pulse width modulation technique for three-level diode clamped inverter technique for three-level diode clamped inverter. IET Power Electron. 2011, 4, 393–399. [Google Scholar] [CrossRef]

- Beig, A.R.; Narayanan, G.; Ranganathan, V.T. Modified SVPWM algorithm for three level VSI with synchronized and symmetrical waveforms. IEEE Trans. Ind. Electron. 2007, 54, 486–494. [Google Scholar] [CrossRef]

- Zhang, H.; Finney, S.J.; Massoud, A.; Williams, B.W. An SVM algorithm to balance the capacitor voltages of the three-level NPC active power filter. IEEE Trans. Power Electron. 2008, 23, 2694–2702. [Google Scholar] [CrossRef]

- Pou, J.; Pindado, R.; Boroyevich, D.; Rodriguez, P. Evaluation of the low frequency neutral-point voltage oscillation in three-level inverter. IEEE Trans. Ind. Appl. 2005, 52, 1582–1588. [Google Scholar]

- Grigoletto, F.B.; Pinheiro, H. A space vector PWM modulation scheme for back-to-back three-level diode-clamped converters. In Proceedings of the Power Electronics Conference, 2009, COBEP'09, Bonito-Mato Grosso do Sul, Brazil, 27 September–1 October 2009; pp. 1058–1065.

- Choi, U.-M.; Lee, K.B. Space vector modulation strategy for neutral-point voltage balancing in three-level inverter systems. IET Power Electron. 2013, 6, 1390–1398. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Bordonau, J.; Boroyevich, D.; Somavilla, S. The nearest three virtual space vector PWM—A modulation for the comprehensive neutral-point balancing in the three-level NPC inverter. IEEE Power Electron. Lett. 2004, 2, 11–15. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Somavilla, S.; Bordonau, J.; Boroyevich, D. Capacitor voltage balance for the neutral-point-clamped converter using the virtual space vector concept with optimized spectral performance. IEEE Power Electron. Lett. 2007, 22, 1128–1135. [Google Scholar] [CrossRef]

- Hu, C.; Wang, Q.; Li, G.; Feng, J.; Jiang, W. A neutral-point potential balancing algorithm for three-level inverter based on virtual-space-vector. Trans. China Electrotech. Soc. 2009, 24, 100–107. [Google Scholar]

- Xia, C.; Shao, H.; Zhang, Y.; He, X. Adjustable proportional hybrid SVPWM strategy for neutral-point-clamped three-Level inverters. IEEE Trans. Ind. Electron. 2013, 60, 4234–4241. [Google Scholar] [CrossRef]

- Zhang, Y.; Zhao, Z.; Zhu, J. A hybrid PWM applied to high-power three-level inverter-fed induction-motor drives. IEEE Trans. Ind. Electron. 2011, 58, 3409–3420. [Google Scholar] [CrossRef]

- Jiang, W.D.; Du, S.W.; Chang, L.C.; Zhang, Y.; Zha, Q. Hybrid PWM strategy of SVPWM and VSVPWM for NPC three-level voltage-source inverter. IEEE Trans. Power Electron. 2010, 25, 2607–2619. [Google Scholar] [CrossRef]

- Govindaraju, C. Efficient sequential switching hybrid modulation techniques for multiphase multilevel inverters. IET Power Electron. 2011, 4, 557–569. [Google Scholar] [CrossRef]

- Das, S.; Narayanan, G. Novel switching sequences for a space-vector-modulated three-level inverter. IEEE Trans. Ind. Electron. 2012, 59, 1477–1487. [Google Scholar] [CrossRef]

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gui, S.W.; Lin, Z.J.; Huang, S.H. A Varied VSVM Strategy for Balancing the Neutral-Point Voltage of DC-Link Capacitors in Three-Level NPC Converters. Energies 2015, 8, 2032-2047. https://doi.org/10.3390/en8032032

Gui SW, Lin ZJ, Huang SH. A Varied VSVM Strategy for Balancing the Neutral-Point Voltage of DC-Link Capacitors in Three-Level NPC Converters. Energies. 2015; 8(3):2032-2047. https://doi.org/10.3390/en8032032

Chicago/Turabian StyleGui, Shi Weng, Zhen Jun Lin, and Sheng Hua Huang. 2015. "A Varied VSVM Strategy for Balancing the Neutral-Point Voltage of DC-Link Capacitors in Three-Level NPC Converters" Energies 8, no. 3: 2032-2047. https://doi.org/10.3390/en8032032