Flux-Balance Control for LLC Resonant Converters with Center-Tapped Transformers

Abstract

:1. Introduction

2. Analysis of Secondary Side Mismatched Leakage Inductances Effects

2.1. Analysis of the Magnetizing Current DC Value

2.2. Analysis of the Voltage Gain under Mismatched Condition

3. Proposed Flux-Balance Control Architecture

3.1. Description of the Proposed Control Architecture

3.2. Magnetizing Current Sampling Scheme

3.3. DC Value Estimation of the Magnetizing Current

3.4. Variable-Frequency-Variable-Duty-Pulse-Width-Modulator

4. Small-Signal Model and Controllers Design

4.1. Small-Signal Models Built Using System Identification

4.2. Flux-Balance Loop Controller Design

4.3. Output-Voltage Loop Controller Design

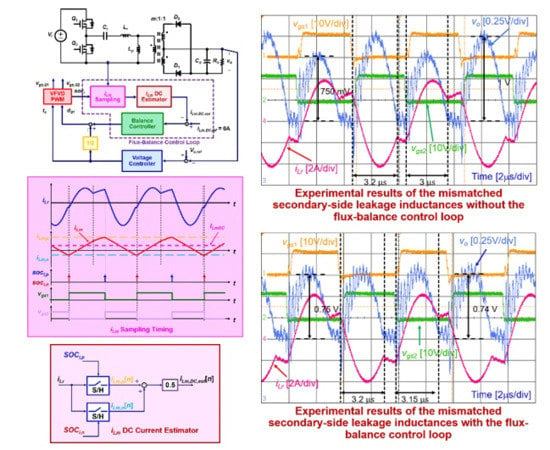

5. Simulation and Experimental Verification

5.1. Steady-State Operation

5.2. Dynamic-State Operation

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Deng, J.; Li, S.; Hu, S.; Mi, C.; Ma, R. Design methodology of LLC resonant converters for electric vehicle battery chargers. IEEE Trans. Veh. Technol. 2014, 63, 1581–1592. [Google Scholar] [CrossRef]

- Shen, Y.; Zhao, W.; Chen, Z.; Ca, C. Full-bridge LLC resonant converter with series-parallel connected transformers for electric vehicle on-board charger. IEEE Access 2018, 6, 13490–13500. [Google Scholar] [CrossRef]

- Amirahmadi, A.; Domb, M.; Persson, E. High power density high efficiency wide input voltage range LLC resonant converter utilizing E-mode GaN switches. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 350–354. [Google Scholar]

- Joung, M.; Kim, H.; Baek, J. Dynamic analysis and optimal design of high efficiency full bridge LLC resonant converter for server power system. In Proceedings of the 2012 27th Annual IEEE Applied Power Electronics Conference and Exposition (APEC202), Orlando, FL, USA, 5–9 February 2012; pp. 1292–1297. [Google Scholar]

- Kim, B.-C.; Park, K.-B.; Kim, C.-E.; Lee, B.-H.; Moon, G.-W. LLC resonant converter with adaptive link-voltage variation for a high-power-density adapter. IEEE Trans. Power Electron. 2010, 25, 2248–2252. [Google Scholar] [CrossRef]

- Hu, S.; Deng, J.; Mi, C.; Zhang, M. LLC resonant converters for PHEV battery chargers. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC2013), Long Beach, CA, USA, 17–21 March 2013; pp. 3051–3054. [Google Scholar]

- Wu, H.; Mu, T.; Gao, X.; Xing, Y. A secondary-side phase-shift-controlled LLC resonant converter with reduced conduction loss at normal operation for hold-up time compensation application. IEEE Trans. Power Electron. 2015, 30, 5352–5357. [Google Scholar] [CrossRef]

- D’Cruz, R.; Rajesh, M. Half bridge LLC resonant DC-DC converter for solar array simulator application. In Proceedings of the 2015 International Conference on Technological Advancements in Power and Energy (TAP Energy), Kollam, India, 24–26 June 2015; pp. 138–143. [Google Scholar]

- Yang, Y.-R. A half-bridge LLC resonant converter with loose-coupling transformer and transition capacitor. In Proceedings of the 2014 9th IEEE Conference on Industrial Electronics and Applications, Hangzhou, China, 9–11 June 2014; pp. 1344–1349. [Google Scholar]

- Huang, Y.-C.; Hsieh, Y.-C.; Lin, Y.-C.; Chiu, H.-R.; Lin, J.-Y. Study and implementation on start-up control of full-bridge LLC resonant converter. In Proceedings of the 2018 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Bangkok, Thailand, 6–9 June 2018. [Google Scholar]

- Lin, R.-L.; Lin, C.-W. Design criteria for resonant tank of LLC DC-DC resonant converter. In Proceedings of the 36th Annual Conference on IEEE Industrial Electronics Society (IECON2010), Glendale, AZ, USA, 7–10 November 2010; pp. 427–432. [Google Scholar]

- Sato, M.; Nagaoka, S.; Uematsu, T.; Zaitsu, T. Mechanism of current imbalance in LLC resonant converter with center tapped transformer. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 118–122. [Google Scholar]

- Jung, J.-H. Bifilar winding of a center-tapped transformer including integrated resonant inductance for LLC resonant converters. IEEE Trans. Power Electron. 2013, 28, 615–620. [Google Scholar] [CrossRef]

- Li, M.; Chen, Q.; Ren, X.; Zhang, Y.; Jin, K.; Chen, B. The integrated LLC resonant converter using center-tapped transformer for on-board EV charger. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE2015), Montreal, QC, Canada, 20–24 September 2015; pp. 6293–6298. [Google Scholar]

- Panov, Y.; Jovanović, M.; Irving, B. Novel transformer-flux-balancing control of dual-active-bridge bidirectional converters. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC2015), Charlotte, NC, USA, 15–19 March 2015; pp. 42–49. [Google Scholar]

- Murakami, Y.; Sato, T.; Nishijima, K.; Nabeshima, T. Small signal analysis of LLC current resonant converters using equivalent source model. In Proceedings of the 42nd Annual Conference of the IEEE Industrial Electronics Society (IECON2016), Florence, Italy, 23–26 October 2016; pp. 1417–1422. [Google Scholar]

- Tian, S.; Lee, F.; Li, Q. A simplified equivalent circuit model of series resonant converter. IEEE Trans. Power Electron. 2016, 31, 3922–3931. [Google Scholar] [CrossRef]

- Tian, S.; Lee, F.; Li, Q. Equivalent circuit modeling of LLC resonant converter. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC2016), Long Beach, CA, USA, 20–24 March 2016; pp. 1608–1615. [Google Scholar]

- Fang, Z.; Wang, J.; Duan, S.; Xiao, L.; Hu, G.; Liu, Q. Rectifier current control for an LLC resonant converter based on a simplified linearized model. Energies 2018, 11, 579. [Google Scholar] [CrossRef]

- MATLAB. System Identification Overview. Available online: https://www.mathworks.com/help/ident/gs/about-system-identification.html (accessed on 30 May 2019).

- MATLAB. System Identification Toolbox. Available online: https://www.mathworks.com/products/sysid.html (accessed on 30 May 2019).

- Simone, S.; Adragna, C.; Spini, C. Design guideline for magnetic integration in LLC resonant converters. In Proceedings of the 2008 International Symposium on Power Electronics, Electrical Drives, Automation and Motion (SPEEDAM2008), Ischia, Italy, 11−13 June 2008; pp. 950–957. [Google Scholar]

- Huang, H. FHA-based voltage gain function with harmonic compensation for LLC resonant converter. In Proceedings of the 25th Annual IEEE Applied Power Electronics Conference and Exposition (APEC2010), Palm Springs, CA, USA, 21−25 February 2010; pp. 1770–1777. [Google Scholar]

| Symbol | Description | Quantity |

|---|---|---|

| Vi | input voltage | 380 V |

| Vo | output voltage | 20 V |

| Po,rated | rated output power | 200 W |

| n | transformer turns ratio | 10 |

| Lm | magnetizing inductance | 310 μH |

| Llk1 | leakage inductance in the primary side | 6.386 μH |

| Llk2,pos | leakage inductance in the secondary side during the positive cycle | 53 nH |

| Llk2,neg | leakage inductance in the secondary side during negative cycle (matched condition) | 53 nH |

| Llk2,neg | leakage inductance in the secondary side during negative cycle (mismatched condition) | 167.77 nH |

| Lext | external resonant inductance | 42 μH |

| Cr | resonant capacitance | 20 nF |

| Co | output capacitance | 1000 μF |

| rCo | equivalent-series-resistance of the output capacitance | 40 mΩ |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, Y.-C.; Chen, D.-T.; Chen, C.-J. Flux-Balance Control for LLC Resonant Converters with Center-Tapped Transformers. Energies 2019, 12, 3211. https://doi.org/10.3390/en12173211

Lin Y-C, Chen D-T, Chen C-J. Flux-Balance Control for LLC Resonant Converters with Center-Tapped Transformers. Energies. 2019; 12(17):3211. https://doi.org/10.3390/en12173211

Chicago/Turabian StyleLin, Yuan-Chih, Ding-Tang Chen, and Ching-Jan Chen. 2019. "Flux-Balance Control for LLC Resonant Converters with Center-Tapped Transformers" Energies 12, no. 17: 3211. https://doi.org/10.3390/en12173211