Research on Unbalance Fault-Tolerant Control Strategy of Modular Multilevel Photovoltaic Grid-Connected Inverter

Abstract

:1. Introduction

- The average switching model of MMC with asymmetric fault is established. Proposed an improved fault-tolerant control strategy by bypassing fault SMs and dividing the converter work status into normal operation status and asymmetric fault-tolerant operation status.

- The focus of MMC on fault-tolerant control in two applications of photovoltaic grid-connected and HVDC transmission is different. This paper is mainly used to reduce total harmonic distortion rate of the grid-connected current; MMC can continue stable operation.

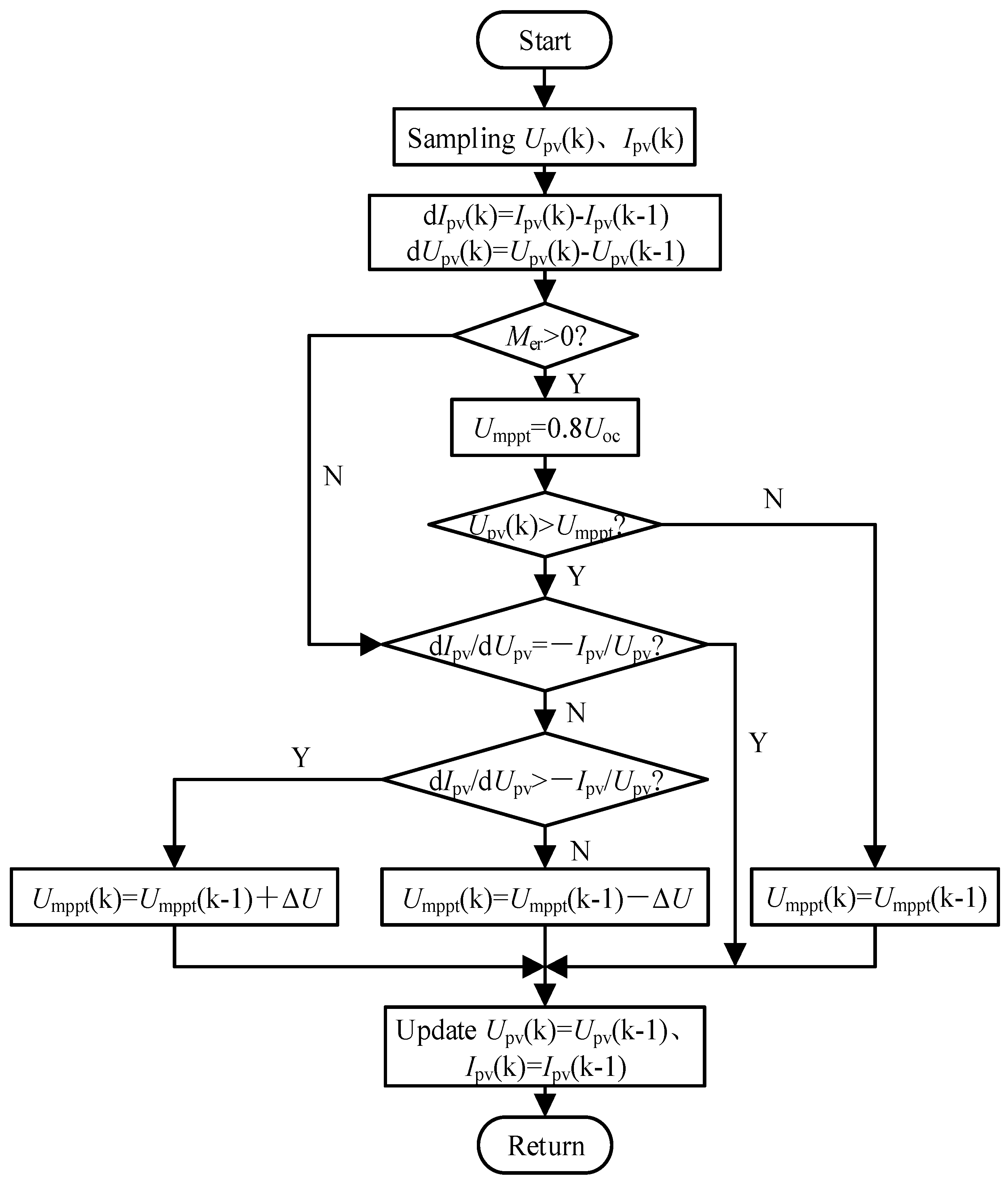

- The constant voltage tracking method of maximum power point tracking (MPPT) cannot complete accurate tracking when the photovoltaic inverter fault, in this case, the improved MPPT control method, is proposed combined with the incremental conductance algorithm; it can realize stable and accurate fault tolerance of MPPT control, and the problem of the voltage support and fault voltage recovery of the DC side bus are solved.

2. MMC Average Switch Model under Fault-Tolerance

3. Improvement of the MPPT Control in Asymmetric Fault-Tolerance

4. Simulation Research

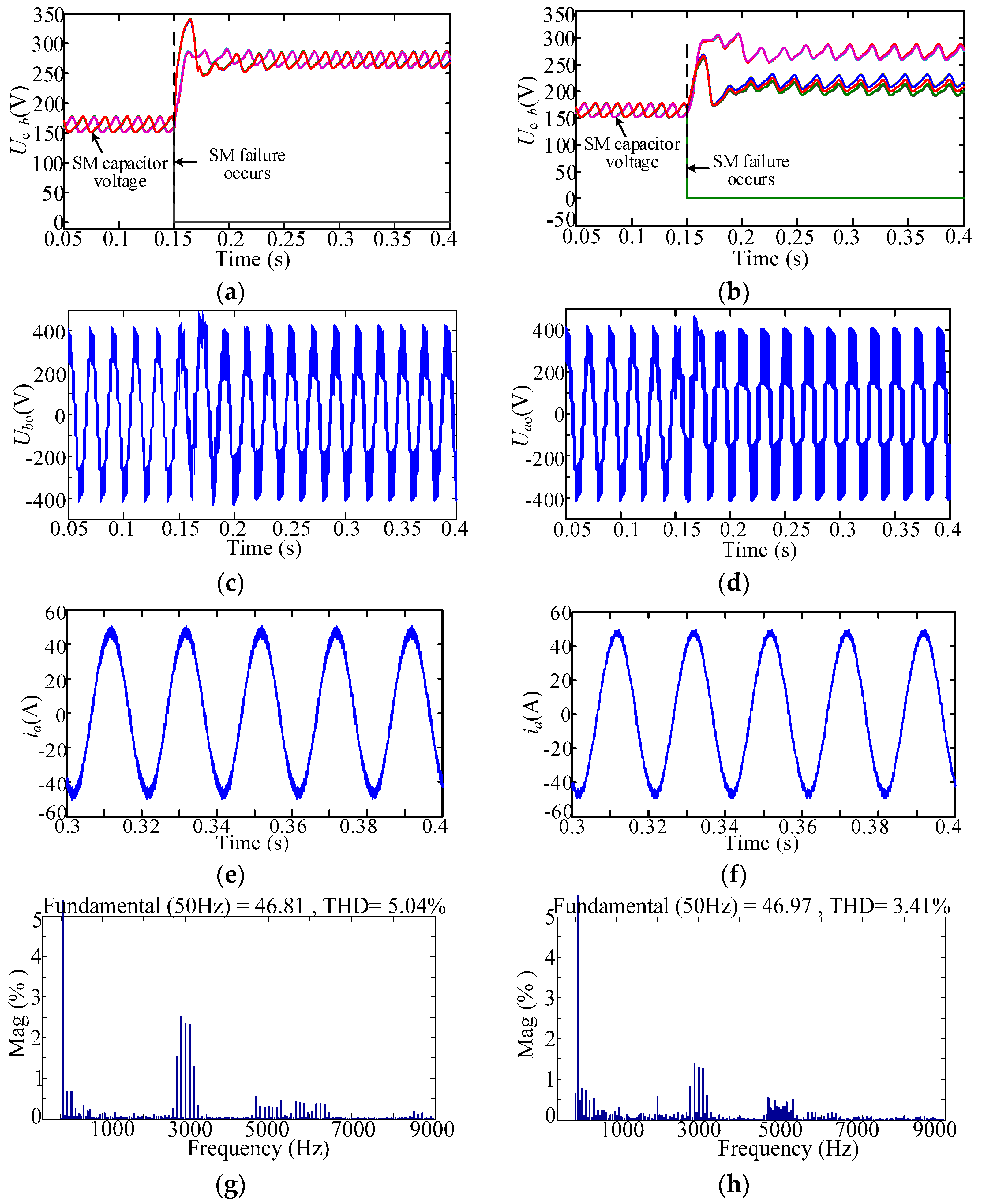

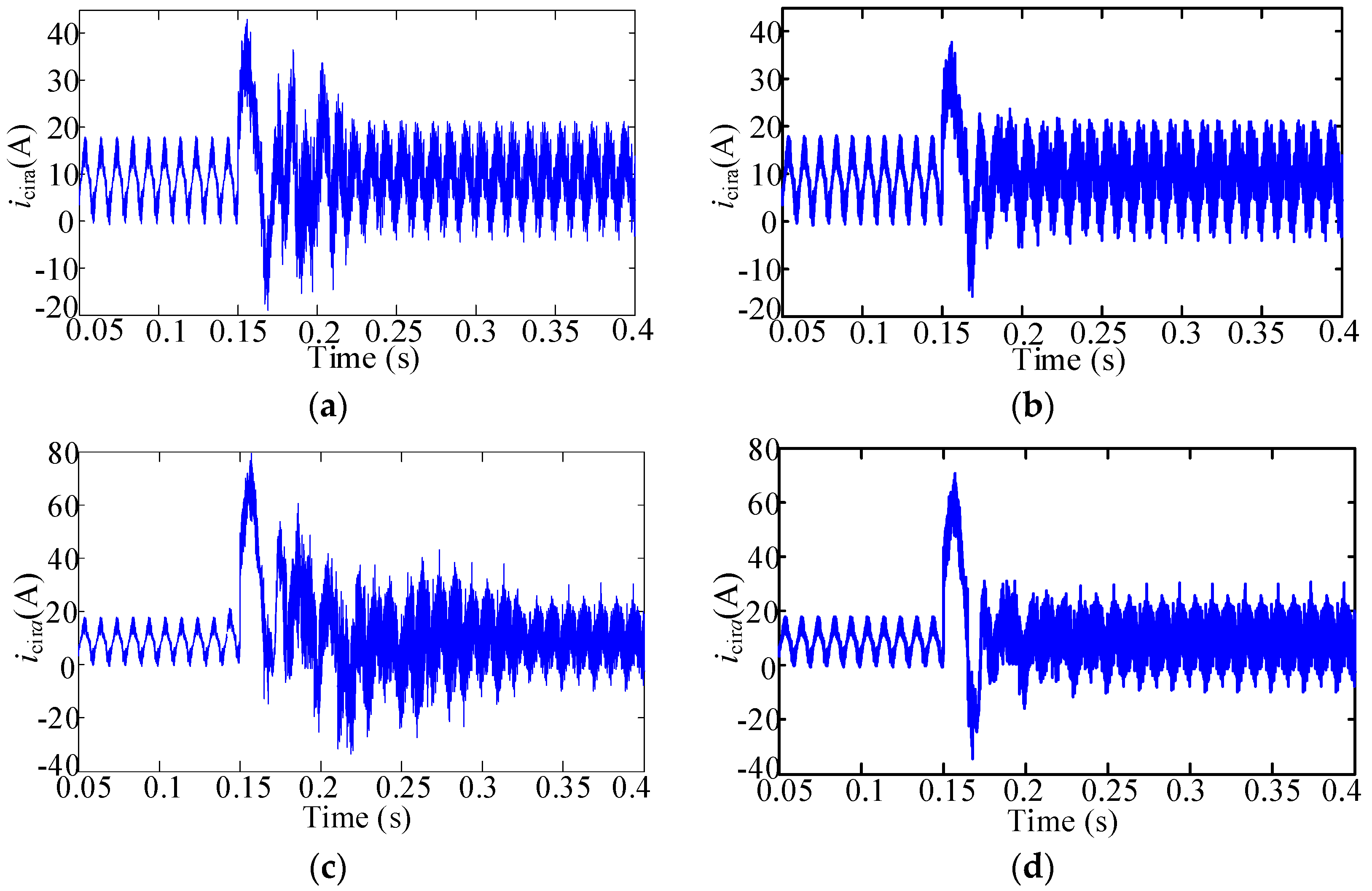

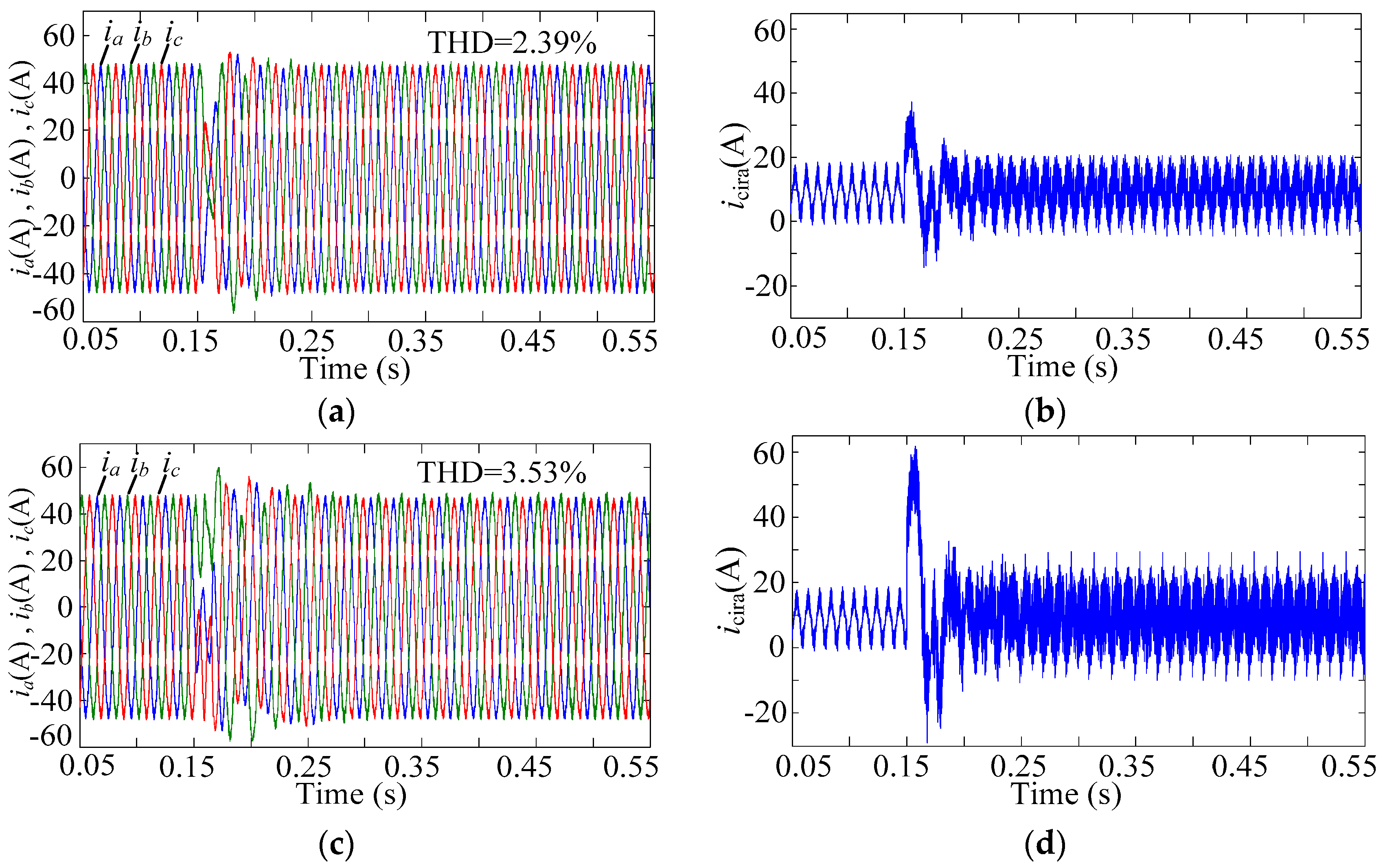

4.1. Simulation Results Analysis of a SM Fault in Phase A

4.2. Analysis of Simulation Results of Two SM Faults in Phase A

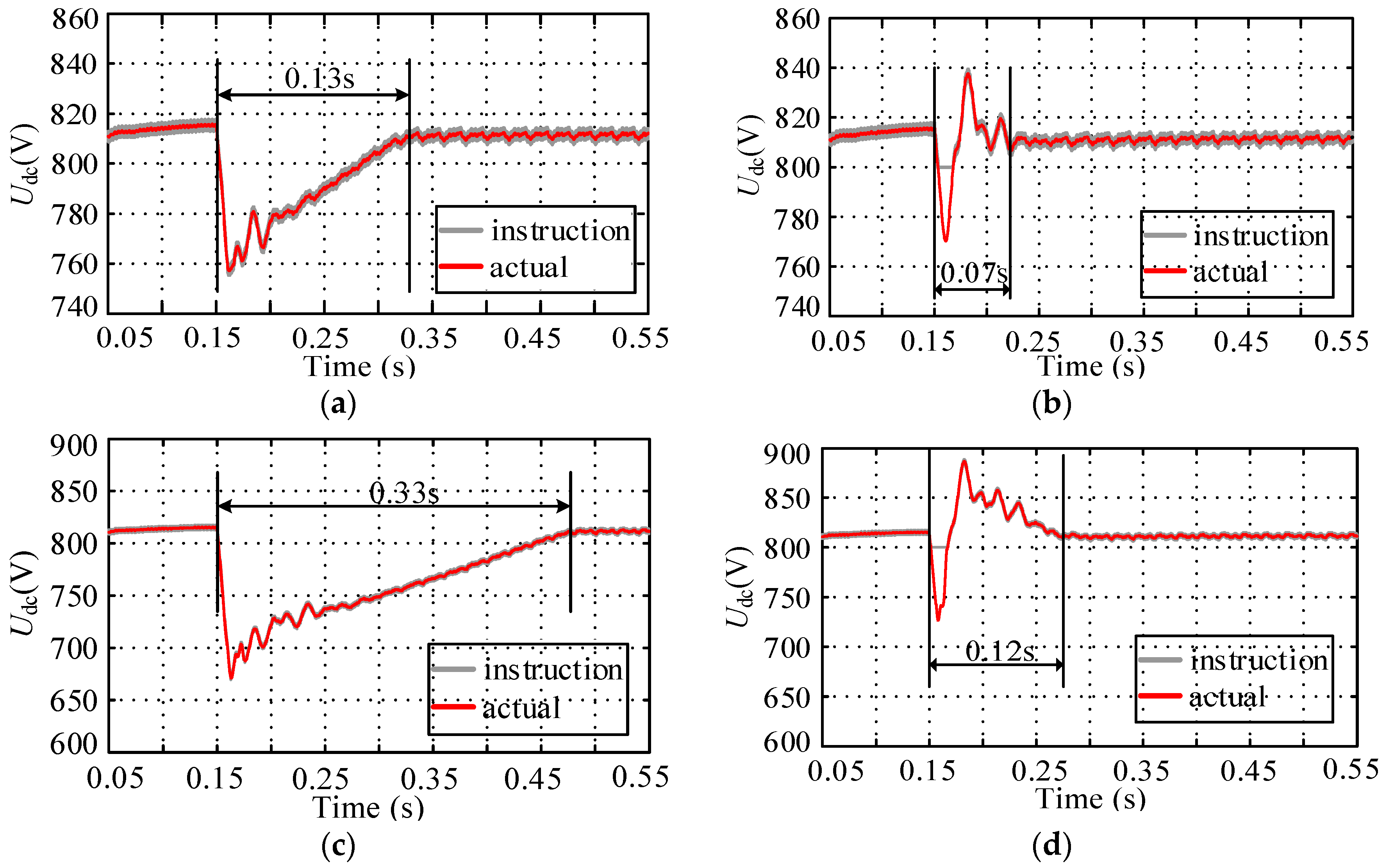

4.3. Simulation Analysis of the MPPT Control Link in Fault-Tolerance

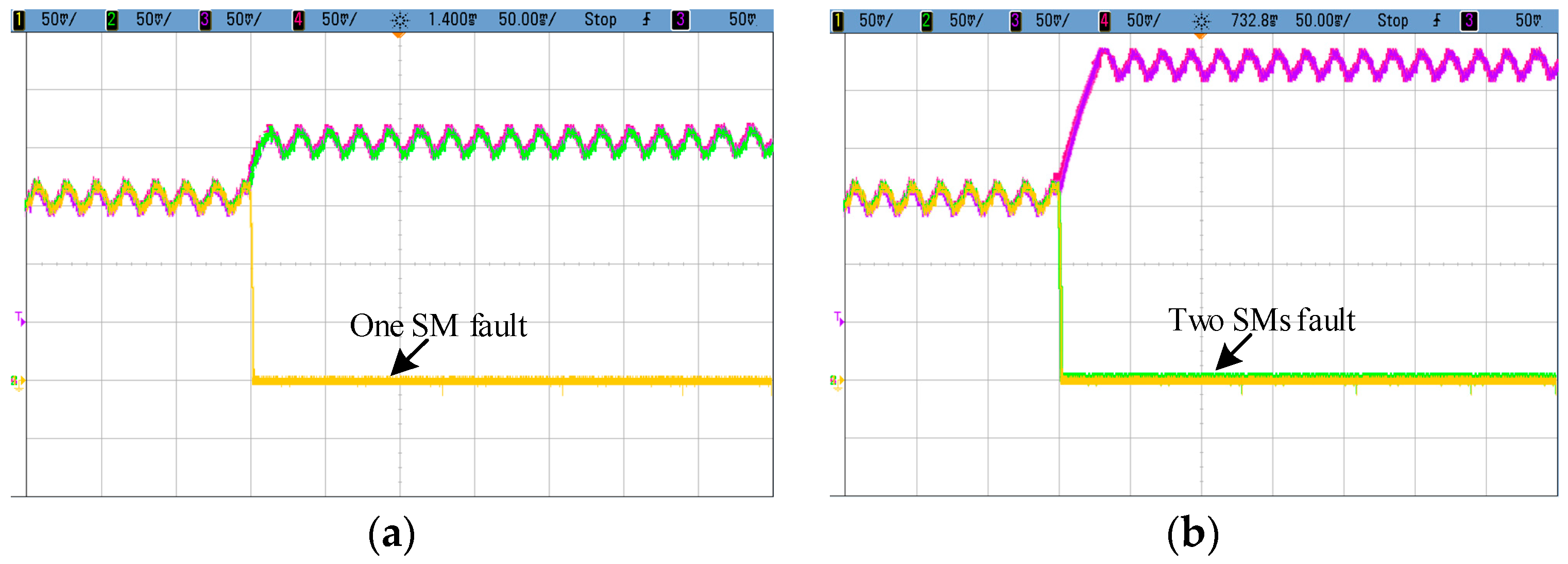

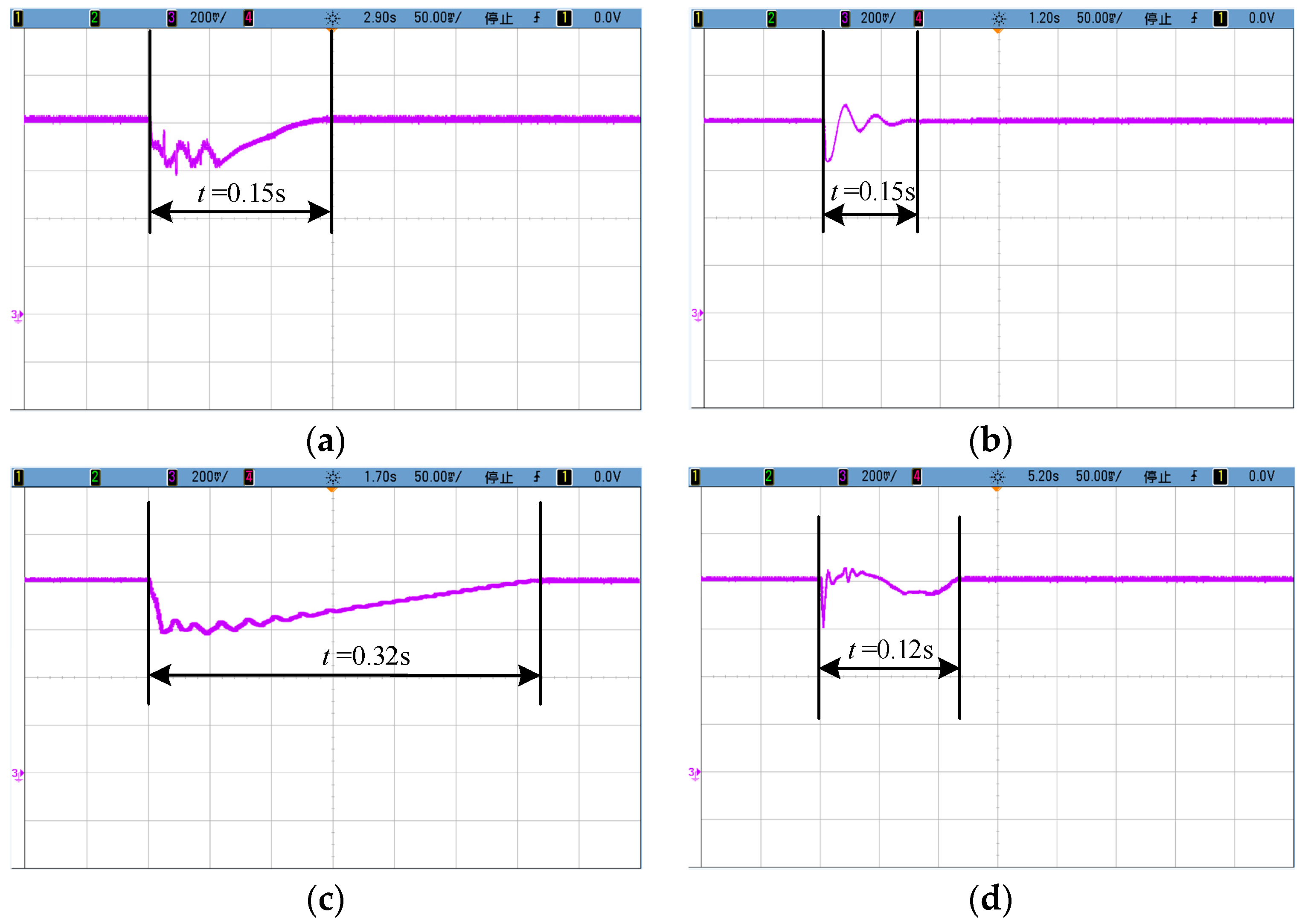

5. Experimental Verification

6. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Moranchel, M.; Bueno, E.; Sanz, I.; Rodríguez, F.J. New Approaches to Circulating Current Controllers for Modular Multilevel Converters. Energies 2017, 10, 86. [Google Scholar] [CrossRef]

- Li, X.; Song, Q.; Liu, W.; Xu, S.; Zhu, Z.; Li, X. Performance Analysis and Optimization of Circulating Current Control for Modular Multilevel Converter. IEEE Trans. Ind. Electron. 2016, 63, 716–727. [Google Scholar] [CrossRef]

- Xu, J.; Zhao, P.; Zhao, C. Reliability Analysis and Redundancy Configuration of MMC with Hybrid SM Topologies. IEEE Trans. Power Electron. 2016, 31, 2720–2729. [Google Scholar] [CrossRef]

- Zhang, F.; Li, W.; Joós, G. A Voltage-Level-Based Model Predictive Control of Modular Multilevel Converter. IEEE Trans. Ind. Electron. 2016, 63, 5301–5312. [Google Scholar] [CrossRef]

- Mehrasa, M.; Pouresmaeil, E.; Zabihi, S.; Catalão, J.P. Dynamic model, control and stability analysis of mmc in HVDC transmission systems. IEEE Trans. Power Deliv. 2017, 32, 1471–1482. [Google Scholar] [CrossRef]

- Mehrasa, M.; Pouresmaeil, E.; Zabihi, S.; Vechiu, I.; Catalão, J.P. A multi-loop control technique for the stable operation of modular multilevel converters in HVDC transmission systems. Int. J. Electr. Power Energy Syst. 2018, 96, 194–207. [Google Scholar] [CrossRef]

- Mehrasa, M.; Pouresmaeil, E.; Zabihi, S.; Trujillo Caballero, J.C.; Catalão, J.P. A novel modulation function-based control of modular multilevel converters for high voltage direct current transmission systems. Energies 2016, 9, 867. [Google Scholar] [CrossRef]

- Gowaid, I.; Adam, G.; Ahmed, S.; Holliday, D.; Williams, B. Analysis and Design of a Modular Multilevel Converter with Trapezoidal Modulation for Medium and High Voltage dc-dc Transformers. IEEE Trans. Power Electron. 2015, 30, 5439–5457. [Google Scholar] [CrossRef]

- Quraan, M.; Yeo, T.; Tricoli, P. Modular Multilevel Converters for HVDC Applications: Review on Converter Cells and Functionalities. IEEE Trans. Power Electron. 2015. [Google Scholar] [CrossRef]

- Soong, T.; Lehn, P.W. Internal Power Flow of a Modular Multilevel Converter with Distributed Energy Resources. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 1127–1138. [Google Scholar] [CrossRef]

- Pouresmaeil, E.; Mehrasa, M.; Shokridehaki, M.A.; Rodrigues, E.M.G.; Catalão, J.P.S. Control of Modular Multilevel Converters for Integration of Distributed Generation Sources into the Power Grid. In Proceedings of the 2015 IEEE International Conference on Smart Energy Grid Engineering (SEGE), Oshawa, ON, Canada, 17–19 August 2015; pp. 1–6. [Google Scholar]

- Du, S.; Liu, J. A Study on DC Voltage Control for Chopper-Cell-Based Modular Multilevel Converters in D-STATCOM Application. IEEE Trans. Power Deliv. 2013, 28, 2030–2038. [Google Scholar] [CrossRef]

- Fei, R.; Gong, X.; Huang, S. A novel grid-connected PV system based on MMC to get the maximum power under partial shading conditions. IEEE Trans. Power Electron. 2017, 32, 4320–4333. [Google Scholar]

- Bayat, H.; Yazdani, A. A Power Mismatch Elimination Strategy for an MMC-Based Photovoltaic System. IEEE Trans. Energy Convers. 2018. [Google Scholar] [CrossRef]

- Rojas, C.A.; Kouro, S.; Perez, M.A.; Echeverria, J. DC-DC MMC for HVDC Grid Interface of Utility-Scale Photovoltaic Conversion Systems. IEEE Trans. Ind. Electron. 2018, 65, 352–362. [Google Scholar] [CrossRef]

- Mehrasa, M.; Pouresmaeil, E.; Akorede, M.F.; Zabihi, S.; Catalão, J.P. Function-based modulation control for modular multilevel converters under varying loading and parameters conditions. IET Gener. Transm. Distrib. 2017, 11, 3222–3230. [Google Scholar] [CrossRef]

- Mehrasa, M.; Pouresmaeil, E.; Taheri, S.; Vechiu, I.; Catalão, J.P. Novel Control Strategy for Modular Multilevel Converters Based on Differential Flatness Theory. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 6, 888–897. [Google Scholar] [CrossRef]

- Li, S.; Wang, X.; Yao, Z.; Li, T.; Peng, Z. Circulating Current Suppressing Strategy for MMC-HVDC Based on Non-ideal Proportional Resonant Controllers Under Unbalanced Grid Conditions. IEEE Trans. Power Electron. 2015, 30, 387–397. [Google Scholar] [CrossRef]

- Moon, J.W.; Kim, C.S.; Park, J.W.; Kang, D.W.; Kim, J.M. Circulating Current Control in MMC Under the Unbalanced Voltage. IEEE Trans. Power Deliv. 2013, 28, 1952–1959. [Google Scholar] [CrossRef]

- Li, W.; Li, G.; Zeng, R.; Ni, K.; Hu, Y.; Wen, H. The Fault Detection, Localization, and Tolerant Operation of Modular Multilevel Converters with an Insulated Gate Bipolar Transistor (IGBT) Open Circuit Fault. Energies 2018, 11, 837. [Google Scholar] [CrossRef]

- Li, B.; Zhang, Y.; Yang, R.; Xu, R.; Xu, D.; Wang, W. Seamless transition control for modular multilevel converters when inserting a cold-reserve redundant SM. IEEE Trans. Power Electron. 2015, 30, 4052–4057. [Google Scholar] [CrossRef]

- Li, K.; Yuan, L.; Zhao, Z.; Lu, S.; Zhang, Y. Fault-Tolerant Control of MMC with Hot Reserved SMs Based on Carrier Phase Shift Modulation. IEEE Trans. Power Electron. 2017, 32, 6778–6791. [Google Scholar] [CrossRef]

- Li, B.; Shi, S.; Wang, B.; Wang, G.; Wang, W.; Xu, D. Fault Diagnosis and Tolerant Control of Single IGBT Open-Circuit Failure in Modular Multilevel Converters. IEEE Trans. Power Electron. 2016, 31, 3165–3176. [Google Scholar] [CrossRef]

- Deng, F.; Tian, Y.; Zhu, R.; Chen, Z. Fault-tolerant approach for modular multilevel converters under SM faults. IEEE Trans. Ind. Electron. 2016, 63, 7253–7263. [Google Scholar] [CrossRef]

- Hu, P.; Jiang, D.; Zhou, Y.; Liang, Y.; Guo, J.; Lin, Z. Energy-balancing Control Strategy for Modular Multilevel Converters Under SM Fault Conditions. IEEE Trans. Power Electron. 2014, 29, 5021–5030. [Google Scholar] [CrossRef]

- Son, G.T.; Lee, H.J.; Nam, T.S.; Chung, Y.H.; Lee, U.H.; Baek, S.T.; Hur, K.; Park, J.W. Design and control of a modular multilevel HVDC converter with redundant power modules for noninterruptible energy transfer. IEEE Trans. Power Deliv. 2012, 27, 1611–1619. [Google Scholar]

- Liu, H.; Loh, P.C.; Blaabjerg, F. Review of fault diagnosis and faulttolerant control for modular multilevel converter of HVDC. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society (IECON 2013), Vienna, Austria, 10–13 November 2013; pp. 1242–1247. [Google Scholar]

- Choi, J.; Han, B.; Kim, H. New scheme of phase-shifted carrier pwm for modular multilevel converter with redundancy SMs. IEEE Trans. Power Deliv. 2016, 31, 407–409. [Google Scholar] [CrossRef]

- Li, K.; Zhao, Z.; Yuan, L.; Lu, S.; Pan, B.; Lu, Z. Fault tolerant control of MMC with redundant sub-modules based on carrier phase shift modulation. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 2613–2619. [Google Scholar]

- Song, W.; Huang, A. Fault-tolerant design and control strategy for cascaded H-bridge multilevel converter-based STATCOM. IEEE Trans. Ind. Electron. 2010, 57, 2700–2708. [Google Scholar] [CrossRef]

- Deng, F.; Chen, Z.; Khan, M.R.; Zhu, R. Fault Detection and Localization Method for Modular Multilevel Converters. IEEE Trans. Power Electron. 2015, 30, 2721–2732. [Google Scholar] [CrossRef]

- Choi, J.; Han, B. An improved phase-shifted carrier PWM for modular multilevel converters with redundancy sub-modules. J. Power Electron. 2016, 16, 473–479. [Google Scholar] [CrossRef]

- Liu, Y.; Chen, Q.; Li, N.; Xie, B.; Wang, J.; Ji, Y. On DC-side Impedance Frequency Characteristics Analysis and DC Voltage Ripple Prediction under Unbalance Conditions for MMC-HVDC System Based on Maximum Modulation Index. J. Power Electron. 2016, 16, 319–328. [Google Scholar] [CrossRef]

- Hagiwara, M.; Akagi, H. PWM control and experiment of modular multilevel converters. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 154–161. [Google Scholar]

- Hagiwara, M.; Akagi, H. Control and Experiment of Pulse width-Modulated Modular Multilevel Converters. IEEE Trans. Power Electron. 2009, 24, 1737–1746. [Google Scholar] [CrossRef]

- Akagi, H. Classification, terminology, and application of the modular multilevel cascade converter (MMCC). IEEE Trans. Power Electron. 2011, 26, 3119–3130. [Google Scholar] [CrossRef]

- Song, Q.; Liu, W.; Li, X.; Rao, H.; Xu, S.; Li, L. A Steady-State Analysis Method for a Modular Multilevel Converter. IEEE Trans. Power Electron. 2013, 28, 3702–3713. [Google Scholar] [CrossRef]

- Wu, W.; Wu, X.; Yin, J.; Jing, L.; Wang, S.; Li, J. Characteristic Analysis and Fault-Tolerant Control of Circulating Current for Modular Multilevel Converters under Sub-Module Faults. Energies 2017, 10, 1827. [Google Scholar] [CrossRef]

| Parameters | Value | Parameters | Value |

|---|---|---|---|

| DC bus voltage | 800 V | Amount of SM (M + N) | 5 |

| Inductance of arm | 1.5 mH | Current loop Kp | 10 |

| Capacitance of SM | 2200 μF | Current loop Kr | 16 |

| Grid-side filtering inductance | 3 mH | Current loop ωc | 5 |

| Switching frequency | 1 kHz | Voltage loop factor | 1 |

| Rated power | 7 KW | ||

| Grid voltage | 311 V | - | - |

| Grid frequency | 50 Hz | - | - |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liu, Y.; Li, D.; Jin, Y.; Wang, Q.; Song, W. Research on Unbalance Fault-Tolerant Control Strategy of Modular Multilevel Photovoltaic Grid-Connected Inverter. Energies 2018, 11, 1368. https://doi.org/10.3390/en11061368

Liu Y, Li D, Jin Y, Wang Q, Song W. Research on Unbalance Fault-Tolerant Control Strategy of Modular Multilevel Photovoltaic Grid-Connected Inverter. Energies. 2018; 11(6):1368. https://doi.org/10.3390/en11061368

Chicago/Turabian StyleLiu, Yiqi, Danhua Li, Yu Jin, Qingbo Wang, and Wenlong Song. 2018. "Research on Unbalance Fault-Tolerant Control Strategy of Modular Multilevel Photovoltaic Grid-Connected Inverter" Energies 11, no. 6: 1368. https://doi.org/10.3390/en11061368