IGBT Dynamic Loss Reduction through Device Level Soft Switching

Abstract

:1. Introduction

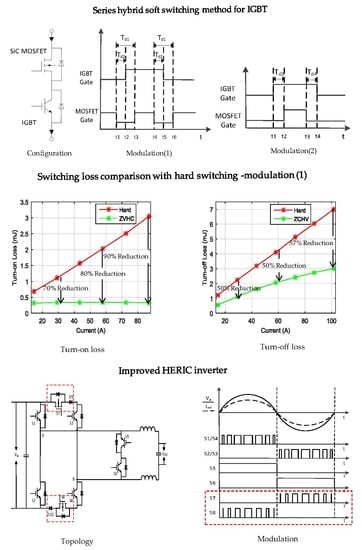

2. IGBT Soft Switching Classification

3. Hybrid Soft Switching Method Based on Device Level

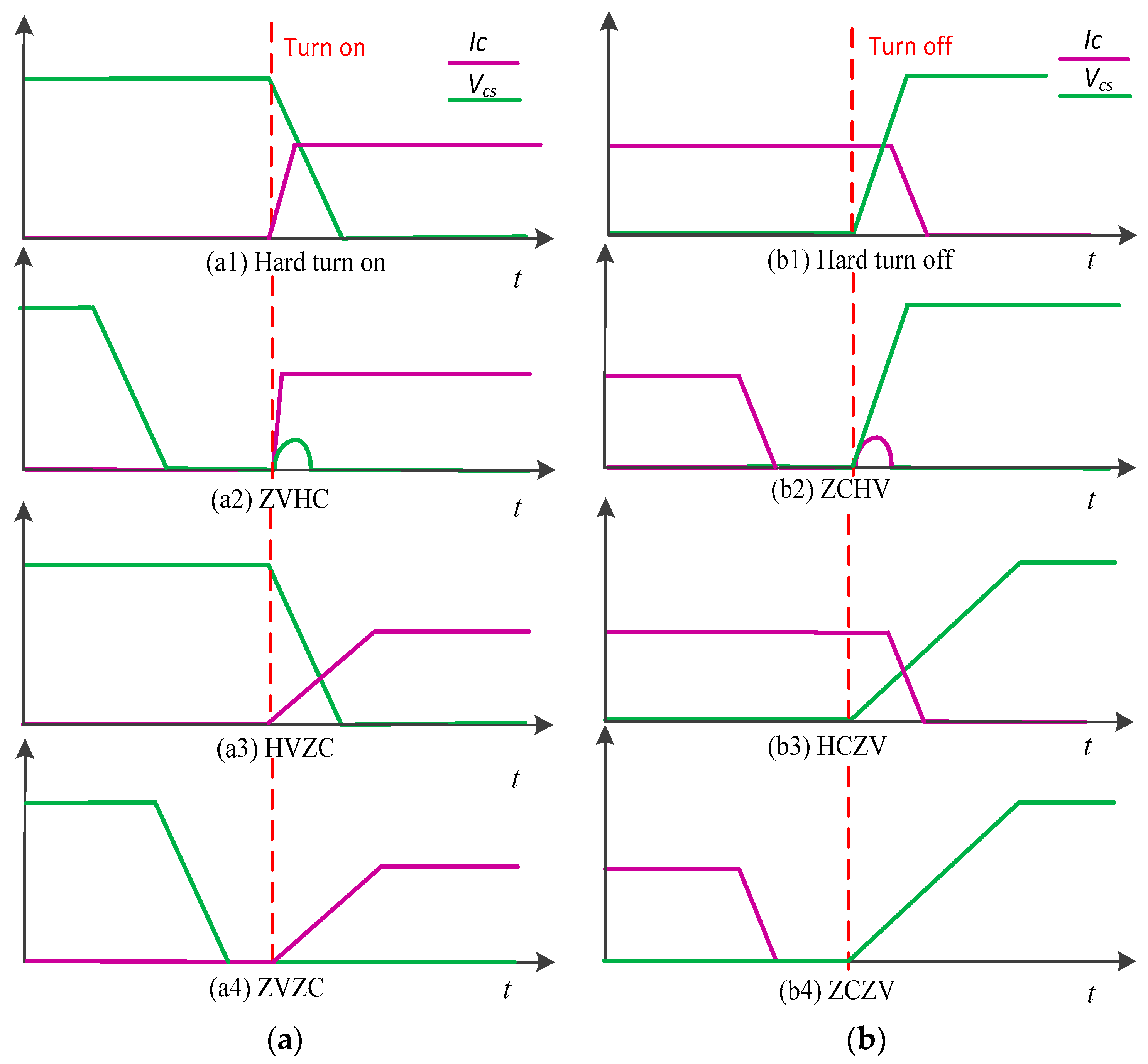

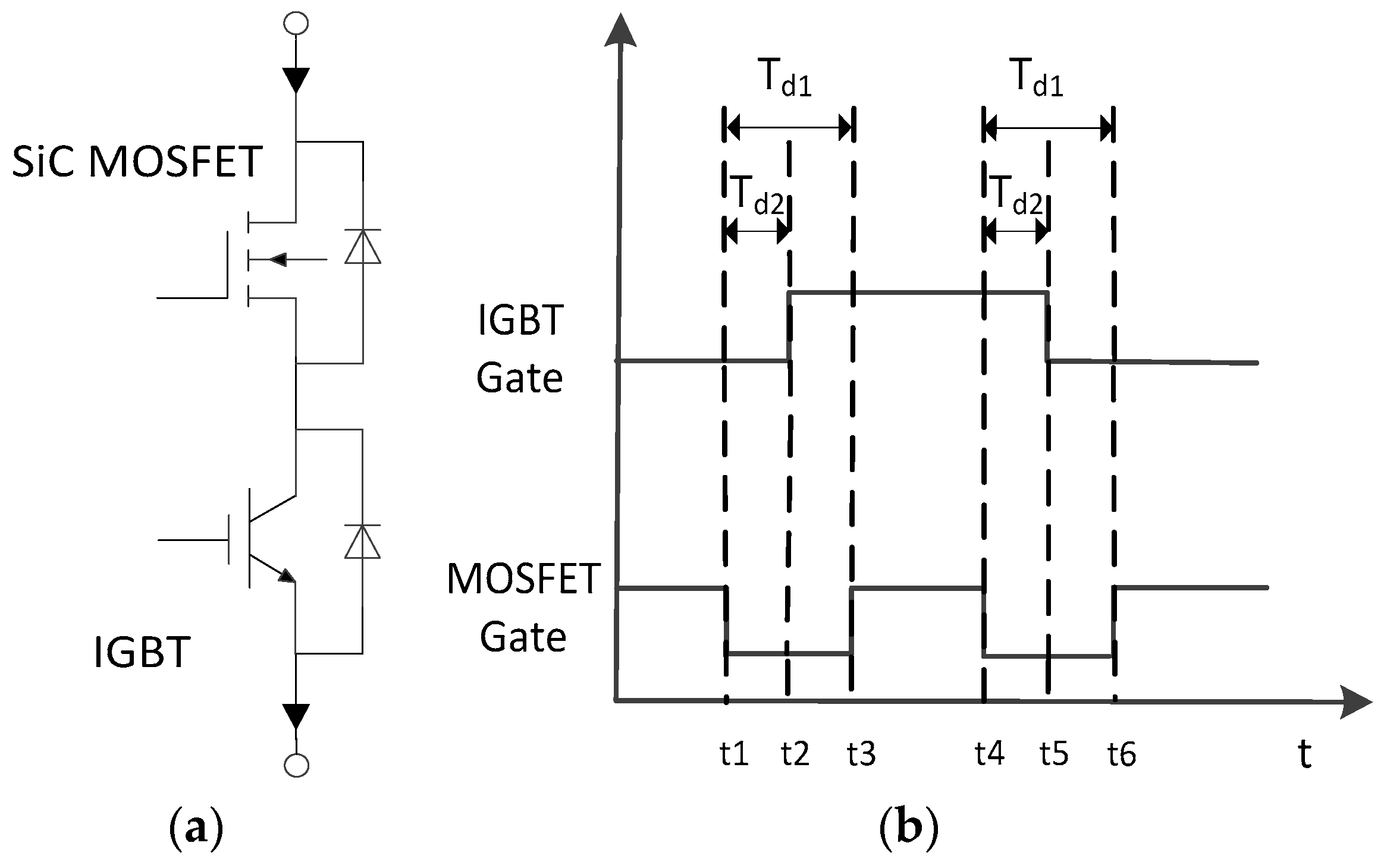

3.1. Proposed Hybrid Switches Configuration and Modulation

3.2. Hybrid Soft Switching Method Analysis in Double Pulse Test

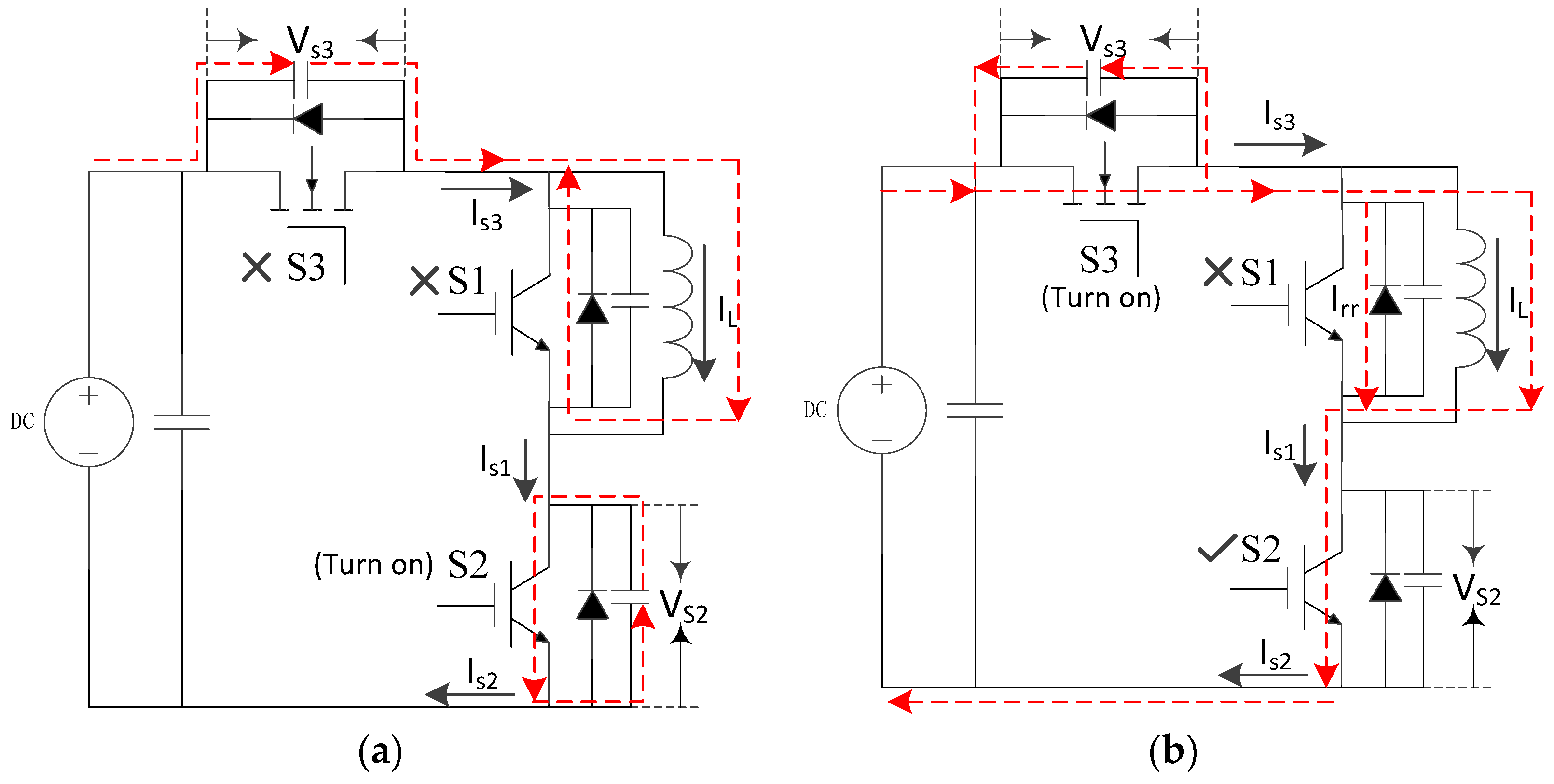

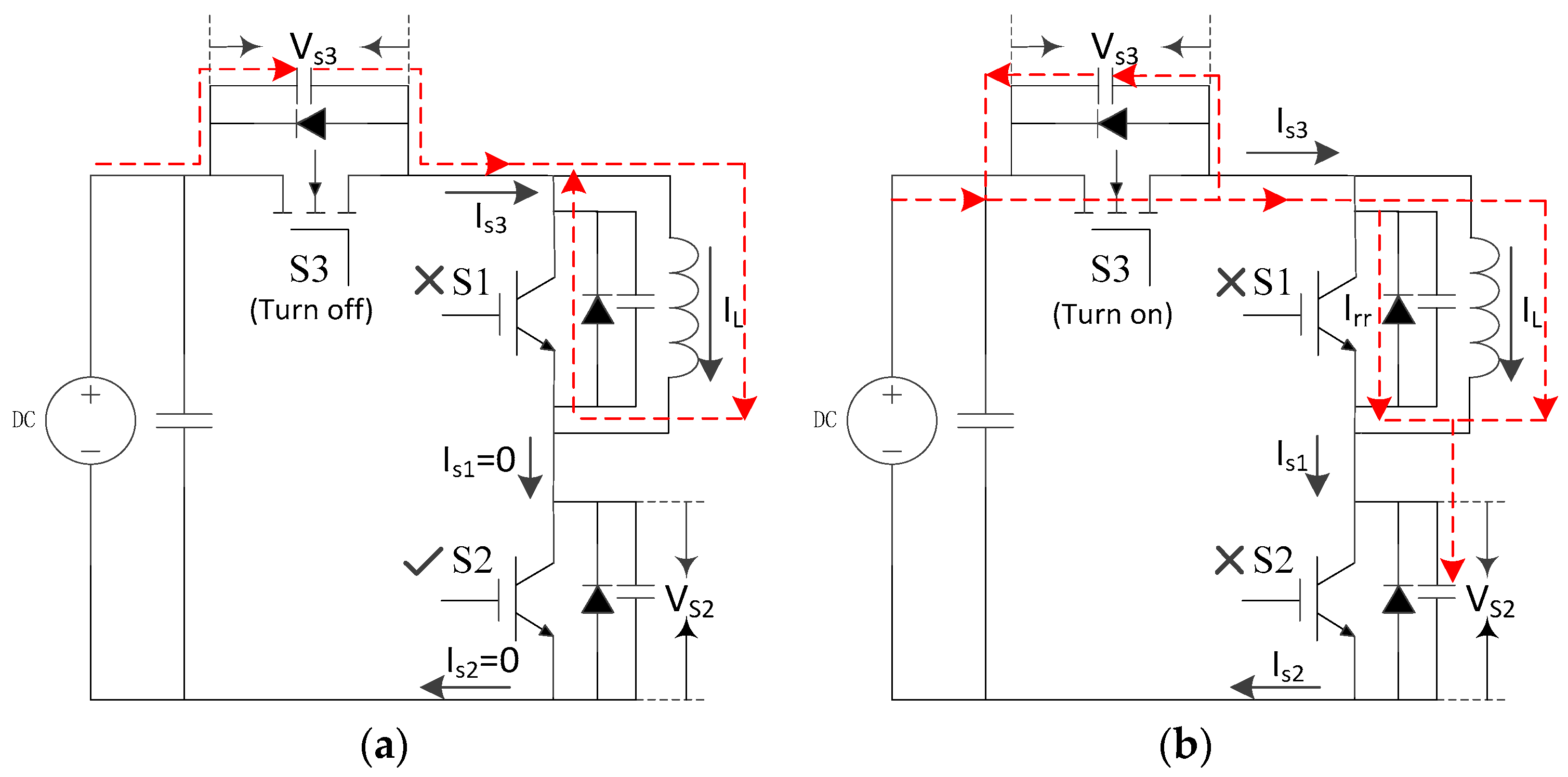

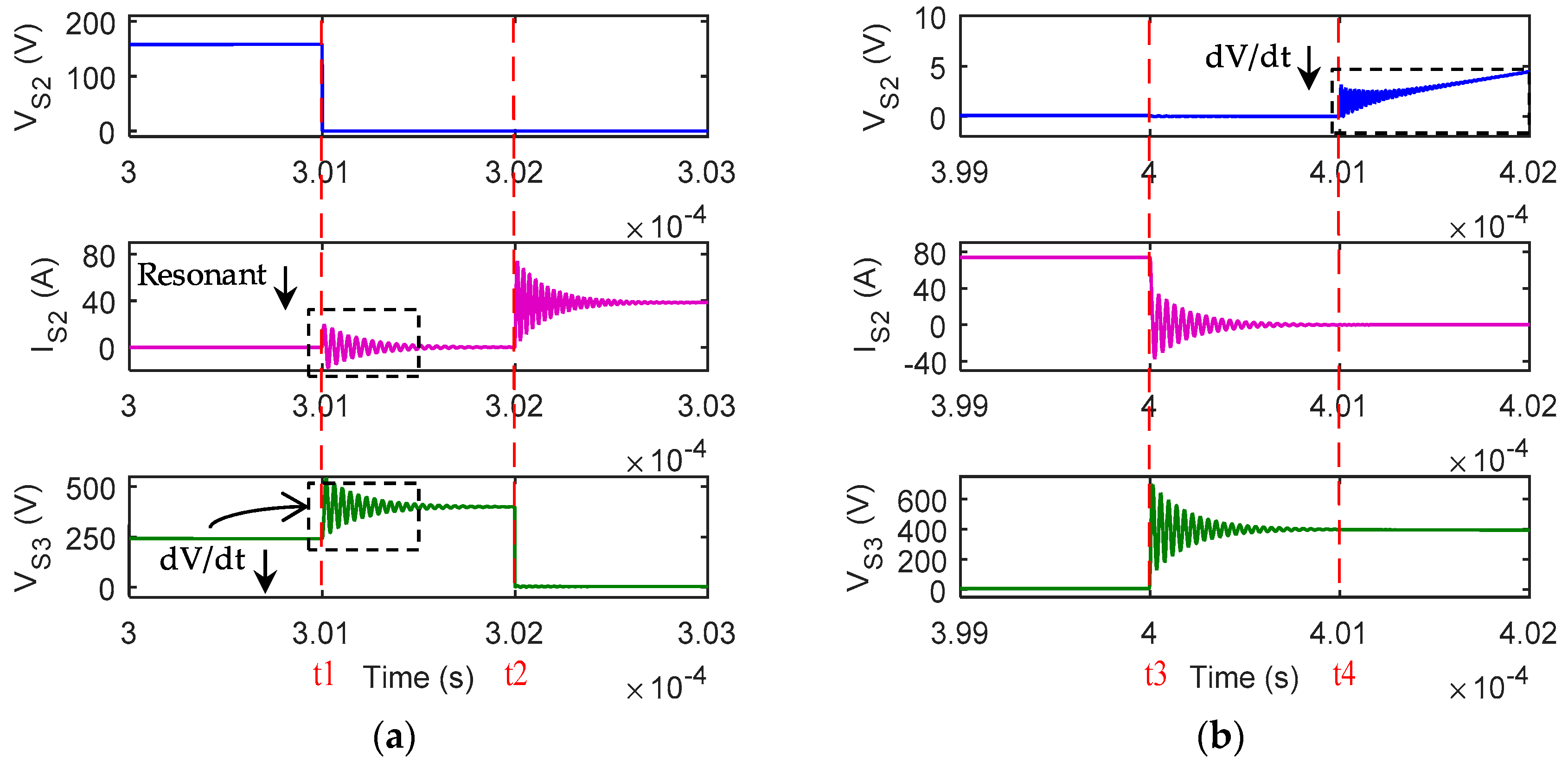

3.2.1. Turn-On Period

3.2.2. Turn-Off Period

3.3. Simulation and Experimental Results

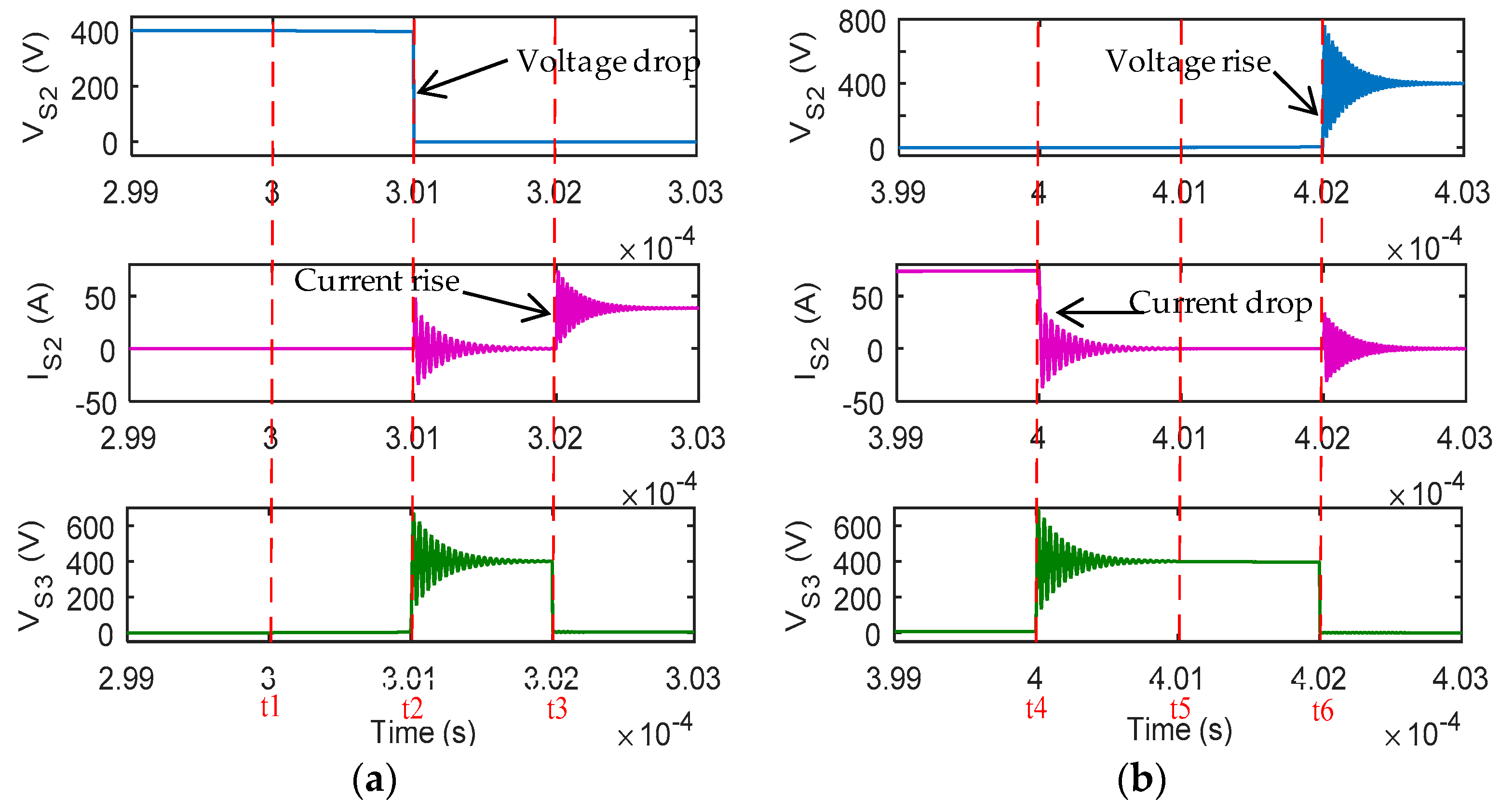

3.3.1. Simulation Results

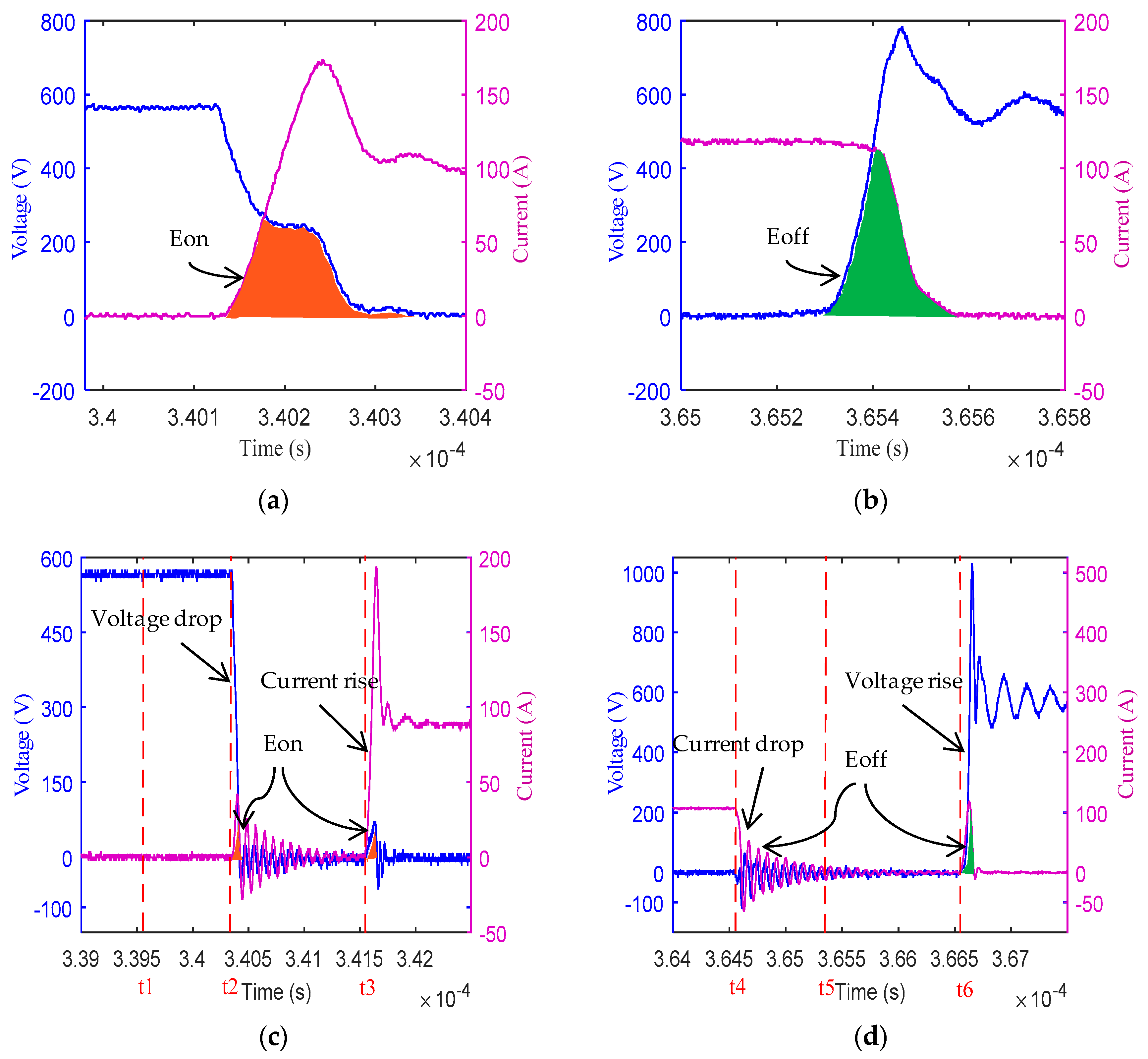

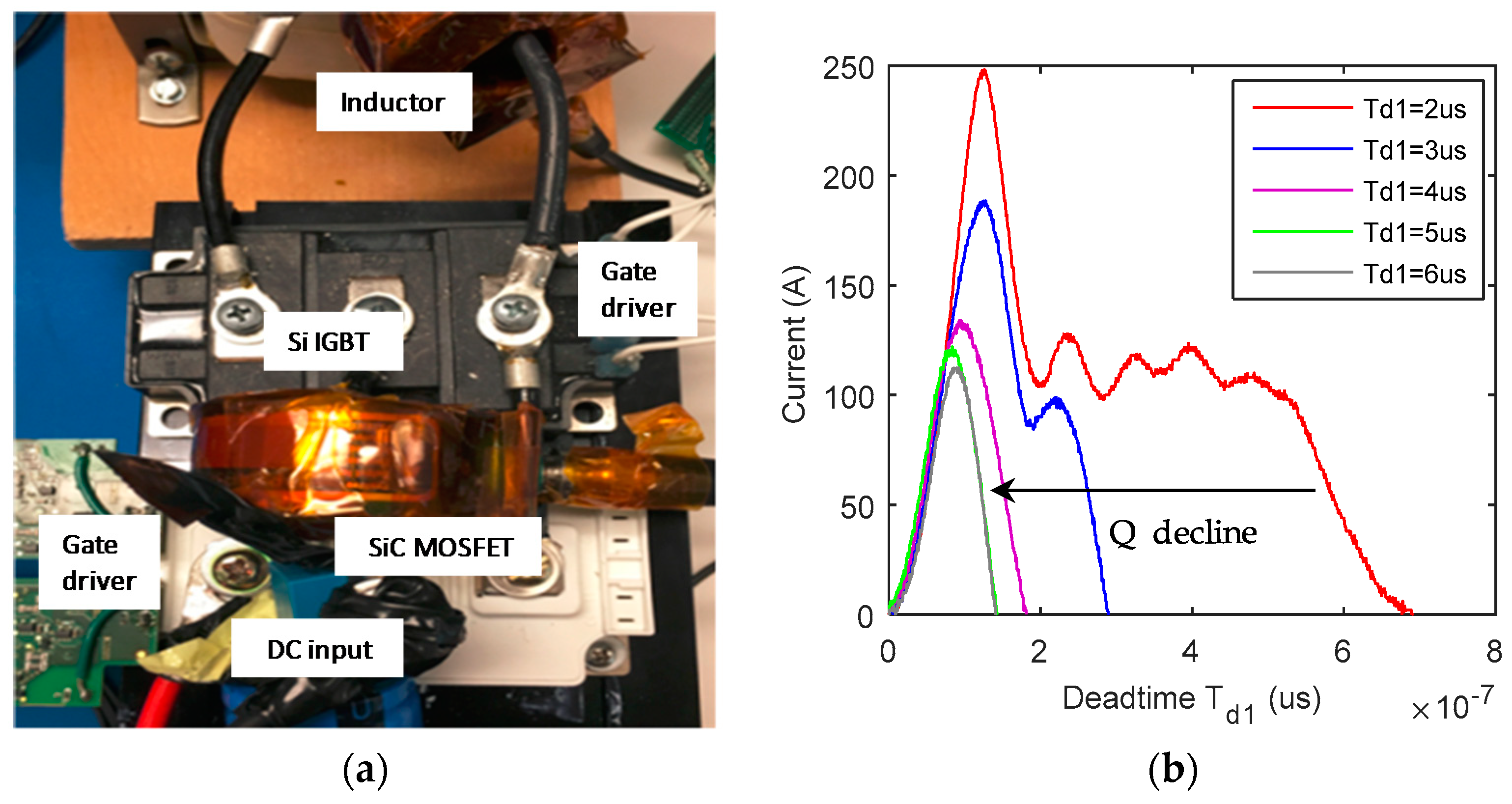

3.3.2. Experimental Results

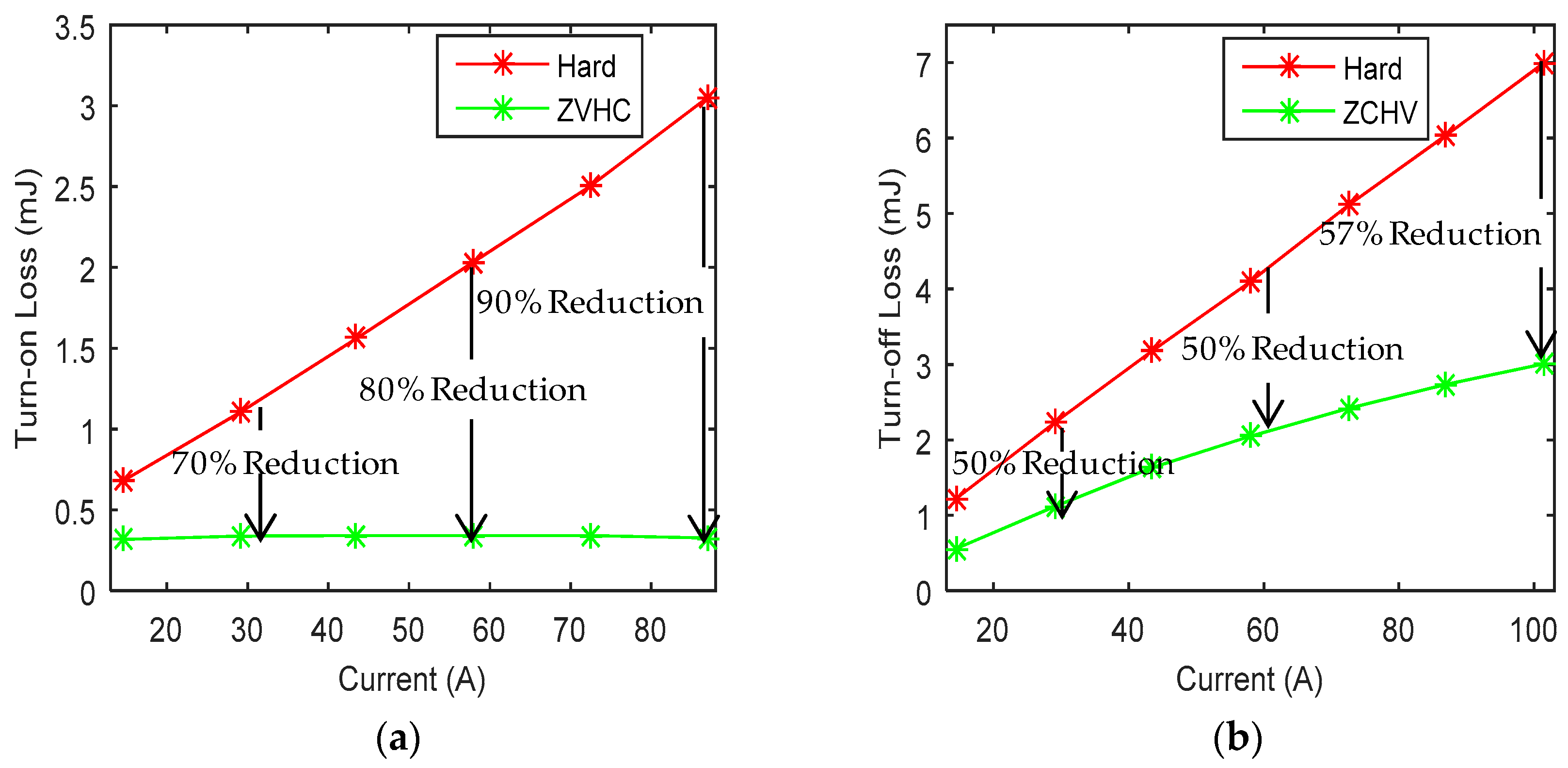

- V-I Switching waveforms

- 2.

- Switching loss comparison

- 3.

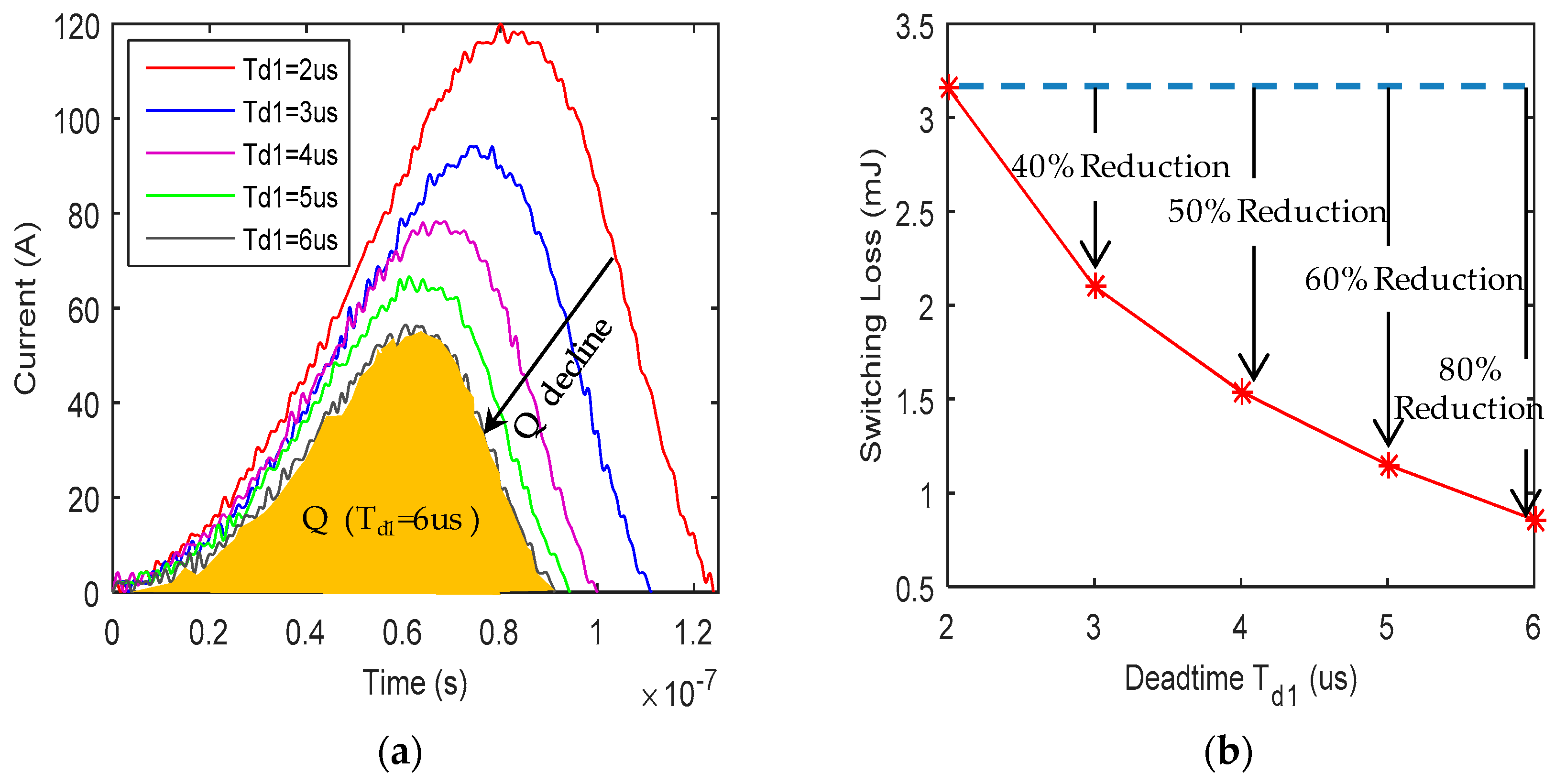

- Parameters design

4. Optimization and Application

4.1. Improved Modulation for the Hybrid Switches

4.1.1. Improved Modulation

4.1.2. Simulation Results

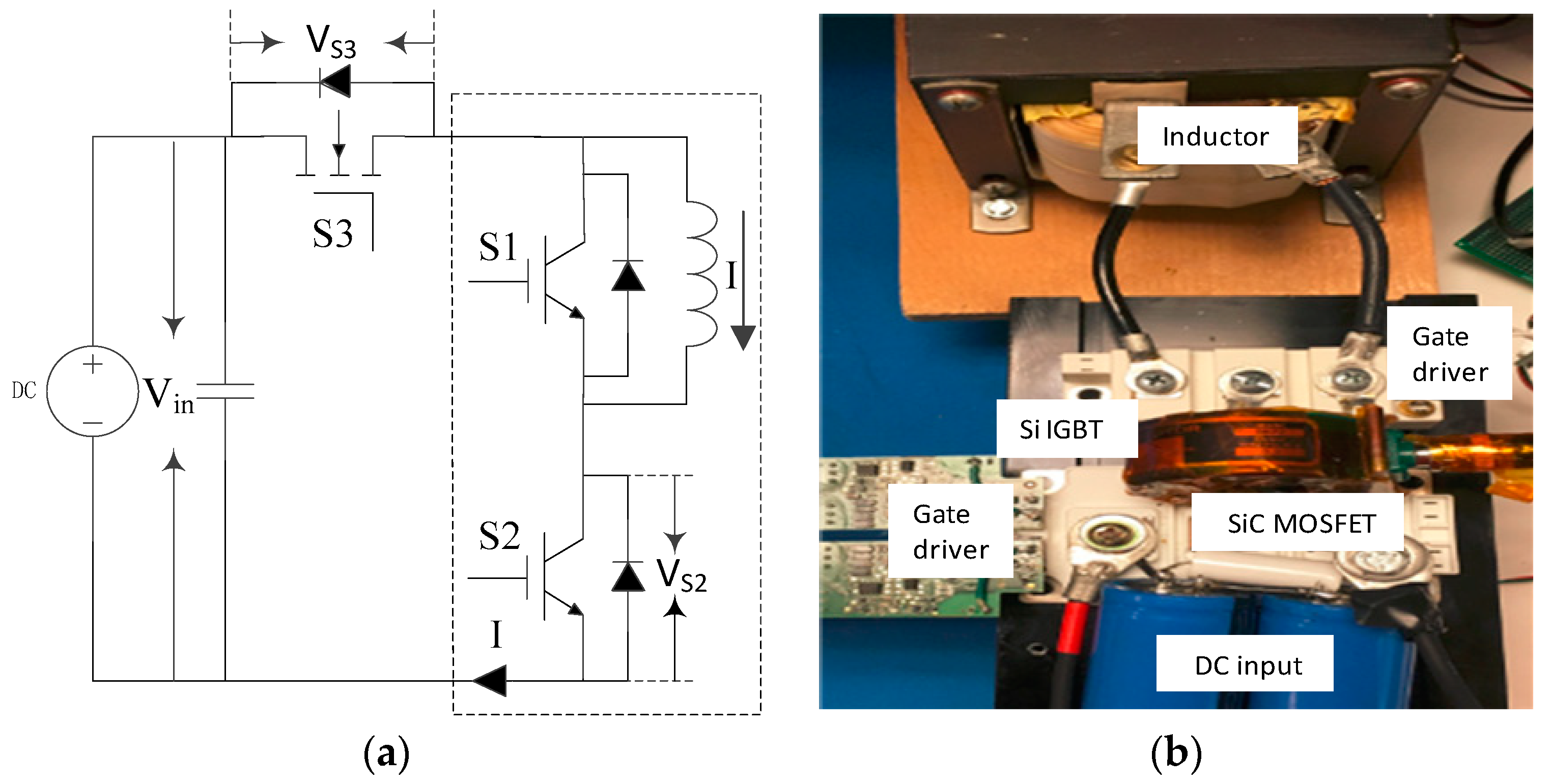

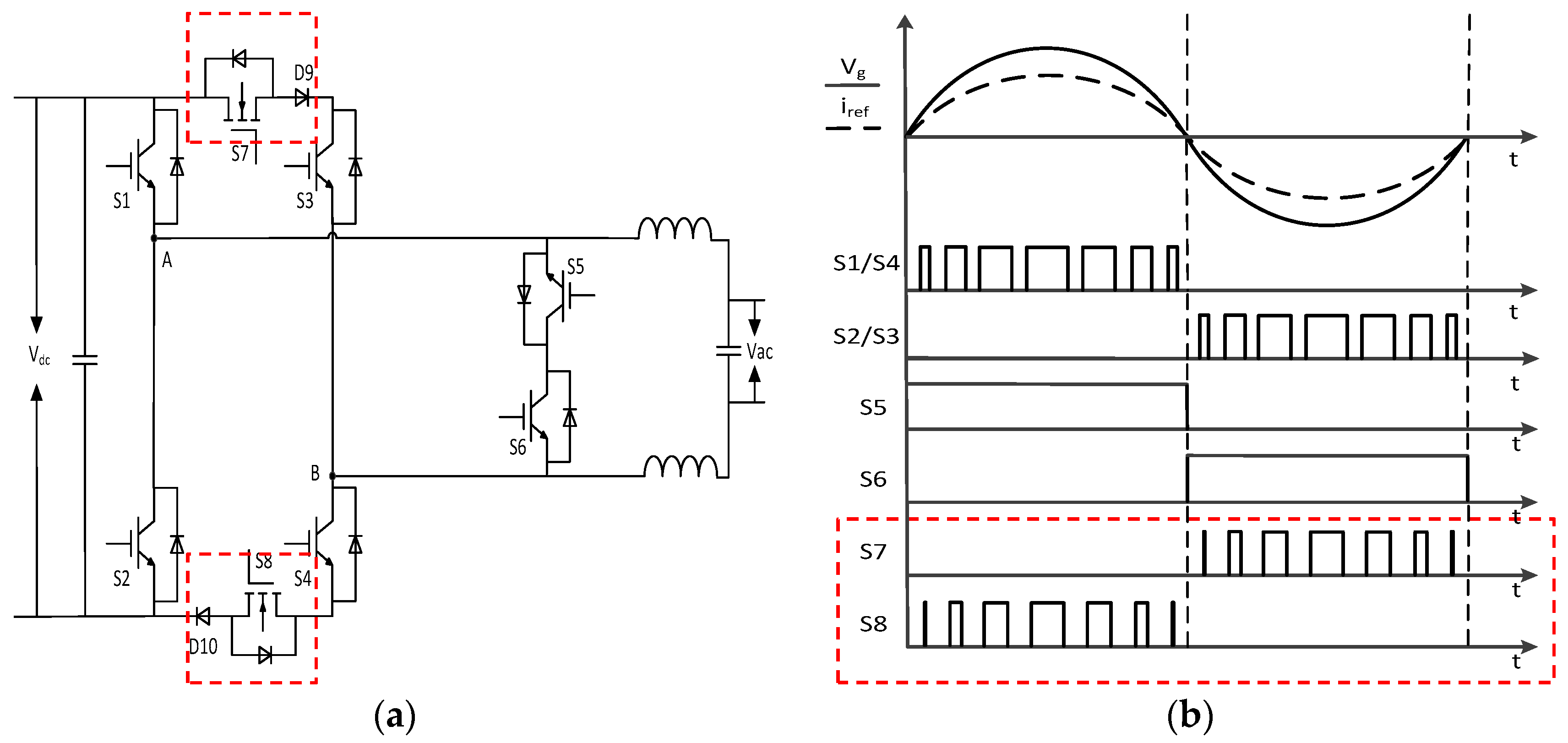

4.2. Hybrid Switching Method Apply to HERIC Inverter

4.2.1. Configuration and Modulation

4.2.2. Simulation Results

5. Conclusions

Author Contributions

Conflicts of Interest

References

- Velander, E.; Kruse, L.; Wiik, T.L.; Wiberg, A.; Colmenares, J.; Nee, H.P. An IGBT Turn-ON Concept Offering Low Losses Under Motor Drive dv/dt Constraints Based on Diode Current Adaption. IEEE Trans. Power Electron. 2017, 99, 1143–1153. [Google Scholar] [CrossRef]

- Chen, K.; Stuart, T.A. A study of IGBT turn-off behavior and switching losses for zero-voltage and zero-current switching. In Proceedings of the Applied Power Electronics Conference and Exposition, Boston, MA, USA, 23–27 February 1992; pp. 411–418. [Google Scholar]

- Hochberg, M.; Sack, M.; Mueller, G. Simple Gate-boosting Circuit for Reduced Switching Losses in Single IGBT Devices. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy, and Energy Management, PCIM-Europe, Nuremberg, Germany, 10–12 May 2016; pp. 1–6. [Google Scholar]

- John, V.; Suh, B.S.; Lipo, T.A. High-performance active gate drive for high power IGBTs. IEEE Trans. Ind. Appl. 1999, 2, 1519–1529. [Google Scholar]

- Sun, Y.; Sun, L.; Esmaeli, A.; Zhao, K. A Novel Three Stage Drive Circuit for IGBT. In Proceedings of the 2006 1ST IEEE Conference on Industrial Electronics and Applications, Singapore, 24–26 May 2006; pp. 1–6. [Google Scholar]

- Sokolov, A.; Mascarella, D.; Joos, G. Variable-speed IGBT gate driver with loss/overshoot balancing for switching loss reduction. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition, Pittsburgh, PA, USA, 14–18 September 2014; pp. 1232–1239. [Google Scholar]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.F.; Blalock, B.J. A di/dt Feedback-Based Active Gate Driver for Smart Switching and Fast Overcurrent Protection of IGBT Modules. IEEE Trans. Power Electron. 2014, 29, 3720–3732. [Google Scholar] [CrossRef]

- Yang, X.; Long, Z.; Wen, Y.; Huang, H.; Palmer, P.R. Investigation of the trade-off between switching losses and EMI generation in Gaussian S-shaping for high-power IGBT switching transients by active voltage control. IET Power Electron. 2016, 9, 1979–1984. [Google Scholar] [CrossRef]

- Caponet, M.C.; Profumo, F.; Tenconi, A. Evaluation of power losses in power electronic converters for industrial applications: Comparison among hard switching, ZVS, and ZVS-ZCS converters. In Proceedings of the IEEEPower Conversion Conference, PCC-Osaka 2002, Osaka, Japan, 2–5 April 2002; pp. 1073–1077. [Google Scholar]

- Gautam, D.S.; Musavi, F.; Eberle, W.; Dunford, W.G. A zero voltage switching full-bridge DC-DC converter with capacitive output filter for a plug-in-hybrid electric vehicle battery charger. IEEE Trans. Appl. Power Electron. 2012, 28, 1381–1386. [Google Scholar]

- Choe, H.J.; Chung, Y.C.; Sung, C.H.; Yun, J.J.; Kang, B. Passive Snubber for Reducing Switching-Power Losses of an IGBT in a DC–DC Boost Converter. IEEE Trans. Power Electron. 2014, 29, 6332–6341. [Google Scholar] [CrossRef]

- Liu, F.; Yan, J.; Ruan, X. Zero-Voltage and Zero-Current-Switching PWM Combined Three-Level DC/DC Converter. IEEE Trans. Ind. Electron. 2010, 57, 1644–1654. [Google Scholar]

- Stein, C.D.; Hey, H.L. A true ZCZVT commutation cell for PWM converters. IEEE Trans. Power Electron. 2000, 15, 185–193. [Google Scholar] [CrossRef]

- Tarzamni, H.; Babaei, E.; Gharehkoushan, A.Z. A Full Soft-Switching ZVZCS Flyback Converter Using an Active Auxiliary Cell. IEEE Trans. Ind. Electron. 2017, 64, 1123–1129. [Google Scholar] [CrossRef]

- Ning, G.; Chen, W.; Shu, L.; Qu, X. A Hybrid ZVZCS Dual-Transformer-Based Full-Bridge Converter Operating in DCM for MVDC Grids. IEEE Trans. Ind. Electron. 2017, 32, 5162–5170. [Google Scholar] [CrossRef]

- Hoffmann, K.F.; Karst, J.P. High-frequency power switch—Improved performance by MOSFETs and IGBTs connected in parallel. In Proceedings of the European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005. [Google Scholar]

- Lai, J.S.; Yu, W.; Sun, P.; Leslie, S.; Arnet, B.; Smith, C.; Cogan, A. A Hybrid-Switch-Based Soft-Switching Inverter for Ultrahigh-Efficiency Traction Motor Drives. IEEE Trans. Ind. Appl. 2012, 50, 1966–1973. [Google Scholar] [CrossRef]

- Sun, P.; Lai, J.S.; Liu, C.; Yu, W. A 55-kW Three-Phase Inverter Based on Hybrid-Switch Soft-Switching Modules for High-Temperature Hybrid Electric Vehicle Drive Application. IEEE Trans. Ind. Appl. 2012, 48, 962–969. [Google Scholar] [CrossRef]

- Ning, P.; Li, L.; Wen, X.; Cao, H. A Hybrid Si IGBT and SiC MOSFET Module Development. CES J. Mag. 2017, 1, 360–366. [Google Scholar]

- Rahimo, M.; Canales, F.; Minamisawa, R.A.; Papadopoulos, C.; Vemulapati, U.; Mihaila, A.; Kicin, S.; Drofenik, U. Characterization of a Silicon IGBT and Silicon Carbide MOSFET Cross-Switch Hybrid. IEEE Trans. Power Electron. 2015, 30, 4638–4642. [Google Scholar] [CrossRef]

- Song, X.; Huang, A.Q.; Lee, M.C.; Peng, C. High voltage Si/SiC hybrid switch: An ideal next step for SiC. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; pp. 289–292. [Google Scholar]

- Minamisawa, R.A.; Vemulapati, U.; Mihaila, A.; Papadopoulos, C.; Rahimo, M. Current Sharing Behavior in Si IGBT and SiC MOSFET Cross-Switch Hybrid. IEEE Electron. Device Lett. 2016, 37, 1178–1180. [Google Scholar] [CrossRef]

- He, J.; Katebi, R.; Weise, N. A Current-Dependent Switching Strategy for Si/SiC Hybrid Switch Based Power Converters. IEEE Trans. Ind. Electron. 2017, 64, 8344–8352. [Google Scholar] [CrossRef]

- Dudrik, J.; Pástor, M.; Lacko, M.; Žatkovič, Z. Zero-Voltage and Zero-Current Switching PWM DC-DC Converter Using Controlled Secondary Rectifier with One Active Switch and Non-Dissipative Turn-Off Snubber. IEEE Trans. Power Electron. 2017, 33, 6012–6023. [Google Scholar] [CrossRef]

- Kai, L.; Zhao, J.C.; Wu, W.J.; Li, M.S.; Ma, L.; Zhang, G. Performance Analysis of Zero Common-Mode Voltage Pulse-Width Modulation Techniques for Three-Level Neutral Point Clamped Inverters. IET Power Electron. 2016, 9, 2654–2664. [Google Scholar] [CrossRef]

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| Input voltage | 400/580 V | Inductor | 1 mH |

| Td1 | 2 us | Td2 | 1/0.7 us |

| Si IGBT Gate Resistor | R = 1 Ω | SiC MOSFET Gate Resistor | Ron = 5 Ω/Roff = 2.5 Ω |

| Si IGBT | SKM100GB12T4 1.2 KV/100 A | SiC MOSFET | CAS120M12BM2 1.2 kV/120 A |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ma, L.; Xu, H.; Huang, A.Q.; Zou, J.; Li, K. IGBT Dynamic Loss Reduction through Device Level Soft Switching. Energies 2018, 11, 1182. https://doi.org/10.3390/en11051182

Ma L, Xu H, Huang AQ, Zou J, Li K. IGBT Dynamic Loss Reduction through Device Level Soft Switching. Energies. 2018; 11(5):1182. https://doi.org/10.3390/en11051182

Chicago/Turabian StyleMa, Lan, Hongbing Xu, Alex Q. Huang, Jianxiao Zou, and Kai Li. 2018. "IGBT Dynamic Loss Reduction through Device Level Soft Switching" Energies 11, no. 5: 1182. https://doi.org/10.3390/en11051182