Article

# **Coordination Control Method Suitable for Practical Engineering Applications for Distributed Power Flow Controller (DPFC)**

# Mengmeng Xiao and Shaorong Wang \*

School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan 430074, China; xiaomengmeng@hust.edu.cn

\* Correspondence: wsrwy96@vip.sina.com

Received: 27 October 2018; Accepted: 30 November 2018; Published: 4 December 2018

**Abstract:** To control multiple series units of distributed power flow controller (DPFC), a hierarchical control method is proposed. This coordination control system consists of a coordination controller and multiple series unit controllers. According to the demand of power flow ordered by a dispatch center, the corresponding series-compensated voltage is calculated by a high-level controller and transferred to each series unit controller. Comparing the targeted compensated voltage with actual injected voltage, the modulation signal of the converter will be modified to change the power flow accurately. The DPFC system model is built in Power Systems Computer Aided Design/ Electromagnetic Transients including DC (PSCAD/EMTDC). The simulation result indicates that the proposed hierarchical control method is effective and can be considered as an option for practical engineering applications in the future.

**Keywords:** AC transmission; distributed power flow controller; hierarchical coordination control; series compensated voltage

# 1. Introduction

The mechanically controlled AC power transmission systems, including the use of high-power electronics, advanced control centers, and communication links, were proposed in 1986 by N.G. Hingorani from American Electric Power Research Institute (EPRI) [1–3]. For a simple flexible AC transmission system (FACTS) parallel device or a simple FACTS series device, only the reactive power can be exchanged if the energy storage unit is not disposed on the DC capacitor side within the FACTS device. That is, its effect is equivalent to a tunable inductor or an adjustable capacitor. As a consequence, it is limited and not flexible enough for regulating the power flow of the transmission line.

The conception of a unified power-flow controller (UPFC) was proposed in 1991 by Dr. L. Gyugyi [4,5] and has been extensively studied to date [6–11]. The UPFC can be regarded as the combination of shunt and series FACTS linked by a common DC. Generally, the shunt device is a static synchronous compensator (STATCOM), while the series device is an example of a static synchronous series compensator (SSSC). Bidirectional active power can flow between the parallel and series units via the DC-bus capacitor to realize 'four quadric' power-flow regulation. Additionally, the active power flow and reactive power flow of the transmission line can be controlled independently, which matches its "universal" mind for control. However, the parallel and series units of UPFC are installed centrally; as a consequence, many land resources are required for the installation. The series side is integrated into one unit, which causes a large fold line change in the voltage distribution of the transmission line. Besides this, the requirement for the insulation is high due to the direct electrical connection of the parallel and series units. The aforementioned factors have led research workers to rethink UPFC from the aspects of project cost, ease of operation and maintenance.

Prof. Deepak Divan proposes the concept of distributed FACTS (D-FACTS) [12–14]. As a member of the DFACTS family, the distributed static series compensator (DSSC) has been studied widely [15–19]. Multiple DSSCs are sparsely hung onto the transmission line through a single-turn transformer (STT). As a single-phase inverter with small capacity, the DSSC can be designed into a simple structured device with low insulation cost and easy installation. The control principle of DSSC is similar to that of SSSC, both of which control the power flow effectively by changing the line reactance flexibly.

The idea of a distributed power flow controller (DPFC) was proposed in 2007, as a new component within the FACTS family by Zhihui Yuan from Delft University of Technology [20–22]. DPFC is derived from UPFC. DPFC can be considered as a UPFC without a common DC link between the shunt and series converters. A parallel unit of the DPFC is installed in a central area while the series units of DPFC employ multiple distributed series units similar to DSSC. In UPFC, the active power support of the series unit is transported by a common DC link. In DPFC, however, the DC power channel is removed and replaced by the transmission power line. Due to the lower impedance characteristic of the third harmonic compared with higher-frequency harmonics, the third harmonic active power is chosen as an energy conversion medium. The parallel unit absorbs the base-frequency active power then is injected to the transmission line and flows along the line. The distributed series units control the exchange between the 3rd harmonic active power and base-frequency active power. Simultaneously, the responding voltages will be generated and injected into the transmission line. In our research, we only care about the base frequency voltage for base frequency power flow control. Thus, later in this paper, the series-compensated voltage indicates the base-frequency series-compensated voltage.

There are different research results about DPFC from different aspects of application. In [23–25], DPFC was used to improve power quality problems during voltage sag and swell conditions. In [26], taking the constraints of DPFC, an optimal scheduling model is established to realize wind power spillage minimization. However, the generation of the reference base-frequency voltage is not clear. In [27], by introducing an MMC (modular multilevel converter) at the shunt side of the DPFC, a new topology of DPFC is proposed. References [28,29] proposed a specific power flow control method: taking the terminal voltage of the transmission line as a reference, this technique requires high-speed communication links to transfer the real-time waveform of the terminal voltage to multiple series unit controllers. From the point view of engineering applications, this power flow control method is not practical and needs to be improved.

To address the above issue, this paper proposes a hierarchical coordination control method for DPFC series units. Taking advantage of the fact that the DPFC series unit is able to collect the real-time phase of the transmission line current, the phase difference between the fundamental frequency line current and the terminal voltage of the transmission line can be reflected by a sine wave generator within the DPFC series unit. Therefore, the waveform of the real-time phase of the terminal voltage can be reproduced correctly during a control period. In this way, a high-speed communication link is not required. In addition, a wide area measurement system (WAMS) is introduced to transfer the receiving-end voltage of the transmission line back to the upper-level controller.

The rest of paper is structured as follows. The basic principle of DPFC is presented in Section 2. In Section 3, the coordination control system is discussed. The computation of the reference series-compensated voltage is introduced in detail, and the lower-level series-unit control scheme is depicted. In Section 4, simulation results in PSCAD/EMTDC are used to demonstrate the effectiveness of the proposed coordination control method, and these are compared with the state-of-the-art methods for DPFC power flow control. In Section 5, conclusions and future work are presented.

#### 2. Basic Principle of the DPFC

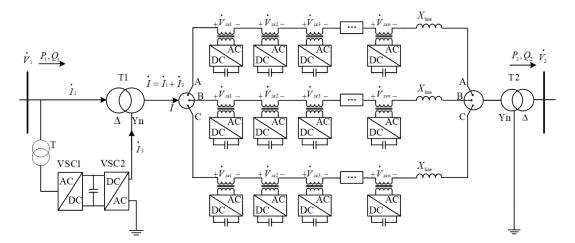

A parallel FACTS device and many distributed series FACTS devices constitute a DPFC. The structure of a DPFC is shown in Figure 1. In the following, the parallel FACTS device is called a parallel

unit while the series FACTS devices are called series units. The parallel unit is located at the sending end of the transmission line, and series units are distributed along the transmission line.

Figure 1. Structure of a distributed power flow controller (DPFC).

As shown in Figure 1, T1 and T2 are delta-wye grounded transformers The delta side of the transformer is blocked for the third harmonic current while the wye grounded side is allowed for flowing 3rd harmonic current; thus, the energy channel of third harmonic active power is formed, which makes the active power exchange between the parallel unit and series units of the DPFC possible.

The parallel unit of the DPFC is composed of two back-to-back voltage source converters (VSCs). VSC1 is a three-phase converter which is responsible for maintaining the bus voltage and keeping the DC capacitor voltage stable. VSC2 is a single-phase converter, which is used to generate a constant third harmonic current. Thus, the parallel unit of the DPFC plays the role of absorbing the active power from the bus, and then converting it to the third harmonic active power. The third harmonic active power is injected into the transmission line and taken in by the DPFC series units as active power support. After that, the base-frequency active power is generated by the power exchange control in the series units.

In Figure 1,  $V_1$  and  $V_2$  represent the voltage at the sending-end and receiving-end of the transmission line, respectively.  $I_3$  is the equivalent third harmonic current.  $P_1$ ,  $Q_1$ ,  $P_2$ , and  $Q_2$  indicate the power flow at the sending-end and receiving-end of the transmission line, respectively. Each DPFC series unit generates a compensated voltage  $V_{sei}$  (i = 1, 2, 3, ..., n), and all the  $V_{sei}$  values form a final compensated voltage  $V_{sei}$ .  $X_{line}$  is the equivalent impedance of the transmission line.

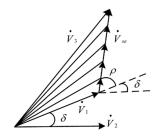

By injecting the compensated voltage  $V_{se}$ , the active and reactive power of the transmission line can be controlled. The equivalent phasor diagram of the DPFC is expressed in Figure 2.

Figure 2. The working principle of the DPFC.

In Figure 2,  $V_{se}$  represents the integrated compensated voltage,  $\delta$  represents the phase angle where  $V_1$  surpasses  $V_2$ ,  $\rho$  stands for the phase angle where  $V_{se}$  surpasses  $V_1$ , and  $(\delta + \rho)$  indicates the

phase angle where  $V_{se}$  surpasses  $V_2$ .  $X_{\Sigma} = X_{T1} + X_{line} + X_{T2}$  denotes the total impedance of the AC transmission power system, where  $X_{T1}$  and  $X_{T2}$  represent the impedance of the transformer T1 and T2, respectively. Thus, the natural power flow of the transmission line is expressed as

$$P_{20} = \frac{V_1 V_2 \sin \delta}{X_{\Sigma}} \tag{1}$$

$$Q_{20} = \frac{V_1 V_2 \cos \delta - {V_2}^2}{X_{\Sigma}}$$

(2)

With DPFC series units, the power flow becomes

$$P_2 = \operatorname{Re}\begin{bmatrix} \bullet & *\\ V_2 I_1 \end{bmatrix} = \frac{V_1 V_2 \sin \delta + V_{\operatorname{se}} \times V_2 \sin(\delta + \rho)}{X_{\Sigma}}$$

(3)

$$Q_2 = \operatorname{Im}\begin{bmatrix} \bullet & *\\ V_2 I_1 \end{bmatrix} = \frac{V_1 V_2 \cos \delta + V_{\text{se}} \times V_2 \sin(\delta + \rho) - V_2^2}{X_{\Sigma}}$$

(4)

$V_1$  and  $V_2$  can be regarded as constant during a certain period of time in the actual power system operation, and so the increment of active and reactive power flow at the receiving-end can be written as follows:

$$\Delta P_2 = \frac{V_{\rm se} \times V_2 \sin(\delta + \rho)}{X_{\Sigma}} \tag{5}$$

$$\Delta Q_2 = \frac{V_{\rm se} \times V_2 \cos(\delta + \rho)}{X_{\Sigma}} \tag{6}$$

Based on the above equations, it is obvious that the power flow of the transmission line can be controlled efficiently by changing the magnitude value and phase angle of the series-compensated voltage slightly and flexibly.

## 3. Coordination Control System of a DPFC

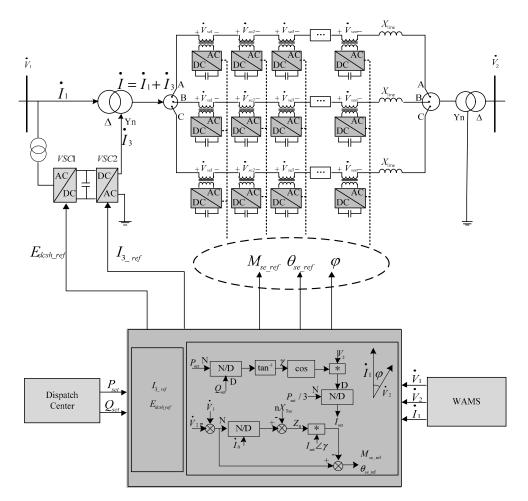

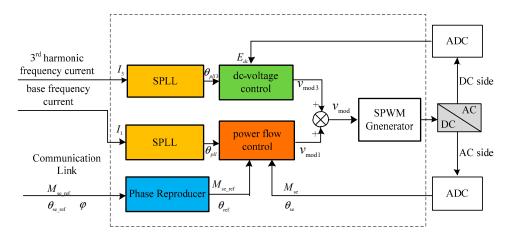

The proposed coordination control system of a DPFC consists of an upper-level controller, a parallel unit controller and multiple series unit controllers. The schematic diagram of this control system is depicted in Figure 3.

In Figure 3,  $E_{dcsh\_ref}$  is the reference value of the DC capacitor voltage in the parallel unit while  $I_{3\_ref}$  indicates the referenced third harmonic frequency. The control method for the parallel unit can be found in [20–22]; thus, the control scheme of the coordination control method for the series unit is mainly discussed in this research work.

Figure 3. The structure of the coordination control system of a DPFC.

# 3.1. The Computation of Reference Compensated Voltage

According to the demand of power flow  $P_{\text{set}}$  and  $Q_{\text{set}}$  ordered by the dispatch center, and the states of transmission line  $V_1$ ,  $V_2$  and  $I_1$  attained by WAMS, the corresponding series-compensated voltage  $V_{\text{se_ref}}$  is calculated by an upper-level controller. The calculation process is as follows:

• Setting the number of DPFC series units to be n, the total base-frequency impedance between the sending-end and receiving-end of the power transmission system is *Z*<sub>0</sub>, the short circuit reactance of each series unit is *X*<sub>Tse</sub>, and the initial current phasor of transmission line is

$$\mathbf{I}_{0} = \frac{\mathbf{V}_{1} - \mathbf{V}_{2}}{Z_{0} + nX_{\text{Tse}}}$$

(7)

• Corresponding to the target power flow,  $I_{set}$  and  $\alpha$  represent the RMS value of  $I_1$  and phase angle that  $I_1$  leads  $V_2$ , respectively.

$$P_{\text{set}} = \operatorname{Re}\left[\overset{\bullet}{V_2} \overset{\bullet}{I_{\text{set}}}^*\right] = V_2 I_{\text{set}} \cos \alpha \tag{8}$$

$$Q_{set} = \operatorname{Im}\left[\frac{\bullet}{V_2}I_{set}^{\bullet}\right] = V_2I_{set}\sin\alpha$$

(9)

where  $I_{set}$  denotes the conjugate complex of the targeted current line  $I_{set}$ . Supposing that the voltage phasors at the sending-end and receiving-end of the transmission system are unchanged during one control cycle, then we have

$$I_{\text{set}} = \frac{P_{\text{set}}}{V_2 \cos \alpha} \tag{10}$$

$$\alpha = \arctan(Q_{\text{set}}/P_{\text{set}}) \tag{11}$$

• The corresponding series-compensated voltage generated by each DPFC series unit is  $V_{se\_ref} = M_{se\_ref} \angle \theta_{se\_ref}$ , where  $M_{se\_ref}$  is the RMS value of the  $V_{se\_ref}$  and  $\theta_{se\_ref}$  is the phase angle that  $V_{se\_ref}$  surpasses the voltage phasor  $V_2$ . From the view of the total system, the effect of  $V_{se\_ref}$  can be regarded as an equivalent series impedance  $Z_{set}$  injected by each series unit. Then, another expression of the transmission line is

$$\mathbf{I}_{\text{set}} = \frac{\mathbf{V}_1 - \mathbf{V}_2}{Z_0 + nZ_{\text{set}}} \tag{12}$$

According to the obvious assumption and analysis, the series-compensated voltage is

- At the initial stable state  $t = t_0$ , the phase angle that  $I_1$  surpasses  $V_2$  is  $\varphi$ , and all these measurements are saved in the upper-level controller.

- The RMS value and phase angle of the corresponding series-compensated voltage M<sub>se\_ref</sub>, θ<sub>se\_ref</sub> and the phase angle φ are transferred to each series unit via a power line carrier communication link.

# 3.2. The Control Scheme of DPFC Series Units

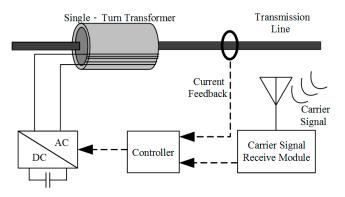

The structure of the DPFC series unit is shown in Figure 4.

Figure 4. The structure of the DPFC series unit.

The series unit of the DPFC consists of a single-turn transformer (STT), a single-phase inverter, an associated controller, and a built-in communication model. The SST uses the transmission line as the secondary winding, inserting compensated voltage into the power line. Each unit of DPFC is controlled by power line carrier communication.

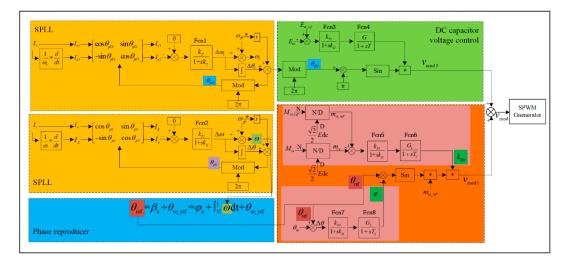

The DPFC series unit has the task of maintaining the DC capacitor voltage and responding to the reference signal effectively. The control scheme for the DPFC series unit including the single-phase locked loop (SPLL), DC capacitor voltage control and power flow control loop is depicted in Figure 5.

**Figure 5.** The working principle of the DPFC series unit controller. Single-phase locked loop (SPLL): single-phase locked loop. ADC: analog-to-digital converter. SPWM: sinusoidal pulse-width modulation (PWM).

The reference value of the compensated voltage  $M_{\text{se_ref}}$  and  $\theta_{\text{se_ref}}$  are transferred to the DPFC series unit via power line carrier (PLC) communication link. In a phase reproducer, the real-time phase of the reference voltage  $\theta_{\text{ref}}$  will be generated, leveraging the advantage that the real-time phase of the transmission line base-frequency current can be captured by series units. The actual value of the compensated voltages  $M_{\text{se}}$  and  $\theta_{\text{se}}$  are acquired and converted to a digital signal by the analog-to-digital converter (ADC) unit. By comparing the real-time reference values  $M_{\text{se_ref}}$  and  $\theta_{\text{ref}}$  with actual values  $M_{\text{se}}$  and  $\theta_{\text{se}}$ , the proportional-integral (PI) controller within the power flow control loop will generate a compensated phase and a magnitude correction factor to modify the modulation signal  $v_{\text{mod1}}$  of the base-frequency compensated voltage.

Based on the comparison of the actual value with the reference value of the DC capacitor voltage in the DPFC series unit, the DC-voltage control loop will generate the modulation signal  $v_{mod3}$  to maintain the DC capacitor voltage. Consequently, the output of the AC/DC converter equals the mutual control effects of  $v_{mod1}$  and  $v_{mod3}$ .

## 3.2.1. The Single-Phase Locked Loop (SPLL)

The adopted phase locked loop method is based on the literature [30]. However, the literature [30] directly integrates the angular frequency to obtain the phase-locked output, which easily leads to the saturation of the integral link. Therefore, the above method is improved in this paper, which can effectively prevent the integral saturation phenomenon.

The single-phase locked loop here is designed to track the frequency and phase of the base-frequency current  $I_1$  and third harmonic current  $I_3$ . The measured value of the line current phase is obtained by current transformer (CT). As shown in Figure 6, the third harmonic current  $I_3$  and base-frequency current  $I_1$  are separated by the filter, and then their phases are locked by the single-phase locked loop (SPLL) in the DPFC series unit. The outputs of SPLL for the base-frequency current are expressed as follows:

$$\theta_{\rm pll} = \omega t + \theta_{\rm pll0} \tag{14}$$

$$\theta_{\text{pll3}} = \omega_3 t + \theta_{\text{pll30}} \tag{15}$$

Figure 6. The scheme of the DPFC series unit controller.

#### 3.2.2. The Reproduced Real-Time Phase for Reference Series-Compensated Voltage

9

The time when the program of the phase locked loop of the line current is started is marked as t = 0. Recording a certain zero-crossing point of the fundamental frequency current phasor of the transmission line as  $t_1$ , at this time, the phase of the line current is measured as  $\varphi_i$ , and then the phase of  $\hat{V}_2$  at time  $t = t_1$  is

$$\varphi_u = \varphi_i - \varphi \tag{16}$$

The real-time phase of  $V_2$  can be attained by

$$\beta_u = \varphi_u + \int_{t_1}^t \omega dt \tag{17}$$

Then, the real-time phase of the reference series-compensated voltage  $V_{se ref}$  can be denoted as

$$\theta_{\rm ref} = \beta_u + \theta_{\rm se\_ref} = \varphi_u + \int_{t_1}^t \omega dt + \theta_{\rm se\_ref}$$

(18)

Considering that DPFC series units have the advantage of capturing the real-time phase of the transmission line current, the waveform of the real-time phase of the terminal voltage can be reproduced during a control period, which is very practical for engineering applications.

## 3.2.3. The DC Capacitor Voltage Control

The DC capacitor voltage control loop is shown in Figure 6. By comparing the actual DC capacitor voltage  $E_{dc}$  with the reference DC capacitor voltage  $E_{dcsh_ref}$ , the PI controller will generate the magnitude value of the modulation signal  $v_{mod3}$ . To simulate the dynamic characteristics of the converter, a first-order inertial loop is introduced for DC capacitor voltage control. To avoid causing extra voltage changes or power loss, the series unit is required to exchange only the active power of the third harmonic with the transmission line. Hence, the modulation signal  $v_{mod3}$  should be the same or inverse to the phase of the third harmonic current of the transmission line.

Thus, the DC-voltage control loop generates the modulation signal  $v_{mod3}$  for the third harmonic frequency voltage. The third harmonic active power generated by the parallel unit can change according to the demand for active power of the DC side to maintain the voltage of the DC capacitor in series units.

## 3.2.4. The Power Flow Control

SPWM (sinusoidal PWM) control is adopted by the series unit. The relationship between the RMS value (root-mean-square) of the inverter output voltage and the DC capacitor voltage is

$$V_{\rm se} = \frac{\sqrt{2}}{2} k_{\rm se} m_{\rm se} E_{\rm dc} \tag{19}$$

where  $k_{se}$  represents the ratio of STT,  $m_{se}$  is the fundamental frequency voltage modulation ratio, and  $E_{dc}$  is the DC capacitor voltage.

In fact, the phase of the control reference voltage signal of the series unit port will be shifted after passing through the inductor-capacitor (LC) filter. In addition, due to the active power loss, the amplitude of the series fundamental frequency voltage actually injected into the transmission line is smaller than the reference value. This will lead to deviations in the flow control. Therefore, it is necessary to correct the fundamental frequency compensation voltage modulation signal by taking the measurement of the mean value correction and the phase compensation.

The target and actual value of the compensated voltage are sent to the comparison module after being conversed and processed in the ADC unit. Then, the PI controller generates the compensated phase and magnitude correction factor to modify the modulation signal  $v_{mod1}$ . The modulating signal for compensated base-frequency voltage is modified as follows:

$$v_{\text{mod1}} = k_{Me} m_{\text{se_ref}} \sin(\theta_{\text{ref}} - e)$$

<sup>(20)</sup>

where  $k_{Me}$  is the magnitude modified factor and *e* represents the correction for the phase.  $m_{se\_ref}$  denotes the modulation ratio of the fundamental frequency voltage.

According to the above analysis, integrating the four control modules together, the detailed scheme for the DPFC series unit can be depicted in Figure 6, where  $\omega_{ff}$  represents the rated angular frequency for fundamental-frequency components, and  $\omega_{ff3}$  represents the rated angular frequency for third harmonic components. Fcn1, Fcn2, Fcn3, Fcn5and Fcn7 are PI controllers. Fcn4, Fcn6 and Fcn8 are first-order inertia blocks. *G*, *G*<sub>1</sub> and *G*<sub>2</sub> represent the gain of the first-order inertia blocks.

### 4. The Simulation and Analysis of the DPFC Coordination Control System

#### 4.1. Simulation of the DPFC Control System

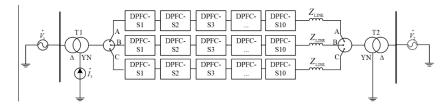

The model of the transmission system including DPFCs is shown in Figure 7. It is built by the software tool PSCAD/EMTDC 4.2.1. The parallel unit is equivalent to the third harmonic current source and the series units of DPFC are built as detailed models.

Figure 7. The simulation model of the DPFC.

4.1.1. Test Case 1

The device parameters of the DPFC are listed in Table 1.

| Items                                                          |                   | Parameter                                                               |  |

|----------------------------------------------------------------|-------------------|-------------------------------------------------------------------------|--|

| System fundamental frequency                                   |                   | 50 Hz                                                                   |  |

| Magnitude of third harmonic current $\overset{ullet}{I_3}$     |                   | 6 A                                                                     |  |

| Number of series units                                         |                   | 10                                                                      |  |

| Magnitude of $\overset{ullet}{V}_1$ and $\overset{ullet}{V}_2$ |                   | 380 V                                                                   |  |

| Phase angle of voltage at sending-end $\boldsymbol{\delta}$    |                   | 8.92°                                                                   |  |

| Phase angle of voltage at receiving-end                        |                   | 0°                                                                      |  |

| Transformer T1                                                 |                   | 380 V/380 V, 1 kVA, 0.1 p.u, Δ-YN                                       |  |

| Transformer T2                                                 |                   | 380 V/380 V, 1 kVA, 0.1 p.u, YN-4                                       |  |

| Single-turn transformer of series unit                         |                   | 20 V/100 V, 0.5 kVA, 0.1 p.u                                            |  |

| Reference value of DC capacitor voltage                        |                   | 20 V                                                                    |  |

| Value of DC capacitor of VSC in series unit                    |                   | 2200 μF                                                                 |  |

| LC filter of VSC in series unit                                |                   | 1.33 mH, 100 μF                                                         |  |

| Switch frequency of Insulated-gate bipolar transistor (IGBT)   |                   | 2100 Hz                                                                 |  |

| Z <sub>line</sub>                                              |                   | $R_{\text{line}} = 0.279 \ \Omega, L_{\text{line}} = 0.0127 \ \text{H}$ |  |

| Initial phase angle $\varphi$                                  |                   | 5.03°                                                                   |  |

| Starting time for the breaker of series unit                   |                   | 0.5 s                                                                   |  |

| Starting time for the power flow control                       |                   | 2.5 s                                                                   |  |

| Targeted power flow                                            | t = 2.5 - 5.0  s  | $P_{\text{set1}} = 800 \text{ W}, Q_{\text{set1}} = -100 \text{ Var}$   |  |

|                                                                | t = 5.0 - 10.0  s | $P_{set2} = 1000$ W, $Q_{set2} = -100$ Var                              |  |

Table 1. DPFC device parameters.

The corresponding parameters for the control loops of DPFC series unit are shown in Table 2.

| Fcn1                                         | Fcn2                                  | Fcn3                     | Fcn4           |

|----------------------------------------------|---------------------------------------|--------------------------|----------------|

| $k_p = 5$ $k_I = 5 \times 10^{-5} \text{ s}$ | $k_{p1} = 5$                          | $k_{p2} = 10$            | G = 0.1        |

|                                              | $k_{I1} = 5 \times 10^{-5} \text{ s}$ | $k_{I2} = 0.2 \text{ s}$ | T = 0.02 s     |

| Fcn5                                         | Fcn6                                  | Fcn7                     | Fcn8           |

| $k_{p3} = 10$                                | $G_1 = 0.2$                           | $k_{p4} = 0.95$          | $G_2 = 1$      |

| $k_{I3} = 0.005 \text{ s}$                   | $T_1 = 0.02$ s                        | $k_{I4} = 0.5$ s         | $T_2 = 0.02 s$ |

Table 2. Tuning parameters for the control loops.

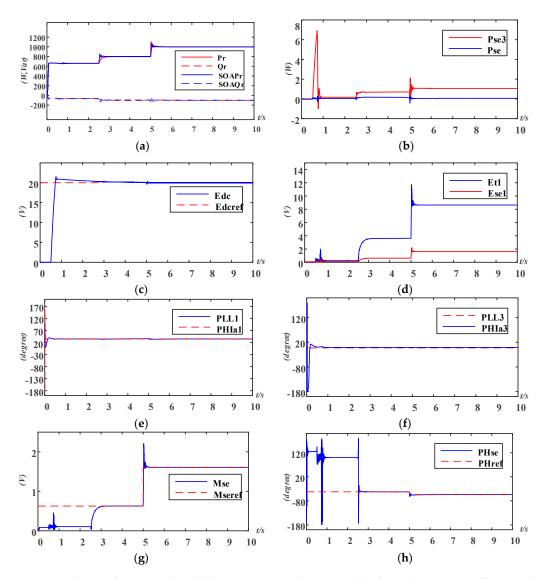

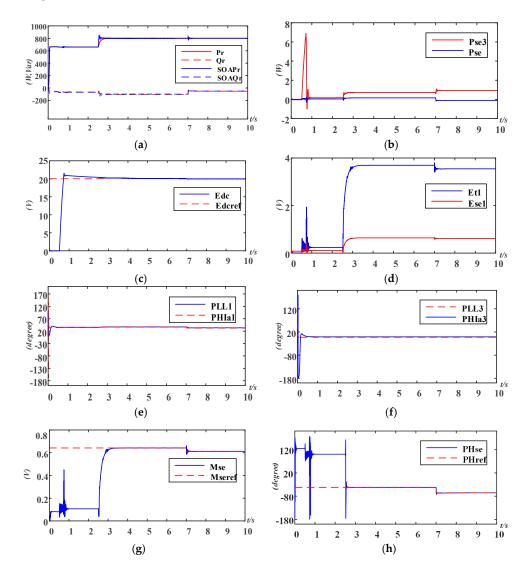

The simulation results of the DPFC coordination control system are depicted in Figure 8.

Figure 8a shows the power flow at the receiving-end of the transmission system by employing the proposed control method. At time t = 3.5 s,  $P_r$  and  $Q_r$  are stable at 799.83 W and -100.66 Var, respectively. At time t = 6.0 s,  $P_r$  and  $Q_r$  are at a new stable state at 999.978 W and -98.25 Var, respectively. Considering the setting value given in Table 2, the power flow control is effective.

Figure 8a also shows the power flow at the receiving end of the transmission system by using the state of art (SOA). At time t = 3.5 s, SOAP<sub>r</sub> and SOAQ<sub>r</sub> are stable at 800.14 W and -98.11 Var, respectively. At time t = 6.0 s, SOAP<sub>r</sub> and SOAQ<sub>r</sub> are at a new stable state 1000.42 W and -99.998 Var, respectively. Considering the setting value given in Table 2, the power flow control is effective.

Comparing the proposed method with the SOA according to the simulation results of the independent active power flow control, it is indicated that both are effective and the control effects are similar.

**Figure 8.** The simulation results of the DPFC control system. (a) Three-phase power flow at the receiving-end; (b) exchange of active power flow in the series unit; (c) DC capacitor voltage of each series unit; (d) magnitude of voltage of the single-turn transformer (STT); (e) SPLL result of the base-frequency line current by fast Fourier transform (FFT) component extraction; (f) SPLL result of the third harmonic current by FFT component extraction; (g) the magnitude of compensated voltage for each series unit; (h) the phase angle of compensated voltage for each series unit.

Figure 8b displays the exchange of the third harmonic active power flow  $P_{se3}$  and base-frequency active power flow  $P_{se1}$  for each series unit. It is worth noting that  $P_{se3} \neq P_{se1}$  for the reason that active power loss of VSC at the third harmonic and base frequency are not equal. Combining this power exchange process with the DC capacitor voltage in Figure 8c, it is verified that the third harmonic frequency active power is used for building and maintaining the voltage of the DC capacitor.

Figure 8c indicates the DC capacitor voltage  $E_{dc}$  of VSC.  $E_{dc}$  grows dramatically and then remains stable at the reference value 20 V, which verifies the validity of DC-voltage control.

Figure 8d represents the magnitudes of the base-frequency voltage at the primary side and secondary side of STT.  $E_{t1}$  is the primary-side voltage while  $E_{se1}$  is the secondary-side voltage. At t = 3.5 s,  $E_{t1} = 3.606$  V and  $E_{se1} = 0.626$  V. At t = 6.0 s,  $E_{t1} = 8.643$  V and  $E_{se1} = 1.607$  V. The ratio of STT is 20:100 (secondary side to primary side); however, the ratio between the actual voltage  $E_{se1}$  and  $E_{t1}$  is not strictly equal to 1:5. Therefore, a modification for the modulation signal  $v_{mod1}$  is needed.

Figure 8e,f display the SPLL results of the line current by FFT (fast Fourier transform) component extraction. Both the phases of base-frequency and the third harmonic line current can be locked quickly and accurately.

Figure 8g,h indicate the magnitude and phase angle of the base-frequency series-compensated voltage for each DPFC series unit. At t = 3.5 s, the actual values are  $M_{se} = 0.626$  V and  $\theta_{se} = -42.365^{\circ}$  while the setting values are  $M_{se\_ref} = 0.627$  V and  $\theta_{se\_ref} = -42.502^{\circ}$ . At t = 6.5 s, the actual values are  $M_{se} = 1.607$  V and  $\theta_{se} = -54.068^{\circ}$  while the setting values are  $M_{se\_ref} = 1.607$  V and  $\theta_{se\_ref} = -53.665^{\circ}$ . Thus, the control of the base-frequency series-compensated voltage is effective.

4.1.2. Test Case 2

The target power flows are changed to  $P_{set3} = 800$  W and  $Q_{set3} = -100$  Var from t = 2.5 to 7.0 s while these are  $P_{set4} = 800$  W and  $Q_{set4} = -50$  Var from t = 7.0 to 10.0 s. The simulation results are shown in Figure 9.

**Figure 9.** The simulation results of the DPFC control system. (a) Three-phase power flow at the receiving-end; (b) exchange of active power flow in the series unit; (c) DC capacitor voltage of each series unit; (d) magnitude of voltage of STT; (e) SPLL result of base-frequency line current; (f) SPLL result of third harmonic current; (g) the magnitude of compensated voltage; (h) the phase angle of compensated voltage.

Figure 9a shows the power flow at the receiving end of the transmission system by employing the proposed control method. At time t = 3.5 s,  $P_r$  and  $Q_r$  are stable at 802.59 W and -101.81 Var, respectively. At time t = 8.0 s,  $P_r$  and  $Q_r$  are at a new stable state of 802.86 W and -50.43 Var, respectively. Considering the given setting value, the power flow control is effective.

Figure 9a also indicates the power flow at the receiving-end of the transmission system by using the state of art (SOA). At time t = 3.5 s, SOAP<sub>r</sub> and SOAQ<sub>r</sub> are stable at 800.14 W and -98.11 Var, respectively. At time t = 8.0 s, SOAP<sub>r</sub> and SOAQ<sub>r</sub> are at a new stable state of 800.01 W and -49.997 Var, respectively. Considering the given setting value, the power flow control is effective.

Therefore, it is verified that both the proposed method and SOA method are effective for the independent reactive power flow control. Additionally, the effects of these two methods are similar.

Figure 9b displays the exchange of the third harmonic active power flow  $P_{se3}$  with base-frequency active power flow  $P_{se1}$  for each series unit. It is worth to noting that the power exchange process is consistent with the tendency of the DC capacitor voltage in Figure 9c; hence, it is indicated that the third harmonic frequency active power is used for building and maintaining the voltage of the DC capacitor.

Figure 9c indicates the DC capacitor voltage  $E_{dc}$  of VSC.  $E_{dc}$  can still stay stable at 20 V when the target power flow changes, which verifies the validity of the DC capacitor voltage control.

Figure 9d represents the magnitudes of the base-frequency voltage at the primary side and secondary side of STT.  $E_{t1}$  is the primary-side voltage while  $E_{se1}$  is the secondary-side voltage. At t = 3.5 s,  $E_{t1} = 3.691$  V and  $E_{se1} = 0.641$  V. At t = 8.0 s,  $E_{t1} = 3.545$  V and  $E_{se1} = 0.612$  V. The ratio of STT is 20:100 (secondary side: primary side); however, the ratio between the actual voltage  $E_{se1}$  and  $E_{t1}$  is not strictly equal to 1:5. Therefore, a correction for the modulation signal  $v_{mod1}$  is necessary.

Figure 9e,f display the SPLL results of the line current extracted by FFT. It is verified that both the phases of the base-frequency and third harmonic line current can be locked quickly with high precision.

Figure 9g,h indicate the magnitude and phase angle of the base-frequency series-compensated voltage generated by each DPFC series unit. At t = 3.5 s, the actual values are  $M_{se} = 0.641$  V and  $\theta_{se} = -42.271^{\circ}$  while the setting values are  $M_{se\_ref} = 0.642$  V and  $\theta_{se\_ref} = -42.401^{\circ}$ . At t = 8.0 s, the actual values are  $M_{se} = 0.612$  V and  $\theta_{se} = -65.776^{\circ}$  while the setting values are  $M_{se\_ref} = 0.612$  V and  $\theta_{se\_ref} = -65.281^{\circ}$ . The control of the base-frequency series-compensated voltage is verified to be effective.

#### 4.2. Comparison of the Proposed Method with the State-of-the-Art

Comparing the proposed method with the SOA in [28] based on the simulation results of power flow control in Figures 8a and 9a in Section 4.1, it is indicated that the control effect of the proposed and existing method are similar in independent active and reactive power flow control.

It should be mentioned that the starting time of the simulation in PSCAD/EMTDC for the phasors of terminal voltage and line current are the same; thus, both the initial phases of the terminal voltage and line current are measurable. In the actual operation system, however, there is no way to acquire the initial phase angle of the terminal voltage except for the phase difference between two phasors.

The SOA takes the real-time phase of the terminal voltage as the input angle of the inverse Park's transformation and generates corresponding reference values of the series-compensated voltage. Thus, the real-time phase of the terminal voltage must be provided for power flow control in multiple series units by high-speed communication link, which is not practical for the actual transmission system.

Using the proposed real-time phase reproducer of the terminal voltage, only the initial difference between the terminal voltage and line current is needed by leveraging the real-time phase of line current locally at the lower control scheme. Hence, the proposed method is much more suitable for practical engineering applications due to the limitations of communication speed, which is not considered in the existing method.

# 5. Conclusions

A coordination control method for DPFC series units has been proposed and verified in this paper. The waveform of the real-time phase of the terminal voltage can be reproduced correctly during a control period within the DPFC series units, and so a high-speed communication link is not required for the real-time power flow control. Hence, it is much more practical for engineering applications. To control the series-compensated voltage exactly, measures to modify the magnitude and angle of the modulation signal through PI control loops have been taken. The control parameters of each series unit are the same to avoid the interaction's inverse impact on multiple series unit. Simulation results from PSCAD/EMTDC have indicated that the proposed power flow control method is effective. By comparing the proposed method with the SOA in simulation and considering the speed limitations of the communication link in an actual transmission system, it can be concluded that the proposed method is more suitable for practical engineering applications with an equivalent control effect to the SOA. In future research work, experimental testing will be carried out to verify the proposed method further.

**Author Contributions:** Supervision, S.W.; Investigation and Formal analysis, M.X.; Research ideas and innovative schemes, S.W. and M.X.; Writing and Revising, M.X.; Project administration, S.W. and M.X.; Resources and Funding acquisition, S.W.

**Funding:** The authors would like to thank for the sponsorship offered by State Grid Science & Technology Project of China (52150016000Y).

**Conflicts of Interest:** The authors declare no conflict of interest.

# References

- Hingorani, N.G. High power electronics and flexible ac transmission system. *IEEE Power Eng. Rev.* 1988, 50, 3–4. [CrossRef]

- 2. Hingorani, N. Flexible AC Transmission. IEEE Spectr. 1993, 30, 40–45. [CrossRef]

- 3. Hingorani, N.G.; Gyugyi, L. Understanding FACTS: Concepts and Technology of Flexible AC Transmission Systems; IEEE Press: New York, NY, USA, 2000.

- 4. Gyugyi, L. Unified power-flow control concept for flexible AC transmission systems. *IEE Proc. C-Gener. Transm. Distrib.* **1992**, *139*, 323–331. [CrossRef]

- 5. Gyugyi, L.; Schauder, C.; Williams, S.; Rietman, T.; Torgerson, D.; Edris, A. The unified power flow controller: A new approach to power transmission control. *IEEE Trans. Power Deliv.* **1995**, *10*, 1085–1097. [CrossRef]

- 6. Li, P.; Wang, Y.; Feng, C.; Lin, J. Application of MMC-UPFC in the 500 kV power grid of Suzhou. *J. Eng.* **2017**, 13, 2514–2518. [CrossRef]

- Albatsh, F.M.; Mekhilef, S.; Ahmad, S.; Mokhlis, H. Fuzzy-Logic-Based UPFC and Laboratory Prototype Validation for Dynamic Power Flow Control in Transmission Lines. *IEEE Trans. Ind. Electron.* 2017, 64, 9538–9548. [CrossRef]

- 8. Pereira, M.; Zanetta, L.C. A current based model for load flow studies with UPFC. *IEEE Trans. Power Syst.* **2013**, *28*, 677–682. [CrossRef]

- 9. Jena, M.K.; Samantaray, S.R. Data-Mining-Based Intelligent Differential Relaying for Transmission Lines Including UPFC and Wind Farms. *IEEE Trans. Neural Netw. Learn. Syst.* **2016**, *27*, 8–17. [CrossRef] [PubMed]

- Yuan, J.; Liu, L.; Fei, W.; Chen, L.; Chen, B.; Chen, B. Hybrid Electromagnetic Unified Power Flow Controller: A Novel Flexible and Effective Approach to Control Power Flow. *IEEE Trans. Power Deliv.* 2018, 33, 2061–2069. [CrossRef]

- 11. Sayed, M.A.; Takeshita, T. Line Loss Minimization in Isolated Substations and Multiple Loop Distribution Systems Using the UPFC. *IEEE Trans. Power Electron.* **2014**, *29*, 5813–5822. [CrossRef]

- Divan, D.; Brumsickle, W.; Schneider, R.; Kranz, B.; Gascoigne, R.; Bradshaw, D.; Ingram, M.; Grant, I. A distributed static series compensator system for realizing active power flow control on existing power lines. In Proceedings of the IEEE PES Power Systems Conference and Exposition, New York, NY, USA, 10–13 October 2004; Volume 2, pp. 654–661.

- Divan, D.; Brumsickle, W.E.; Schneider, R.S.; Kranz, B.; Gascoigne, R.; Bradshaw, D.; Ingram, M.; Grant, I. A Distributed Static Series Compensator System for Realizing Active Power Flow Control on Existing Power Lines. *IEEE Trans. Power Deliv.* 2007, 22, 642–649. [CrossRef]

- 14. Divan, D.; Johal, H. Distributed FACTS—A New Concept for Realizing Grid Power Flow Control. *IEEE Trans. Power Electron.* **2007**, *22*, 2253–2260. [CrossRef]

- 15. Dorostkar-Ghamsari, M.; Fotuhi-Firuzabad, M. Probabilistic Worth Assessment of Distributed Static Series Compensators. *IEEE Trans. Power Deliv.* **2011**, *26*, 1734–1743. [CrossRef]

- 16. Dorostkar-Ghamsari, M.; Fotuhi-Firuzabad, M. Optimal distributed static series compensator placement for enhancing power system loadability and reliability. *IET Gener. Transm. Distrib.* **2015**, *9*, 1043–1050. [CrossRef]

- 17. Brissette, A.; Maksimović, D.; Levron, Y. Distributed Series Static Compensator Deployment Using a Linearized Transmission System Model. *IEEE Trans. Power Deliv.* **2015**, *30*, 1269–1277. [CrossRef]

- Raythaththa, K.G.; Vyas, B.Y. System parameters improvement of transmission line using Distributed Static Series Compensator (DSSC). In Proceedings of the International Conference on Energy Efficient Technologies for Sustainability (ICEETS), Nagercoil, India, 7–8 April 2016; pp. 459–463.

- Gaigowal, S.R.; Renge, M.M. Distributed power flow controller using single phase DSSC to realize active power flow control through transmission line. In Proceedings of the 2016 International Conference on Computation of Power Energy Information and Communication (ICCPEIC), Chennai, India, 20–21 April 2016; pp. 747–751.

- 20. Yuan, Z.; de Haan, S.W.H.; Ferreira, J.B.; Cvoric, D. A FACTS Device: Distributed Power-Flow Controller (DPFC). *IEEE Trans. Power Electron.* 2010, *25*, 2564–2572. [CrossRef]

- Yuan, Z.; de Haan, S.W.H.; Ferreira, J.B. Control scheme to improve DPFC performance during series converter failures. In Proceedings of the IEEE Power and Energy Society General Meeting, Providence, RI, USA, 25–29 July 2010; pp. 1–6.

- 22. Yuan, Z.; de Haan, S.W.H.; Ferreira, J.B. Construction and first result of a scaled transmission system with the Distributed Power Flow Controller (DPFC). In Proceedings of the European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–10.

- 23. Divya, S.; Shyamala, U. Power Quality Improvement in Transmission Systems Using DPFC. In Proceedings of the IEEE 2nd International Conference on Electronics and Communication System (ICECS), Coimbatore, India, 26–27 February 2015.

- 24. Jamshidi, A.; Barakati, S.M.; Ghahderijani, M.M. Power quality improvement and mitigation case study using distributed power flow controller. In Proceedings of the 2012 IEEE International Symposium on Industrial Electronics (ISIE), Hangzhou, China, 28–31 May 2012; pp. 464–468.

- Ramya, K.; Rajan, C.C.A. Analysis and Regulation of System Parameters Using DPFC. In Proceedings of the IEEE International Conference on Advances in Engineering, Science and Management (ICAESM), Nagapattinam, Tamil Nadu, India, 30–31 March 2012; pp. 505–509.

- 26. Tang, Y.; Liu, Y.; Ning, J.; Zhao, J. Multi-Time Scale Coordinated Scheduling Strategy with Distributed Power Flow Controllers for Minimizing Wind Power Spillage. *Energies* **2017**, *10*, 1804. [CrossRef]

- 27. Tang, A.; Shao, Y.; Huang, Y.; Xu, Q. A new topology of the distributed power flow controller and its electromagnetic transient characteristics. *Electr. Power Syst. Res.* **2018**, *163*, 280–287. [CrossRef]

- 28. Tang, A.; Lu, J.; Xuan, J.; Yuan, W.; Wang, S. Study of the power control ability of the distributed power flow controller. *Power Syst. Prot. Control* **2012**, *40*, 15–20.

- 29. Tang, A. Study on a new distributed power flow control method. Power Syst. Prot. Control 2011, 39, 89–94.

- Picardi, C.; Sgrò, D.; Gioffré, G. A simple and low-cost PLL structure for single-phase grid-connected inverters. In Proceedings of the 2010 International Symposium on Power Electronics Electrical Drives Automation and Motion (SPEEDAM), Pisa, Italy, 14–16 June 2010; pp. 358–362.

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).