Control Algorithms of Shunt Active Power Filter for Harmonics Mitigation: A Review

Abstract

:1. Introduction

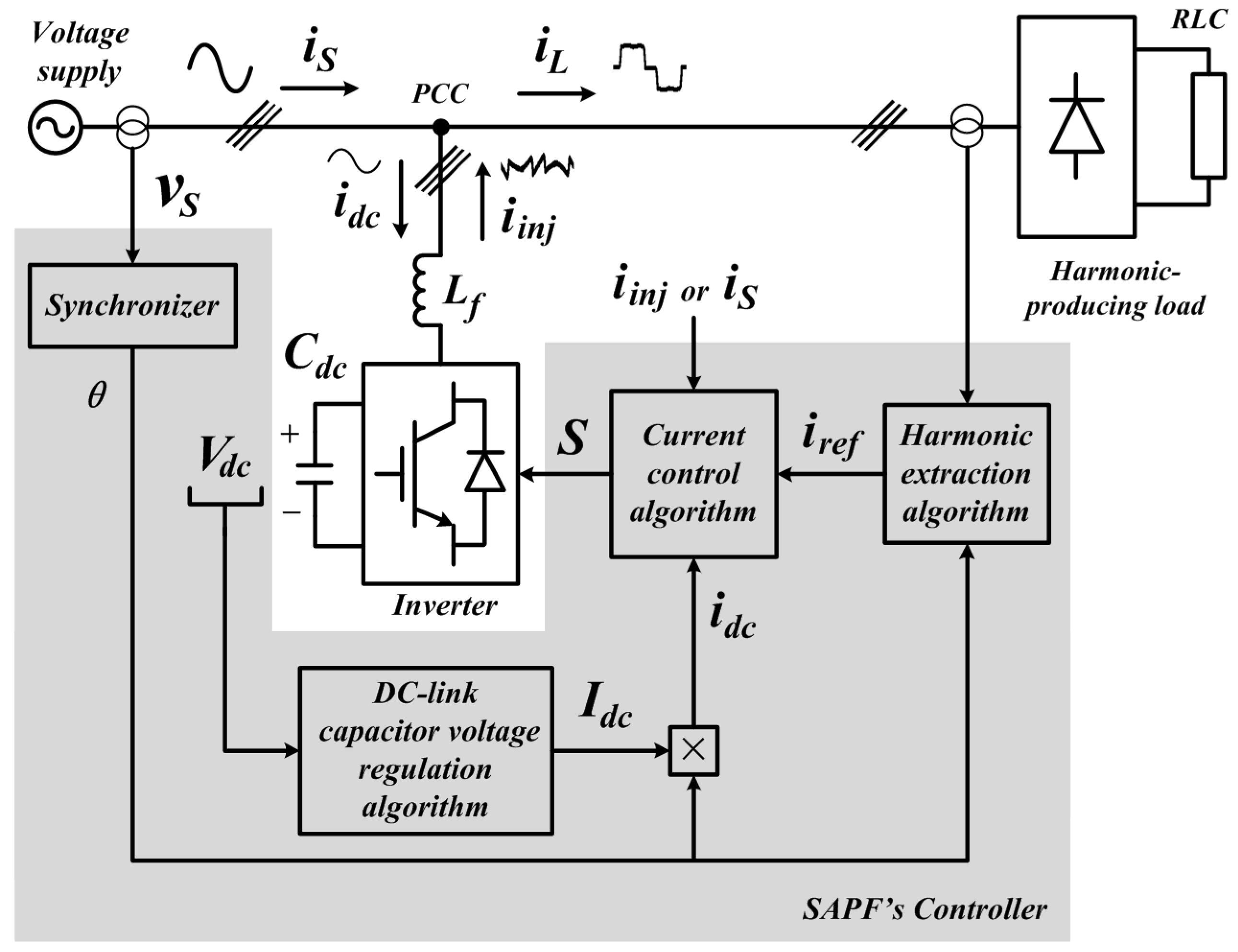

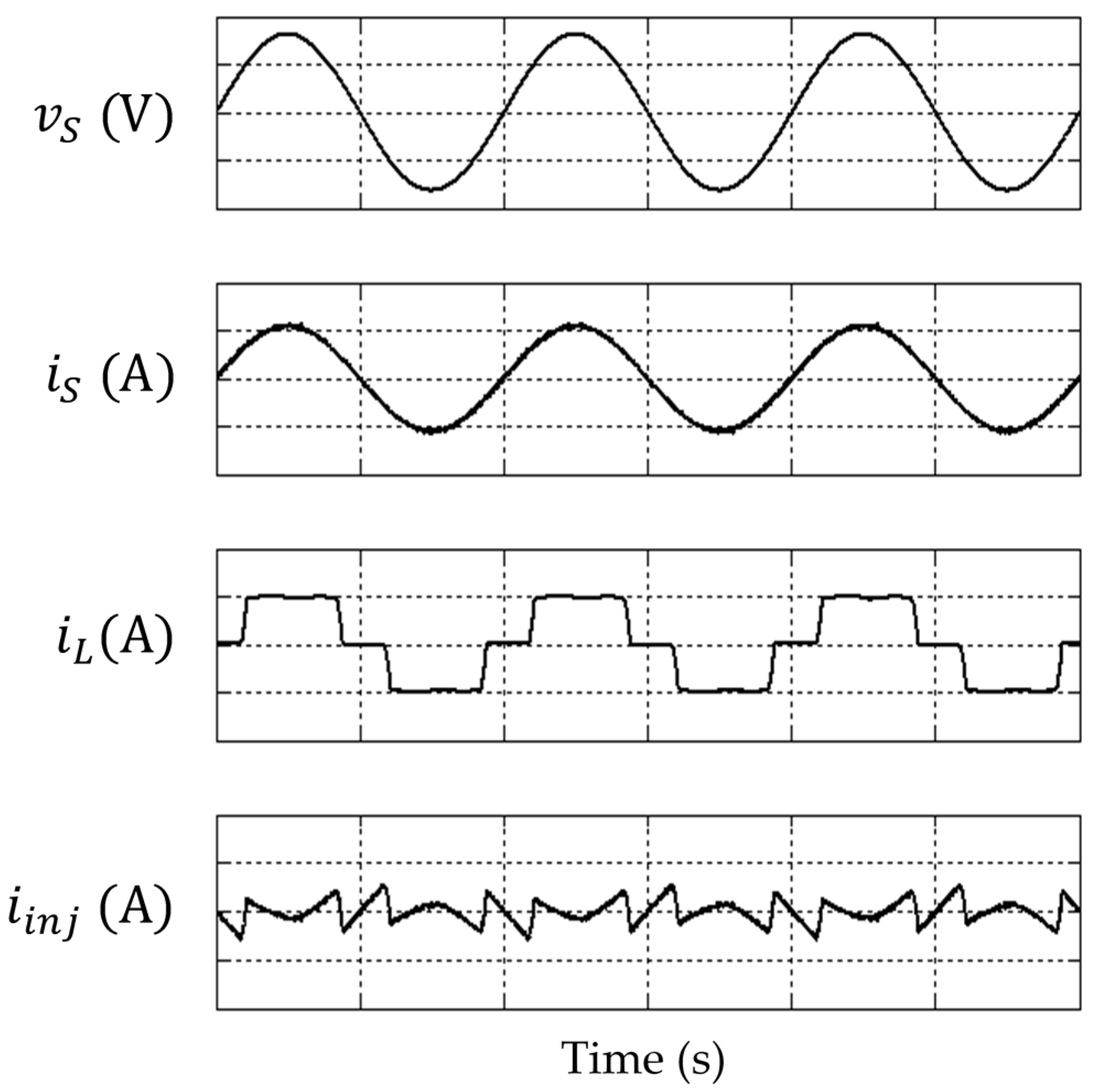

2. Control Structure and Working Principle of Shunt Active Power Filter

- (1)

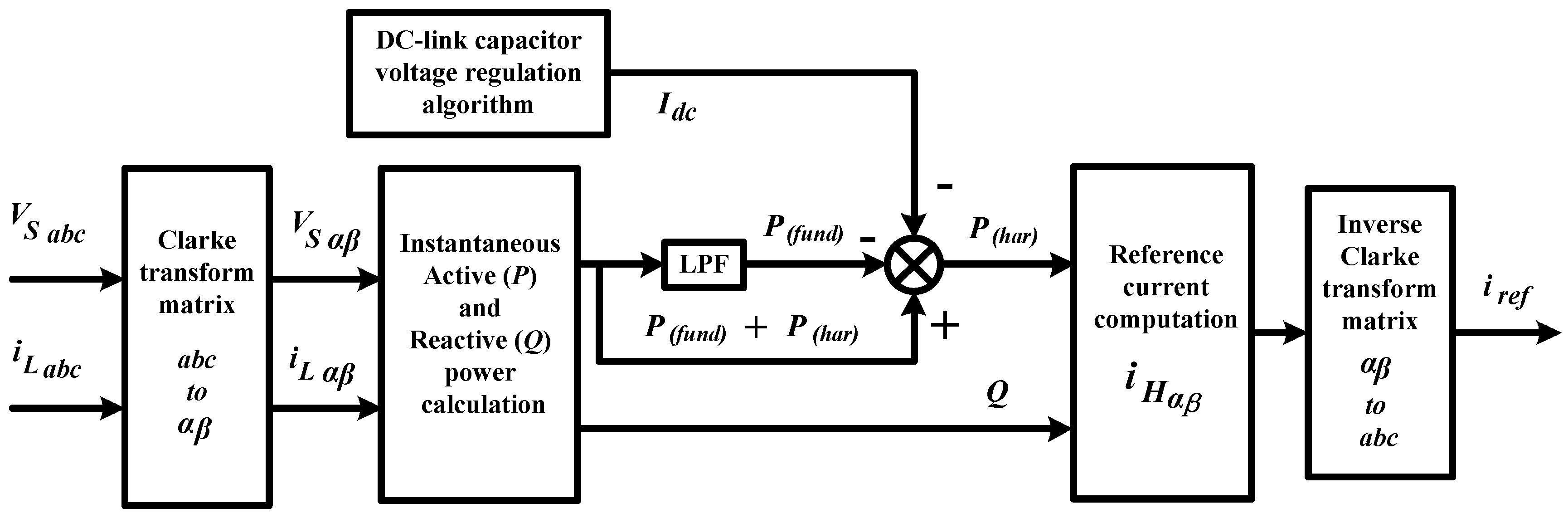

- Harmonic Extraction Algorithm. This control algorithm operates by first taking the distorted load current signal from the harmonic-polluted power system, followed by isolation of harmonic and fundamental current components, and ends with the generation of a reference current signal . The generated reference current signal is used to govern the operation of the SAPF in reducing the harmonic distortion. Since its main purpose is to generate a reference current signal, hence it is also known as reference current generation algorithm.

- (2)

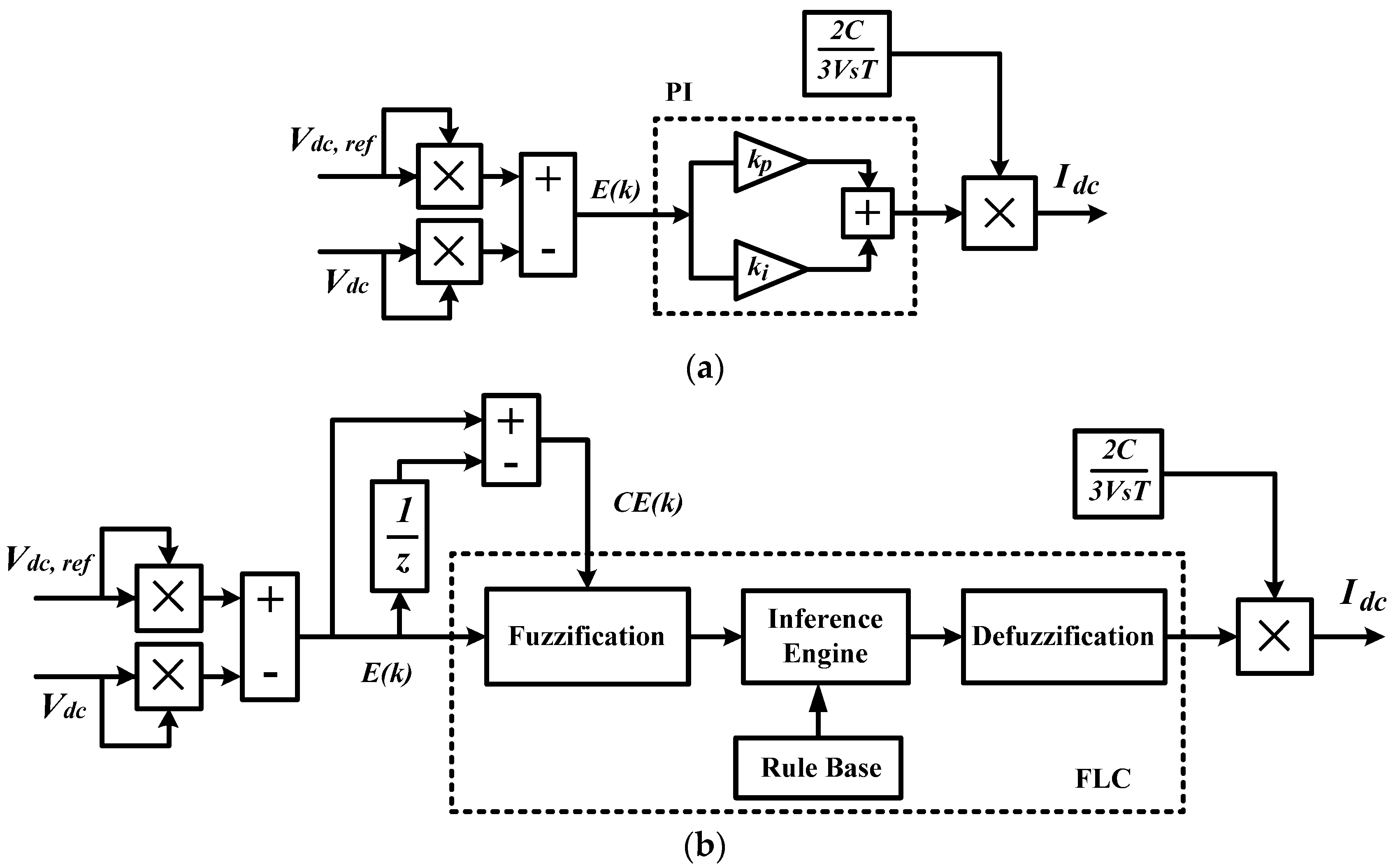

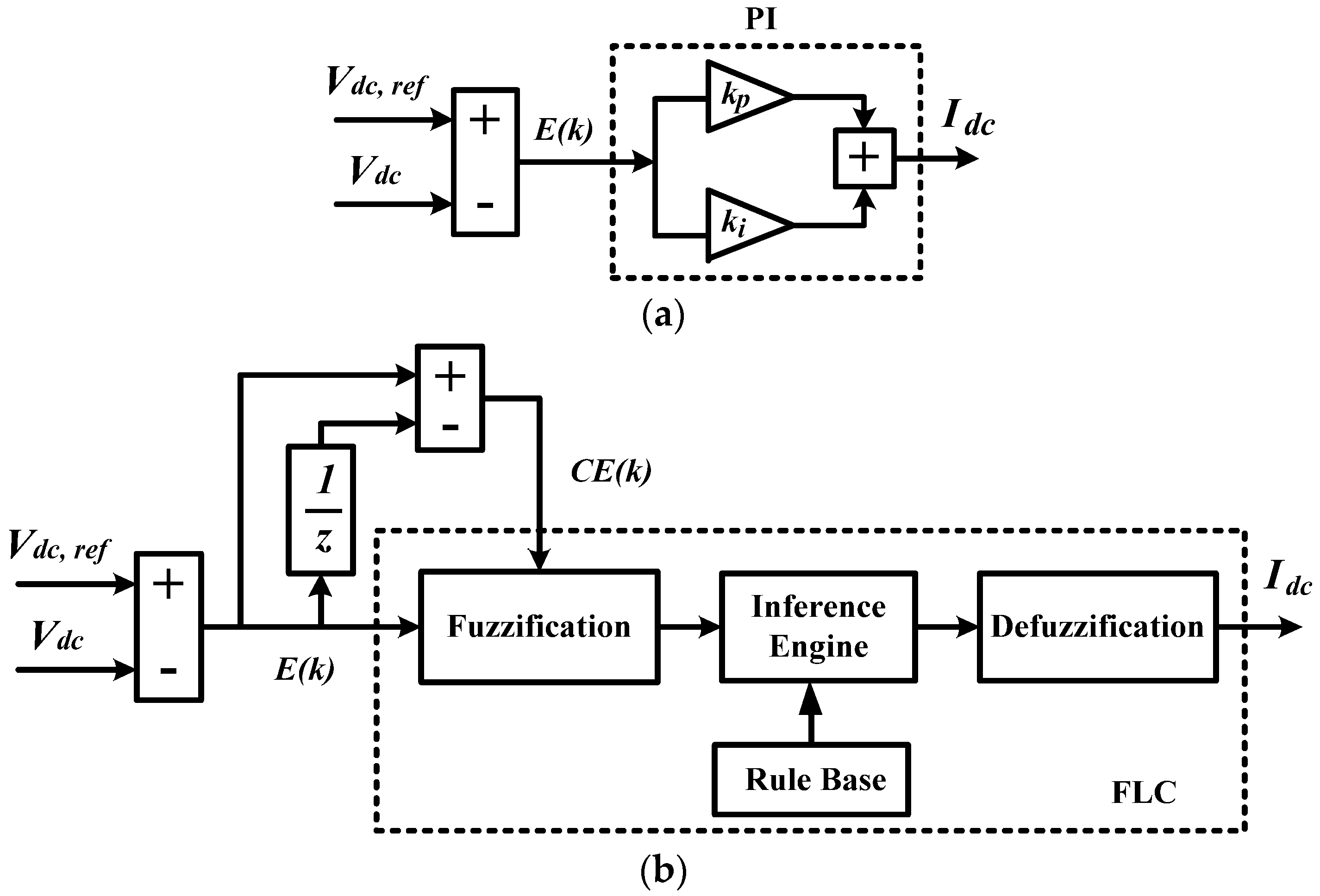

- DC-link Capacitor Voltage Regulation Algorithm. The control algorithm that takes the instantaneous DC-link capacitor voltage and compares it with a desired reference value. The resulting error is used to estimate the suitable magnitude of the instantaneous DC-link charging current . The estimated is the amount of needed to be drawn by the SAPF to regulate its switching losses so as to constantly maintain DC-link capacitor voltage at the desired reference value.

- (3)

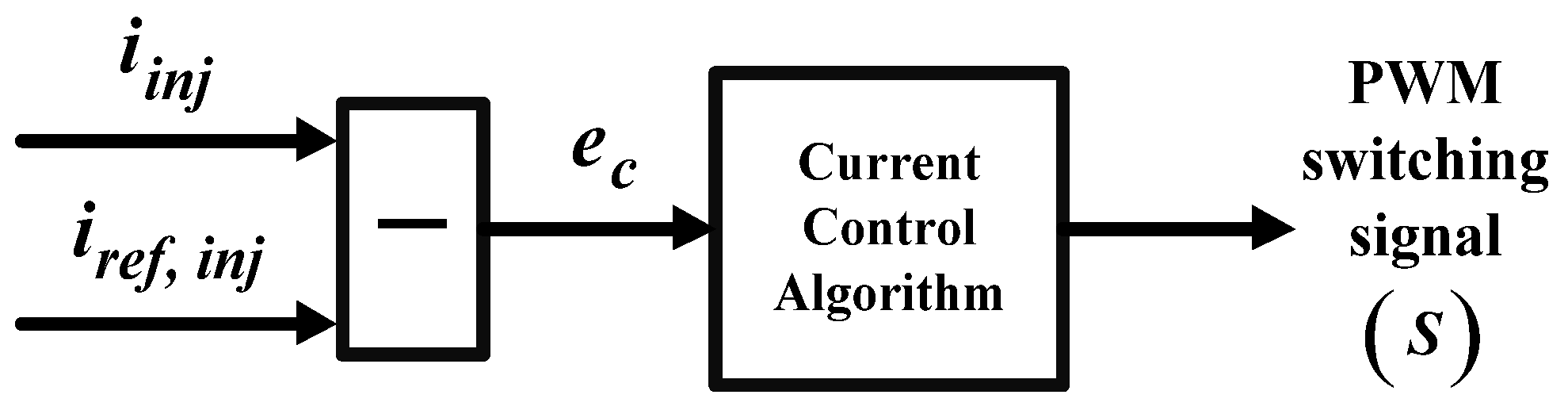

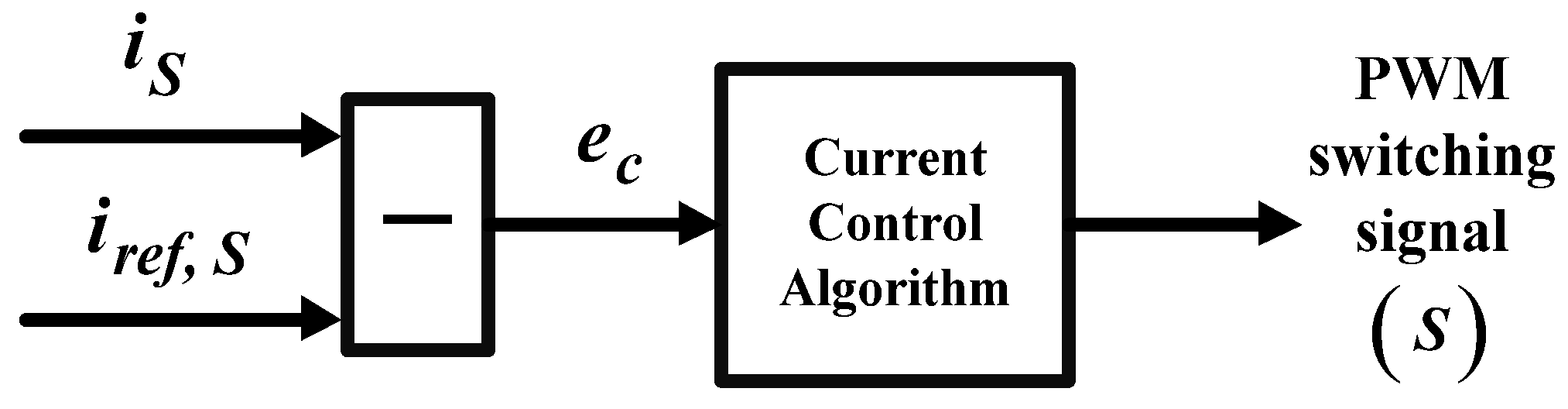

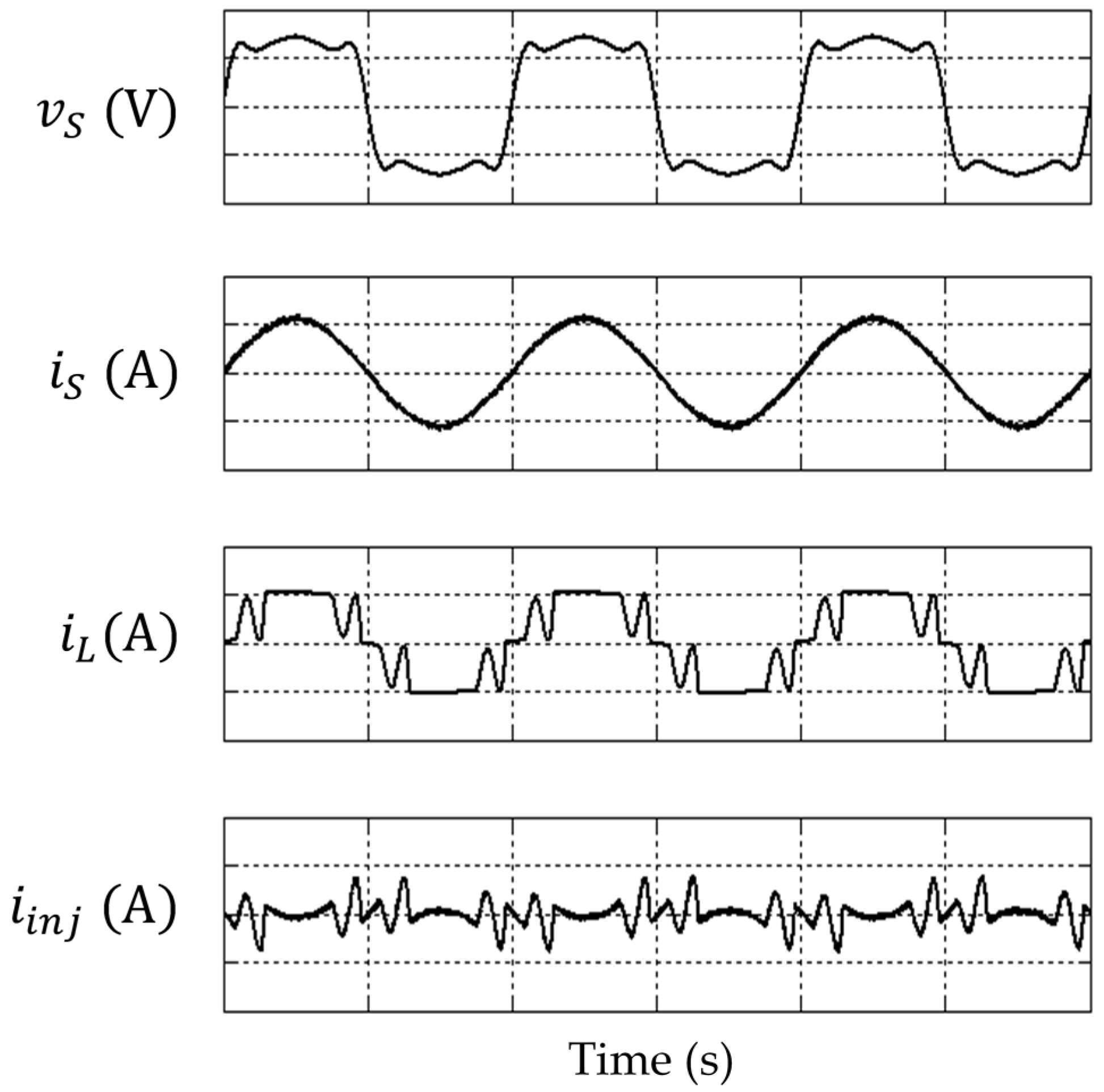

- Current Control Algorithm. This is the control algorithm that takes the output of the harmonic extraction and DC-link capacitor voltage regulation algorithms to generate switching pulses for the controlling operation of the inverter so that it functions as a SAPF. It consists of a pulse-width modulator to generate the desired switching pulses and a local current control loop that ensures that the injection current is generated according to the reference current .

- (4)

- Synchronizer Algorithm. This control algorithm (commonly developed based on phase-locked loop (PLL) techniques) takes the source voltage signal and generates a synchronization angle/phase, so that injection current which is injected by the SAPF into the operating power system is correctly synchronized with the source voltage. It should be noted that certain SAPF controllers do not require explicit synchronization algorithms.

- (5)

- Voltage Source Inverter. This is a power converter which is systematically controlled to reproduce the reference current as injection current , at suitable magnitude. It is equipped with a DC-link capacitor (energy storage element) to compensate real power unbalance that occurs during dynamic operation of the SAPF and a filter inductor to minimize the ripples of injection current .

- (6)

- Harmonic-producing Load. This is a nonlinear load which injects a harmonic current into an operating power system via PCC. Switch-mode power supplies, arc furnaces, adjustable speed drive (ASD), and rectifiers are a few examples of practical loads that generate serious amounts of harmonic currents and reactive power in the power system. However, in simulation and laboratory evaluations, an uncontrolled bridge rectifier is most commonly applied, as it causes the worst harmonic current distortions [1,17,19]. Note that, the output of the bridge rectifier is normally connected to three types of loads: (1) series connected resistor and inductor (simply known as inductive load); (2) parallel connected resistor and capacitor (simply known as capacitive load); and (3) a single resistor (simply known as resistive load).

3. SAPF Control Algorithms

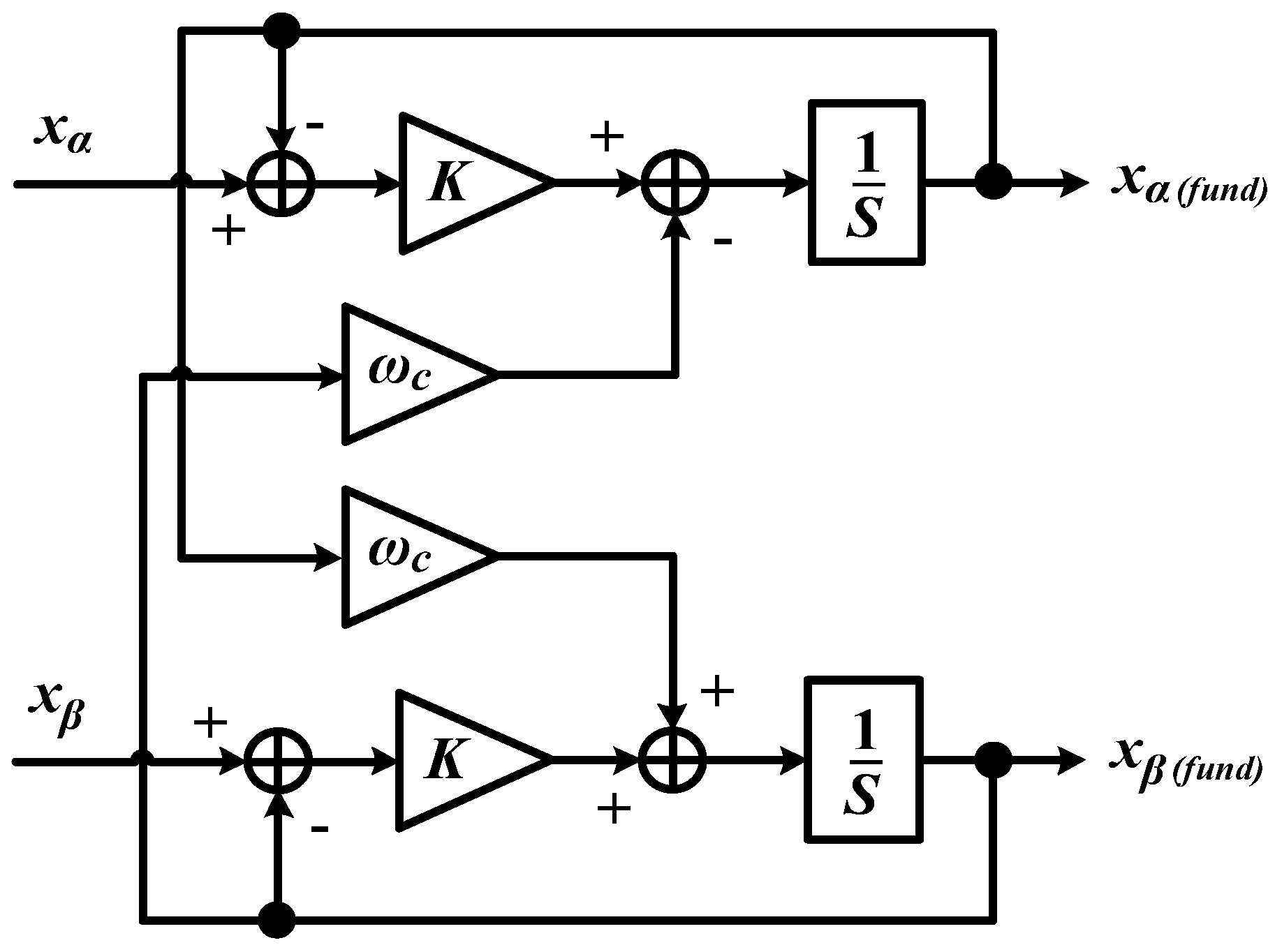

3.1. Harmonic Extraction Algorithm

3.1.1. Time-Domain

3.1.2. Frequency-Domain

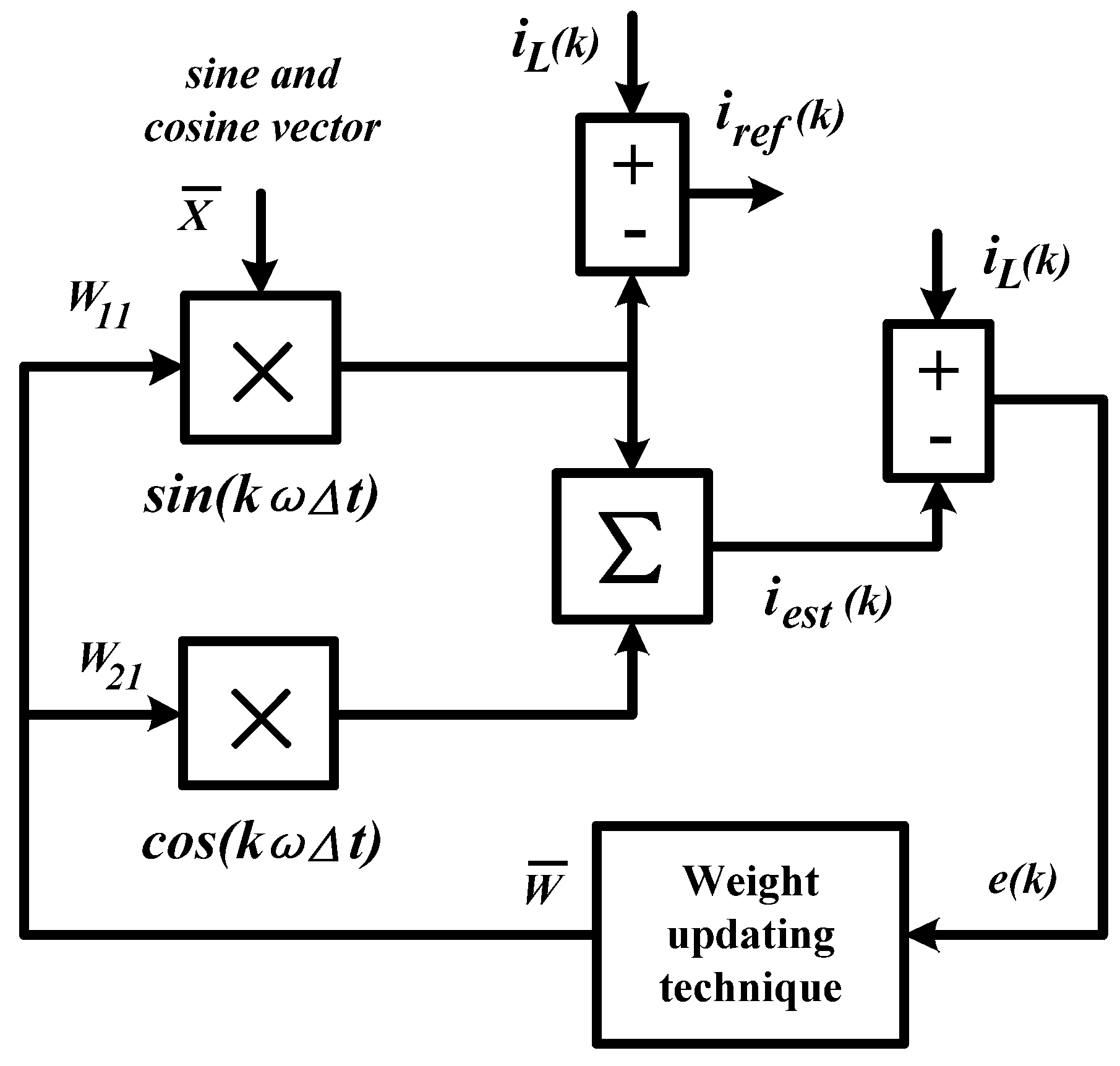

3.1.3. Learning Techniques

3.1.4. Other Algorithms

3.2. DC-Link Capacitor Voltage Regulation Algorithm

3.2.1. Direct Voltage Error Manipulation Approach

3.2.2. Self-Charging Technique

3.2.3. Other Approaches

3.3. Current Control Algorithm

3.3.1. Direct and Indirect Current Control of SAPF

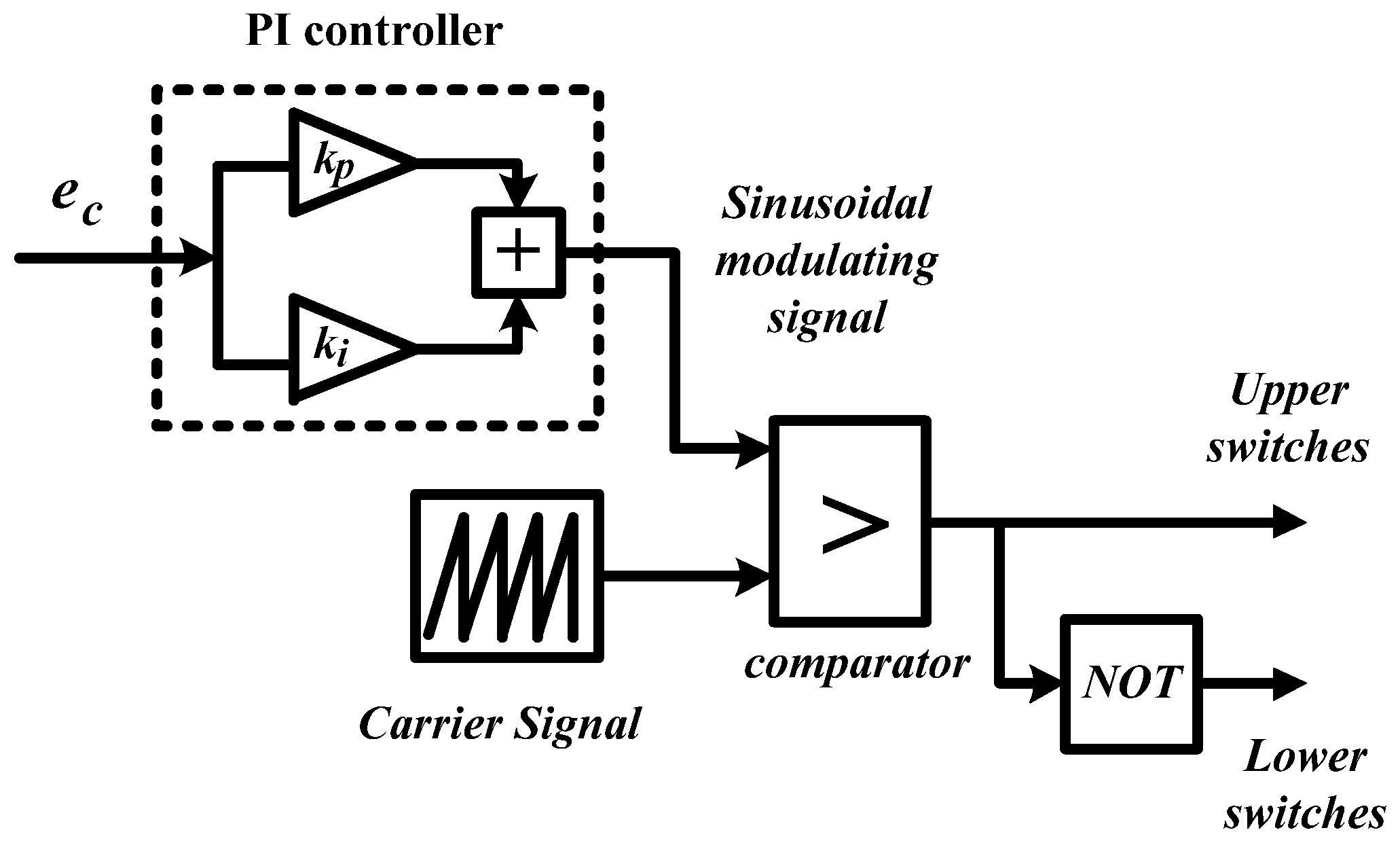

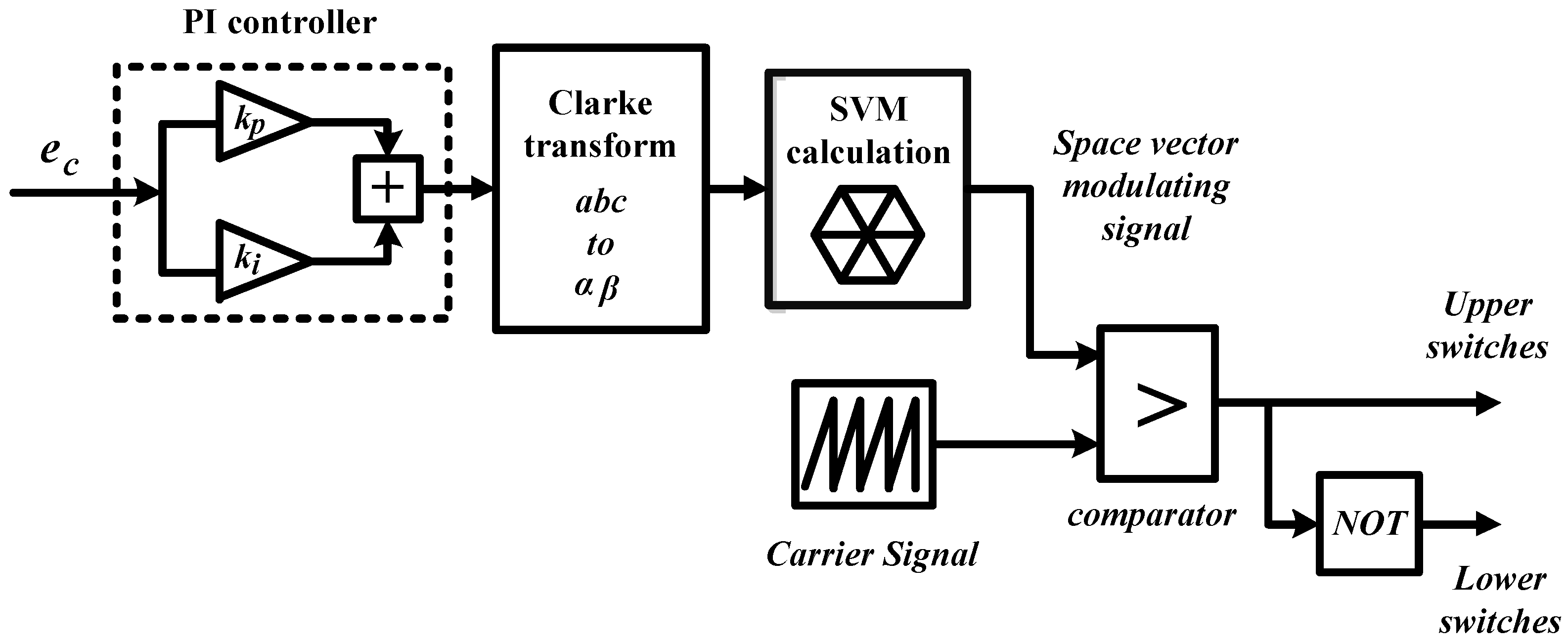

3.3.2. Pulse-Width Modulation (PWM)

3.3.3. Hysteresis Current Control

3.3.4. Predictive Control

3.4. Synchronizer Algorithm

4. SAPF Operation under Non-Ideal Source Voltage Conditions

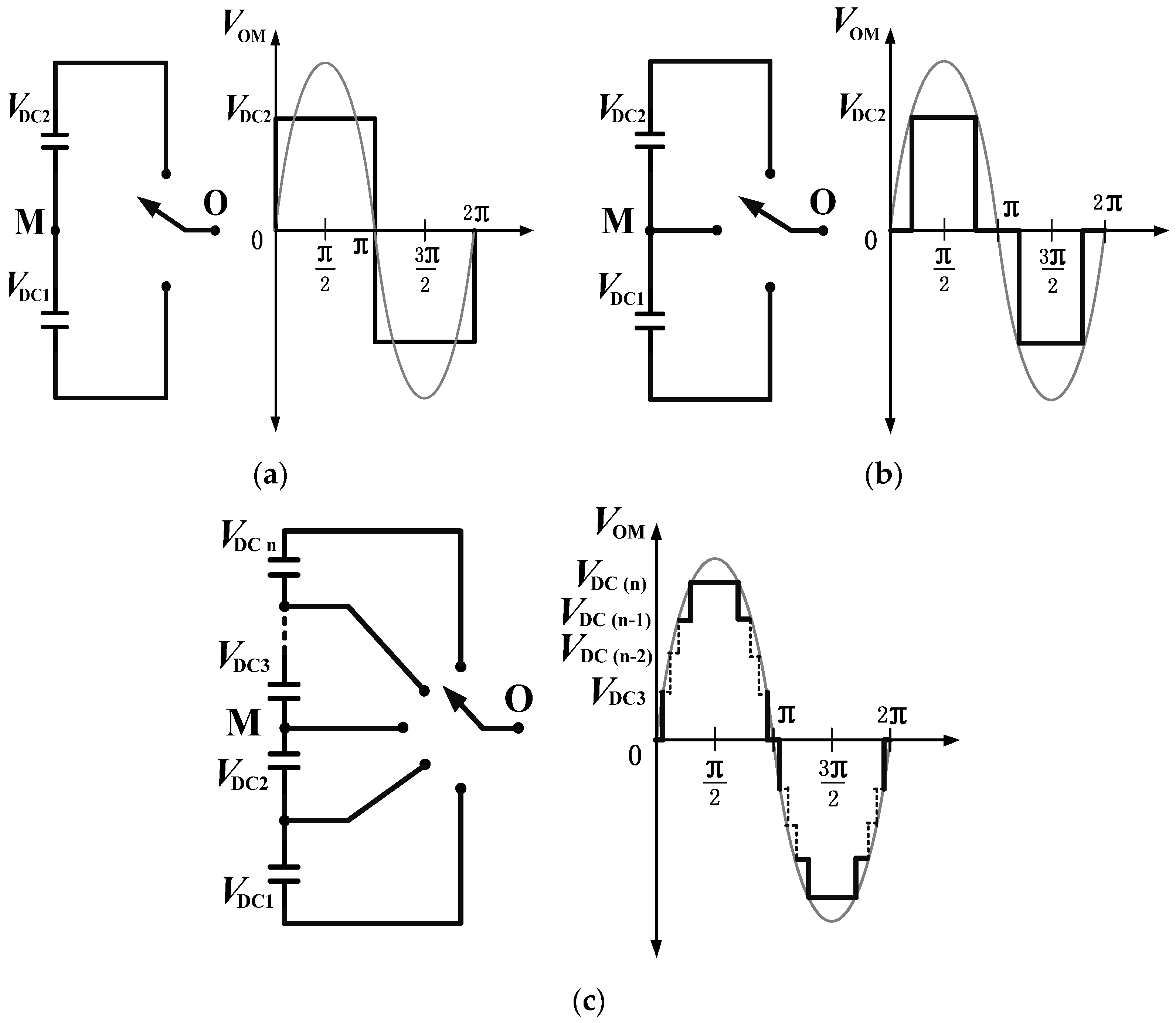

5. Operation of SAPFs with Multilevel Inverters as Circuit Topology

- They produce output voltages with negligible harmonic distortion, thereby improving the mitigation performance of SAPFs.

- They significantly reduce voltage stresses across the power semiconductor switches, which allows the usage of lower voltage-rated semiconductor devices, and thus improves the economical features of the SAPF.

- They are not only suitable for low voltage applications, but also can fulfill the higher output voltage requirements which are needed for medium and high voltage applications.

- They are able to work with both fundamental switching frequency and high switching frequency pulse-width modulation (PWM). Note that, operating with lower switching frequency provides lower switching losses and higher efficiency.

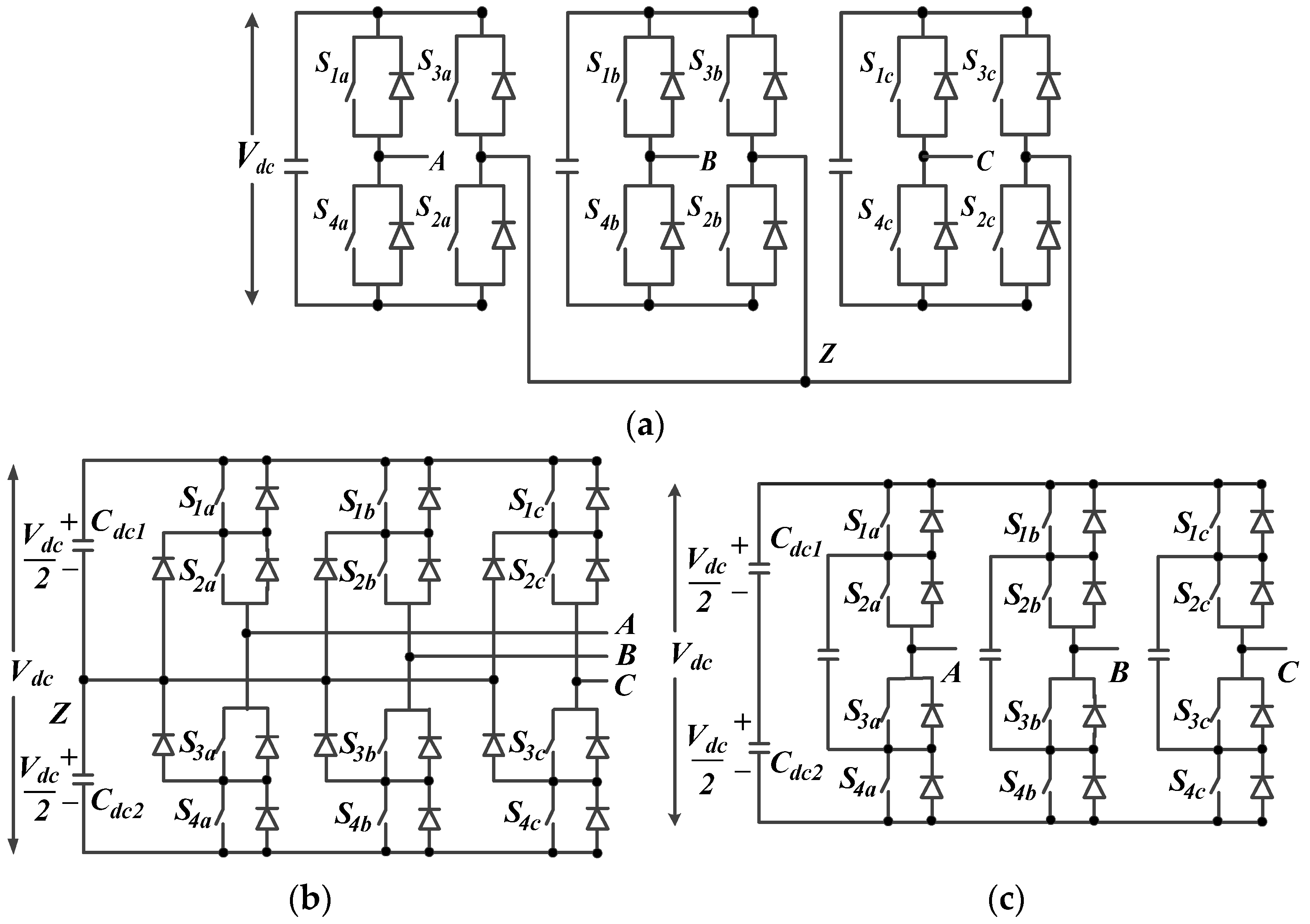

5.1. Comparative Study of Multilevel Inverters

5.2. Control Algorithms of Multilevel Inverter-Based SAPF

6. Conclusions

Author Contributions

Conflicts of Interest

References

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F. Enhanced instantaneous power theory with average algorithm for indirect current controlled three-level inverter-based shunt active power filter under dynamic state conditions. Math. Probl. Eng. 2016. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F. DC-link capacitor voltage regulation for three-phase three-level inverter-based shunt active power filter with inverted error deviation control. Energies 2016, 9, 533. [Google Scholar] [CrossRef]

- Institute of Electrical and Electronics Engineers (IEEE). IEEE recommended practice and requirement for harmonic control in electric power systems. In IEEE Std 519-2014 (Revision of IEEE Std 519-1992); IEEE: Piscataway, NJ, USA, 2014; pp. 1–29. [Google Scholar]

- Akagi, H. Active harmonic filters. IEEE Proc. 2005, 93, 2128–2141. [Google Scholar] [CrossRef]

- Grady, W.M.; Samotyj, M.J.; Noyola, A.H. Survey of active power line conditioning methodologies. IEEE Trans. Power Deliv. 1990, 5, 1536–1542. [Google Scholar] [CrossRef]

- Singh, B.; Al-Haddad, K.; Chandra, A. A review of active filters for power quality improvement. IEEE Trans. Ind. Electron. 1999, 46, 960–971. [Google Scholar] [CrossRef]

- Peng, F.Z. Harmonic sources and filtering approaches. IEEE Ind. Appl. Mag. 2001, 7, 18–25. [Google Scholar] [CrossRef]

- El-Habrouk, M.; Darwish, M.K.; Mehta, P. Active power filters: A review. IEEE Proc. Electr. Power Appl. 2000, 147, 403–413. [Google Scholar] [CrossRef]

- Green, T.C.; Marks, J.H. Control techniques for active power filters. IEEE Proc. Electr. Power Appl. 2005, 152, 369–381. [Google Scholar] [CrossRef]

- Asiminoaei, L.; Blaabjerg, F.; Hansen, S. Detection is key—Harmonic detection methods for active power filter applications. IEEE Ind. Appl. Mag. 2007, 13, 22–33. [Google Scholar] [CrossRef]

- Bhattacharya, A.; Chakraborty, C.; Bhattacharya, S. Shunt compensation—Reviewing traditional methods of reference current generation. IEEE Ind. Electron. Mag. 2009, 3, 38–49. [Google Scholar] [CrossRef]

- Kale, M.; Ozdemir, E. Harmonic and reactive power compensation with shunt active power filter under non-ideal mains voltage. Electr. Power Syst. Res. 2005, 74, 363–370. [Google Scholar] [CrossRef]

- Djazia, K.; Krim, F.; Chaoui, A.; Sarra, M. Active power filtering using the ZDPC method under unbalanced and distorted grid voltage conditions. Energies 2015, 8, 1584–1605. [Google Scholar] [CrossRef]

- ABB SACE. Power Factor Correction and Harmonic Filtering in Electrical Plants; Technical Application Papers; ABB SACE: Bergamo, Italy, 2008; pp. 1–62. [Google Scholar]

- Schaffner. ECOsine Active: Harmonics Compensation in Real-Time—The Compact, Fast, and Flexible Solution for Better Power Quality; Schaffner: Luterbach, Switzerland, 2011; pp. 1–4. [Google Scholar]

- Schneider Electric. AccuSine PCS Active Harmonic Filter: Cruising through Rough Waves in Your Electrical Network; Schneider Electric: Rueil-Malmaison, France, 2009; pp. 1–16. [Google Scholar]

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F.; Wahab, N.I.A. A simplified synchronous reference frame for indirect current controlled three-level inverter-based shunt active power filters. J. Power Electron. 2016, 16, 1964–1980. [Google Scholar] [CrossRef]

- Rodríguez, J.; Lai, J.-S.; Peng, F.Z. Multilevel inverters: A survey of topologies, controls and applications. IEEE Trans. Ind. Electron. 2002, 49, 724–738. [Google Scholar] [CrossRef]

- Marks, J.H.; Green, T.C. Predictive transient-following control of shunt and series active power filters. IEEE Trans. Power Electron. 2002, 17, 574–584. [Google Scholar] [CrossRef] [Green Version]

- Tey, L.H.; So, P.L.; Chu, Y.C. Improvement of power quality using adaptive shunt active filter. IEEE Trans. Power Deliv. 2005, 20, 1558–1568. [Google Scholar] [CrossRef]

- Eskandarian, N.; Beromi, Y.A.; Farhangi, S. Improvement of dynamic behavior of shunt active power filter using fuzzy instantaneous power theory. J. Power Electron. 2014, 14, 1303–1313. [Google Scholar] [CrossRef]

- Zainuri, M.A.A.M.; Radzi, M.A.M.; Soh, A.C.; Mariun, N.; Rahim, N.A.; Hajighorbani, S. Fundamental active current adaptive linear neural networks for photovoltaic shunt active power filters. Energies 2016, 9, 397. [Google Scholar] [CrossRef]

- Monfared, M.; Golestan, S.; Guerrero, J.M. A new synchronous reference frame-based method for single-phase shunt active power filters. J. Power Electron. 2013, 13, 692–700. [Google Scholar] [CrossRef]

- Jain, N.; Gupta, A. Comparison between two compensation current control methods of shunt active power filter. Int. J. Eng. Res. Gen. Sci. 2014, 2, 603–615. [Google Scholar]

- Mattavelli, P.; Marafao, F.P. Repetitive-based control for selective harmonic compensation in active power filters. IEEE Trans. Ind. Electron. 2004, 51, 1018–1024. [Google Scholar] [CrossRef]

- Maza-Ortega, J.M.; Rosendo-Macías, J.A.; Gómez-Expósito, A.; Ceballos-Mannozzi, S.; Barragán-Villarejo, M. Reference current computation for active power filters by running dft techniques. IEEE Trans. Power Deliv. 2010, 25, 1986–1995. [Google Scholar] [CrossRef]

- Vodyakho, O.; Mi, C.C. Three-level inverter-based shunt active power filter in three-phase three-wire and four-wire systems. IEEE Trans. Power Electron. 2009, 24, 1350–1363. [Google Scholar] [CrossRef]

- Chen, K.F.; Mei, S.L. Composite interpolated fast Fourier transform with the Hanning window. IEEE Trans. Instrum. Meas. 2010, 59, 1571–1579. [Google Scholar] [CrossRef]

- Masoum, M.A.S.; Fuchs, E.F. Power Quality in Power Systems and Electrical Machines, 2nd ed.; Elsevier Science & Technology Books: Amsterdam, The Netherlands, 2015. [Google Scholar]

- Saribulut, L.; Teke, A.; Tümay, M. Artificial neural network based discrete-fuzzy logic controlled active power filter. IET Power Electron. 2014, 7, 1536–1546. [Google Scholar] [CrossRef]

- Welsh, M.; Mehta, P.; Darwish, M.K. Genetic algorithm and extended analysis optimisation techniques for switched capacitor active filters—Comparative study. IEEE Proc. Electr. Power Appl. 2000, 147, 21–26. [Google Scholar] [CrossRef]

- Ibrahim, W.R.A.; Morcos, M.M. Artificial intelligence and advanced mathematical tools for power quality applications: A survey. IEEE Trans. Power Deliv. 2002, 17, 668–673. [Google Scholar] [CrossRef]

- Radzi, M.A.M.; Rahim, N.A. Neural network and bandless hysteresis approach to control switched capacitor active power filter for reduction of harmonics. IEEE Trans. Ind. Electron. 2009, 56, 1477–1484. [Google Scholar] [CrossRef]

- Areerak, K.-L.; Areerak, K.-N. The comparison study of harmonic detection methods for shunt active power filters. World Acad. Sci. Eng. Technol. 2010, 4, 204–209. [Google Scholar]

- Sujitjorn, S.; Areerak, K.-L.; Kulworawanichpong, T. The dq axis with Fourier (dqF) method for harmonic identification. IEEE Trans. Power Deliv. 2007, 22, 737–739. [Google Scholar] [CrossRef]

- Firouzjah, K.G.; Sheikholeslami, A.; Karami-Mollaei, M.R.; Khaleghi, M. A new harmonics detection method for shunt active filter based on wavelet transform. J. Appl. Sci. Res. 2008, 4, 1561–1568. [Google Scholar]

- Tiyarachakun, S.; Areerak, K.; Areerak, K. Instantaneous power theory with Fourier and optimal predictive controller design for shunt active power filter. Model. Simul. Eng. 2014. [Google Scholar] [CrossRef]

- Jain, S.K.; Agrawal, P.; Gupta, H.O. Fuzzy logic controlled shunt active power filter for power quality improvement. IEEE Proc. Electr. Power Appl. 2002, 149, 317–328. [Google Scholar] [CrossRef]

- Mikkili, S.; Panda, A.K. Simulation and real-time implementation of shunt active filter id-iq control strategy for mitigation of harmonics with different fuzzy membership functions. IET Power Electron. 2012, 5, 1856–1872. [Google Scholar] [CrossRef]

- Afghoul, H.; Krim, F. Comparison between PI and fuzzy DPC control of a shunt active power filter. In Proceedings of the IEEE International Energy Conference and Exhibition (ENERGYCON), Florence, Italy, 9–12 September 2012; pp. 146–151. [Google Scholar]

- Zainuri, M.A.A.M.; Radzi, M.A.M.; Soh, A.C.; Mariun, N.; Rahim, N.A. DC-link capacitor voltage control for single-phase shunt active power filter with step size error cancellation in self-charging algorithm. IET Power Electron. 2016, 9, 323–335. [Google Scholar] [CrossRef]

- Kwan, K.H.; So, P.L.; Chu, Y.C. An output regulation-based unified power quality conditioner with kalman filters. IEEE Trans. Ind. Electron. 2012, 59, 4248–4262. [Google Scholar] [CrossRef]

- De Araujo Ribeiro, R.L.; De Oliveira Alves Rocha, T.; Maciel de Sousa, R.; dos Santos Junior, E.C.; Lima, A.M.N. A robust DC-link voltage control strategy to enhance the performance of shunt active power filters without harmonic detection schemes. IEEE Trans. Ind. Electron. 2015, 62, 803–813. [Google Scholar] [CrossRef]

- Mahanty, R. Indirect current controlled shunt active power filter for power quality improvement. Int. J. Electr. Power Energy Syst. 2014, 62, 441–449. [Google Scholar] [CrossRef]

- Mekri, F.; Mazari, B.; Machmoum, M. Control and optimization of shunt active power filter parameters by fuzzy logic. Can. J. Electr. Comput. Eng. 2006, 31, 127–134. [Google Scholar] [CrossRef]

- Suresh, Y.; Panda, A.K.; Suresh, M. Real-time implementation of adaptive fuzzy hysteresis-band current control technique for shunt active power filter. IET Power Electron. 2012, 5, 1188–1195. [Google Scholar] [CrossRef]

- Karuppanan, P.; Mahapatra, K.K. PI and fuzzy logic controllers for shunt active power filter—A Report. ISA Trans. 2012, 51, 163–169. [Google Scholar] [CrossRef]

- Karuppanan, P.; Mahapatra, K.K. PI, PID and fuzzy logic controller for reactive power and harmonic compensation. ACEEE Int. J. Electr. Power Eng. 2010, 1, 54–58. [Google Scholar]

- Suetake, M.; Silva, I.N.D.; Goedtel, A. Embedded DSP-based compact fuzzy system and its application for induction-motor v/f speed control. IEEE Trans. Ind. Electron. 2011, 58, 750–760. [Google Scholar] [CrossRef]

- Saad, S.; Zellouma, L. Fuzzy logic controller for three-level shunt active filter compensating harmonics and reactive power. Electr. Power Syst. Res. 2009, 79, 1337–1341. [Google Scholar] [CrossRef]

- Wu, Y.; Zhang, B.; Lu, J.; Du, K.-L. Fuzzy logic and neuro-fuzzy systems: A systematic introduction. Int. J. Artif. Intell. Expert Syst. 2011, 2, 47–80. [Google Scholar]

- Kumar, P.; Mahajan, A. Soft computing techniques for the control of an active power filter. IEEE Trans. Power Deliv. 2009, 24, 452–461. [Google Scholar] [CrossRef]

- Mikkili, S.; Panda, A.K. Types-1 and -2 fuzzy logic controllers-based shunt active filter id–iq control strategy with different fuzzy membership functions for power quality improvement using RTDS hardware. IET Power Electron. 2013, 6, 818–833. [Google Scholar] [CrossRef]

- Gupta, T.; Boudreaux, R.R.; Nelms, R.M.; Hung, J.Y. Implementation of a fuzzy controller for DC-DC converters using an inexpensive 8-b microcontroller. IEEE Trans. Ind. Electron. 1997, 44, 661–669. [Google Scholar] [CrossRef]

- Belaidi, R.; Haddouche, A.; Guendouz, H. Fuzzy logic controller based three-phase shunt active power filter for compensating harmonics and reactive power under unbalanced mains voltages. Energy Proced. 2012, 18, 560–570. [Google Scholar] [CrossRef]

- Deva, T.R.; Nair, N.K. ANN based control algorithm for harmonic elimination and power factor correction using shunt active filter. Int. J. Electr. Power Eng. 2007, 1, 152–157. [Google Scholar]

- Rahman, N.A.; Radzi, M.A.M.; Mariun, N.; Soh, A.C.; Rahim, N.A. Integration of dual intelligent algorithms in shunt active power filter. In Proceedings of the IEEE Conference on Clean Energy and Technology (CEAT), Langkawi, Malaysia, 18–20 November 2013; pp. 259–264. [Google Scholar]

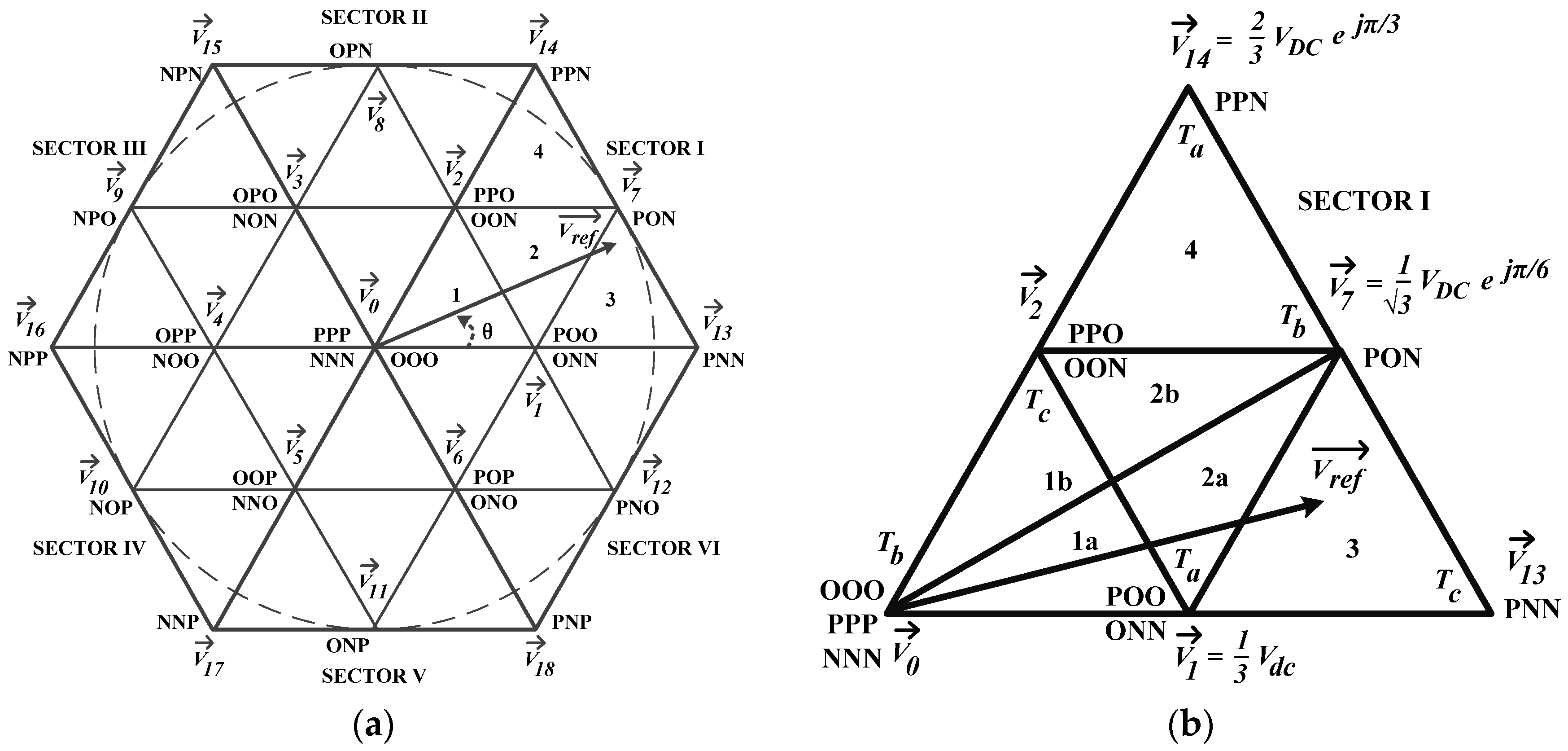

- Gupta, A.K.; Khambadkone, A.M. A space vector PWM scheme for multilevel inverters based on two-level space vector PWM. IEEE Trans. Ind. Electron. 2006, 53, 1631–1639. [Google Scholar] [CrossRef]

- Hu, H.; Yao, W.; Lu, Z. Design and implementation of three-level space vector PWM IP core for FPGAs. IEEE Trans. Ind. Electron. 2007, 22, 2234–2244. [Google Scholar] [CrossRef]

- Choi, U.-M.; Lee, K.-B. Space vector modulation strategy for neutral-point voltage balancing in three-level inverter systems. IET Power Electron. 2013, 6, 1390–1398. [Google Scholar] [CrossRef]

- Adel, M.; Zaid, S.; Mahgoub, O. Improved active power filter performance based on an indirect current control technique. J. Power Electron. 2011, 11, 931–937. [Google Scholar] [CrossRef]

- Babu, G.M. Simulation study of indirect current control technique for shunt active filter. Int. J. Eng. Res. Appl. 2013, 3, 831–851. [Google Scholar]

- Singh, B.N.; Singh, B.; Chandra, A.; Rastgoufard, P.; Al-Haddad, K. An improved control algorithm for active filters. IEEE Trans. Power Deliv. 2007, 22, 1009–1020. [Google Scholar] [CrossRef]

- Fei, J.; Li, T.; Wang, F.; Juan, W. A novel sliding mode control technique for indirect current controlled active power filter. Math. Probl. Eng. 2012. [Google Scholar] [CrossRef]

- Zhang, C.; Chen, Q.; Zhao, Y.; Li, D.; Xiong, Y. A novel active power filter for high-voltage power distribution systems application. IEEE Trans. Power Deliv. 2007, 22, 911–918. [Google Scholar] [CrossRef]

- Wu, L.; Zhuo, F.; Zhang, P.; Li, H.; Wang, Z. Study on the influence of supply-voltage fluctuation on shunt active power filter. IEEE Trans. Power Deliv. 2007, 22, 1743–1746. [Google Scholar] [CrossRef]

- Rahmani, S.; Al-Haddad, K.; Kanaan, H.Y. Two PWM techniques for single-phase shunt active power filters employing a direct current control strategy. IET Power Electron. 2008, 1, 376–385. [Google Scholar] [CrossRef]

- Dai, N.-Y.; Wong, M.-C.; Han, Y.-D. Application of a three-level NPC inverter as a three-phase four-wire power quality compensator by generalized 3dsvm. IEEE Trans. Power Electron. 2006, 21, 440–449. [Google Scholar] [CrossRef]

- Wu, B. High-Power Converters and AC Drives; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2006. [Google Scholar]

- Mondal, S.K.; Bose, B.K.; Oleschuk, V.; Pinto, J.O. Space vector pulsewidth modulation of three-level inverter extending operation into overmodulation region. IEEE Trans. Power Electron. 2003, 18, 604–611. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F. Neutral-point voltage deviation control for three-level inverter-based shunt active power filter with fuzzy-based dwell time allocation. IET Power Electron. 2016, 10, 429–441. [Google Scholar] [CrossRef]

- Choi, U.-M.; Lee, J.-S.; Lee, K.-B. New modulation strategy to balance the neutral-point voltage for three-level neutral-clamped inverter systems. IEEE Trans. Energy Convers. 2014, 29, 91–100. [Google Scholar] [CrossRef]

- Vahedi, H.; Sheikholeslami, A.; Bina, M.T.; Vahedi, M. Review and simulation of fixed and adaptive hysteresis current control considering switching losses and high-frequency harmonics. Adv. Power Electron. 2011. [Google Scholar] [CrossRef]

- Chang, G.W.; Shee, T.-C. A novel reference compensation current strategy for shunt active power filter control. IEEE Trans. Power Deliv. 2004, 19, 1751–1758. [Google Scholar] [CrossRef]

- Kale, M.; Ozdemir, E. An adaptive hysteresis band current controller for shunt active power filter. Electr. Power Syst. Res. 2005, 73, 113–119. [Google Scholar] [CrossRef]

- Padmanaban, P.A.; Marimuthu, M.R. Fuzzy logic based UPQC controller for compensating power quality problems. Aust. J. Basic Appl. Sci. 2012, 6, 167–168. [Google Scholar]

- Doǧan, H.; Akkaya, R. A control scheme employing an adaptive hysteresis current controller and an uncomplicated reference current generator for a single-phase shunt active power filter. Turk. J. Electr. Eng. Comput. Sci. 2014, 22, 1085–1097. [Google Scholar] [CrossRef]

- Hamasaki, S.; Kawamura, A. Improvement of current regulation of line-current-detection-type active filter based on deadbeat control. IEEE Trans. Ind. Appl. 2003, 39, 536–541. [Google Scholar] [CrossRef]

- Nishida, K.; Konishi, Y.; Nakaoka, M. Current control implementation with deadbeat algorithm for three-phase current-source active power filter. IEEE Proc. Electr. Power Appl. 2002, 149, 275–282. [Google Scholar] [CrossRef]

- Sawant, R.R.; Chandorkar, M.C. A multifunctional four-leg grid-connected compensator. IEEE Trans. Ind. Appl. 2009, 45, 249–259. [Google Scholar] [CrossRef]

- Odavic, M.; Biagini, V.; Zanchetta, P.; Sumner, M.; Degano, M. One-sample-period-ahead predictive current control for high-performance active shunt power filters. IET Power Electron. 2011, 4, 414–423. [Google Scholar] [CrossRef]

- Hamad, M.S.; Masoud, M.I.; Williams, B.W.; Finney, S. Medium voltage 12-pulse converter: AC side compensation using a shunt active power filter in a novel front end transformer configuration. IET Power Electron. 2012, 5, 1315–1323. [Google Scholar] [CrossRef]

- Massoud, A.M.; Finney, S.J.; Cruden, A.J.; Williams, B.W. Three-phase, three-wire, five-level cascaded shunt active filter for power conditioning, using two different space vector modulation techniques. IEEE Trans. Ind. Electron. 2007, 22, 2349–2361. [Google Scholar] [CrossRef]

- Chauhan, S.K.; Shah, M.C.; Tiwari, R.R.; Tekwani, P.N. Analysis, design and digital implementation of a shunt active power filter with different schemes of reference current generation. IET Power Electron. 2014, 7, 627–639. [Google Scholar] [CrossRef]

- Salim, C.; Toufik, B.M. Three-level (NPC) shunt active power filter performances based on fuzzy controller for harmonic currents compensation under non-ideal voltage conditions. Int. J. Electr. Eng. Inform. 2014, 6, 342–358. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F. A self-tuning filter-based adaptive linear neuron approach for operation of three-level inverter-based shunt active power filters under non-ideal source voltage conditions. Energies 2017, 10, 667. [Google Scholar] [CrossRef]

- Chang, G.W. A new approach for optimal shunt active power filter control considering alternative performance indices. IEEE Trans. Power Deliv. 2006, 21, 406–413. [Google Scholar] [CrossRef]

- Chang, G.W.; Yeh, C.-M.; Chen, W.-C. Meeting IEEE-519 current harmonics and power factor constraints with a three-phase three-wire active power filter under distorted source voltages. IEEE Trans. Power Deliv. 2006, 21, 1648–1654. [Google Scholar] [CrossRef]

- Dinh, N.D.; Tuyen, N.D.; Fujita, G.; Funabashi, T. Adaptive notch filter solution under unbalanced and/or distorted point of common coupling voltage for three-phase four-wire shunt active power filter with sinusoidal utility current strategy. IET Gener. Transm. Distrib. 2015, 9, 1580–1596. [Google Scholar] [CrossRef]

- Abdulsalam, M.; Poure, P.; Karimi, S.; Saadate, S. New digital reference current generation for shunt active power filter under distorted voltage conditions. Electr. Power Syst. Res. 2009, 79, 759–765. [Google Scholar] [CrossRef]

- Hoon, Y.; Radzi, M.A.M.; Hassan, M.K.; Mailah, N.F. A refined self-tuning filter-based instantaneous power theory algorithm for indirect current controlled three-level inverter-based shunt active power filters under non-sinusoidal source voltage conditions. Energies 2017, 10, 277. [Google Scholar] [CrossRef]

- Biricik, S.; Redif, S.; Özerdem, Ö.C.; Khadem, S.K.; Basu, M. Real-time control of shunt active power filter under distorted grid voltage and unbalanced load condition using self-tuning filter. IET Power Electron. 2014, 7, 1895–1905. [Google Scholar] [CrossRef]

- Campanhol, L.B.G.; Silva, S.A.O.; Goedtel, A. Application of shunt active power filter for harmonic reduction and reactive power compensation in three-phase four-wire systems. IET Power Electron. 2014, 7, 2825–2836. [Google Scholar] [CrossRef]

- Lu, Z.-G.; Zhao, L.-L.; Zhu, W.-P.; Wu, C.-J.; Qin, Y.-S. Research on cascaded three-phase-bridge multilevel converter based on CPS-PWM. IET Power Electron. 2013, 6, 1088–1099. [Google Scholar] [CrossRef]

- Teichmann, R.; Bernet, S. A comparison of three-level converters versus two-level converters for low-voltage drives, traction, and utility applications. IEEE Trans. Ind. Electron. 2005, 41, 855–865. [Google Scholar] [CrossRef]

- De, S.; Banerjee, D.; Siva Kumar, K.; Gopakumar, K.; Ramchand, R.; Patel, C. Multilevel inverters for low-power application. IET Power Electron. 2011, 4, 384–392. [Google Scholar] [CrossRef]

- Akagi, H.; Inoue, S.; Yoshii, T. Control and performance of a transformerless cascade PWM STATCOM with star configuration. IEEE Trans. Ind. Appl. 2007, 43, 1041–1049. [Google Scholar] [CrossRef]

- Chen, Z.; Luo, Y.; Chen, M. Control and performance of a cascaded shunt active power filter for aircraft electric power system. IEEE Trans. Ind. Electron. 2012, 59, 3614–3623. [Google Scholar] [CrossRef]

- Mouton, H.D.T. Natural balancing of three-level neutral-point-clamped pwm inverters. IEEE Trans. Ind. Electron. 2002, 49, 1017–1025. [Google Scholar] [CrossRef]

- Soto, D.; Green, T.C. A comparison of high-power converter topologies for the implementation of FACTS controllers. IEEE Trans. Ind. Electron. 2002, 49, 1072–1080. [Google Scholar] [CrossRef] [Green Version]

- Lin, B.-R.; Huang, C.-H. Implementation of a three-phase capacitor clamped active power filter under unbalanced condition. IEEE Trans. Ind. Electron. 2006, 53, 1621–1630. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Pérez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Masaoud, A.; Ping, H.W.; Mekhilef, S.; Belkamel, H. Highly efficient three-phase three-level multilevel inverter employing different commutation strategies. Turk. J. Electr. Eng. Comput. Sci. 2016, 24, 76–87. [Google Scholar] [CrossRef]

- Maswood, A.I.; Gabriel, O.H.P.; Ammar, E.A. Comparative study of multilevel inverters under unbalanced voltage in a single DC link. IET Power Electron. 2013, 6, 1530–1543. [Google Scholar] [CrossRef]

- Shukla, A.; Ghosh, A.; Joshi, A. Hysteresis current control operation of flying capacitor multilevel inverter and its application in shunt compensation of distribution systems. IEEE Trans. Power Deliv. 2007, 22, 396–405. [Google Scholar] [CrossRef] [Green Version]

- Choi, U.-M.; Lee, K.-B. Neutral-point voltage balancing method for three-level inverter systems with a time-offset estimation scheme. J. Power Electron. 2013, 13, 243–249. [Google Scholar] [CrossRef]

- Lee, C.K.; Hui, S.Y.R.; Chung, S.-H.; Shrivastava, Y. A randomized voltage vector switching scheme for three-level power inverters. IEEE Trans. Power Electron. 2002, 17, 94–100. [Google Scholar] [CrossRef]

- Bhat, A.H.; Langer, N.; Sharma, D.; Agrawal, P. Capacitor voltage balancing of a three-phase neutral-point clamped bi-directional rectifier using optimised switching sequences. IET Power Electron. 2013, 6, 1209–1219. [Google Scholar] [CrossRef]

- Langer, N.; Bhat, A.H.; Agrawal, P. Neural-network-based space-vector pulse-width modulation for capacitor voltage balancing of three-phase three-level improved power quality converter. IET Power Electron. 2014, 7, 973–983. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Ortega, J.D.; Bordonau, J.; Beristain, J.A.; Rocabert, J. Closed-loop control of a three-phase neutral-point-clamped inverter using an optimized virtual-vector-based pulsewidth modulation. IEEE Trans. Ind. Electron. 2008, 55, 2061–2071. [Google Scholar] [CrossRef]

- Bhalodi, K.H.; Agarwal, P. Space vector modulation with DC-link voltage balancing control for three-level inverters. ACEEE Int. J. Commun. 2010, 1, 14–18. [Google Scholar]

- Abdelkrim, T.; Berkouk, E.M.; Benkhelifa, A.; Benamrane, K.; Benslimane, T. Neutral point potential balancing algorithm for autonomous three-level shunt active power filter. J. Electr. Control Eng. 2012, 2, 20–26. [Google Scholar]

- Raj, P.H.; Maswood, A.I.; Ooi, G.H.P.; Lim, Z. Voltage balancing technique in a space vector modulated 5-level multiple-pole multilevel diode clamped inverter. IET Power Electron. 2015, 8, 1263–1272. [Google Scholar] [CrossRef]

- Lin, L.; Zou, Y.; Wang, Z.; Jin, H. Modeling and control of neutral-point voltage balancing problem in three-level NPC PWM inverters. In Proceedings of the IEEE 36th Conference in Power Electronics Specialists (PESC), Recife, Brazil, 12–16 June 2005; pp. 861–866. [Google Scholar]

| Characteristics | Cascaded H-Bridge [102,103] | Neutral-Point Diode Clamped [100,103,104] | Flying Capacitor [18,104,105] | |||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Level | 3 | 5 | n | 3 | 5 | n | 3 | 5 | n | |

| Number of components | Switches with freewheeling diodes | 12 | 24 | 6 (n − 1) | 12 | 24 | 6 (n − 1) | 12 | 24 | 6 (n − 1) |

| DC-link capacitors | 3 | 6 | 3 (n − 1)/2 | 2 | 4 | (n − 1) | 2 | 4 | (n − 1) | |

| Clamping diodes | Not applicable | 6 | 36 | 3 (n − 1)(n − 2) | Not applicable | |||||

| Clamping capacitors | Not applicable | 3 | 18 | 3 (n − 1)(n − 2)/2 | ||||||

| Advantages | Simple structure and control due to its modularity | Robust structure and requires the least amount of DC-link capacitors (less voltage imbalance problems) | Phase redundancy is available to achieve voltage balancing of DC-link capacitors | |||||||

| Limitations | Limited applications due to requirement of separate DC sources | Amount of clamping diodes becomes excessively high with the increase in number of level | Bulky size, high development cost, and complex voltage balancing and switching control algorithm | |||||||

| Switching State | Inverter Switching Status (Phase A) | Terminal Voltage | |||

|---|---|---|---|---|---|

| N | Off | Off | On | On | /2 |

| O | Off | On | On | Off | 0 |

| P | On | On | Off | Off | /2 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hoon, Y.; Mohd Radzi, M.A.; Hassan, M.K.; Mailah, N.F. Control Algorithms of Shunt Active Power Filter for Harmonics Mitigation: A Review. Energies 2017, 10, 2038. https://doi.org/10.3390/en10122038

Hoon Y, Mohd Radzi MA, Hassan MK, Mailah NF. Control Algorithms of Shunt Active Power Filter for Harmonics Mitigation: A Review. Energies. 2017; 10(12):2038. https://doi.org/10.3390/en10122038

Chicago/Turabian StyleHoon, Yap, Mohd Amran Mohd Radzi, Mohd Khair Hassan, and Nashiren Farzilah Mailah. 2017. "Control Algorithms of Shunt Active Power Filter for Harmonics Mitigation: A Review" Energies 10, no. 12: 2038. https://doi.org/10.3390/en10122038