Control of a Three-Phase to Single-Phase Back-to-Back Converter for Electrical Resistance Seam Welding Systems

Abstract

:1. Introduction

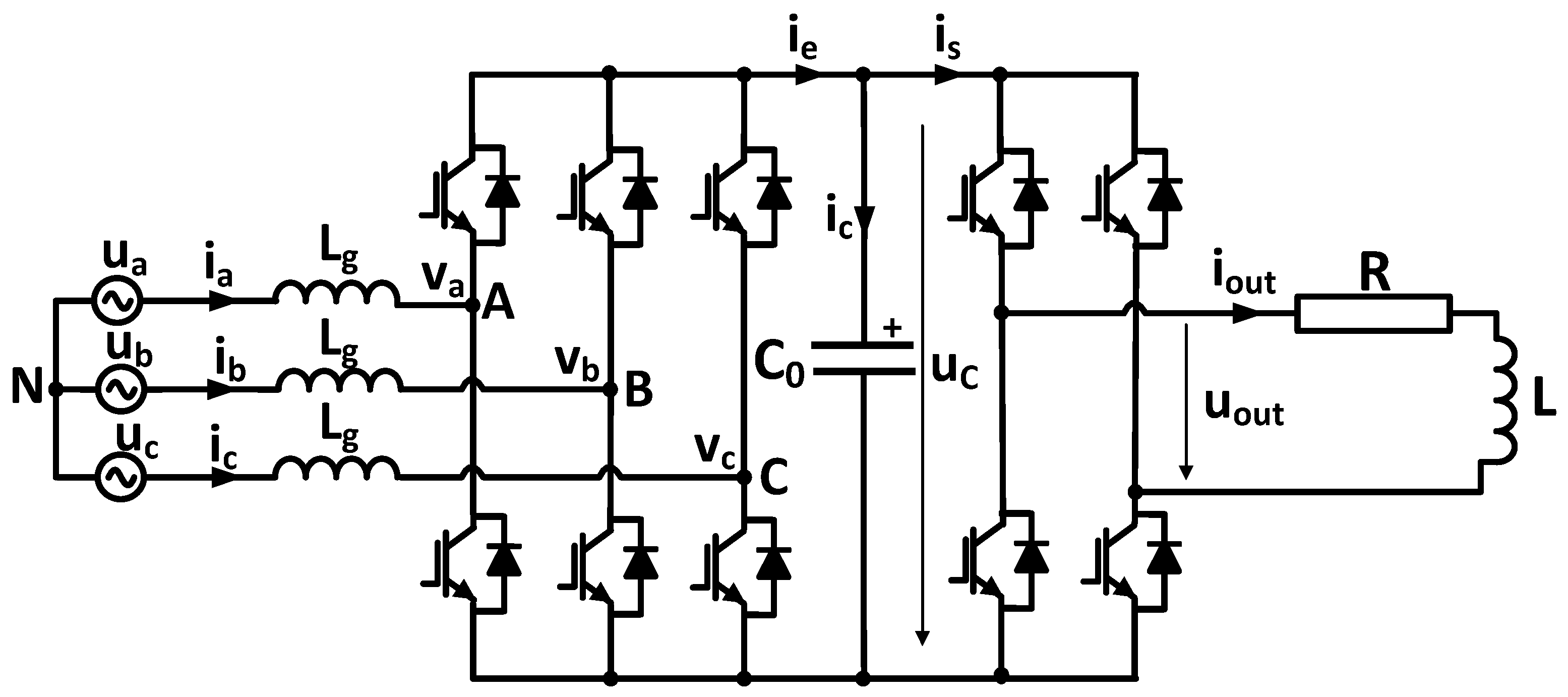

2. System Description and Analysis

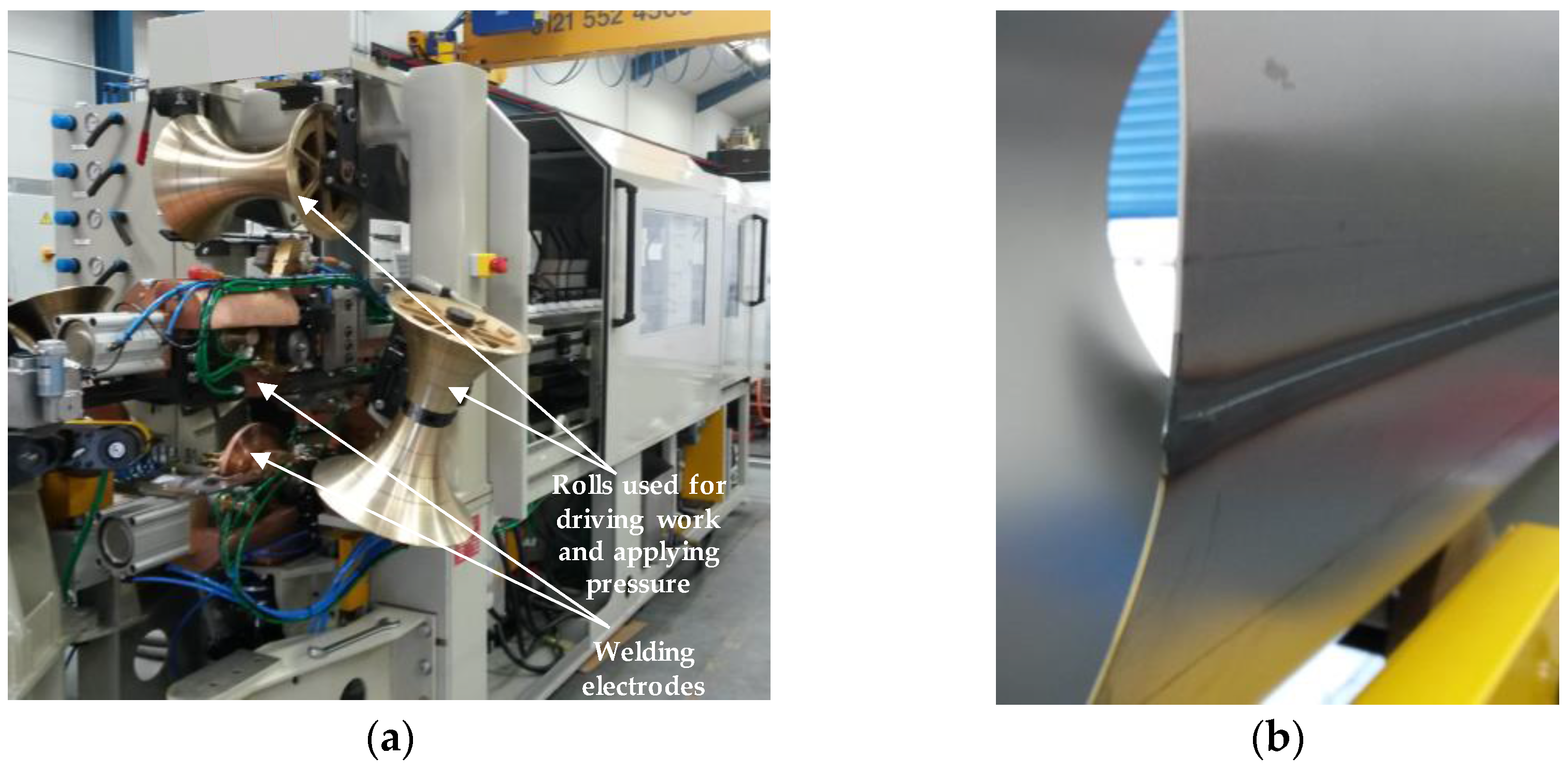

2.1. System Description

2.2. Mathematical Description of the System

2.2.1. Pulse Width Modulated Rectifier

2.2.2. Power Pulsation Compensation

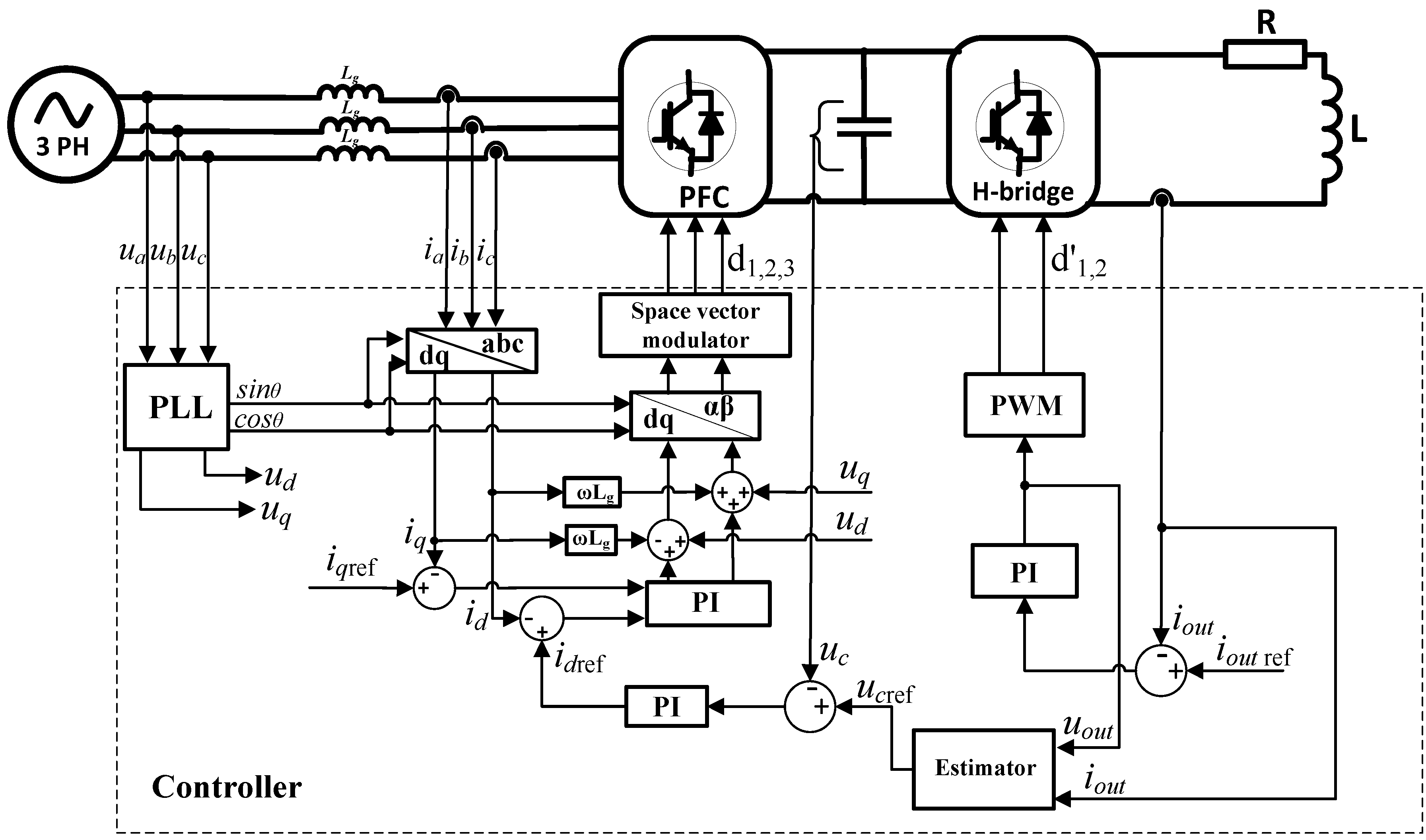

3. Control Strategy

3.1. Unity Power Factor Formulation

3.2. Control of the Output Current

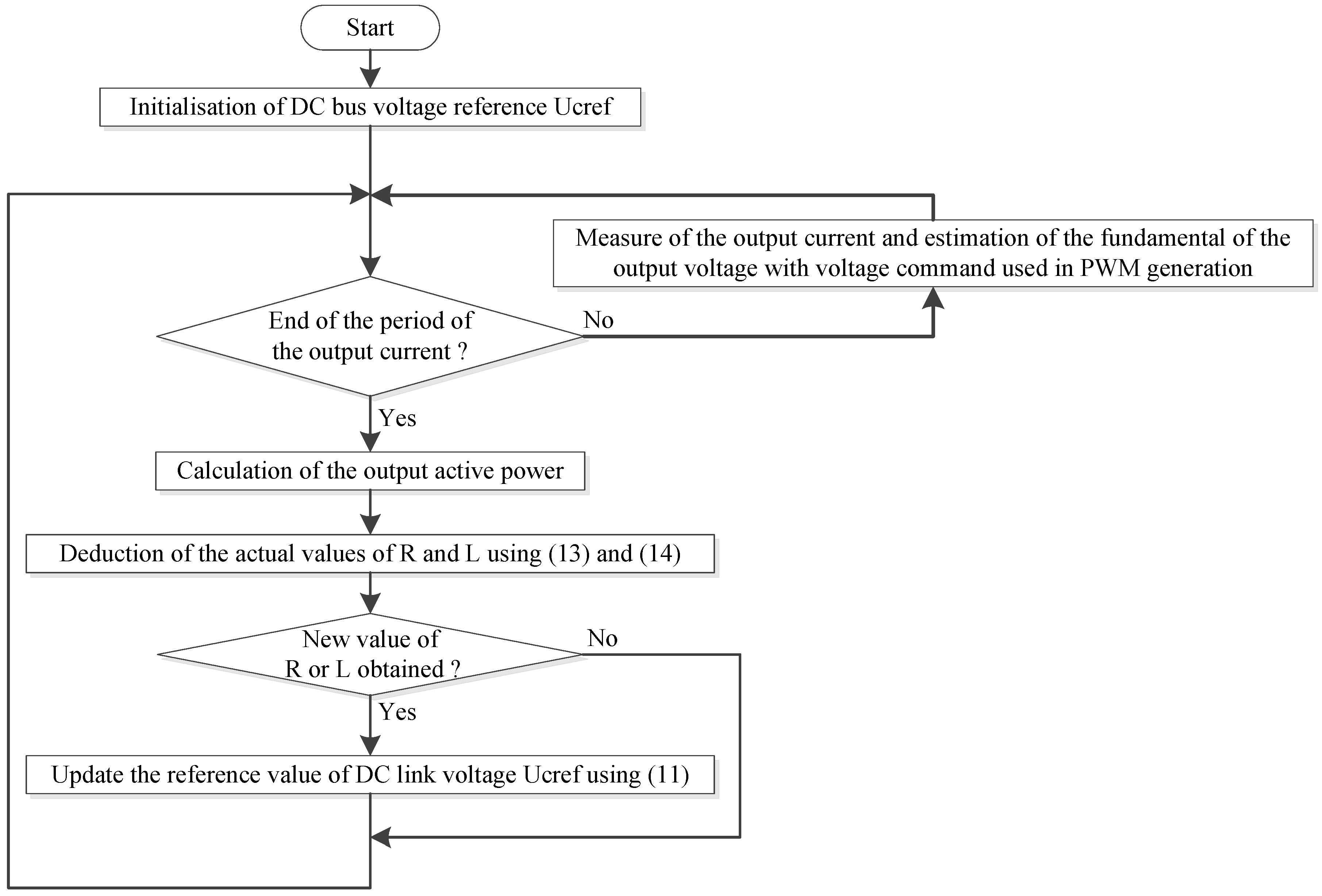

3.3. Proposed Estimation of Equivalent Load Parameter’s Values

3.4. Tuning of the Controllers

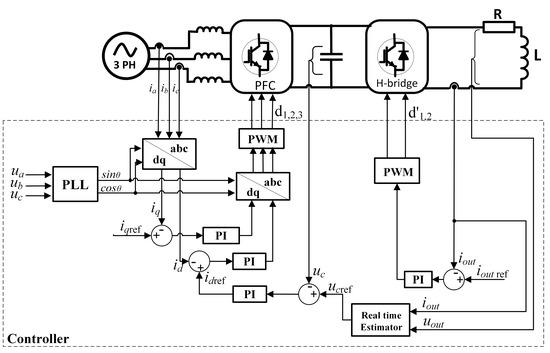

3.5. Overview of the Control System

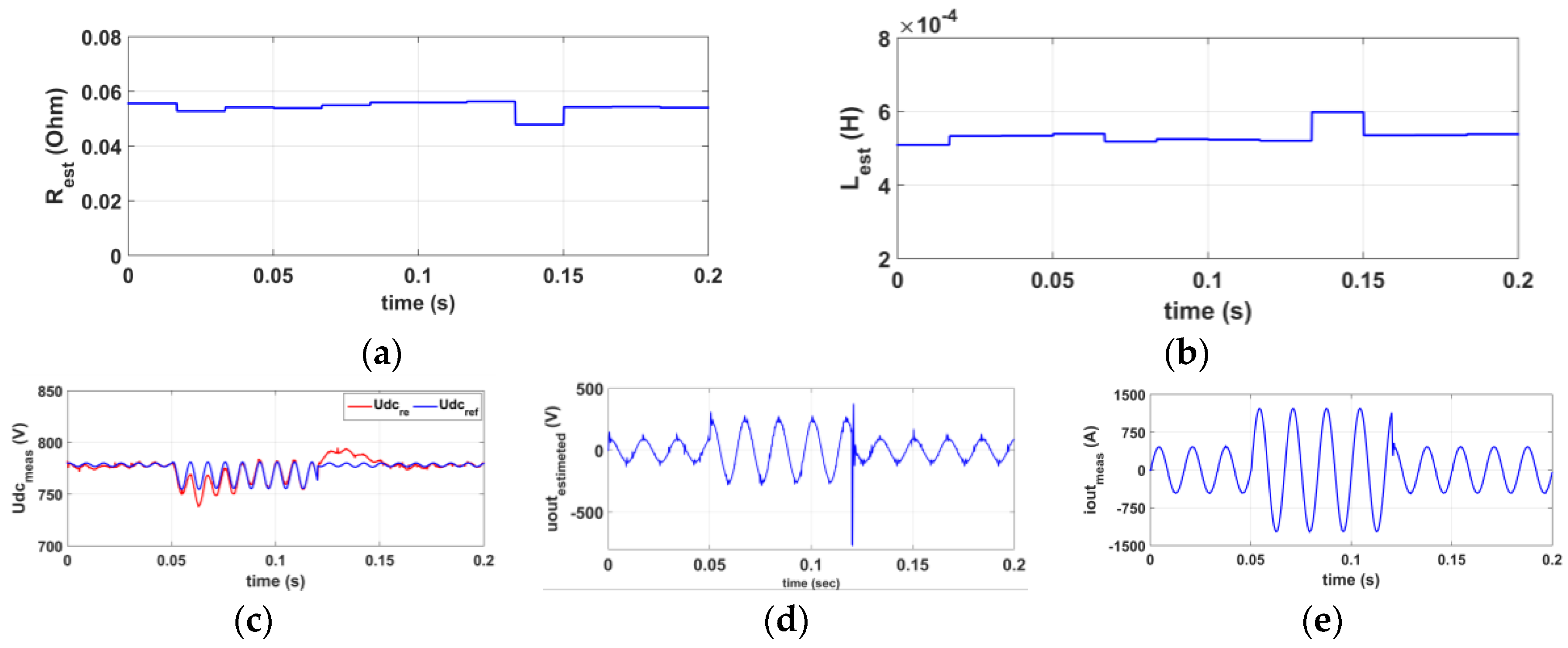

3.6. Simulations Results

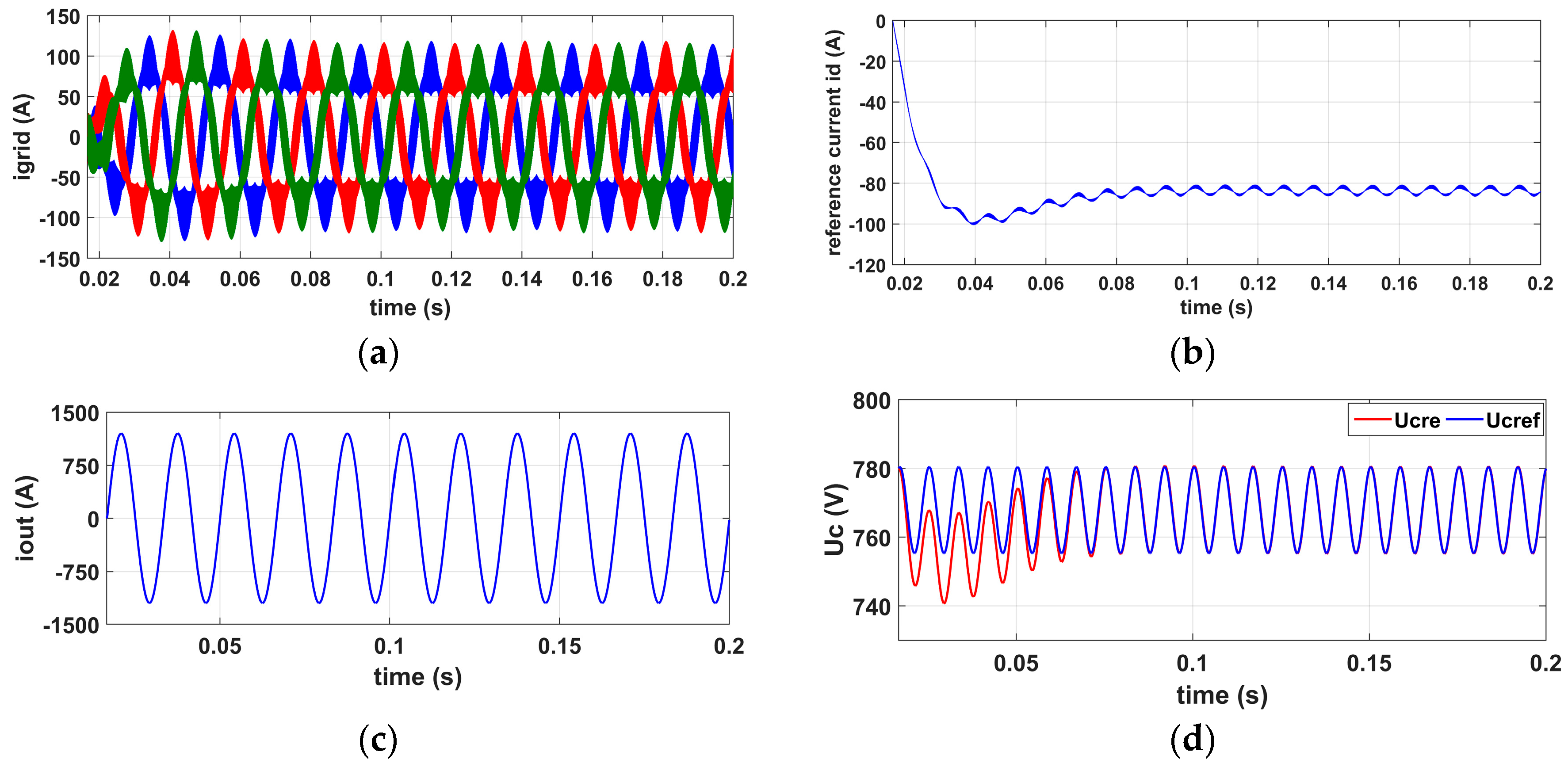

3.6.1. Constant Load Simulations

3.6.2. Step Change in the Output Current Reference

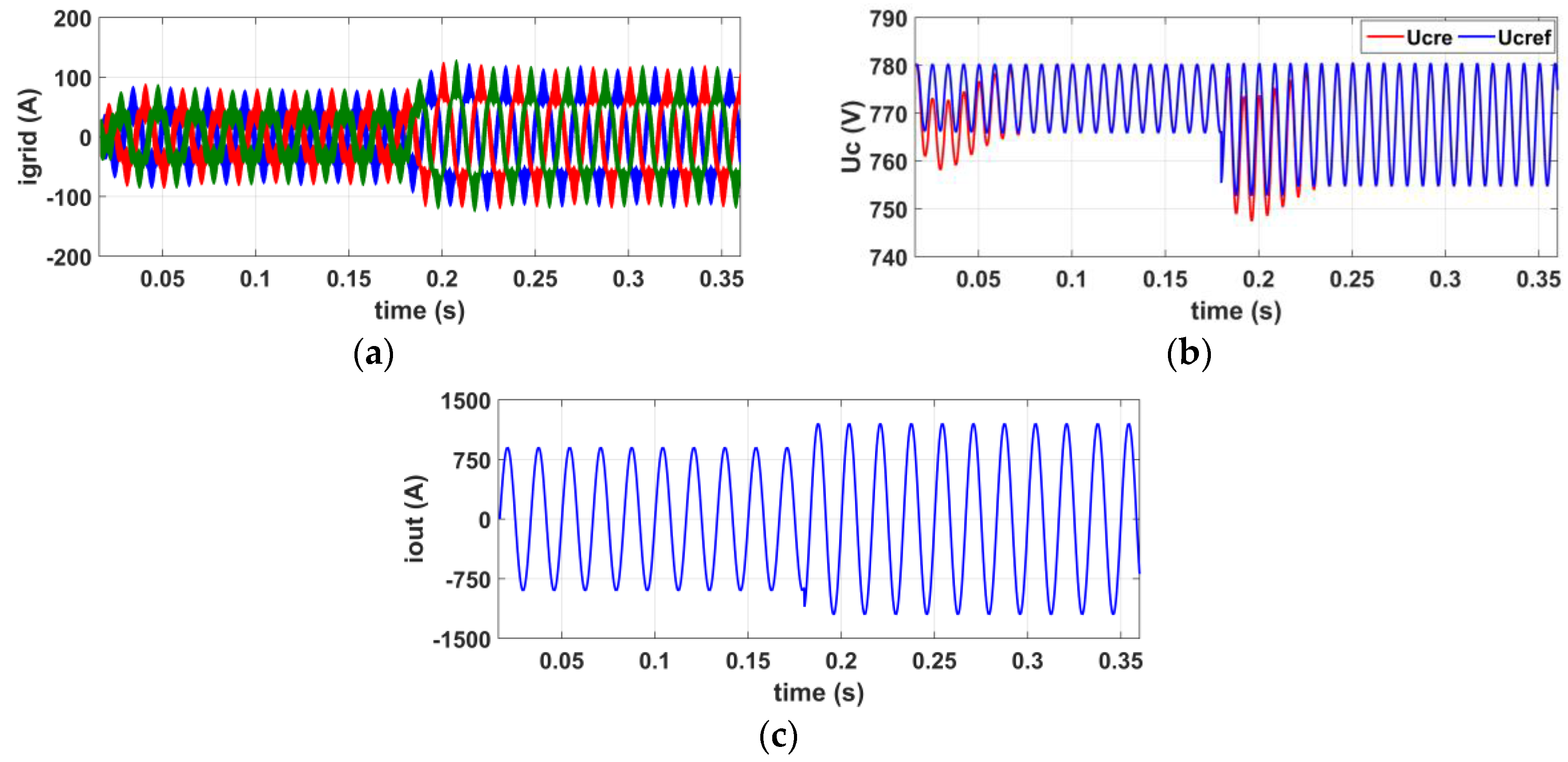

3.6.3. Step Change of Output Parameter Values

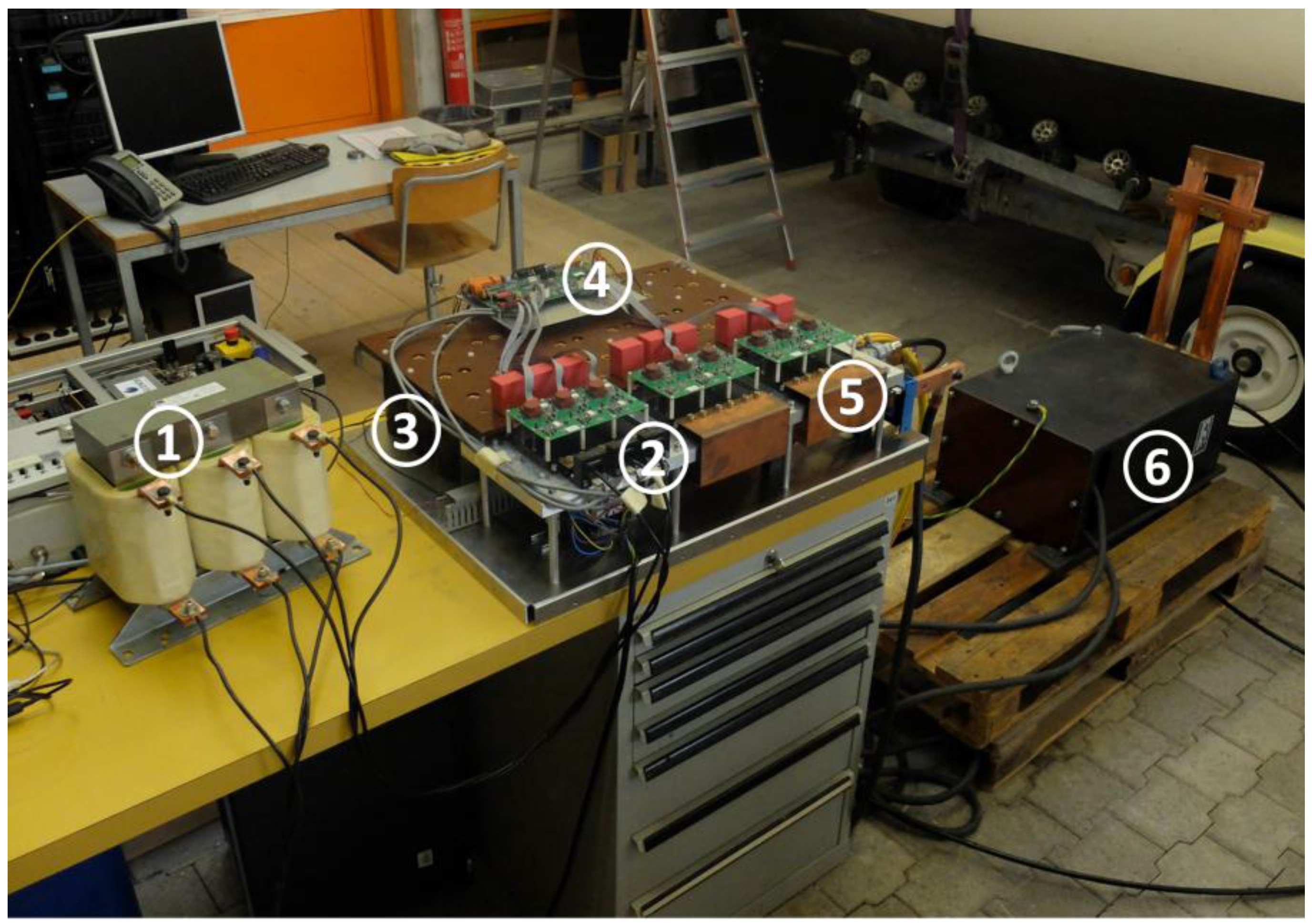

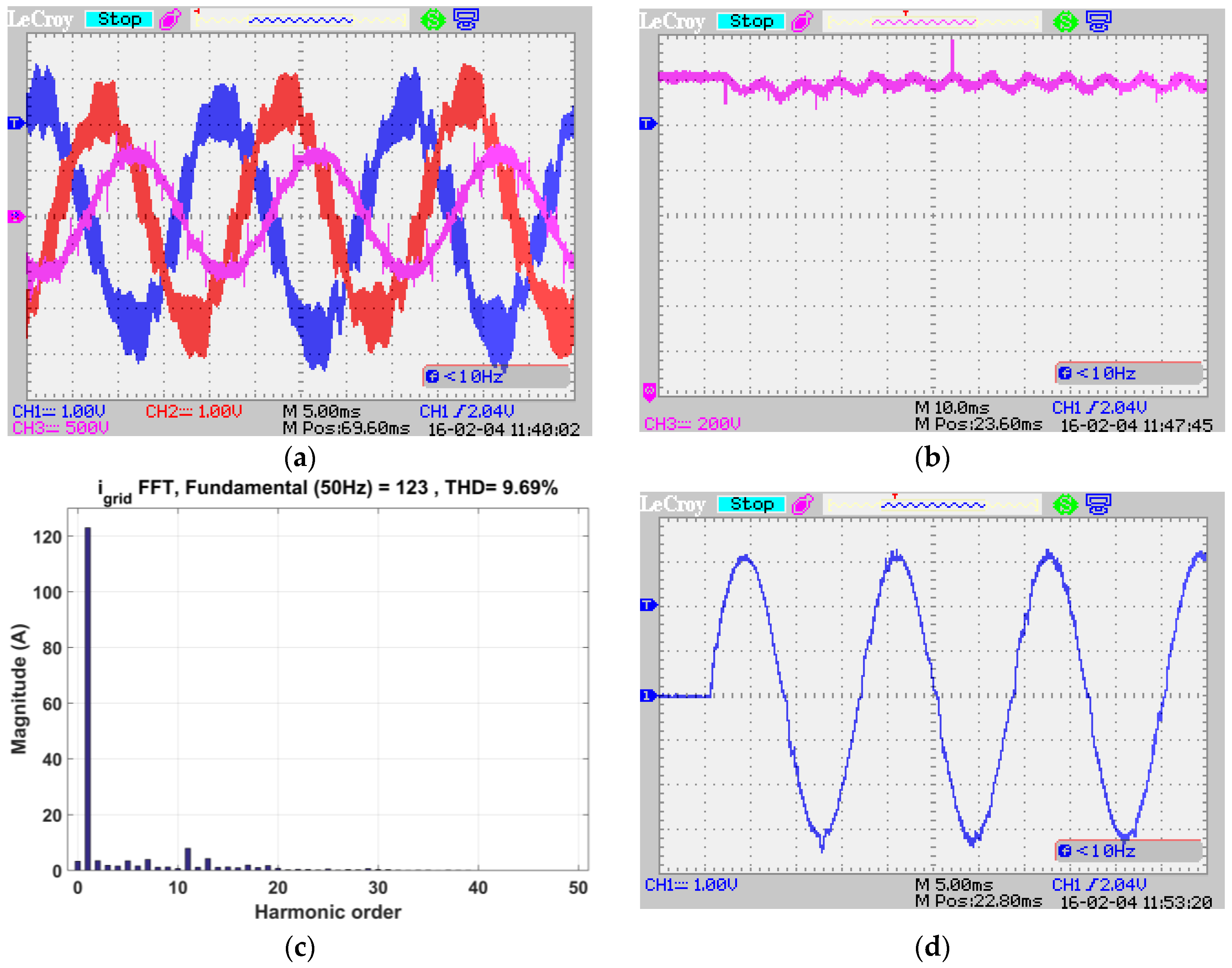

4. Experimental Results

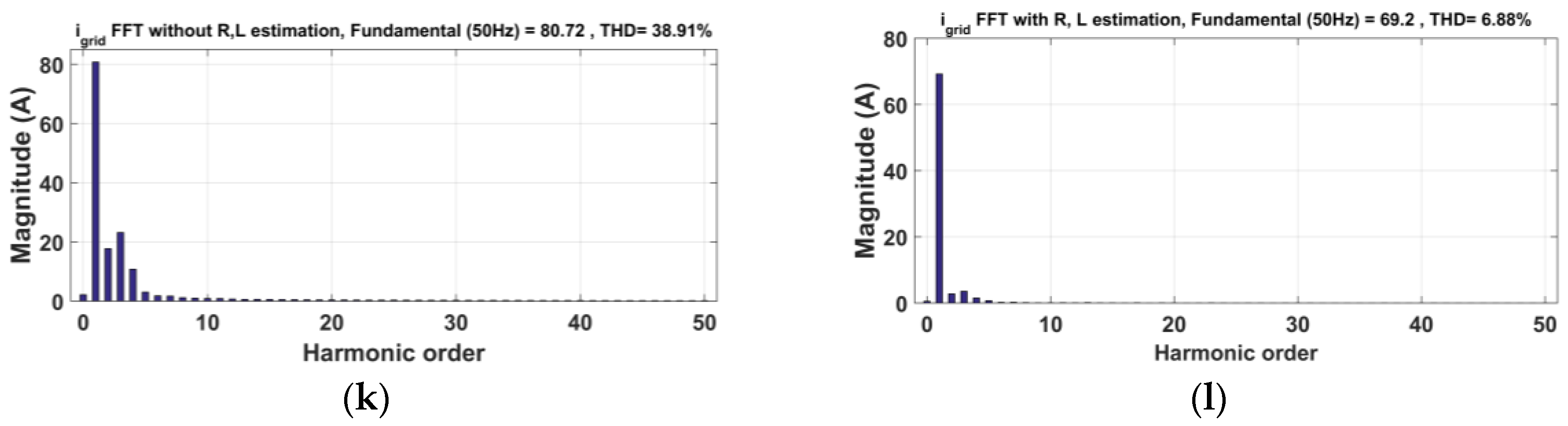

4.1. Tests on a Dummy Load

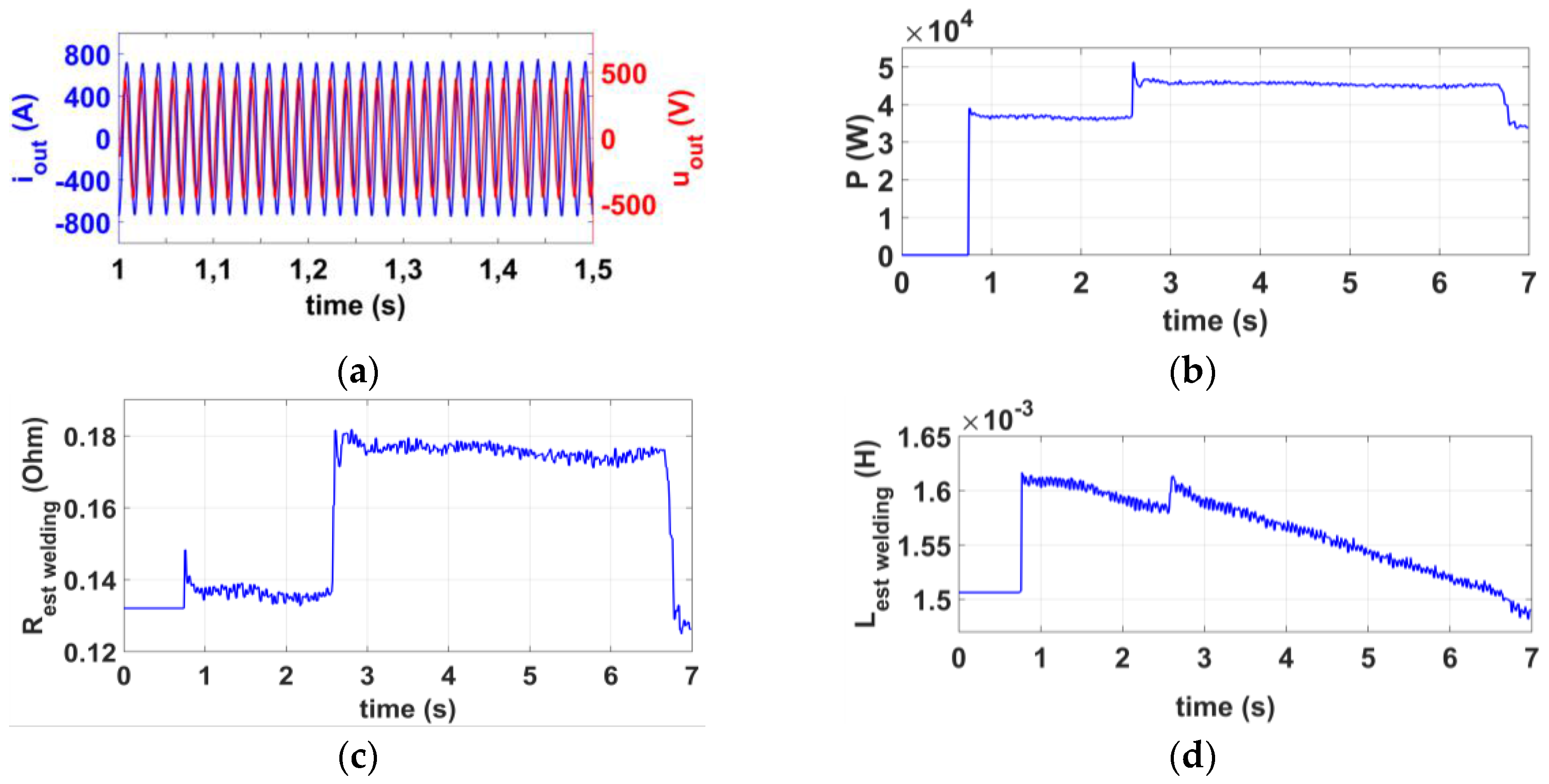

4.2. Welding Test with the Converter

5. Conclusions

Author Contributions

Conflicts of Interest

References

- Zhang, H.; Senkara, J. Welding metallurgy. In Resistance Welding Fundamentals and Applications; Taylor & Francis Group: Boca Raton, FL, USA, 2006; pp. 1–16. [Google Scholar]

- Weman, K. Pressure welding methods. In Welding Process Handbook; Woodhead Publishing Limited: Cambridge, UK, 2003; pp. 87–91. [Google Scholar]

- Mathers, G. Resistance welding processes. In The Welding of Aluminium and Its Alloys; Woodhead Publishing Limited: Cambridge, UK, 2002; pp. 166–180. [Google Scholar]

- Winkler, T.; Doebbelin, R.; Lindemann, A. Mitigation of conducted emission of power electronic resistance welding equipment. In Proceedings of the Power Electronics and Motion Control Conference (EPE‑PEMC), Portoroz, Slovenia, 30 August–1 September 2006; pp. 450–455.

- International Electrotechnical Commission. Resistance Welding Equipment. Electromagnetic Compatibility (EMC) Requirements; IEC 62135-2; International Electrotechnical Commission: Geneva, Switzerland, 2015. [Google Scholar]

- Malesani, L.; Rossetto, L.; Tenti, P.; Tomasin, P. AC/DC/AC PWM converter with reduced energy storage in the DC link. IEEE Trans. Ind. Appl. 1995, 31, 287–292. [Google Scholar] [CrossRef]

- Dos Santos, E.C.; Da Silva, E.R. Advanced Power Electronics Converters: PWM Converters Processing AC Voltages; Wiley-IEEE Press: New York, NY, USA, 2014. [Google Scholar]

- Hwang, J.G.; Winkelnkemper, M.; Lehn, P.W. Control of AC-DC-AC converters with minimized DC link capacitance under grid distortion. In Proceedings of the IEEE International Symposium on Industrial Electronics, Montreal, QC, Canada, 9–13 July 2006; pp. 1217–1222.

- Friedli, T.; Kolar, J.W.; Rodriguez, J.; Wheeler, P.W. Comparative evaluation of three-phase AC–AC matrix converter and voltage DC-Link back-to-back converter systems. IEEE Trans. Ind. Electron. 2012, 59, 4487–4510. [Google Scholar] [CrossRef]

- Shen, L.; Bozhko, S.; Asher, G.; Patel, C.; Wheeler, P. Active DC-link capacitor harmonic current reduction in two-level back-to-back converter. IEEE Trans. Power Electron. Electron. 2016, 31, 6947–6954. [Google Scholar] [CrossRef]

- Kazmierkowski, M.P.; Krishnan, R.; Blaabjerg, F. Control of three-phase PWM rectifiers. In Control in Power Electronics: Selected Problems; Academic Press: San Diego, CA, USA, 2002; pp. 419–459. [Google Scholar]

- Salem, M. Control and Power Supply for Resistance Spot Welding (RSW). Ph.D. Thesis, Western Ontario University, London, ON, Canada, 2011. [Google Scholar]

- Ohnuma, Y.; Itoh, J. A control method for a single-to-three-phase power converter with an active buffer and a charge circuit. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 1801–1807.

- Harb, S.; Mirjafari, M.; Balog, R.S. Ripple-port module-integrated inverter for grid-connected PV applications. IEEE Trans. Ind. Appl. 2013, 49, 2692–2698. [Google Scholar] [CrossRef]

- Hu, W.; Chen, Z.; Wang, Y.; Wang, Z. Flicker mitigation by active power control of variable-speed wind turbines with full-scale back-to-back power converters. IEEE Trans. Energy Convers. 2009, 24, 24–640. [Google Scholar]

- Kolar, J.W.; Friedli, T. The essence of three-phase PFC rectifier systems—Part I. IEEE Trans. Power Electron. 2013, 28, 176–198. [Google Scholar] [CrossRef]

- Åström, K.J.; Hägglund, T. Controller design. In PID Controllers: Theory, Design, and Tuning, 2nd ed.; Instrument Society of America: Research Triangle Park, NC, USA, 1995; pp. 120–197. [Google Scholar]

- Kaura, V.; Blasko, V. Operation of a phase locked loop system under distorted utility conditions. IEEE Trans. Ind. Appl. 1997, 33, 58–63. [Google Scholar] [CrossRef]

- Electrical Engineering Software PLEXIM. Available online: http://www.plexim.com (assessed on 20 November 2016).

- IGBT Modules—6MBI450V-120-50. Available online: http://www.fujielectric-europe.com/downloads/6MBI450V-120-50_1734379.PDF (assessed on 20 November 2016).

- TMS320F28335 Delfino Microcontroller. Available online: http://www.ti.com/product/TMS320F28335 (assessed on 20 November 2016).

| Control Section | Open Loop Transfer Function | Tn | Ti | Criterion Used |

|---|---|---|---|---|

| Grid current control loop | Symmetrical optimum | |||

| DC link voltage control loop | Symmetrical optimum | |||

| Output current control loop | Modulus optimum |

| Symbol | Quantity | Value |

|---|---|---|

| Ugrid | Effective value of the grid voltage | 230 V |

| C0 | DC-link Capacitor tank | 19.8 mF |

| R | Theoretical load resistance | 56 mΩ |

| L | Theoretical load inductance | 512 µH |

| fs_PFC | Switching frequency of the PFC rectifier | 10 kHz |

| fs_INV | Switching frequency of the inverter | 5 kHz |

| fech | Sampling frequency | 10 kHz |

| fgrid | Grid frequency | 50 Hz |

| Iout | Effective value of the output reference current | 848 A |

| fout | Output frequency | 60 Hz |

| Lg | Grid coupling inductance | 123 µH |

| Ucnom | Nominal DC bus voltage | 780 V |

© 2017 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kissling, S.; Talon Louokdom, E.; Biya-Motto, F.; Essimbi Zobo, B.; Carpita, M. Control of a Three-Phase to Single-Phase Back-to-Back Converter for Electrical Resistance Seam Welding Systems. Energies 2017, 10, 133. https://doi.org/10.3390/en10010133

Kissling S, Talon Louokdom E, Biya-Motto F, Essimbi Zobo B, Carpita M. Control of a Three-Phase to Single-Phase Back-to-Back Converter for Electrical Resistance Seam Welding Systems. Energies. 2017; 10(1):133. https://doi.org/10.3390/en10010133

Chicago/Turabian StyleKissling, Simon, Elie Talon Louokdom, Frédéric Biya-Motto, Bernard Essimbi Zobo, and Mauro Carpita. 2017. "Control of a Three-Phase to Single-Phase Back-to-Back Converter for Electrical Resistance Seam Welding Systems" Energies 10, no. 1: 133. https://doi.org/10.3390/en10010133