Finite Element Analysis of Film Stack Architecture for Complementary Metal-Oxide–Semiconductor Image Sensors

Abstract

:1. Introduction

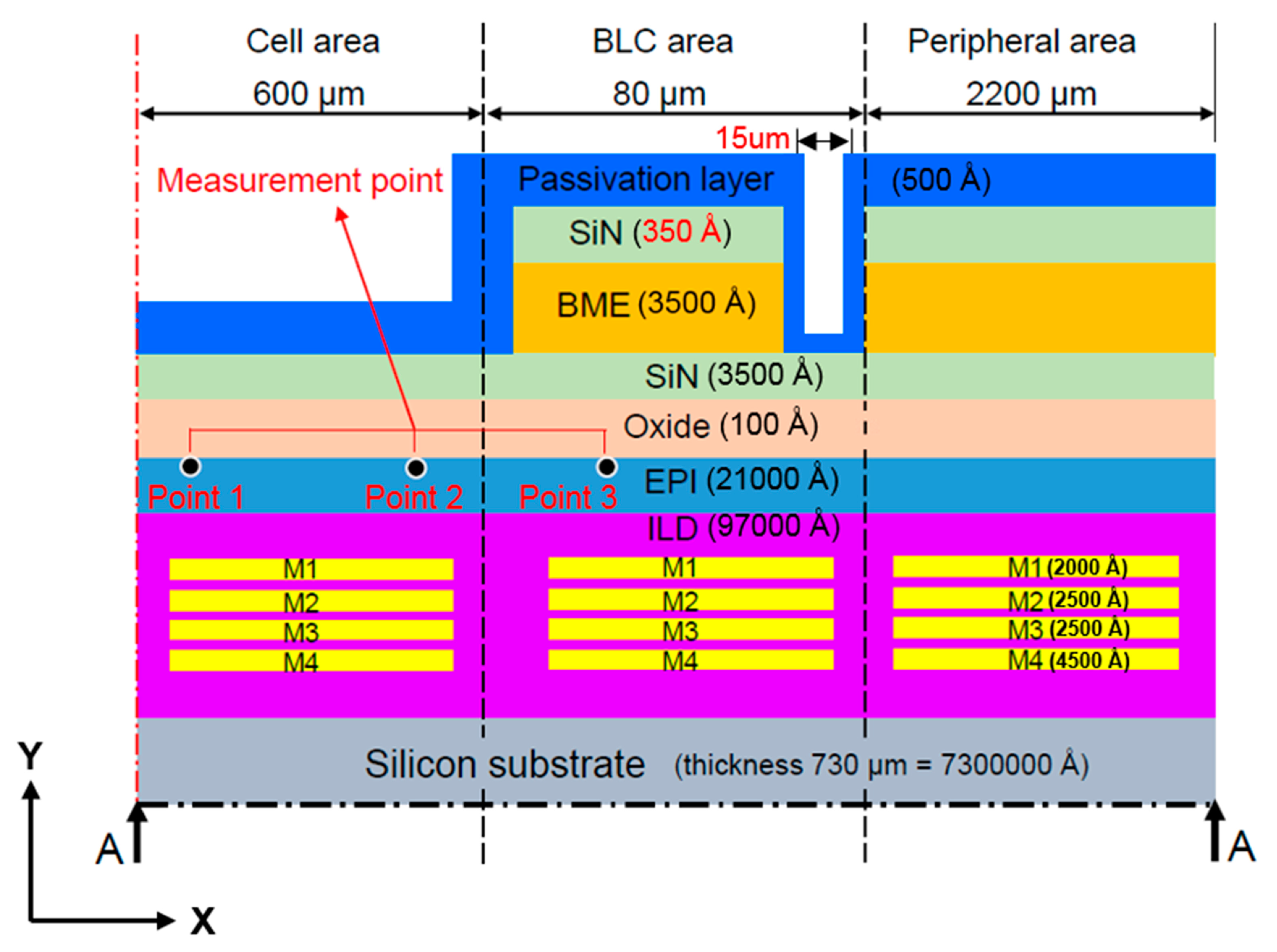

2. Analysis Method

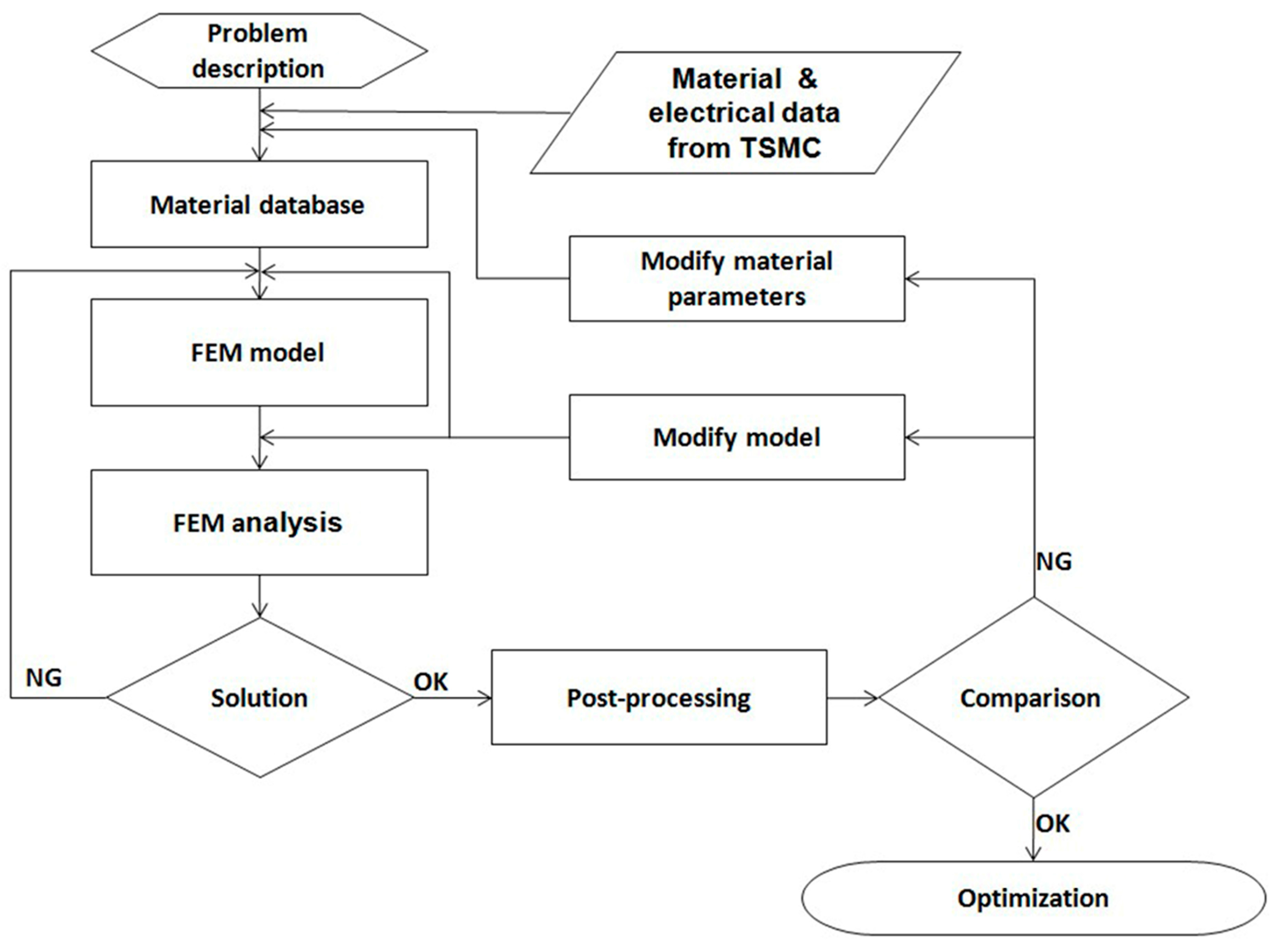

2.1. Finite Element Analysis

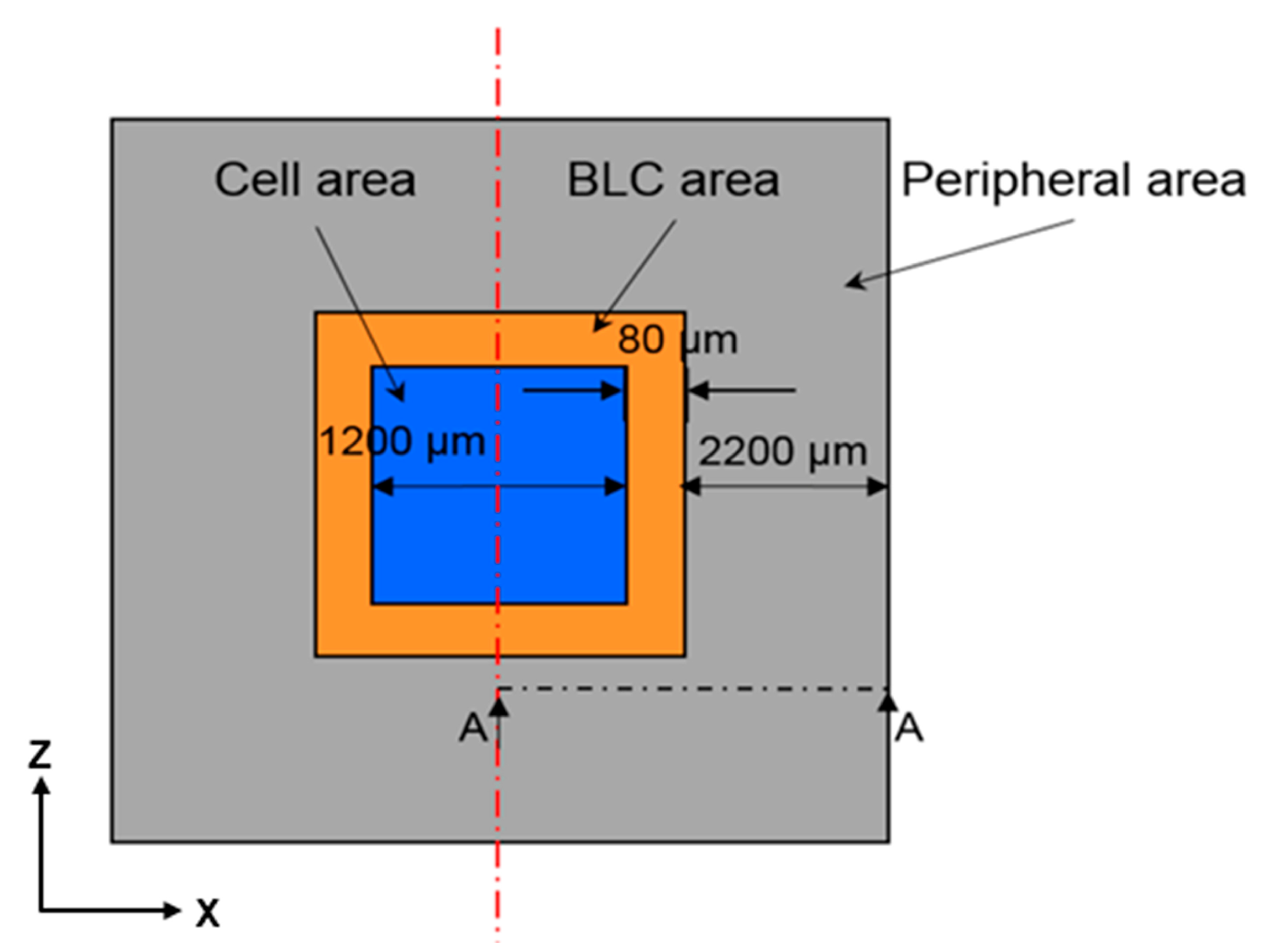

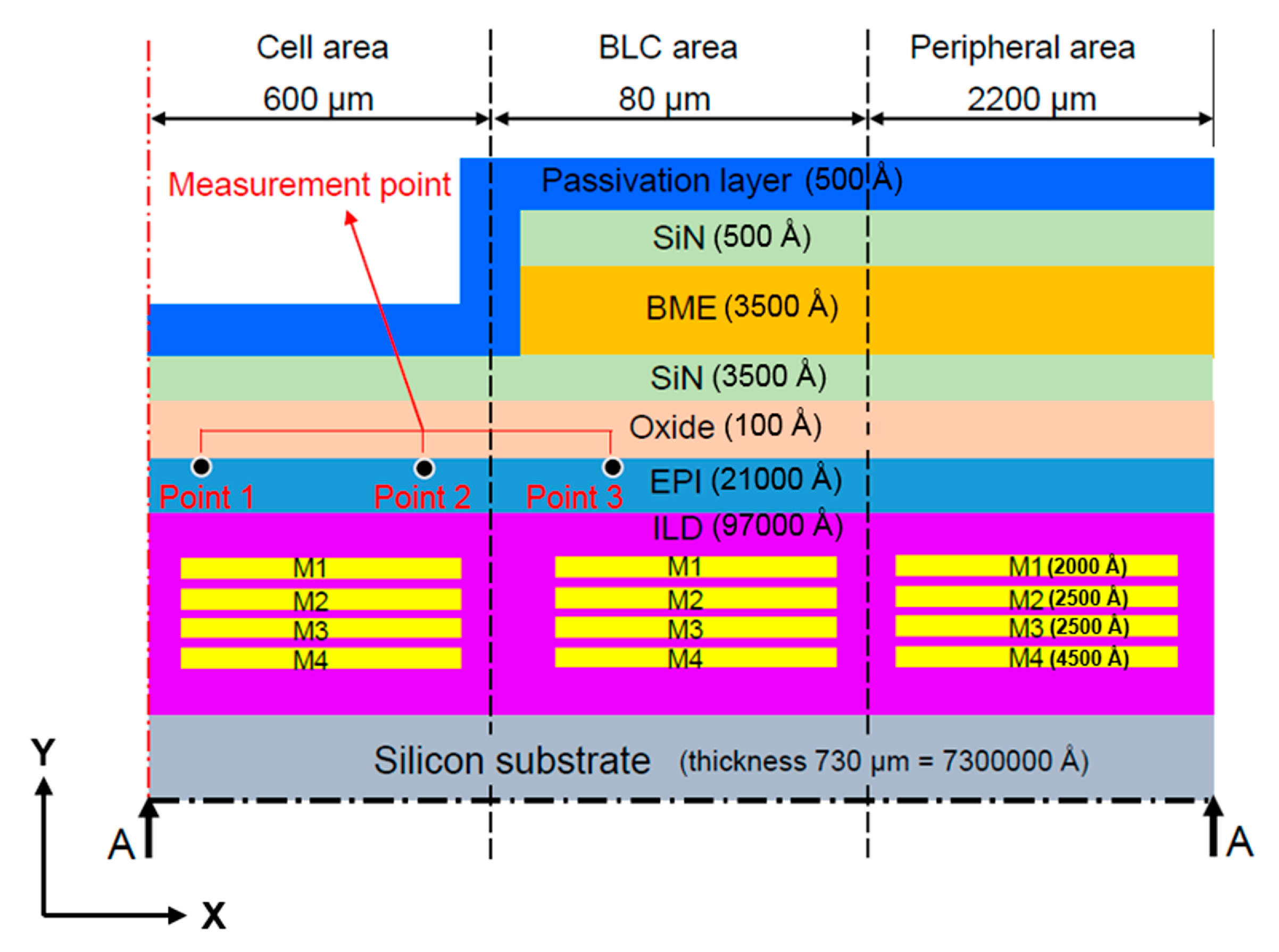

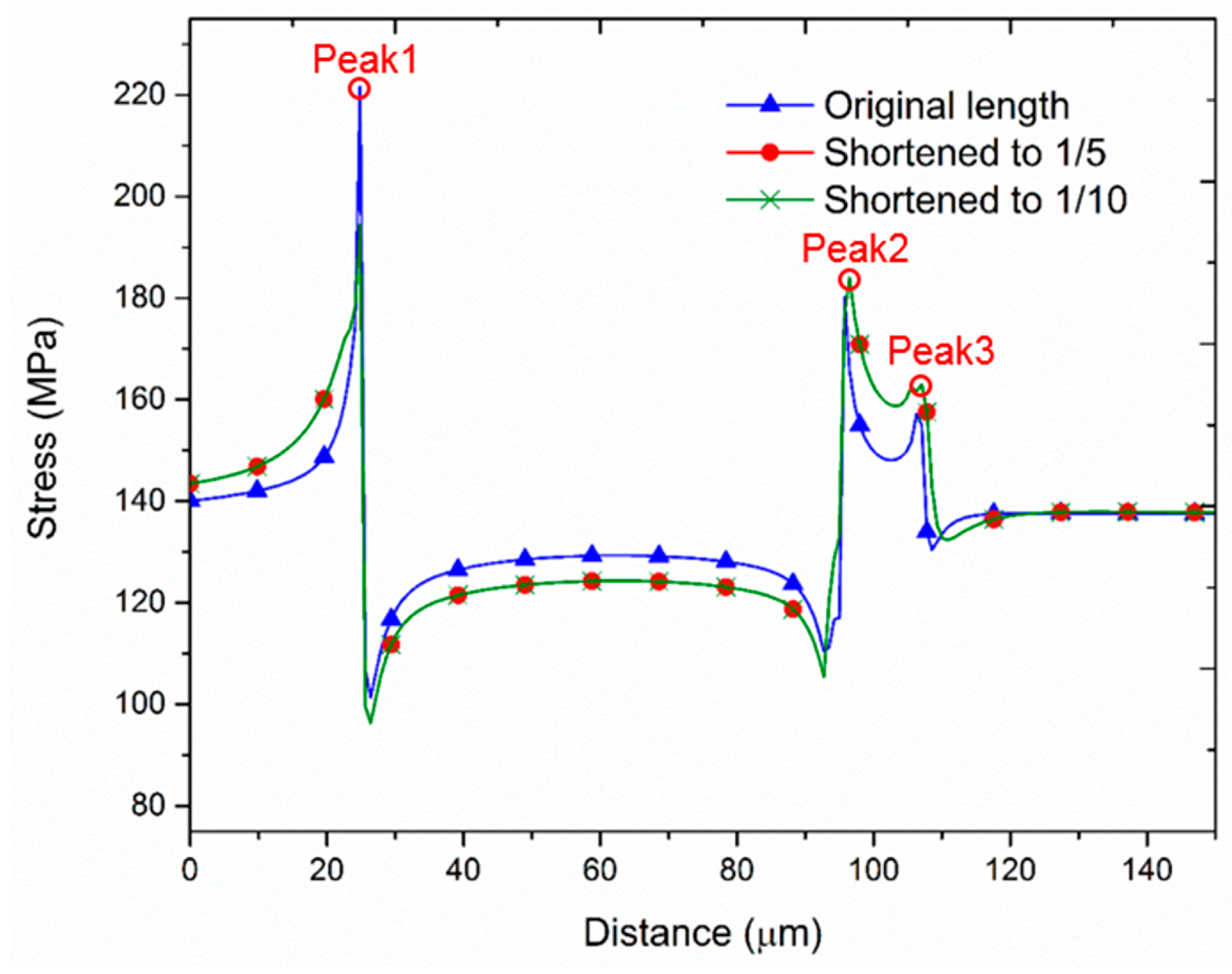

2.1.1. Mesh and Convergence

2.1.2. Boundary Conditions

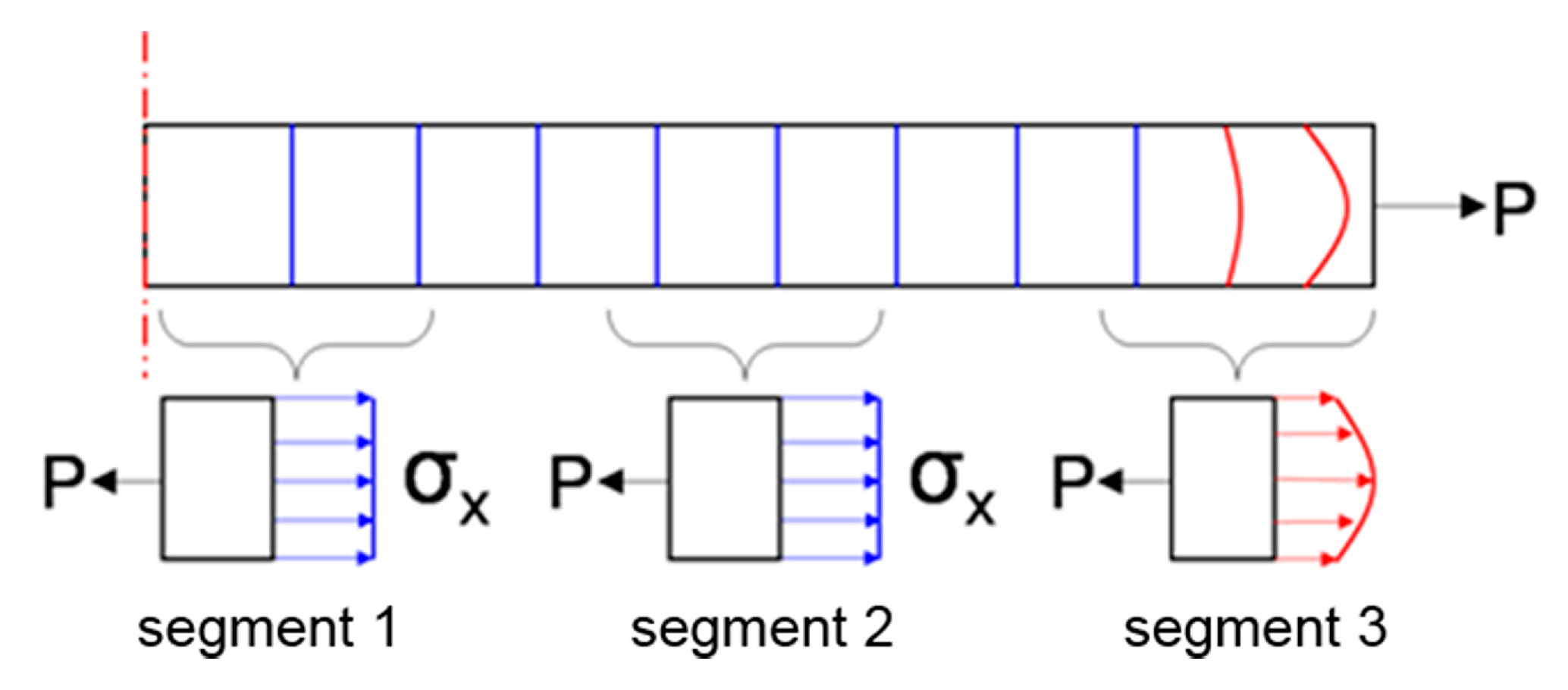

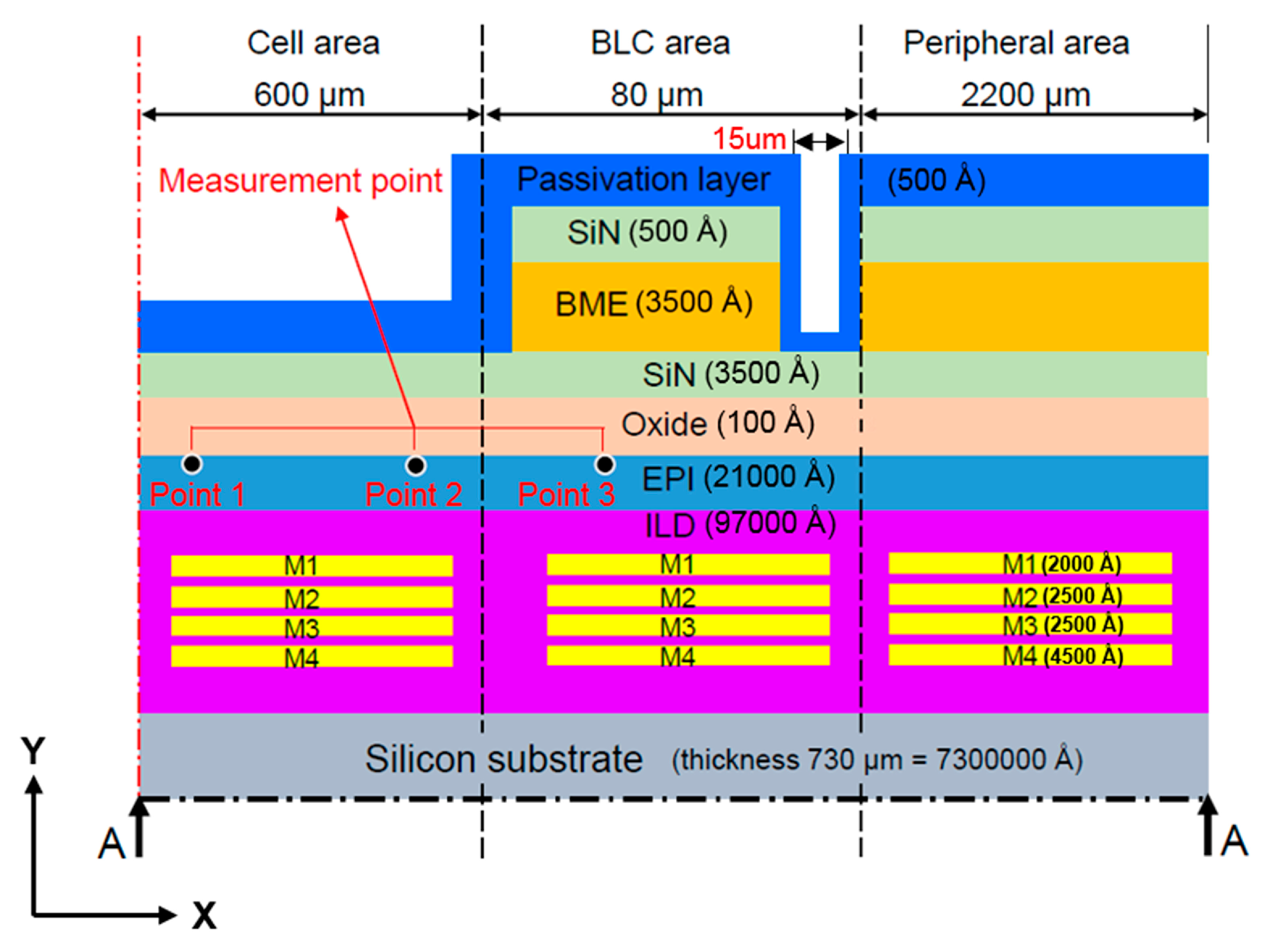

2.1.3. Simplification of the Simulation

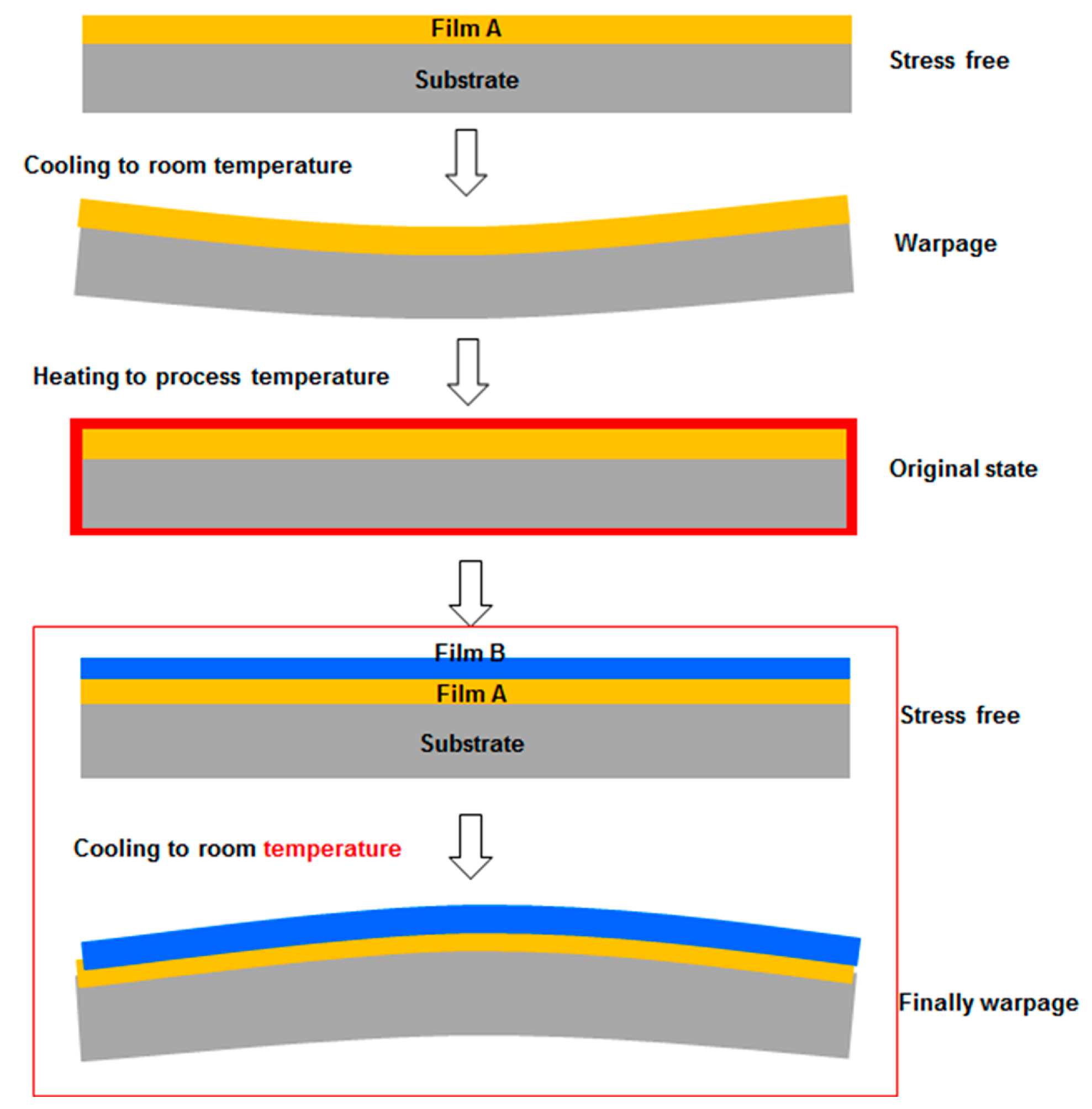

2.1.4. Simulating the Thin Film Stack Process

2.1.5. Discussion on the Stress Singularity

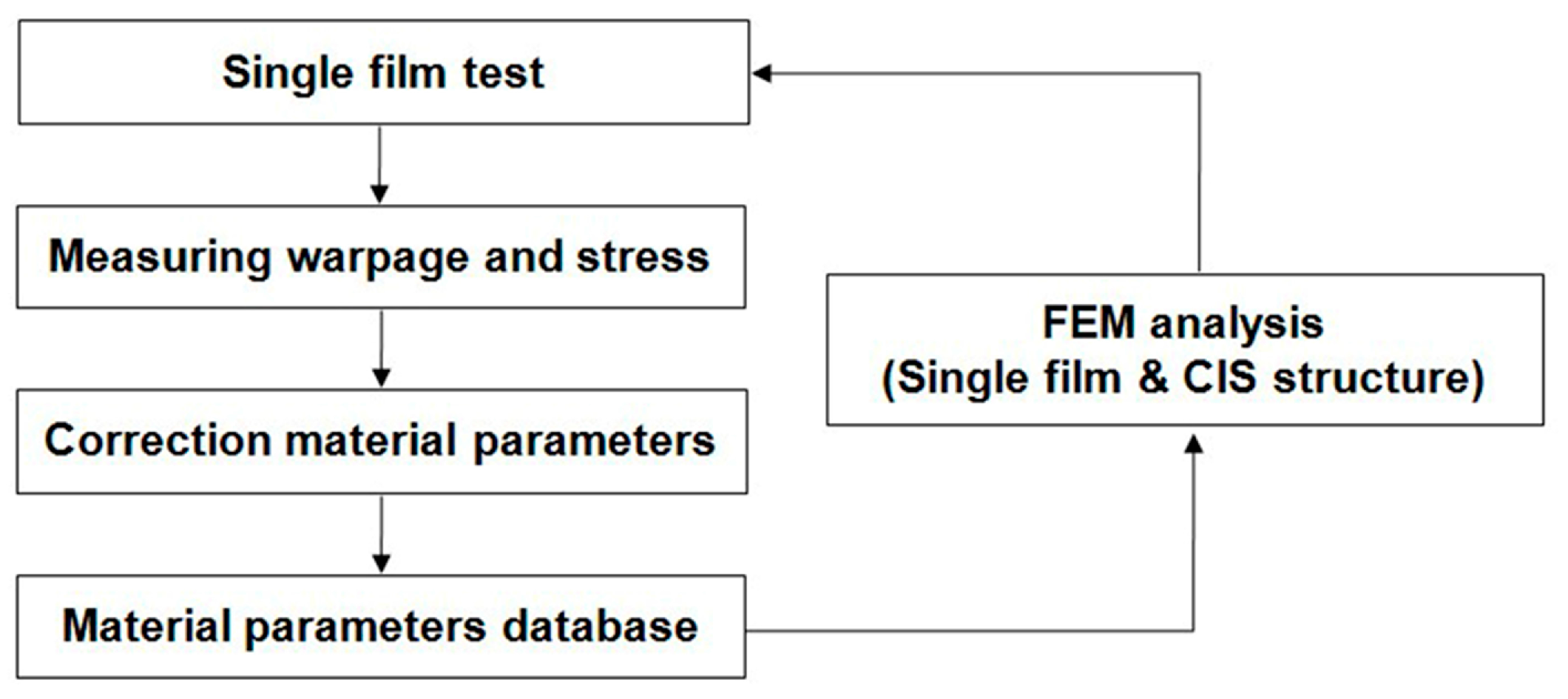

2.2. Correction of Material Parameters

3. Simulation Analysis and Experimental Measurements

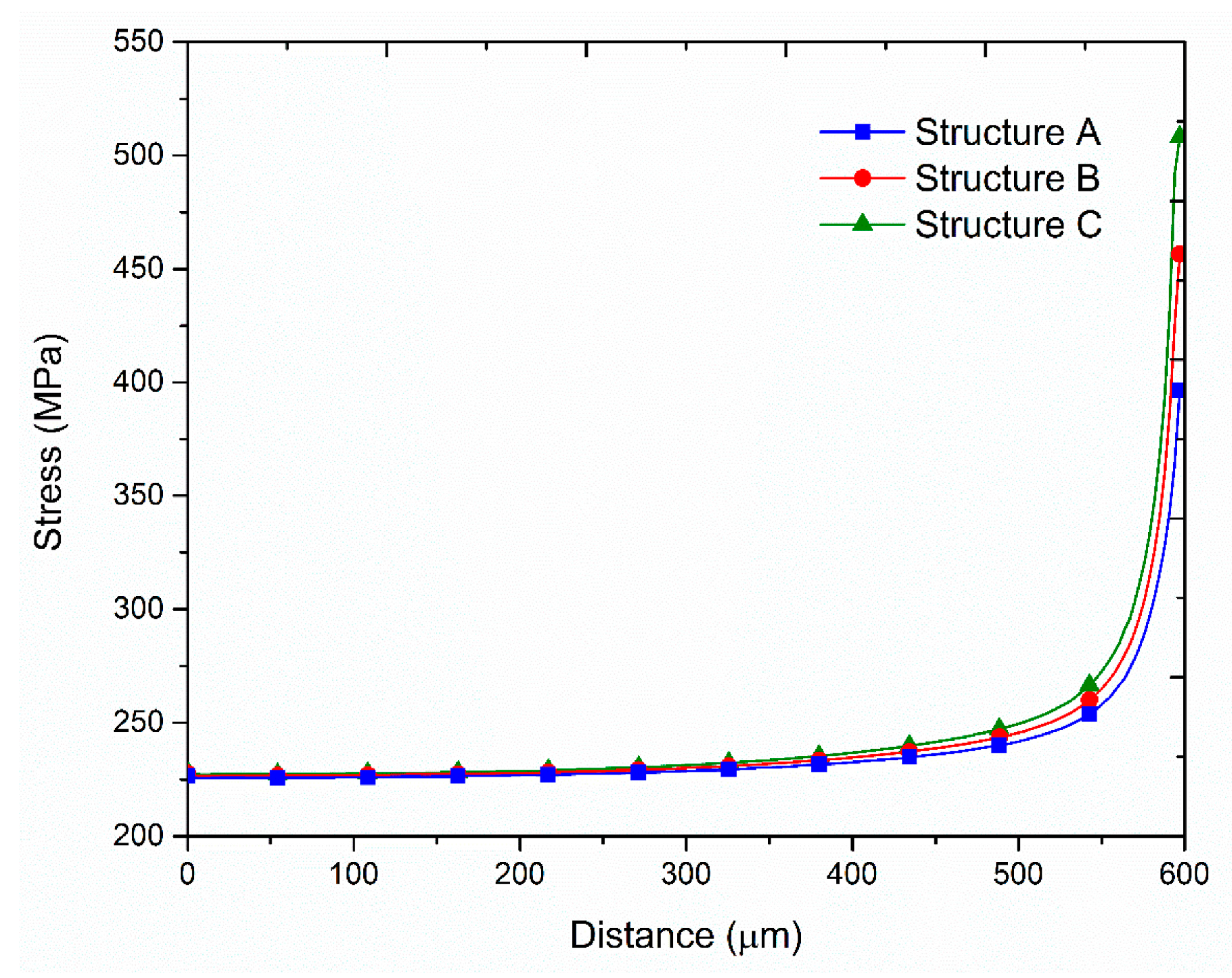

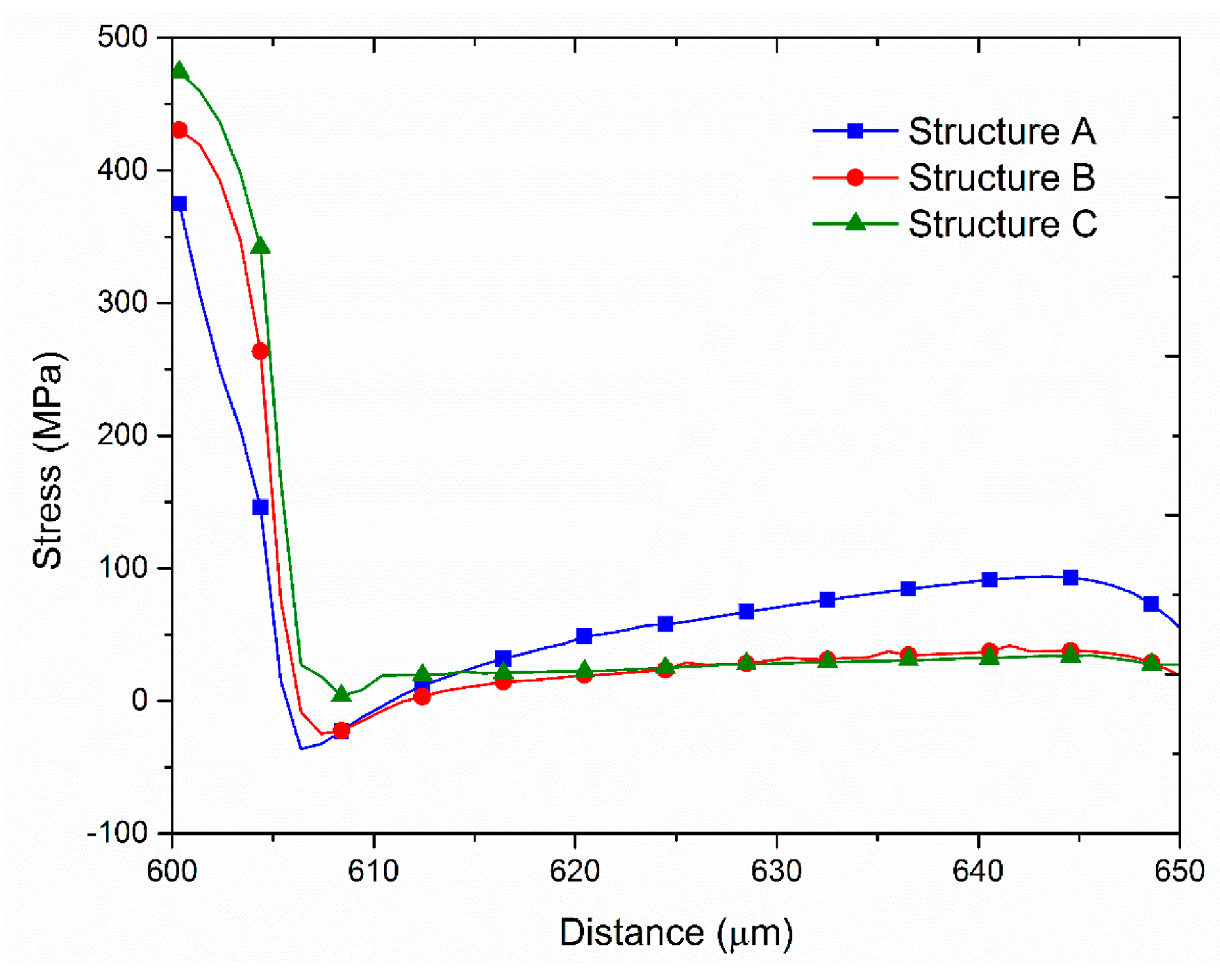

4. Results and Discussion

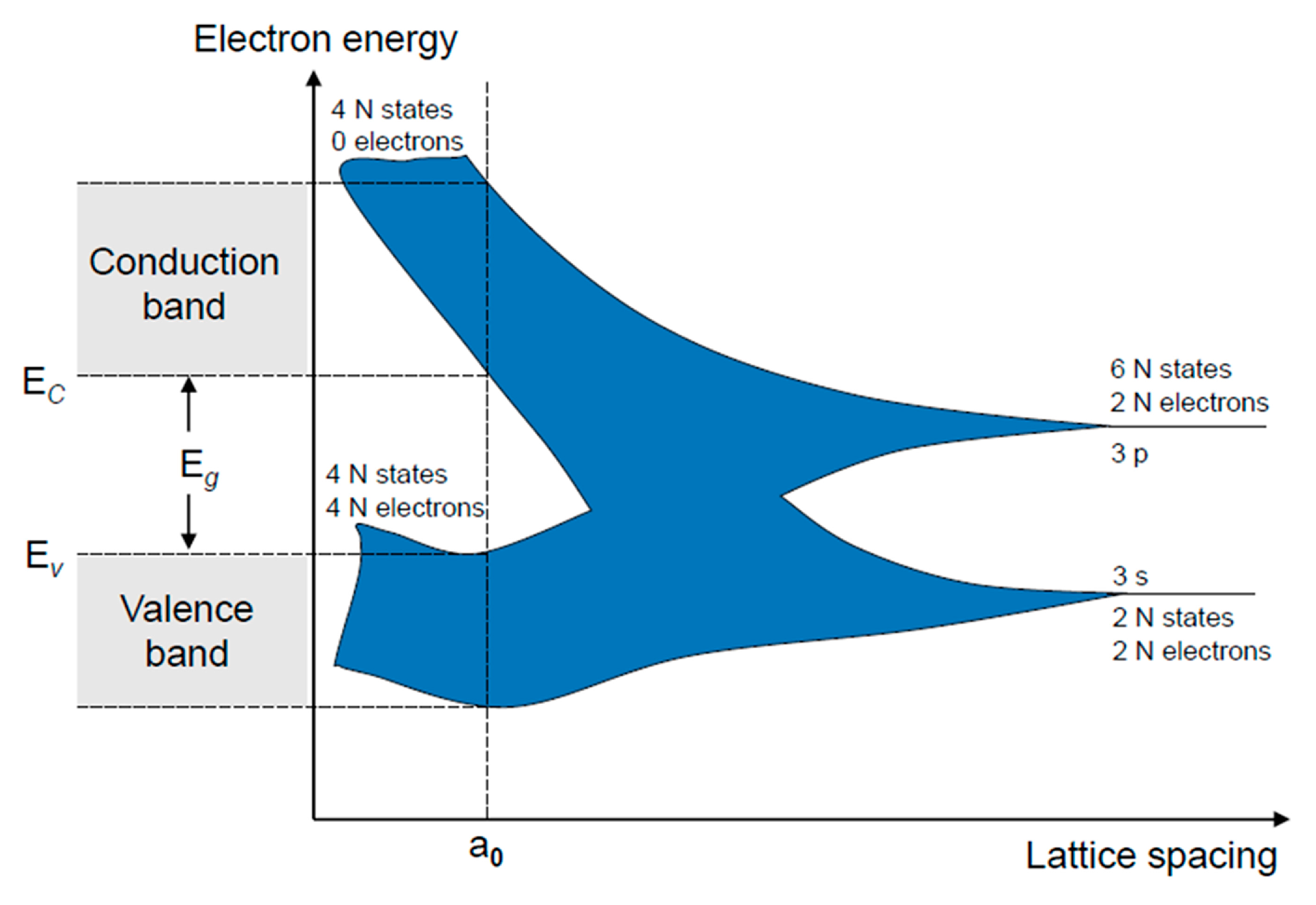

4.1. Solid-State Quantum Theory

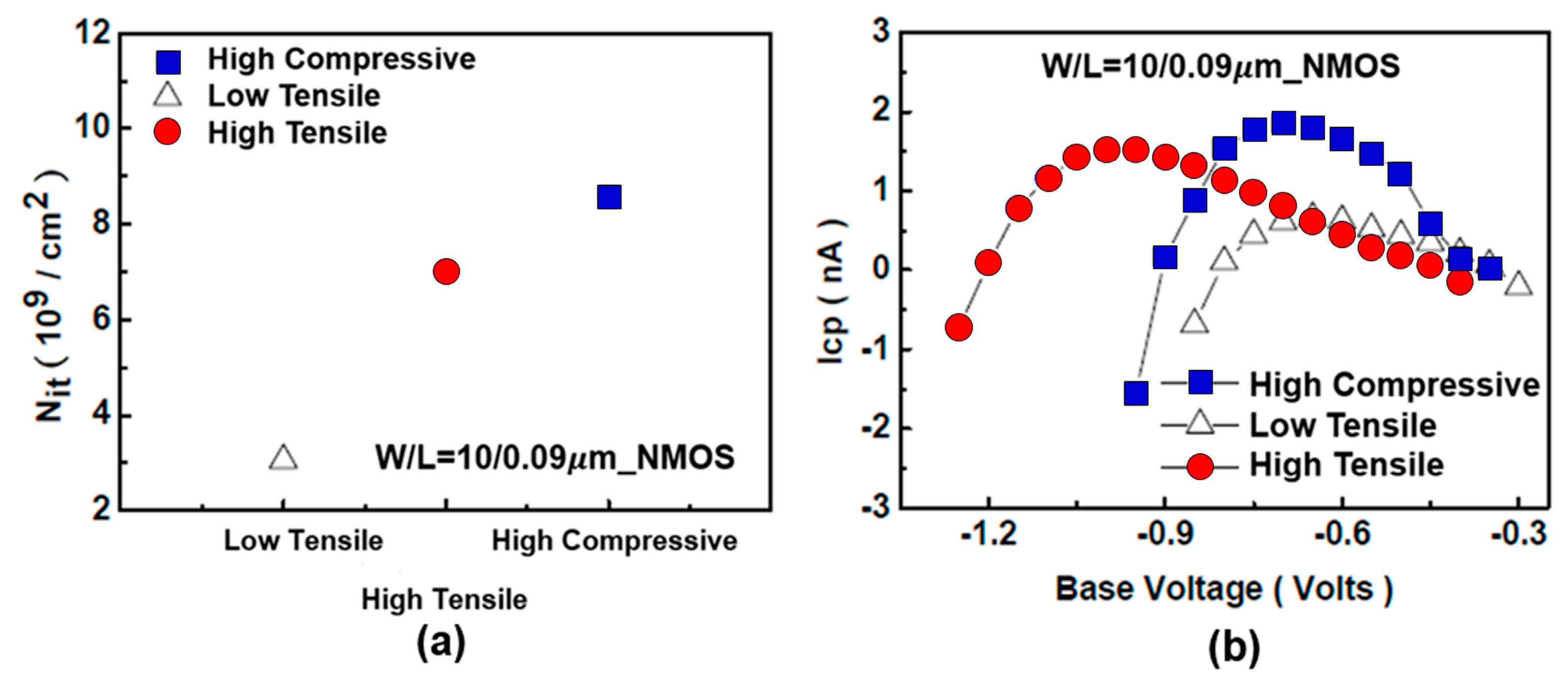

4.2. Defects Caused by High Stress

5. Verification of the Relation

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Hsu, T.H. The Study of Advanced Technologies and Novel Structures for High Performance Deep Submicron CMOS Image Sensors. Ph.D. Thesis, National Cheng Kung University, Tainan, Taiwan, 2005. [Google Scholar]

- Cammarata, R.C. Surface and interface stress effects in thin films. Prog. Surf. Sci. 1994, 46, 1–38. [Google Scholar] [CrossRef]

- Spaepen, F. Interfaces and stresses in thin films. Acta Mater. 2000, 48, 31–42. [Google Scholar] [CrossRef]

- Nix, W.D.; Clement, B.M. A mechanism for intrinsic tensile stresses in the thin films. J. Mater. Res. 1999, 14, 3467–3473. [Google Scholar] [CrossRef]

- Nix, W.D.; Doerner, M.F. Stresses and deformation processes in thin films on substrates. Crit. Rev. Solid State 1998, 14, 225–268. [Google Scholar]

- Nix, W.D. Mechanical properties of thin films. Metall. Mater. Trans. A 1999, 20, 2217–2245. [Google Scholar] [CrossRef]

- Wang, T.J.; Ko, C.H.; Chang, S.J.; Wu, S.L.; Kuan, T.M.; Lee, W.C. The Effects of Mechanical Uniaxial Stress on Junction Leakage in Nanoscale CMOSFETs. IEEE Trans. Electron Devices 2008, 55, 572–577. [Google Scholar] [CrossRef]

- Rueda, H.A. Modeling of Mechanical Stress in Silicon Isolation Technology and It’s Influence on Device Characteristics. Ph.D. Thesis, University of Florida, Gainesville, FL, USA, 1999. [Google Scholar]

- Lo, G.Q.; Kwong, D.L.; Lee, S. Reliability characteristics of metal-oxide-semiconductor capacitors with chemical vapor deposited Ta2O5 gate dielectrics. Appl. Phys. Lett. 1993, 62, 973–975. [Google Scholar] [CrossRef]

- Tsuchiya, T.; Sato, Y.; Tomizawa, M. Three mechanisms determining short-channel effects in fully-depleted SOI MOSFETs. IEEE Trans. Electron Devices 1998, 45, 1116–1121. [Google Scholar] [CrossRef]

- Lai, C.M.; Fang, Y.K.; Yeh, W.K.; Lin, C.T.; Chou, T.H. The Investigation of post-annealing-Induced Defects Behavior on 90-nm In-Halo nMOSFETs with Low-Frequency Noise and Charge-Pumping Measuring. IEEE Electron Device Lett. 2007, 28, 142–144. [Google Scholar] [CrossRef]

- Wang, C.A. The Investigation of Characteristic and Reliability for 90 nm SOI CMOSFETs with Strain Technology. Master’s Thesis, National University of Kaohsiung, Kaohsiung, Taiwan, 2007. [Google Scholar]

- Chen, J.Y.; Wang, C.A.; Yeh, W.K. The impact of strain technology on device performance and reliability for sub-90 nm FUSI SOI MOSFETs. In Proceedings of the IEEE Conference on Electron Devices and Solid-State Circuits, Tainan, Taiwan, 20–22 December 2007. [Google Scholar]

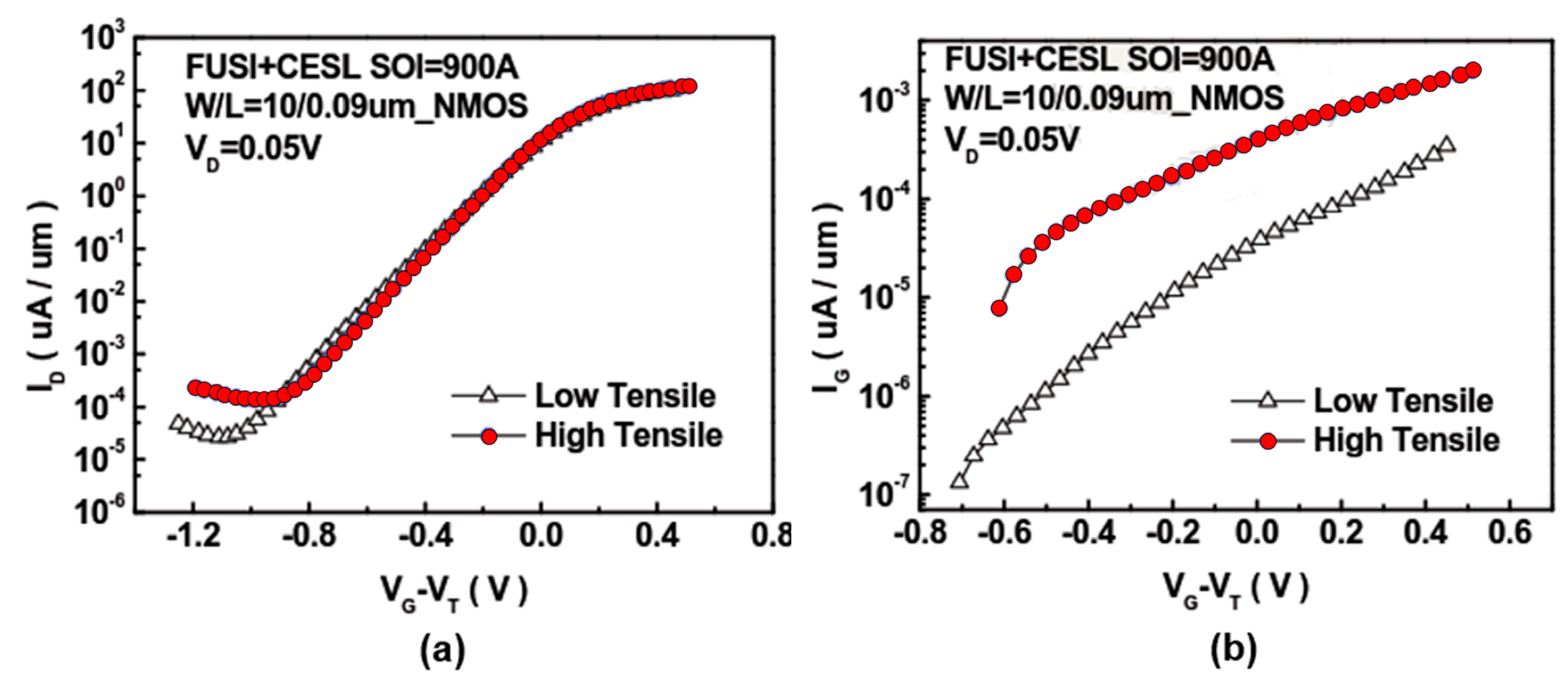

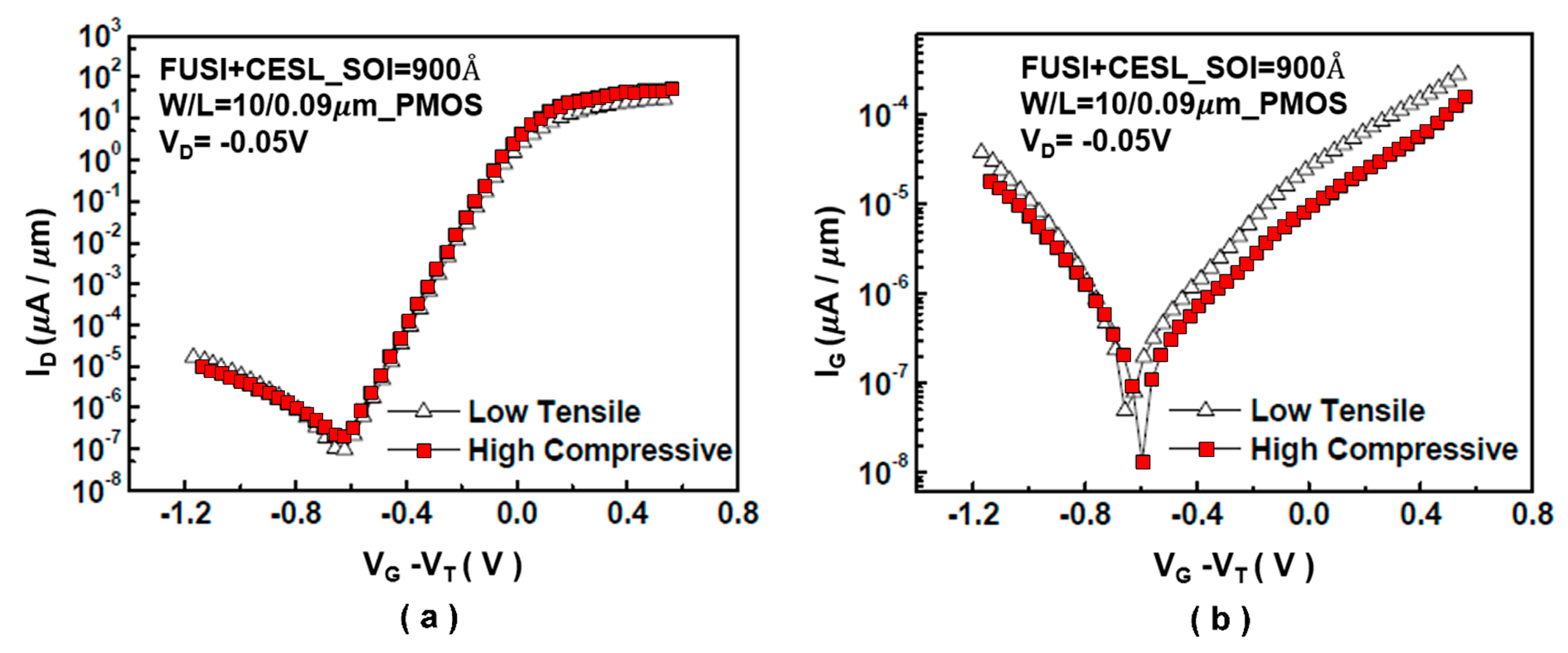

- Chang, W.T.; Wang, C.C.; Lin, J.A.; Yeh, W.K. External Stresses on Tensile and Compressive Contact Etching Stop Layer SOI MOSFETs. IEEE Trans. Electron Devices 2010, 57, 8. [Google Scholar] [CrossRef]

- Watanabe, T.; Park, J.H.; Aoyama, S.; Isobe, K.; Kawahito, S. Effects of Negative-Bias Operation and Optical Stress on Dark Current in CMOS Image Sensors. IEEE Trans. Electron Devices 2010, 57, 1512–1518. [Google Scholar] [CrossRef]

- Shcherback, I.; Belenky, A.; Yadid-Pecht, O. Empirical dark current modeling for complementary metal oxide semiconductor active pixel sensor. Opt. Eng. 2002, 41, 1216–1219. [Google Scholar] [CrossRef]

- Kim, D.H.; Park, S.; Jung, D.; Park, E.; Mhin, S.W.; Lee, C.W. Analysis of structural effect on mechanical stress at backside deep trench isolation using finite element method. Microelectron. Eng. 2016, 154, 42–47. [Google Scholar] [CrossRef]

- Lee, H.H. Meshing. In Finite Element Simulations with ANSYS Workbench 16; Schroff Development Corporation: Mission, KS, USA, 2015; pp. 350–361. [Google Scholar]

- Chuang, W.C.; Lin, D.T.W.; Hu, Y.C.; Lee, H.L.; Cheng, C.H.; Chang, P.Z.; Quyen, N.B. A Method Integrating Optimal Algorithmand FEM on CMOS Residual Stress. J. Mech. 2014, 30, 123–128. [Google Scholar] [CrossRef]

- ANSYS Inc. Chapter 13: Element Birth and death, ANSYS Engineering Data Help for Workbench. In ANSYS Release15.0; ANSYS Inc.: Canonsburg, PA, USA, 2013. [Google Scholar]

- Stoney, G.G. The tension of metallic films deposited by electrolysis. Proc. R. Soc. A 1909, 82, 172–175. [Google Scholar] [CrossRef]

- Gallon, C.; Reimbold, G.; Ghibaudo, G.; Bianchi, R.A.; Gwoziecki, R. Electrical analysis of external mechanical stress effects in short channel MOSFETs on (001) silicon. Solid State Electron. 2004, 48, 561–566. [Google Scholar] [CrossRef]

- Dong, J.W. Investigation of Strain-Temperature Stress on Rapid Thermal Ultra-Thin Gate Oxides. Master’s Thesis, National Taiwan University, Taipei, Taiwan, 2005. [Google Scholar]

- Wang, T.J.; Chen, H.W.; Yeh, P.C.; Ko, C.H.; Chang, S.J.; Yeh, J.; Wu, S.L.; Lee, C.Y.; Lee, W.C.; Tang, D.D. Effects of mechanical uniaxial stress on SiGe HBT characteristics. J. Electrochem. Soc. 2007, 154, 105–108. [Google Scholar] [CrossRef]

- Lee, W.I. Physics II, National Chiao Tung University OpenCourseWare. Available online: http://ocw.nctu.edu.tw/course_detail.php?bgid=1&gid=3&nid=383#.WCqUlS195pg (accessed on 29 April 2017).

| Model Length | Number of Elements |

|---|---|

| Original | 207,605 |

| 1/5 | 108,962 |

| 1/10 | 57,754 |

| Stress | Element Size (μm) | |||

|---|---|---|---|---|

| 0.2 | 0.15 | 0.1 | 0.05 | |

| Peak 1 | 225.2 MPa | 225.2 MPa | 225.1 MPa | 225.1 MPa |

| Peak 2 | 182.3 MPa | 182.3 MPa | 182.3 MPa | 182.2 MPa |

| Peak 3 | 154.7 MPa | 154.7 MPa | 154.6 MPa | 154.6 MPa |

| Materials | E (GPa) | Poisson Ratio | CTE (ppm/°C) |

|---|---|---|---|

| Oxide | 73 | 0.17 | 0.55 |

| SiN | 130 | 0.3 | 10 |

| Epitaxial silicon | 190 | 0.28 | 2.33 |

| Silicon chip | 160 | 0.28 | 3 |

| Inter metal dielectric (IMD) | 11.7 | 10.1 | 1.16 |

| Film Structure | Electrical Data (e−/s) | ||

|---|---|---|---|

| Point 1 | Point 2 | Point 3 | |

| Structure A | 74.8 | 9 | 8.31 |

| Structure B | 14.9 | 8 | 1.8 |

| Structure C | 11.7 | 10.1 | 1.16 |

| Film Structure | Electrical Data (e−/s) | ||

|---|---|---|---|

| Point 1 | Point 2 | Point 3 | |

| Structure C | 11.7 | 10.1 | 1.16 |

| Structure 2T | 14.6 | 13 | 0.9 |

| Structure 4T | 15.8 | 18.7 | 0.84 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, K.-T.; Hwang, S.-J.; Lee, H.-H. Finite Element Analysis of Film Stack Architecture for Complementary Metal-Oxide–Semiconductor Image Sensors. Sensors 2017, 17, 1004. https://doi.org/10.3390/s17051004

Wu K-T, Hwang S-J, Lee H-H. Finite Element Analysis of Film Stack Architecture for Complementary Metal-Oxide–Semiconductor Image Sensors. Sensors. 2017; 17(5):1004. https://doi.org/10.3390/s17051004

Chicago/Turabian StyleWu, Kuo-Tsai, Sheng-Jye Hwang, and Huei-Huang Lee. 2017. "Finite Element Analysis of Film Stack Architecture for Complementary Metal-Oxide–Semiconductor Image Sensors" Sensors 17, no. 5: 1004. https://doi.org/10.3390/s17051004