A Study on the Thermomechanical Reliability Risks of Through-Silicon-Vias in Sensor Applications

Abstract

:1. Introduction

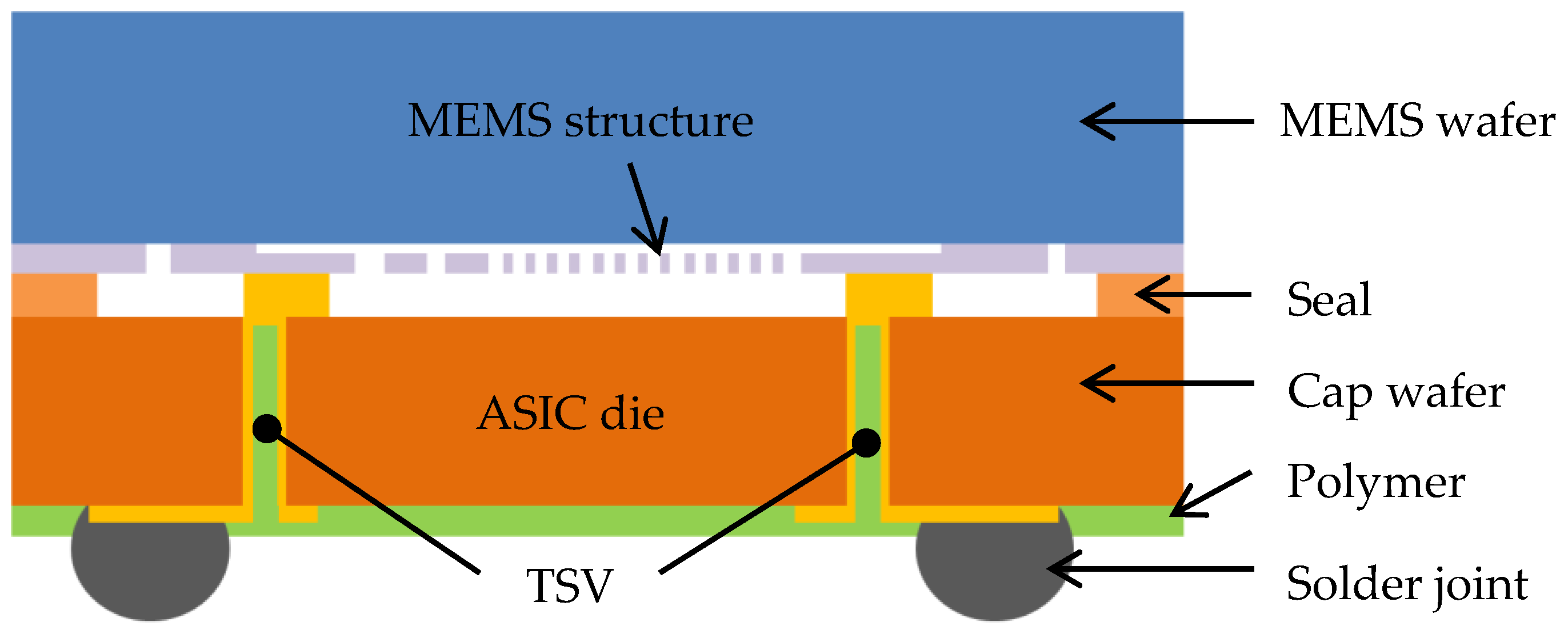

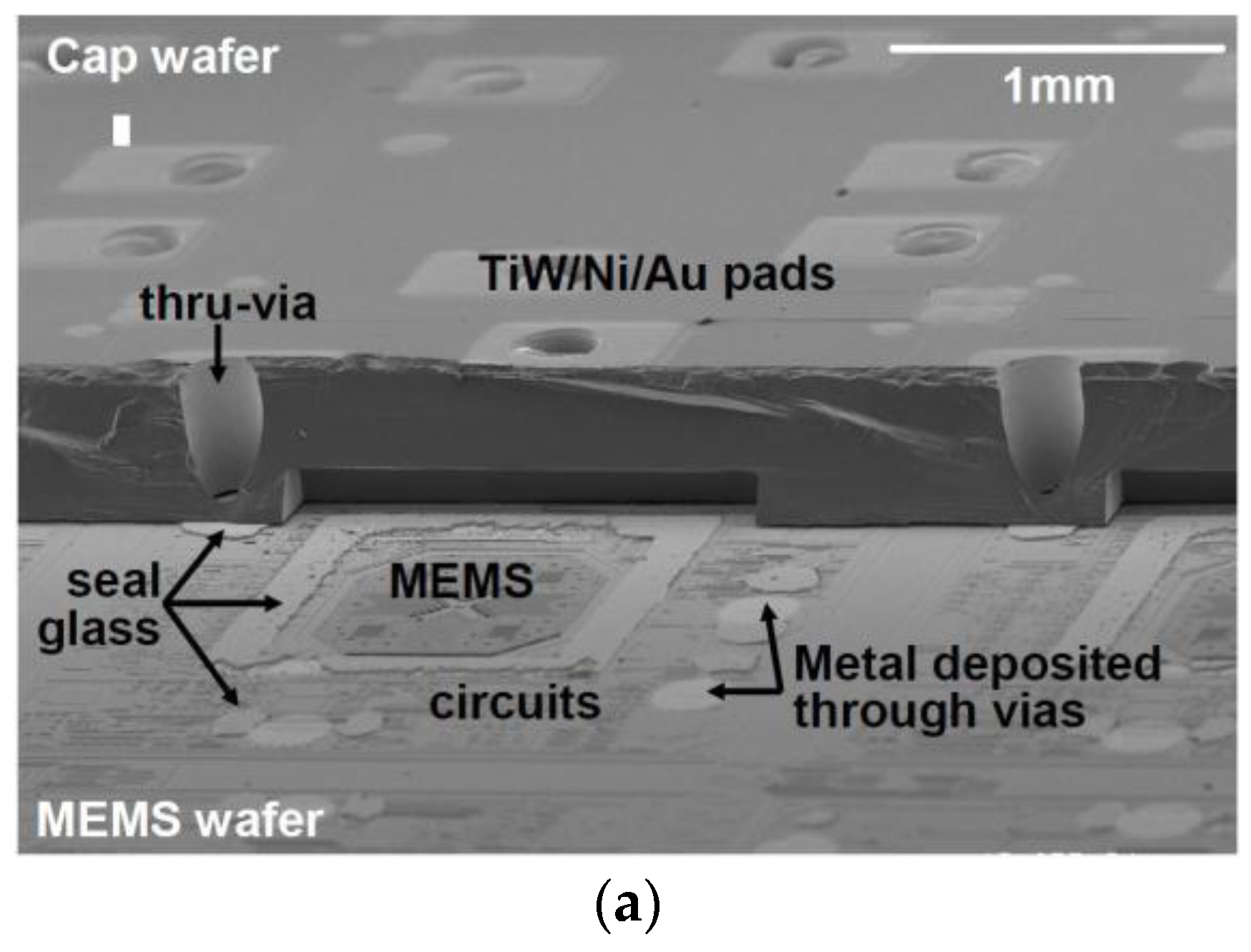

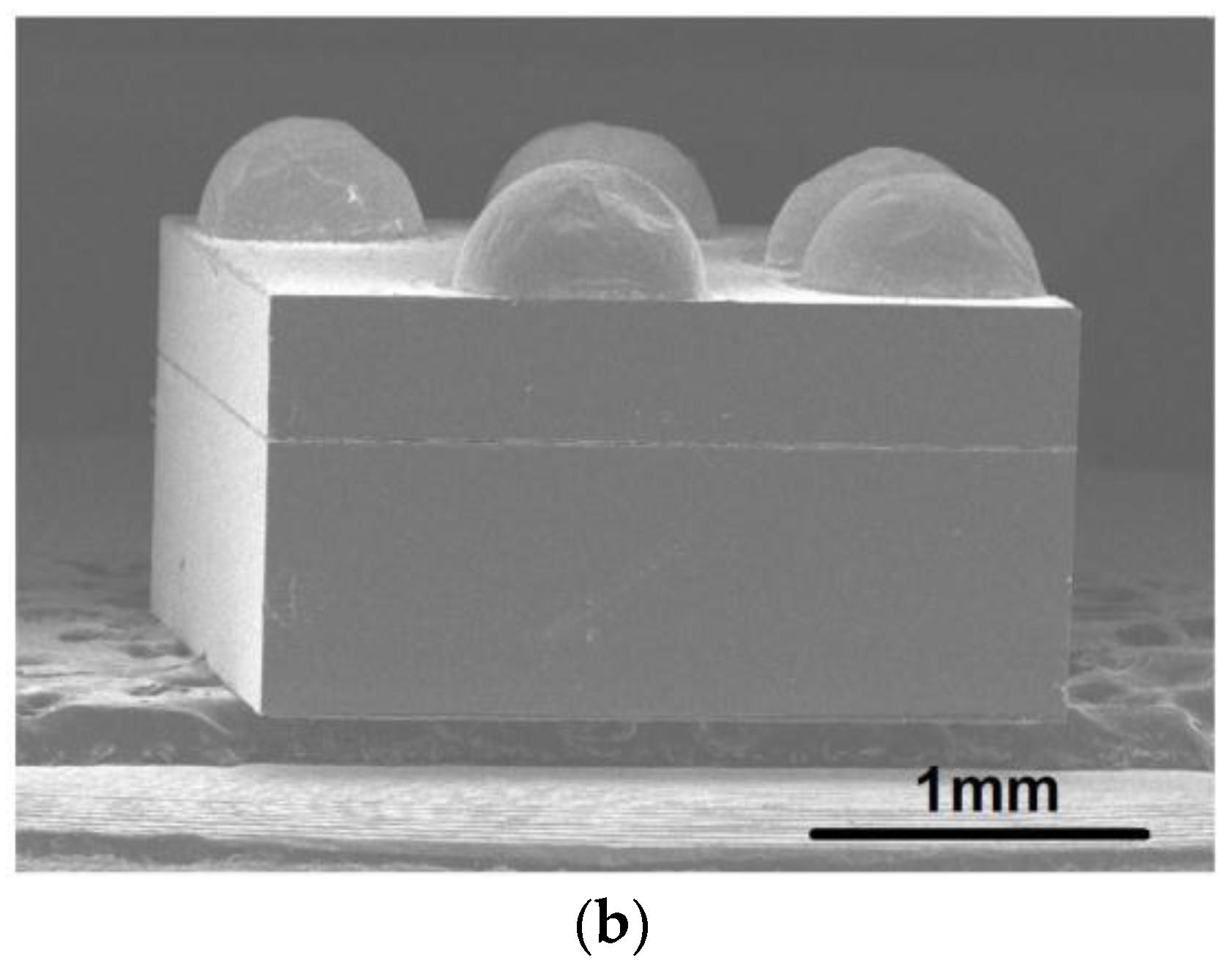

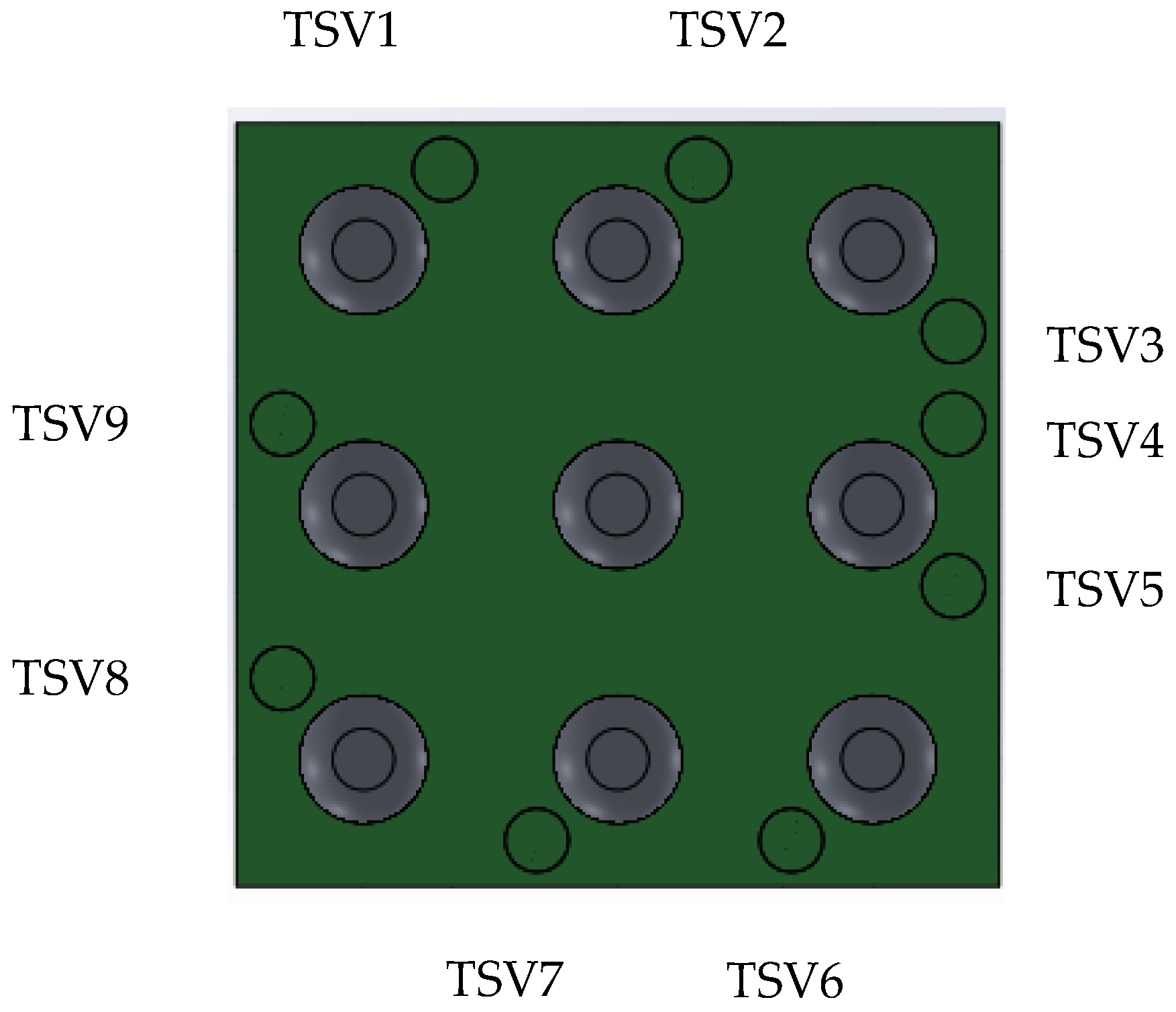

2. TSV in MEMS Sensor

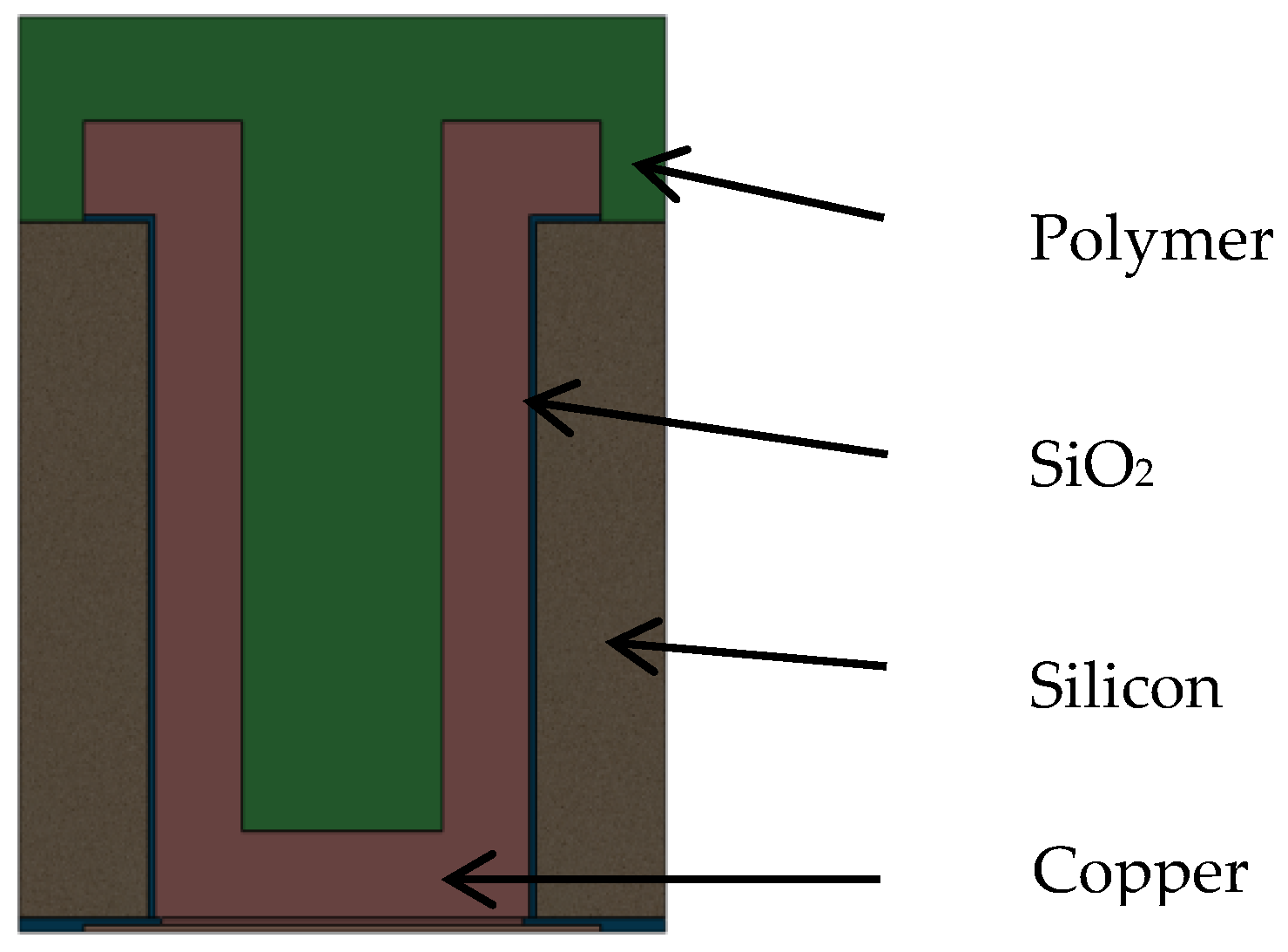

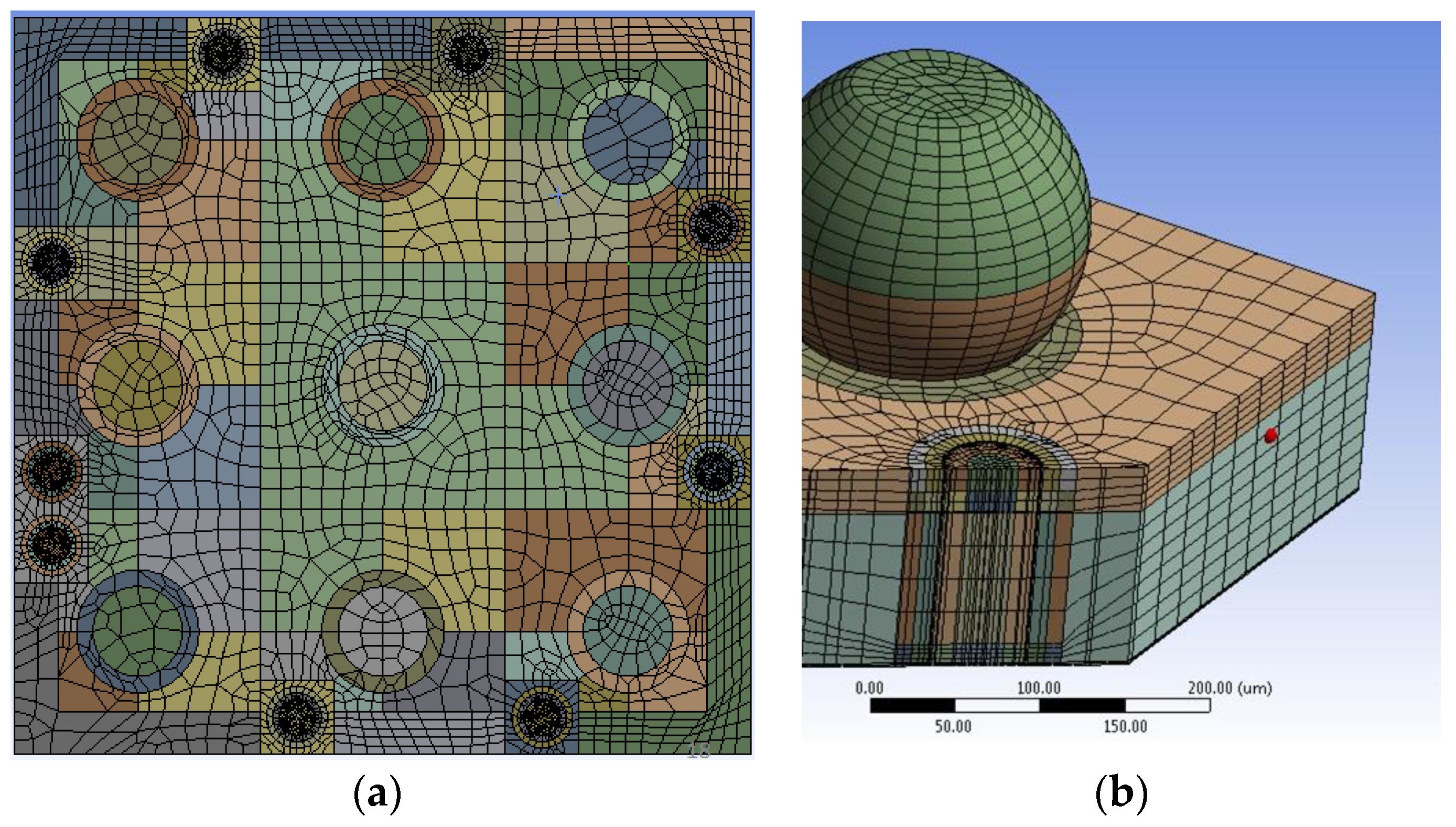

3. Finite Element Model for Cu TSV

4. Discussion: Reliability Risks for Cu TSV

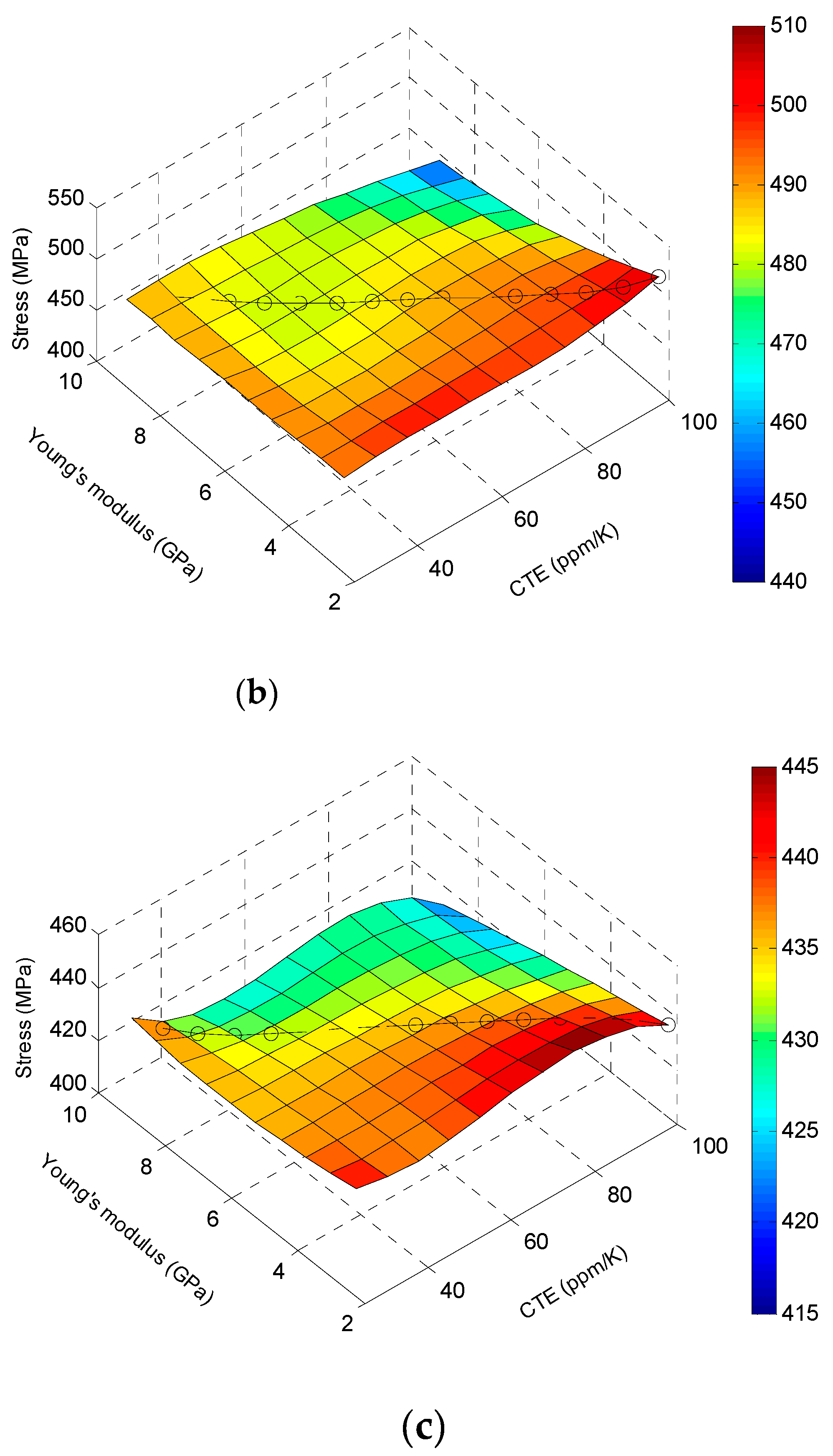

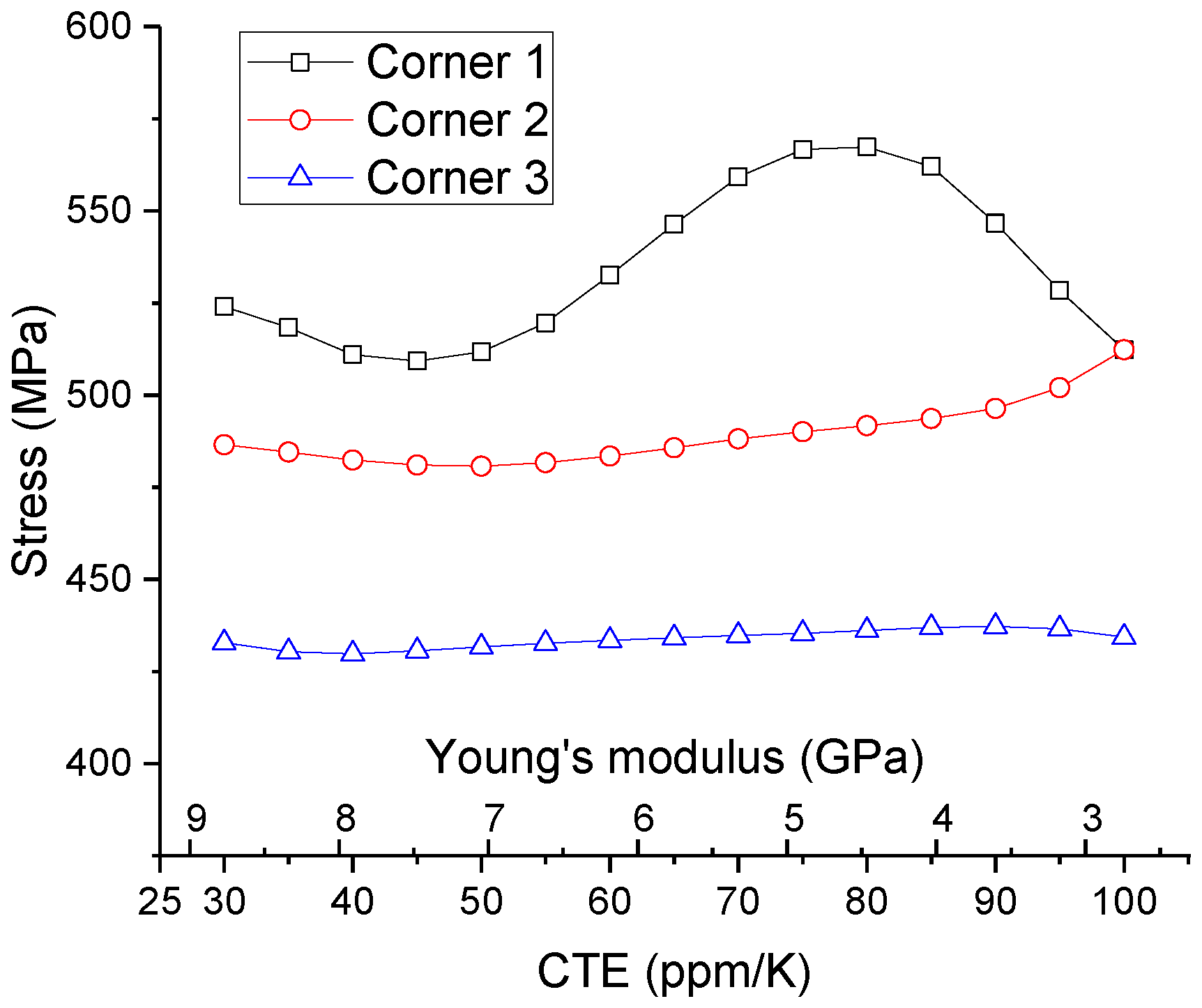

Effect of the Polymer Material Properties: CTE and Young’s Modulus

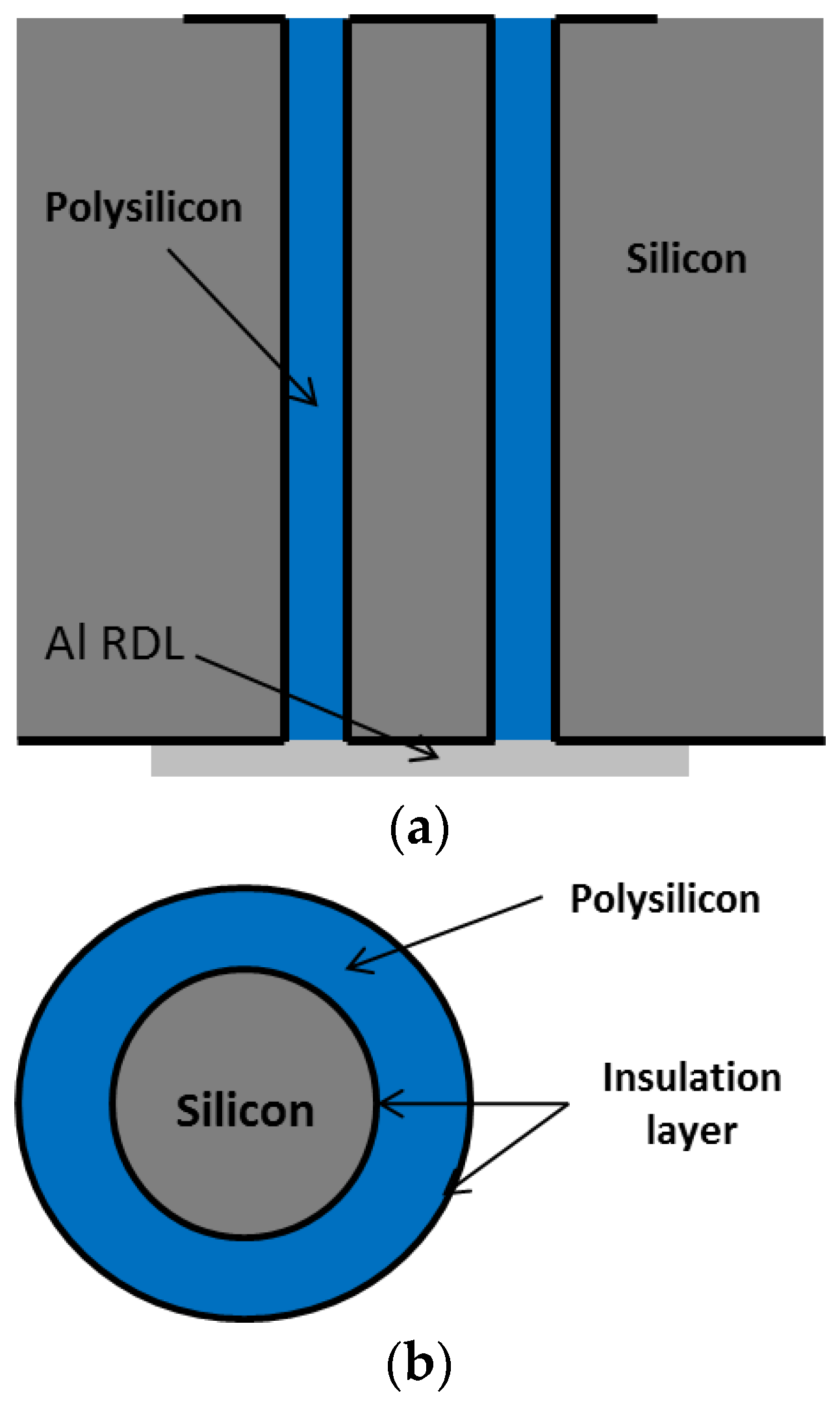

5. Poly-Si TSV for Optical Sensor

6. Finite Element Model for Poly-Si TSV in Optical Sensor

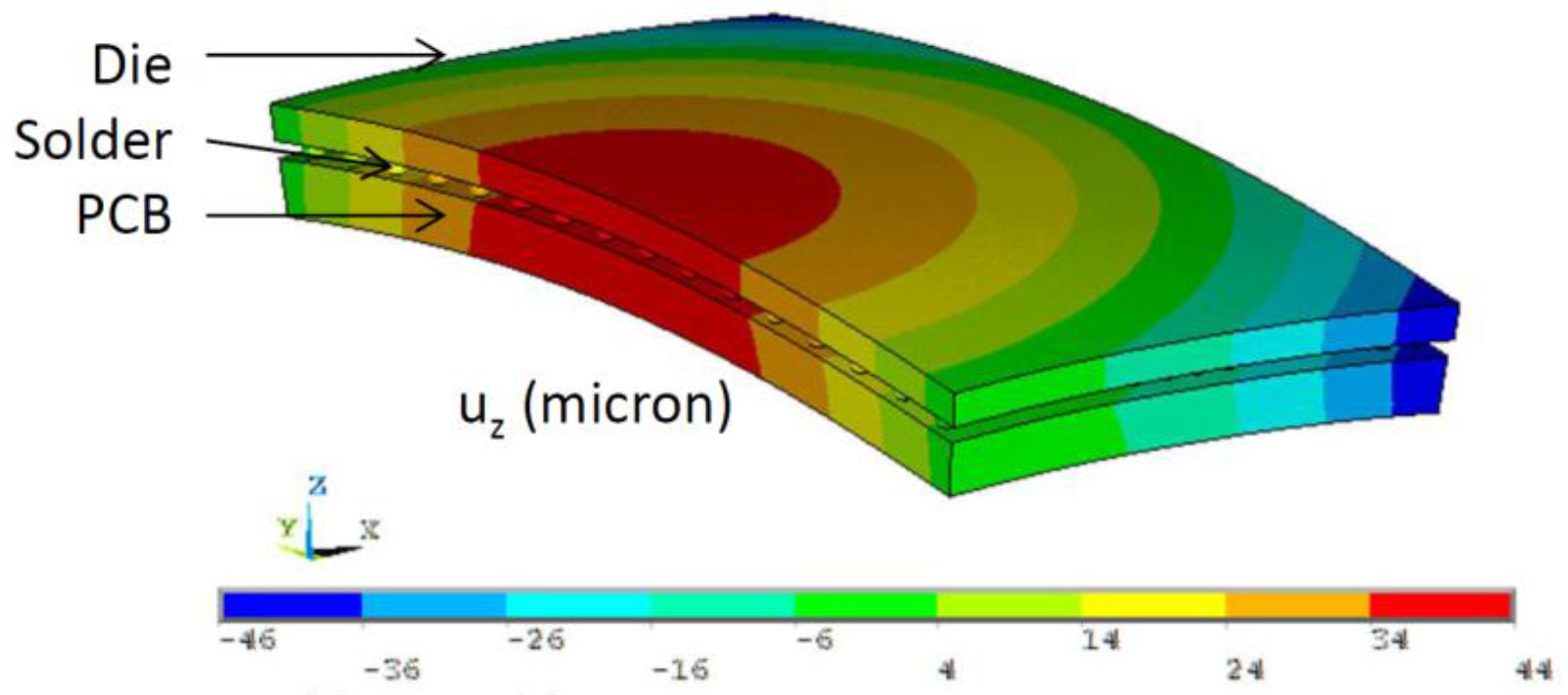

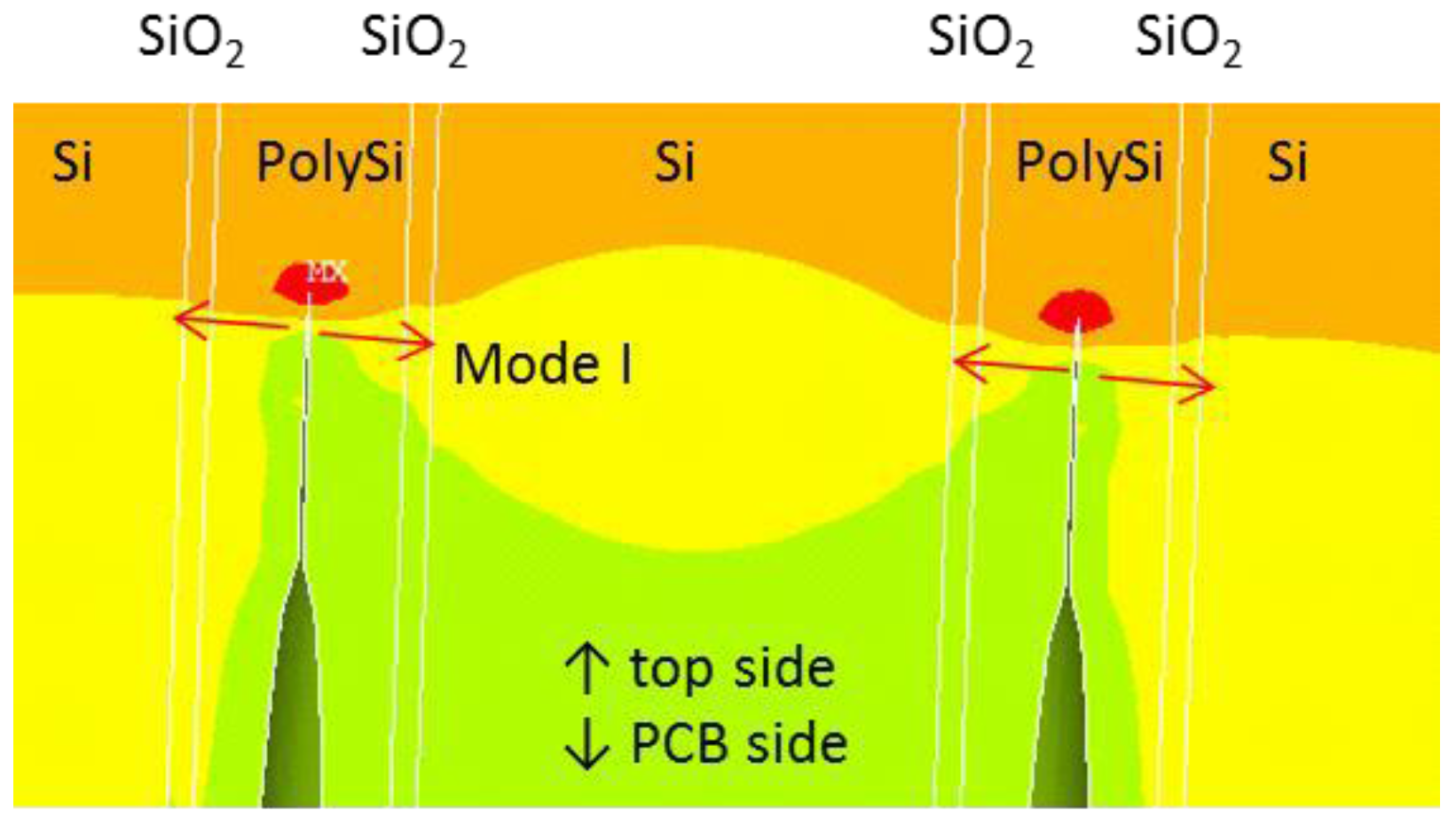

7. Discussion: Reliability Risks of Poly-Si TSV in Sensor Assembled on PCB

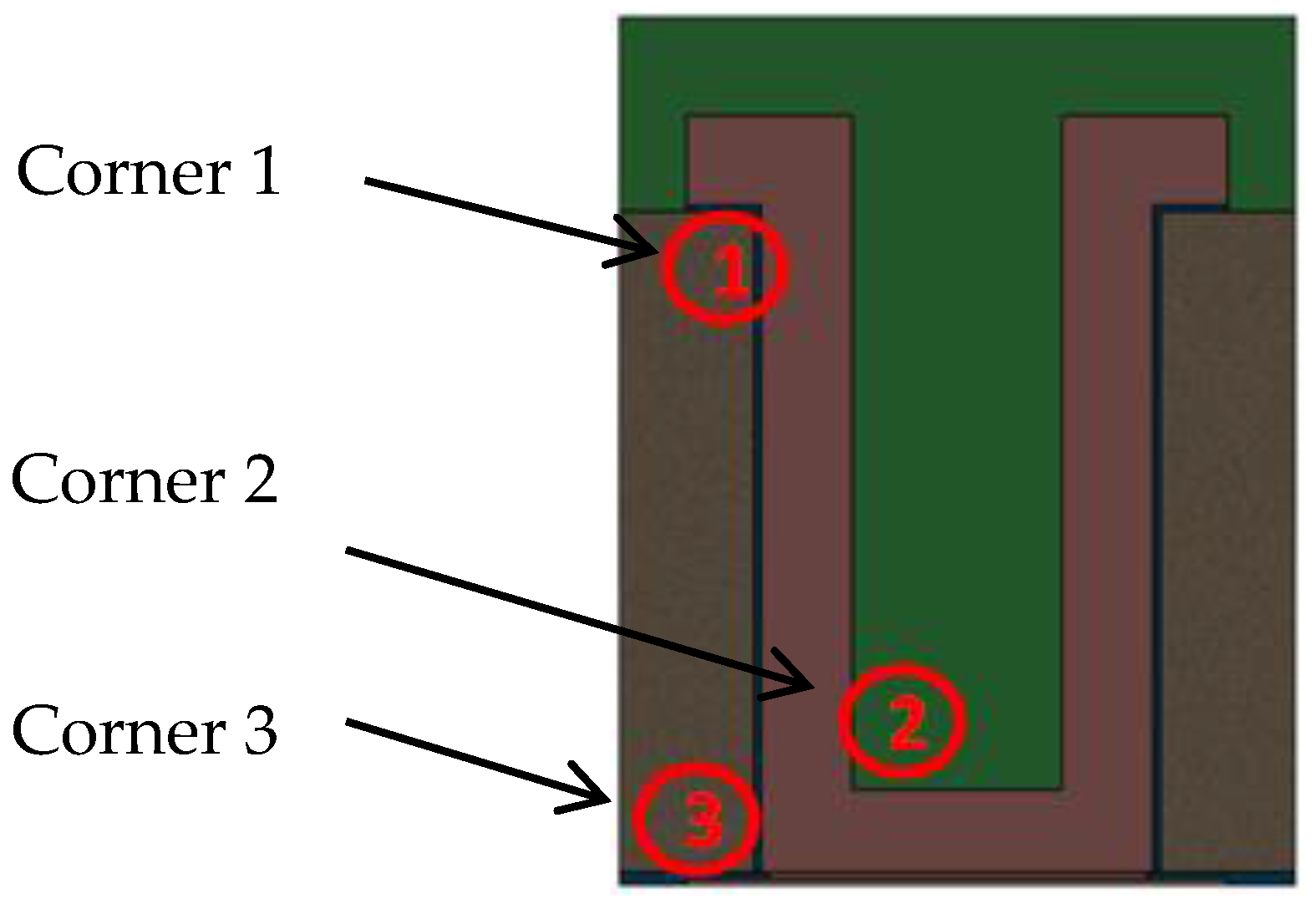

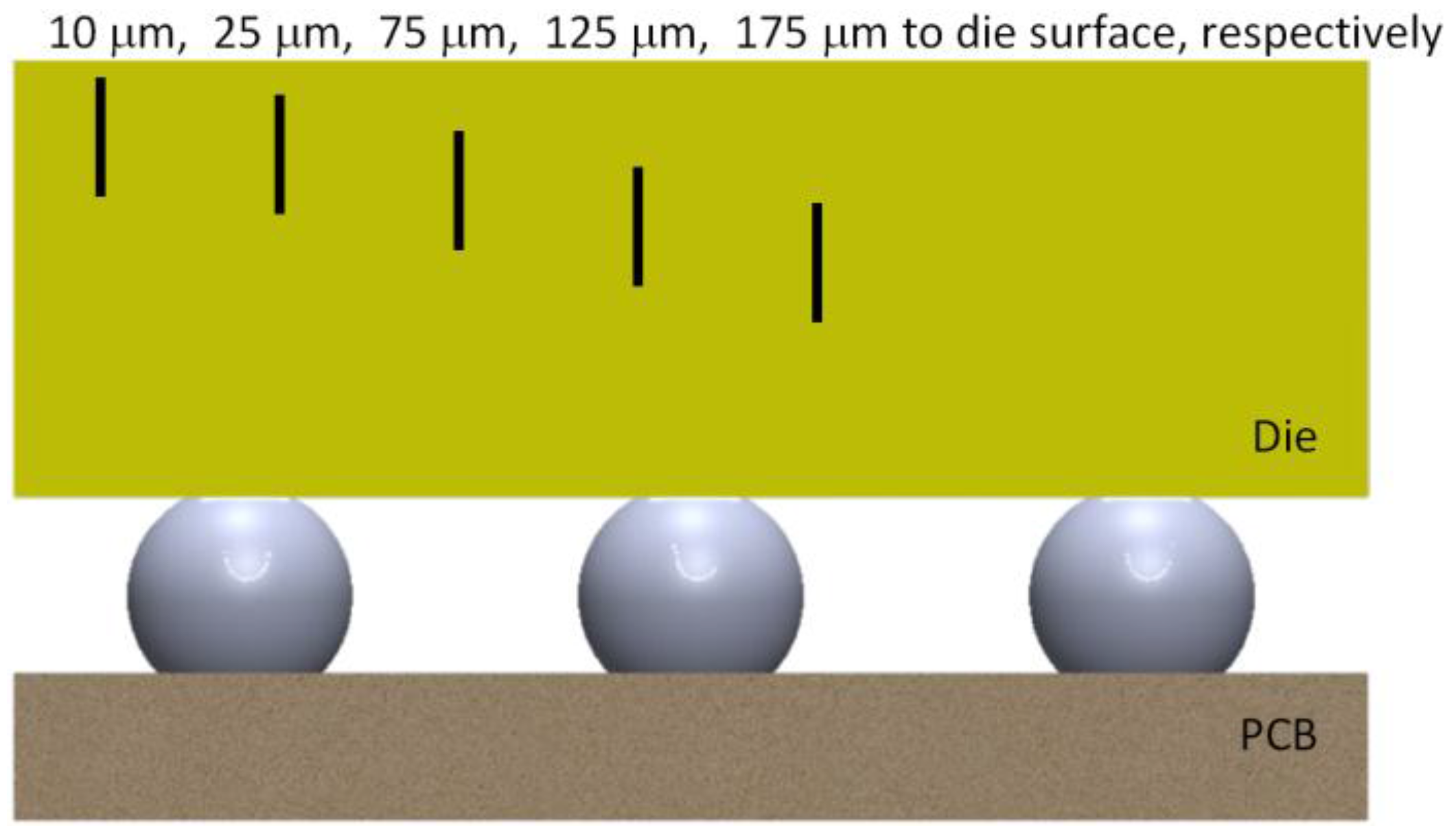

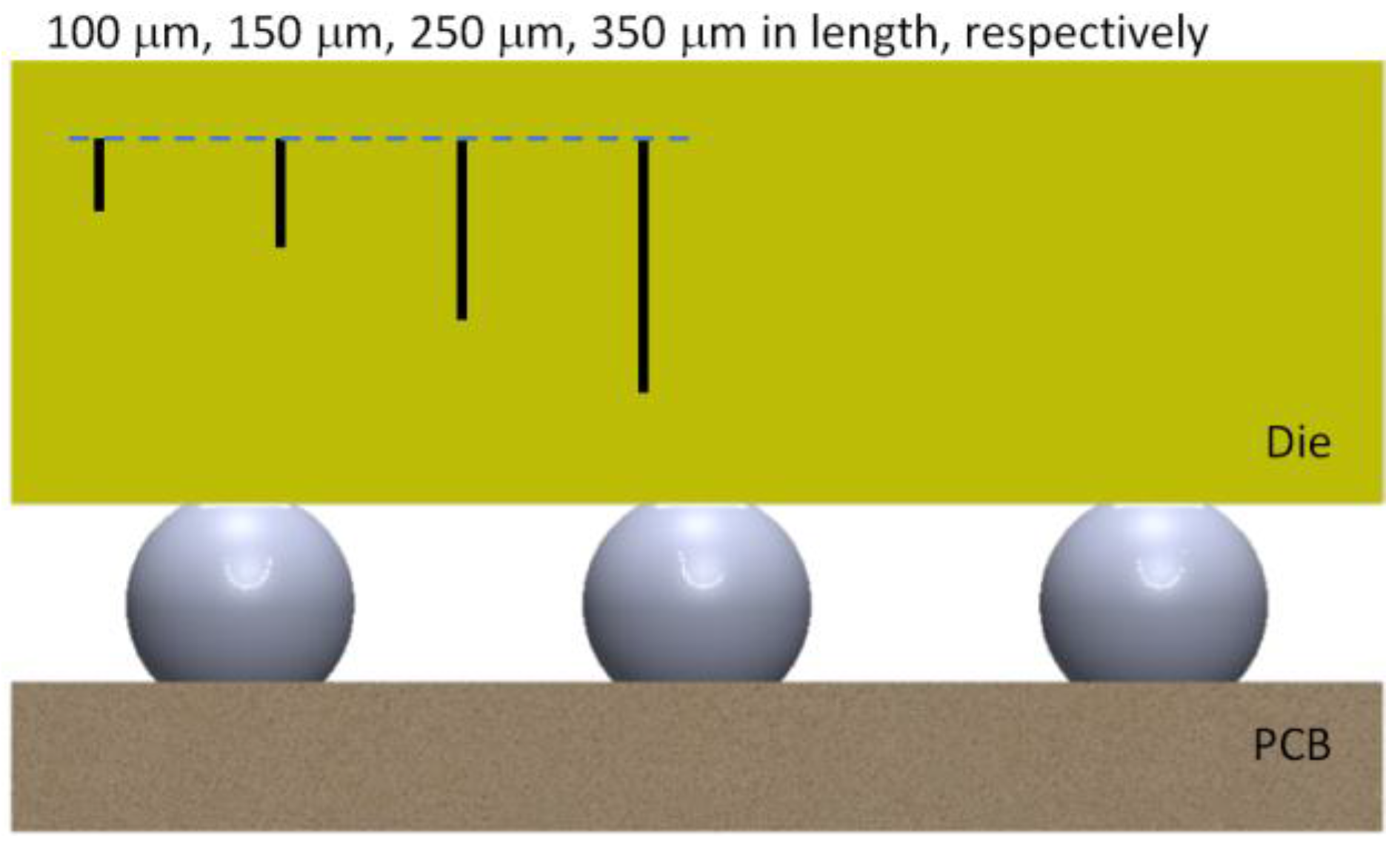

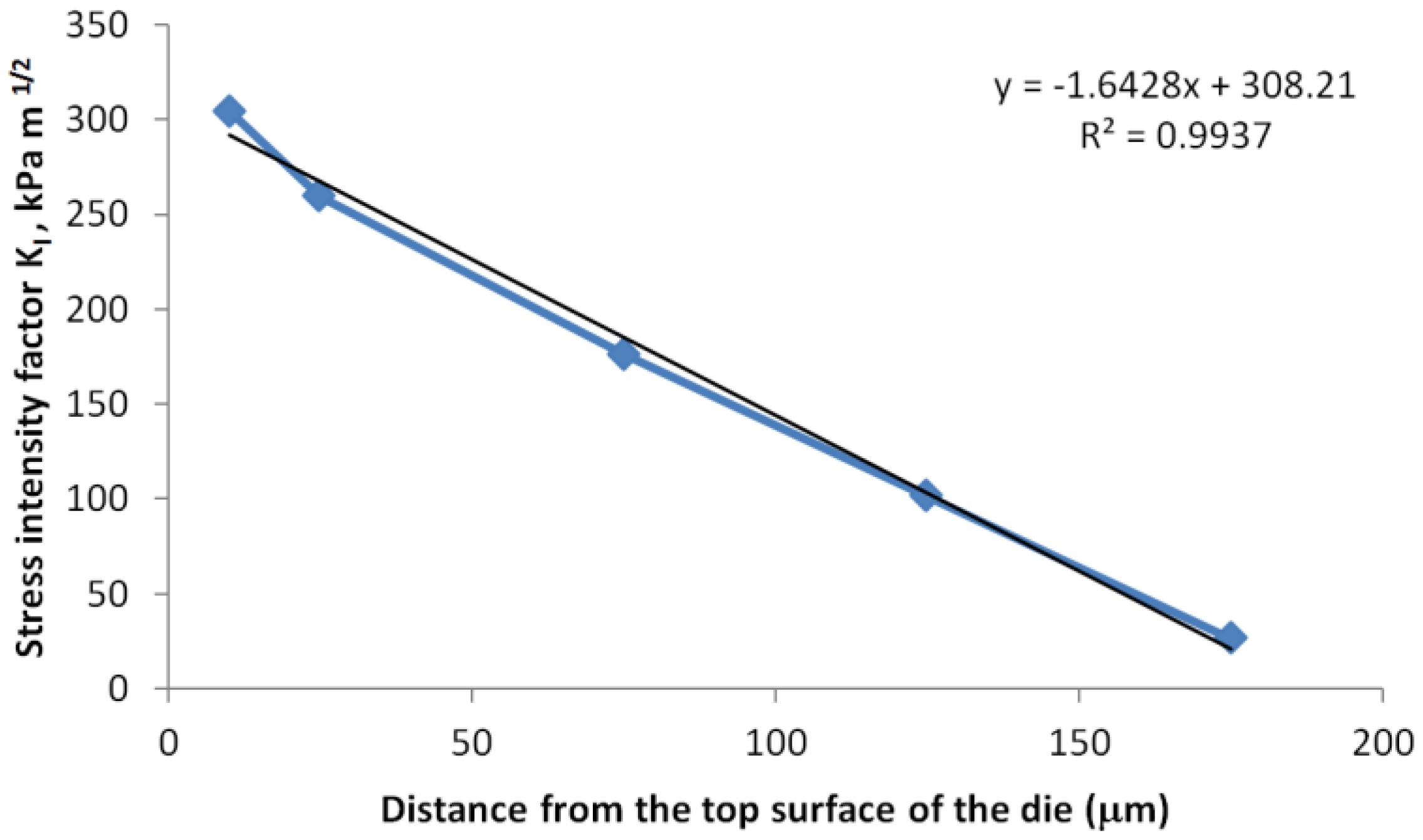

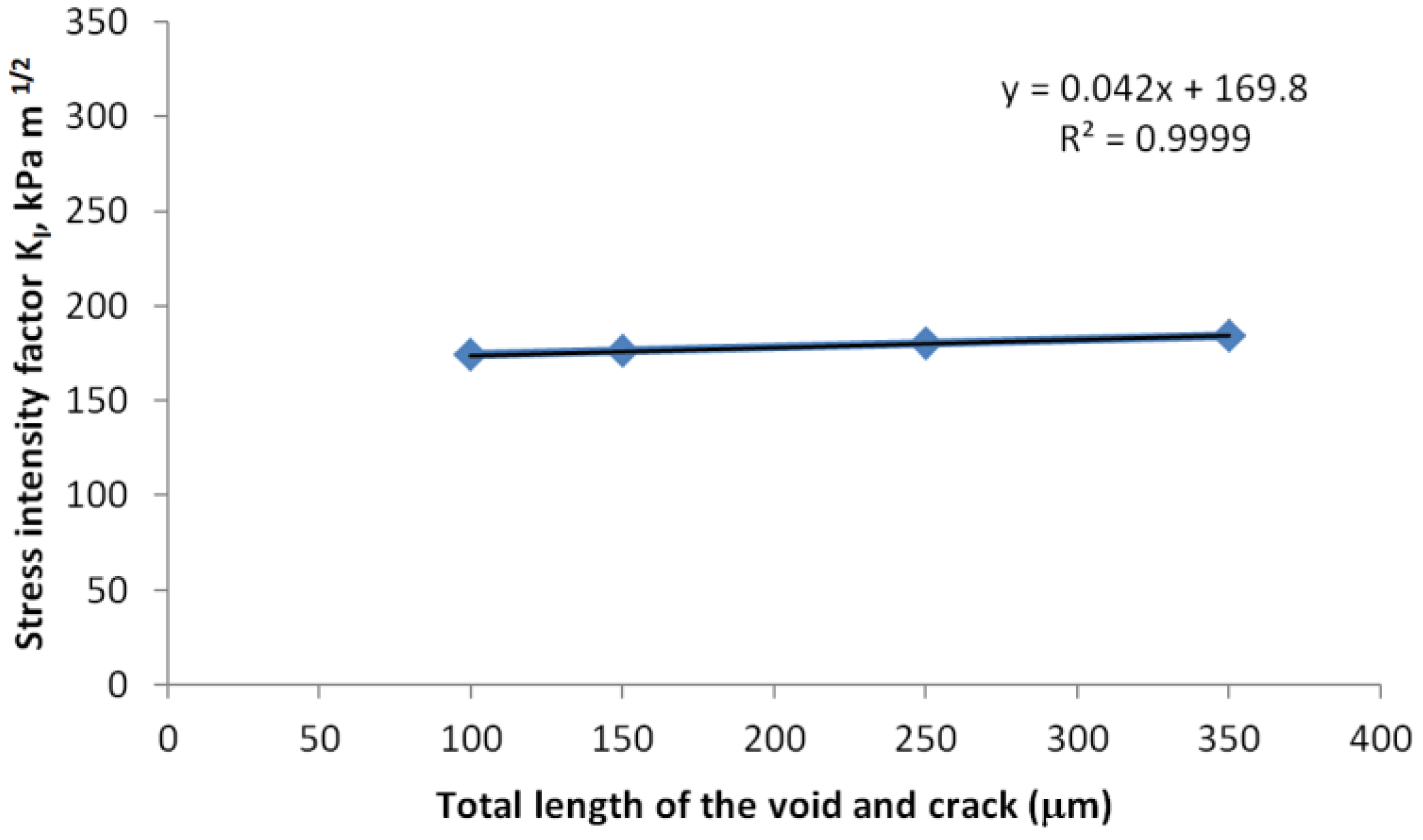

7.1. Effect of Crack Length and Crack Tip Location

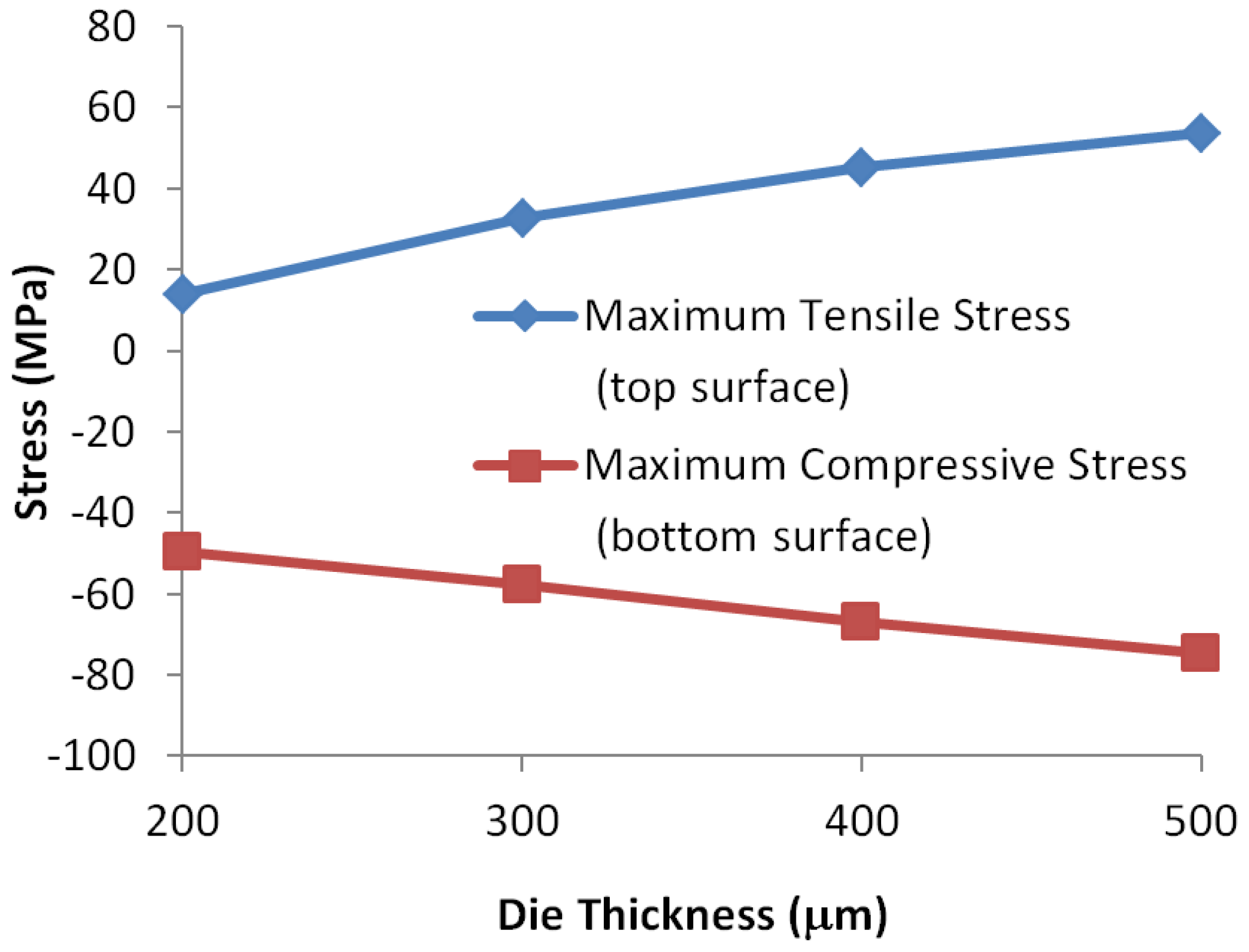

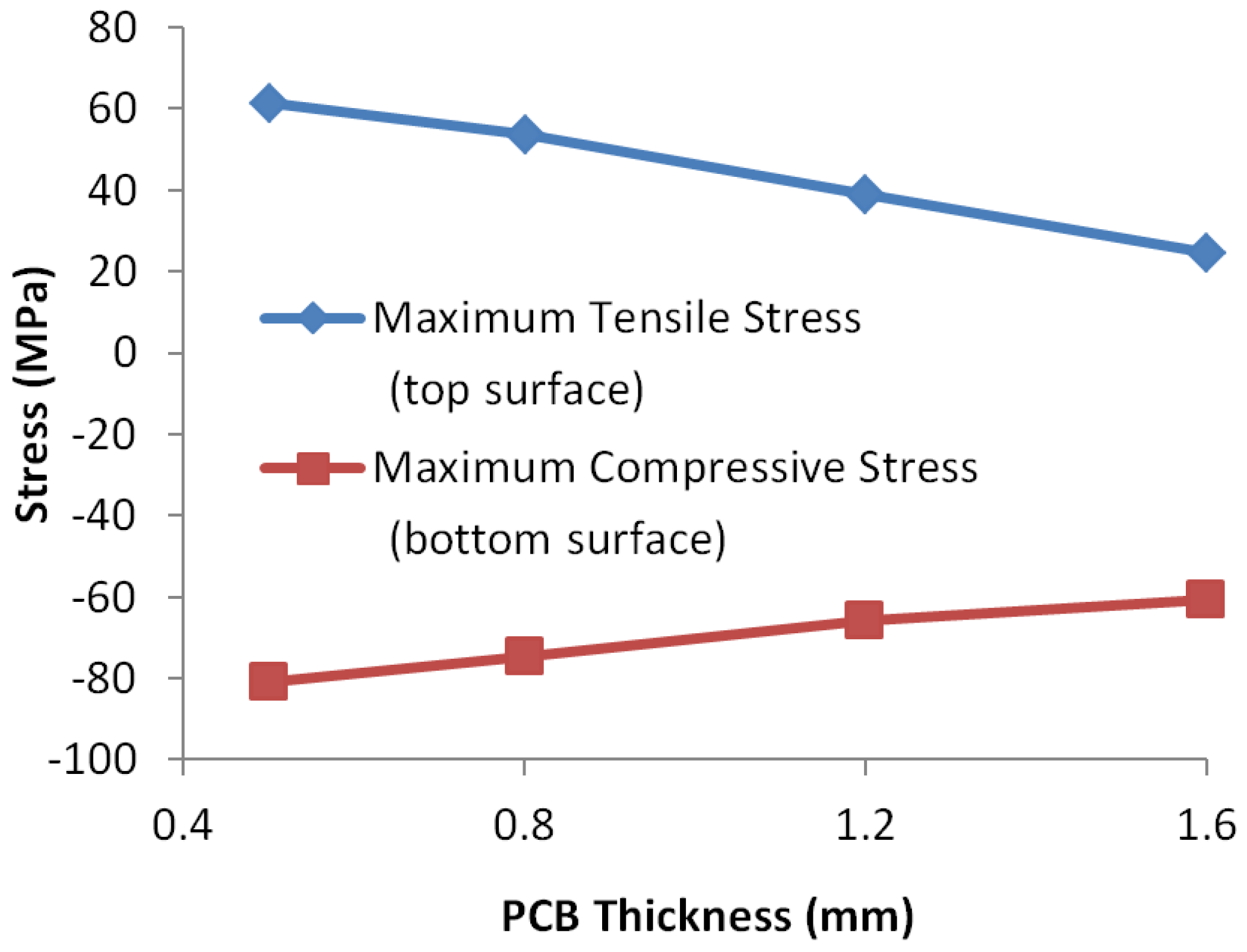

7.2. Effect of Die and Board Thickness

7.3. Possibility of Failure Due to Die Bending

8. Discussion: Reliability Risks of Poly-Si TSV in Sensor Assembled on Flexible Substrate

Parametric Study on Die Thickness and Substrate Thickness

9. Summary

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Gu, J.; Liu, B.; Yang, H.; Li, X. A fast and CMP-free TSV process based on wafer-level liquid-metal injection for MEMS packaging. In Proceedings of the IEEE 29th International Conference on Micro Electro Mechanical Systems (MEMS) 2016, Shanghai, China, 24–28 January 2016; pp. 569–572.

- Liu, D.; Park, S. Three-Dimensional and 2.5 Dimensional Interconnection Technology: State of the Art. J. Electron. Packag. 2014, 136. [Google Scholar] [CrossRef]

- Gong, J.; Sood, S. Wafer edge defect study of temporary bonded and thin wafers in TSV process flow. In Proceedings of the IEEE 65th Electronic Components and Technology Conference (ECTC) 2015, San Diego, CA, USA, 26–29 May 2015; pp. 1707–1712.

- Tan, C.S.; Chen, K.N.; Koester, S.J. 3D Integration for VLSI Systems; Pan Stanford: Boca Raton, FL, USA, 2011. [Google Scholar]

- Venkatadri, V.; Sammakia, B.; Srihari, K.; Santos, D. A Review of Recent Advances in Thermal Management in Three Dimensional Chip Stacks in Electronic Systems. J. Electron. Packag. 2011, 133. [Google Scholar] [CrossRef]

- Park, A.Y.; Chaparala, S.C.; Park, S. Risk assessment of the crack propagation and delamination of the Cu-to-Cu direct bonded (CuDB) interface. Microelectron. Reliab. 2016. [Google Scholar] [CrossRef]

- Tu, K.N. Reliability Challenges in 3D IC Packaging Technology. Microelectron. Reliab. 2011, 51, 517–533. [Google Scholar] [CrossRef]

- Wang, Z. 3-D Integration and Through-Silicon Vias in MEMS and Microsensors. J. Microelectromech. Syst. 2015, 24, 1211–1244. [Google Scholar] [CrossRef]

- Zoschke, K.; Manier, C.-A.; Wilke, M.; Jürgensen, N.; Oppermann, H.; Ruffieux, D.; Dekker, J.; Heikkinen, H.; Piazza, S.D.; Allegato, G.; et al. Hermetic wafer level packaging of MEMS components using through silicon via and wafer to wafer bonding technologies. In Proceedings of the IEEE 63rd Electronic Components and Technology Conference (ECTC) 2013, Las Vegas, NV, USA, 28–31 May 2013; pp. 1500–1507.

- Ramm, P.; Klumpp, A.; Weber, J. 3D integration technologies for MEMS/IC systems. In Proceedings of the IEEE Bipolar/BiCMOS Circuits and Technology Meeting 2009, Capri, Italy, 12–14 October 2009; pp. 138–141.

- Cao, Y.; Ning, W.; Luo, L. Wafer-Level Package with Simultaneous TSV Connection and Cavity Hermetic Sealing by Solder Bonding for MEMS Device. IEEE Trans. Electron. Packag. 2009, 32, 125–132. [Google Scholar]

- Ferrandon, C.; Greco, F.; Lagoutte, E.; Descours, P.; Enyedy, G.; Pellat, M.; Gillot, C.; Rey, P.; Mercier, D.; Cueff, M.; et al. Hermetic wafer-level packaging development for RF MEMS switch. In Proceedings of the IEEE 3rd Electronic System-Integration Technology Conference (ESTC), Berlin, Germany, 13–16 September 2010; pp. 1–6.

- Ogawa, S.; Soda, S.; Lee, S.-S.; Lzuo, S.; Yoshida, Y. F-MEMS switch with through-silicon via by the molten solder ejection method. Sens. Actuators A Phys. 2012, 191, 77–80. [Google Scholar] [CrossRef]

- Griffin, B.A.; Chandrasekaran, V.; Sheplak, M. Thermoelastic Ultrasonic Actuator with Piezoresistive Sensing and Integrated Through-Silicon Vias. J. Microelectromech. Syst. 2012, 21, 350–358. [Google Scholar] [CrossRef]

- Hirama, I. New MEMS sensor process by TSV technology for smaller packaging. In Proceedings of the 2015 International Conference on Electronic Packaging and iMAPS All Asia Conference (ICEP-IACC), Kyoto, Japan, 14–17 April 2015; pp. 456–459.

- Zimmer, F.; Lapisa, M.; Bakke, T.; Bring, M.; Stemme, G; Niklaus, F. One-megapixel monocrystalline-silicon micromirror array on CMOS driving electronics manufactured with very large-scale heterogeneous integration. J. Microelectromech. Syst. 2011, 20, 564–572. [Google Scholar] [CrossRef]

- Suhir, E. Analytical stress modeling for TSVs in 3D packaging. In Proceedings of the 31st Thermal Measurement, Modeling & Management Symposium (SEMI-THERM), San Jose, CA, USA, 15–19 March 2015.

- Frank, T.; Moreau, S.; Chappaz, C.; Leduc, P.; Arnaud, L.; Thuaire, A.; Chery, E.; Lorut, F.; Anghel, L.; Poupon, G. Reliability of TSV interconnects: Electromigration, thermal cycling, and impact on above metal level dielectric. Microelectron. Reliab. 2013, 53, 17–29. [Google Scholar] [CrossRef]

- Ding, Y.; Yan, Y.; Chen, Q.; Wang, S.; Su, R.; Dang, H. Analytical solution on interfacial reliability of 3-D through-silicon-via (TSV) containing dielectric liner. Microelectron. Reliab. 2014, 54, 1384–1391. [Google Scholar] [CrossRef]

- Lau, J.H.; Lee, C.; Premachandran, C.S.; Yu, A. Advanced MEMS Packaging, 1st ed.; McGraw-Hill Companies, Inc.: New York, NY, USA, 2009. [Google Scholar]

- Yun, C.H.; Brosnihan, T.J.; Webster, W.A.; Villarreal, J. Wafer-Level Packaging of MEMS Accelerometers with Through-Wafer Interconnects. In Proceedings of the IEEE Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2005; pp. 320–323.

- Sekiguchi, M.; Numata, H.; Sato, N.; Shirakawa, T.; Matsuo, M.; Yoshikawa, H.; Yanagida, M.; Nakayoshi, H.; Takahashi, K. Novel low cost integration of through chip interconnection and application to CMOS image sensor. In Proceedings of the IEEE 56th Electronic Components and Technology Conference, San Diego, CA, USA, 30 May–2 June 2006; pp. 1367–1374.

- Chung, H.; Tu, C.; Lwo, B.; Lee, C. A complete resistance extraction methodology and circuit models for typical TSV structures. Int. J. Electron. 2013, 100, 1256–1269. [Google Scholar] [CrossRef]

- Gagnard, X.; Mourier, T. Through silicon via: From the CMOS imager sensor wafer level package to the 3D integration. Microelectron. Eng. 2010, 87, 470–476. [Google Scholar] [CrossRef]

- Wang, M.; Hung, C.; Kao, C.; Lee, P.; Chen, C.; Huang, C.; Tong, H. TSV Technology for 2.5D IC Solution. In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012.

- Liu, X.; Chen, Q.; Dixit, P.; Chatterjee, R.; Tummala, R.R.; Sitaraman, S.K. Failure mechanisms and optimum design for electroplated copper Through-Silicon Vias (TSV). In Proceedings of the Electronic Components and Technology Conference, San Diego, CA, USA, 26–29 May 2009.

- Lu, K.H. Thermo-Mechanical Reliability of 3-D Interconnects Containing Through-Silicon-Vias (TSVs). Ph.D. Thesis, The University of Texas at Austin, Austin, TX, USA, 2010. [Google Scholar]

- Sharpe, W.N.; Yuan, B.; Vaidyanathan, R.; Edwards, R.L. Measurements of Young’s modulus, Poisson’s ratio, and tensile strength of polysilicon. In Proceedings of the Tenth Annual International Workshop on Micro Electro Mechanical Systems, MEMS ’97, Nagoya, Japan, 26–30 January 1997; pp. 424–429.

- Pares, G.; Bresson, N.; Moreau, S.; Lapras, V.; Henry, D.; Sillon, N. Effects of stress in polysilicon VIA—First TSV technology. In Proceedings of the 2010 12th Electronics Packaging Technology Conference (EPTC), Singapore, 8–10 December 2010; pp. 333–337.

- Pares, G.; De Crecy, F.; Moreau, S.; Maurice, C.; Borbely, A.; Mazuir, J.; Chapelon, L.L.; Sillon, N. Assessment and Characterization of Stress Induced by Via-First TSV Technology. J. Microelectron. Electron. Packag. 2011, 8, 129–139. [Google Scholar] [CrossRef]

- Gong, J.; Ume, I.C. Nondestructive Evaluation of Poor-Wetted Lead-Free Solder Bumps in Ball Grid Array Packages Using Laser Ultrasound and Interferometric Technique. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 1301–1309. [Google Scholar] [CrossRef]

- Ume, I.C.; Gong, J.; Ahmad, R.; Valdes, A. Laser Ultrasonic Inspection of Solder Bumps in Flip Chip Packages Using Virtual Package Device as Reference. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1739–1746. [Google Scholar] [CrossRef]

- Gong, J.; Ume, C.; Akinade, K.; Rogers, B.; Guirguis, C.; Chan, D.; Escobar, C. Non-Destructive Evaluation of Solder Bump Quality Under Mechanical Bending Using Laser Ultrasonic Technique. In Proceedings of the SMTA International Conference, Rosemont, IL, USA, 28 September–2 October 2014.

- Ume, I.C.; Gong, J. Evaluation of Lead-Free Solder Bump Voiding Ball Grid Array Packages Using Laser Ultrasound and Interferometric Technique. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 1310–1320. [Google Scholar] [CrossRef]

- Gong, J.; Ume, I.C.; Akinade, K.; Chaudhuri, A.R. Quality Evaluation of Solder Bump in PBGA Package for Commercial Product Application Using Laser Ultrasonic Technique. In Proceedings of the ASME 2013 International Mechanical Engineering Congress and Exposition, San Diego, CA, USA, 15–21 November 2013; Volume 10.

- Krueger, R. Virtual crack closure technique: History, approach, and applications. Appl. Mech. Rev. 2004, 57, 109–143. [Google Scholar] [CrossRef]

- Sun, C.T.; Jin, Z.H. Chapter 4—Energy Release Rate. In Fracture Mechanics, 1st ed.; Sun, C.T., Jin, Z.H., Eds.; Academic Press: Boston, MA, USA, 2012; pp. 77–103. [Google Scholar]

- Chasiotis, I.; Cho, S.W.; Jonnalagadda, K. Fracture Toughness and Subcritical Crack Growth in Polycrystalline Silicon. J. Appl. Mech. 2005, 73, 714–722. [Google Scholar] [CrossRef]

- Timoshenko, S. Analysis of Bi-Metal Thermostats. J. Opt. Soc. Am. 1925, 11, 233–255. [Google Scholar] [CrossRef]

- Suhir, E. Stresses in Bi-Metal Thermostats. J. Appl. Mech. 1986, 53, 657–660. [Google Scholar] [CrossRef]

- Suhir, E. Interfacial Stresses in Bimetal Thermostats. J. Appl. Mech. 1989, 56, 595–600. [Google Scholar] [CrossRef]

- Mishkevich, V.; Suhir, E. Simplified Engineering Approach for the evaluation of Thermally Induced Stresses in Bi-Material Microelectronic Structures. In Proceedings of the ASME Structural Analysis in Microelectronics and Fiber Optics, EEP, New Orleans, LA, USA, 28 November–3 December 1993; pp. 127–133.

- Tsai, M.Y.; Hsu, C.H.; Han, C.N. A Note on Suhir’s Solution of Thermal Stresses for a Die-Substrate Assembly. J. Electron. Packag. 2004, 126, 115–119. [Google Scholar] [CrossRef]

| Material | Young’s Modulus (GPa) | Poisson’s Ratio | CTE (ppm/°C) |

|---|---|---|---|

| Silicon | = = 169; = 130 = 50.8; = = 79.5 | = 0.062 = = 0.36 | 2.6 |

| SiO2 | 75 | 0.17 | 0.5 |

| Al | 69 | 0.35 | 22.2 |

| Copper | 110 | 0.35 | 16.4 |

| Insulation polymer (Type A) | 2.3 to 9.2 | 0.26 | 25 to 100 |

| FR4 (Type B) | 22 | 0.28 | 18 |

| Au (Type B) | 2.5 | 0.42 | 14.4 |

| Polyimide film (Type B) | 2.5 | 0.34 | 20 (20 °C); 30 (100 °C); 40 (150 °C) |

| Test Matrix | Total Length of Voids and Cracks (μm) | ||||

|---|---|---|---|---|---|

| 100 | 150 | 250 | 350 | ||

| Crack tip location (distance to die surface, μm) | 10 | √ | |||

| 25 | √ | ||||

| 75 | √ | √ | √ | √ | |

| 125 | √ | ||||

| 175 | √ | ||||

| Test Matrix | Die Thickness (μm) | ||||

|---|---|---|---|---|---|

| 200 | 300 | 400 | 500 | ||

| PCB thickness (mm) | 0.5 | √ | |||

| 0.8 | √ | √ | √ | √ | |

| 1.2 | √ | ||||

| 1.6 | √ | ||||

| Parameter | PCB (0.8 mm) | Flexible Substrate (49 μm) |

|---|---|---|

| Tensile bending stress on the die (MPa) | 53.7 | 14.2 |

| Stress-intensity factor KI (kPam1/2) | 304.4 | 69.3 |

| Parameter | Die Thickness (μm) | ||

|---|---|---|---|

| 500 | 400 | 300 | |

| Tensile bending stress on the die (MPa) | 14.2 | 18.2 | 24.9 |

| Stress-intensity factor KI (kPam1/2) | 69.3 | 89.2 | 120.2 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shao, S.; Liu, D.; Niu, Y.; O’Donnell, K.; Sengupta, D.; Park, S. A Study on the Thermomechanical Reliability Risks of Through-Silicon-Vias in Sensor Applications. Sensors 2017, 17, 322. https://doi.org/10.3390/s17020322

Shao S, Liu D, Niu Y, O’Donnell K, Sengupta D, Park S. A Study on the Thermomechanical Reliability Risks of Through-Silicon-Vias in Sensor Applications. Sensors. 2017; 17(2):322. https://doi.org/10.3390/s17020322

Chicago/Turabian StyleShao, Shuai, Dapeng Liu, Yuling Niu, Kathy O’Donnell, Dipak Sengupta, and Seungbae Park. 2017. "A Study on the Thermomechanical Reliability Risks of Through-Silicon-Vias in Sensor Applications" Sensors 17, no. 2: 322. https://doi.org/10.3390/s17020322