Guidelines for Designing Surface Ion Traps Using the Boundary Element Method

Abstract

:1. Introduction

2. Background

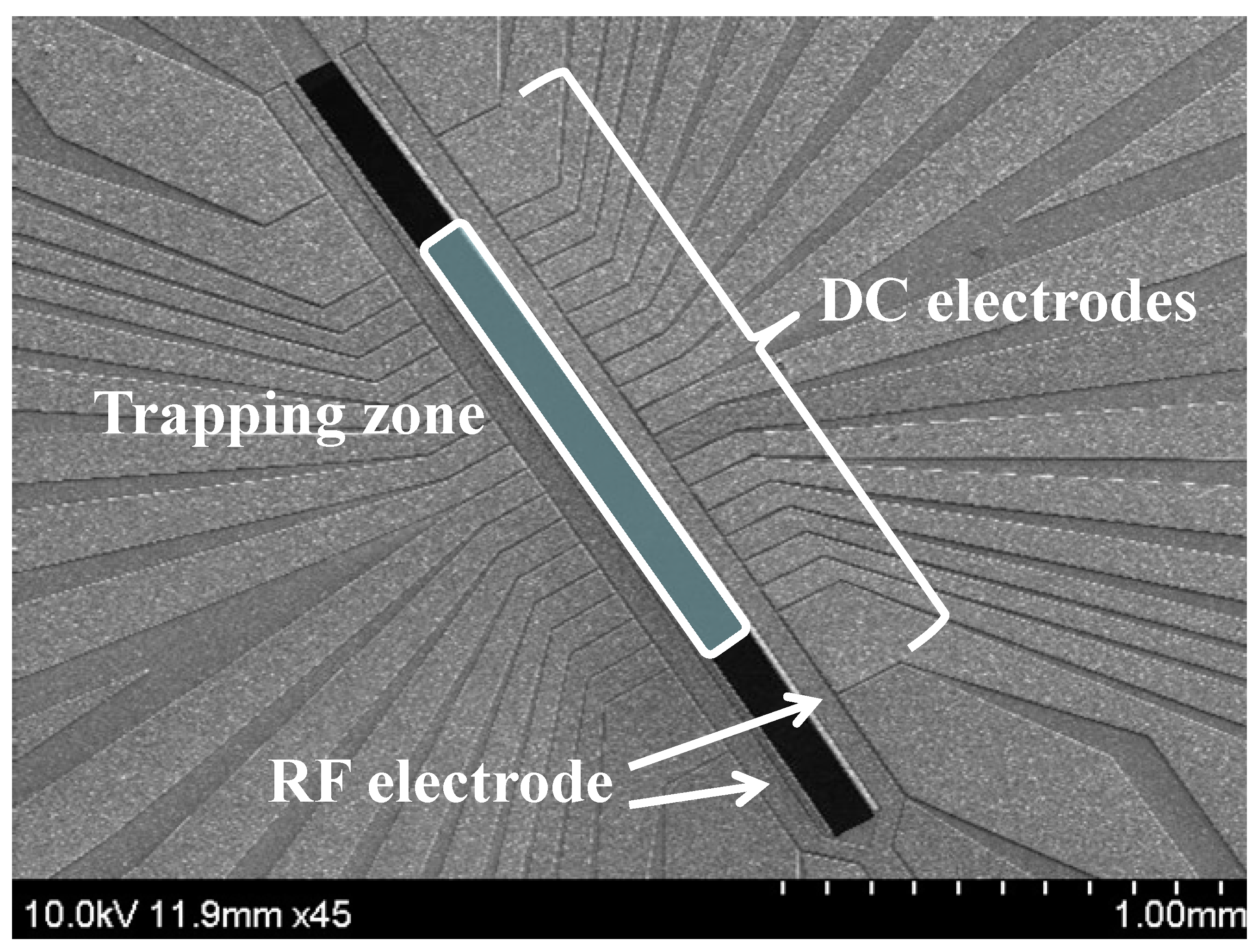

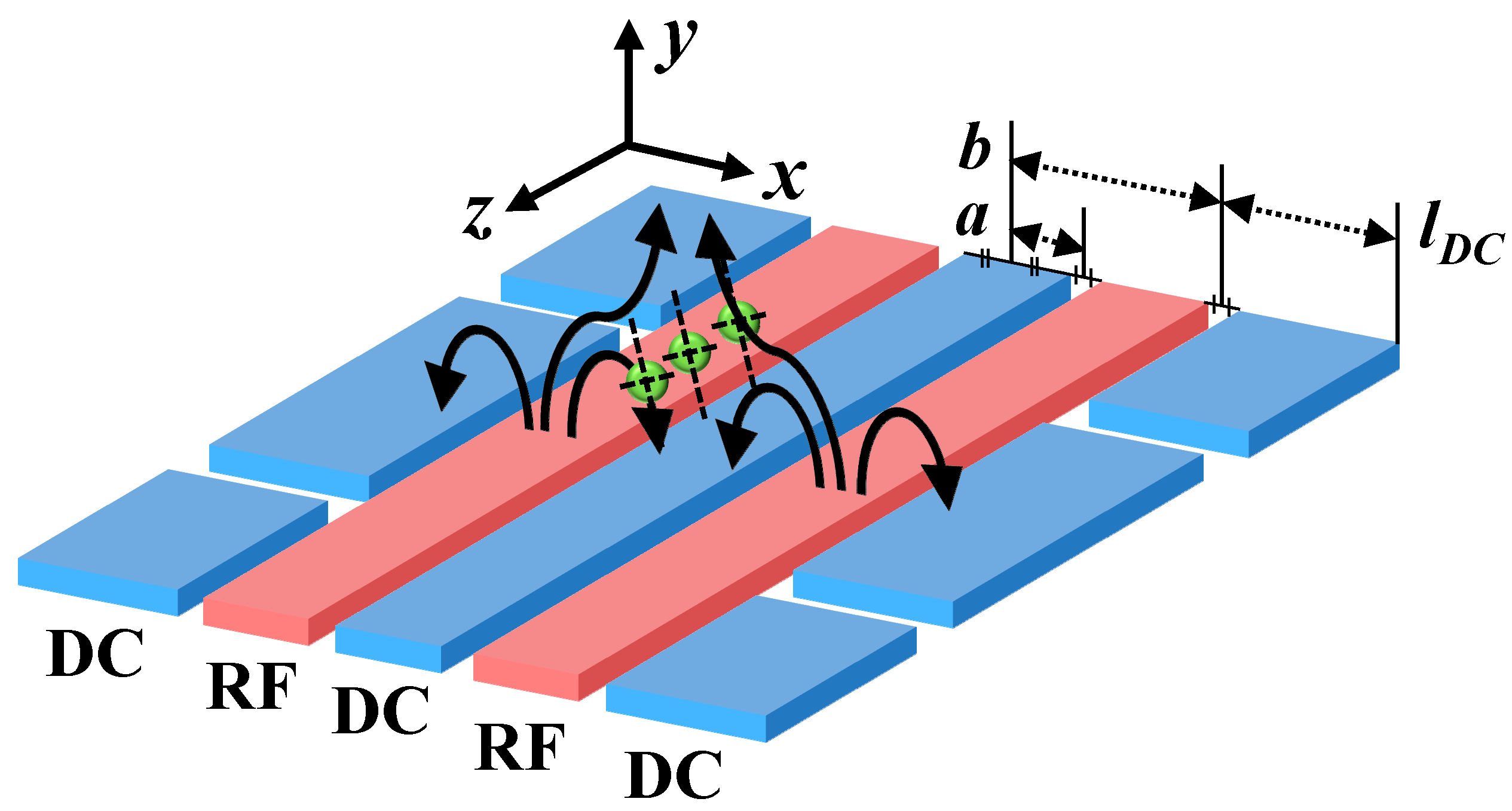

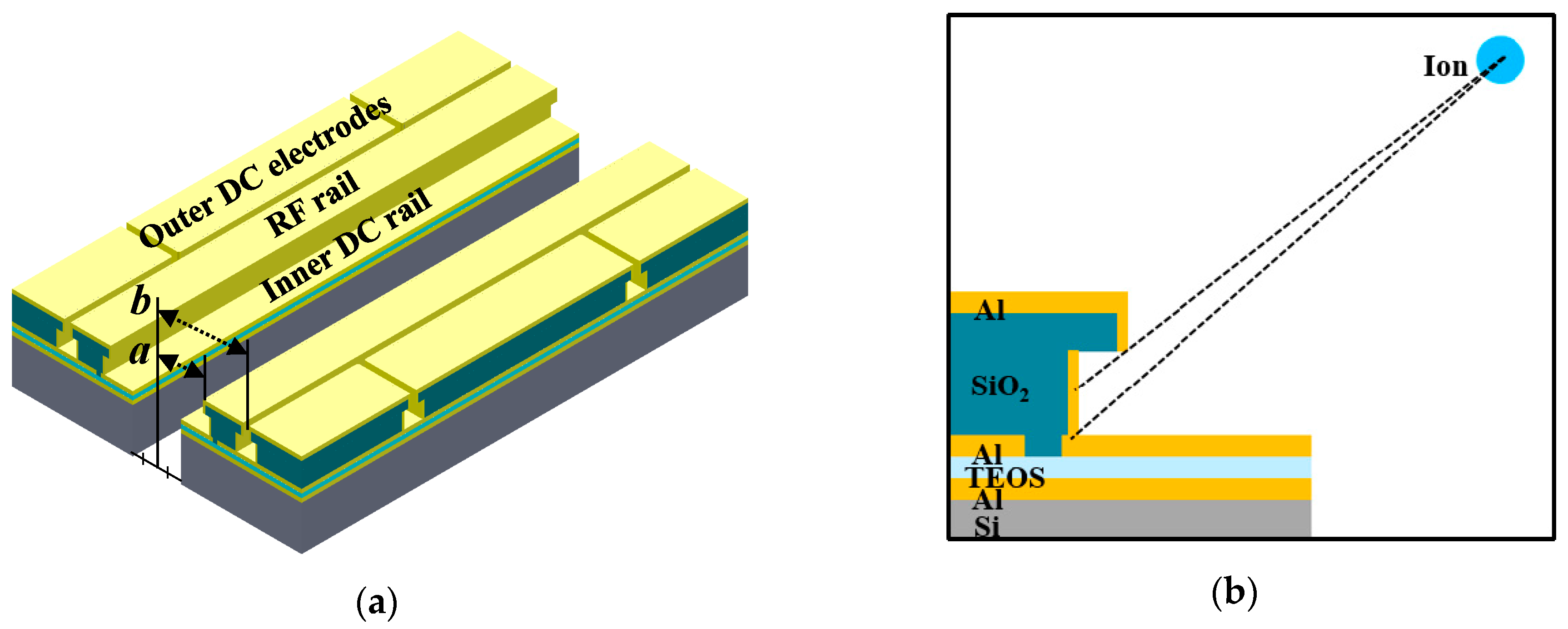

2.1. Principle of Surface Ion Traps

2.2. Specifications of Surface Ion Traps

2.2.1. Trap Depth

2.2.2. q-Parameter

2.2.3. Secular Frequency

2.2.4. Ion Height

2.3. Analytic Solutions

2.4. BEM Simulations

3. Design Methodology for Surface Ion-Trap Chips

3.1. Basic Assumptions

3.2. Shape and Size of the Chip

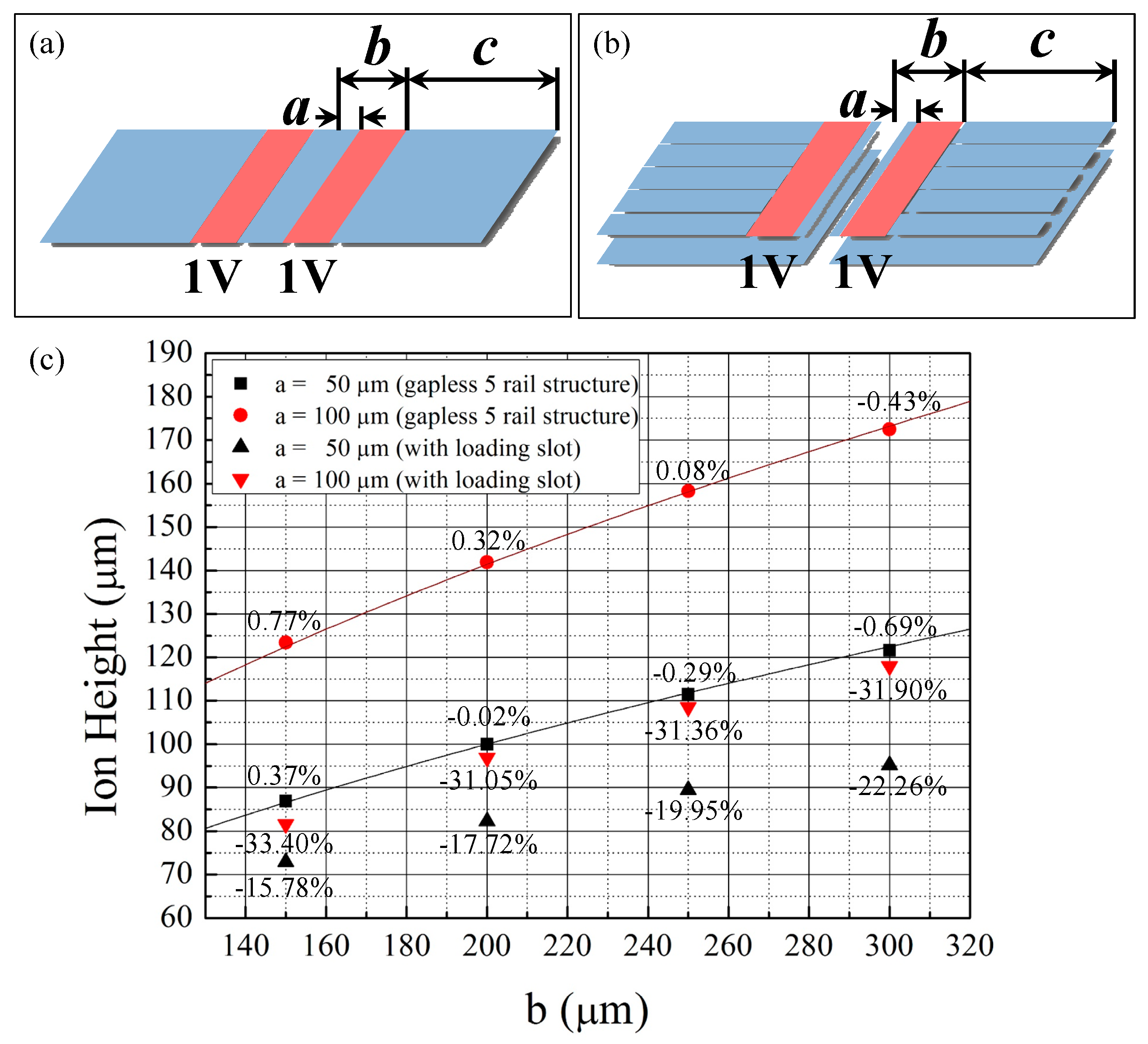

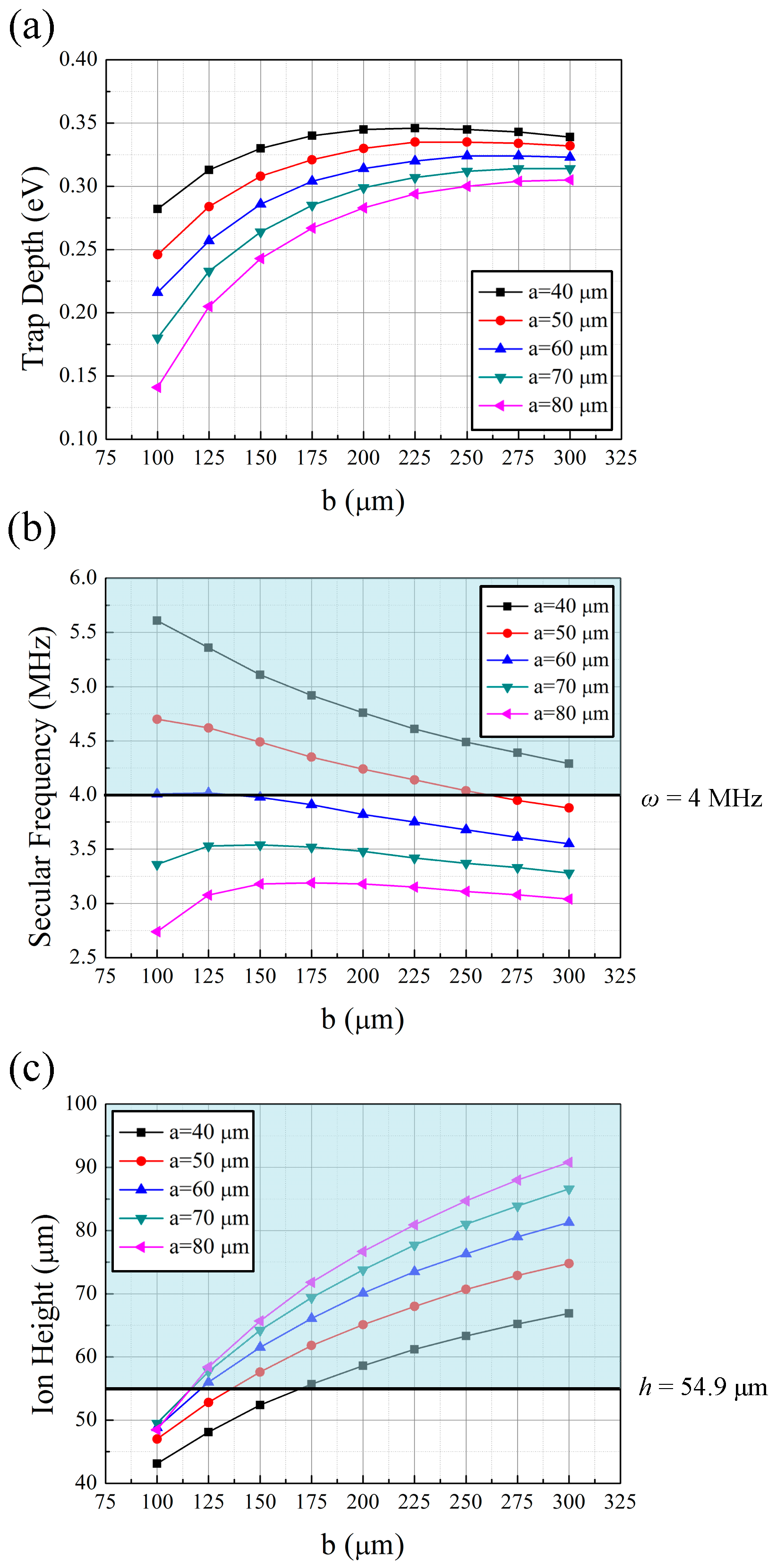

3.3. Design of RF electrodes

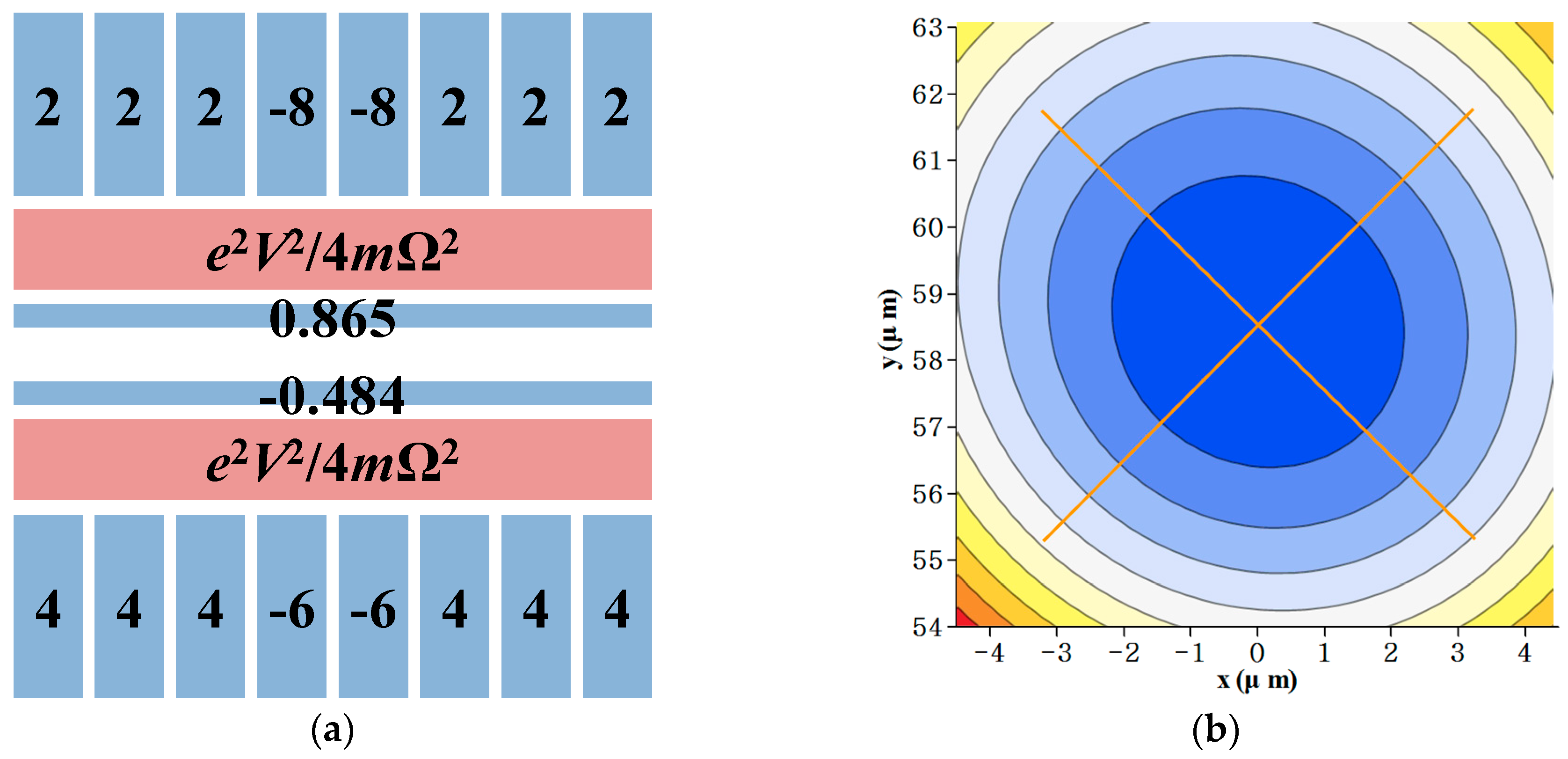

3.4. Investigation of Effects of DC Voltages

4. Case Study of the Design Methodology

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations

| AC | Alternating current |

| BEM | Boundary element method |

| DC | Direct current |

| FEM | Finite element method |

| RF | Radio frequency |

| SEM | Scanning electron micrograph |

| TEOS | Tetraethyl orthosilicate |

| UV | Ultra violet |

References

- Crain, S.; Mount, E.; Baek, S.; Kim, J. Individual addressing of trapped 171Yb+ ion qubits using a microelectromechanical systems-based beam steering system. Appl. Phys. Lett. 2014, 105, 181115. [Google Scholar] [CrossRef]

- Ospelkaus, C.; Warring, U.; Colombe, Y.; Brown, K.R.; Amini, J.M.; Leibfried, D.; Wineland, D.J. Microwave quantum logic gates for trapped ions. Nature 2011, 476, 181–184. [Google Scholar] [CrossRef] [PubMed]

- Blatt, R.; Wineland, D. Entangled states of trapped atomic ions. Nature 2008, 453, 1008–1015. [Google Scholar] [CrossRef] [PubMed]

- Udem, T.; Holzwarth, R.; Hänsch, T.W. Optical frequency metrology. Nature 2002, 416, 233–237. [Google Scholar] [CrossRef] [PubMed]

- Margolis, H.S.; Barwood, G.P.; Huang, G.; Klein, H.A.; Lea, S.N.; Szymaniec, K.; Gill, P. Hertz-level measurement of the optical clock frequency in a single 88Sr+ ion. Science 2004, 306, 1355–1358. [Google Scholar] [CrossRef] [PubMed]

- Dawson, P.H. Quadrupole Mass Spectrometry and Its Applications; Elsevier: Amsterdam, The Netherlands, 2013. [Google Scholar]

- Kielpinski, D.; Monroe, C.; Wineland, D.J. Architecture for a large-scale ion-trap quantum computer. Nature 2002, 417, 709–711. [Google Scholar] [CrossRef] [PubMed]

- Stick, D.; Hensinger, W.K.; Olmschenk, S.; Madsen, M.J.; Schwab, K.; Monroe, C. Ion trap in a semiconductor chip. Nat. Phys. 2006, 2, 36–39. [Google Scholar] [CrossRef]

- Seidelin, S.; Chiaverini, J.; Reichle, R.; Bollinger, J.J.; Leibfried, D.; Britton, J.; Wesenberg, J.H.; Blakestad, R.B.; Epstein, R.J.; Hume, D.B.; et al. Microfabricated surface-electrode ion trap for scalable quantum information processing. Phys. Rev. Lett. 2006, 96, 253003. [Google Scholar] [CrossRef] [PubMed]

- Monroe, C.; Kim, J. Scaling the ion trap quantum processor. Science 2013, 339, 1164–1169. [Google Scholar] [CrossRef] [PubMed]

- Cho, D.D.; Hong, S.; Lee, M.; Kim, T. A review of silicon microfabricated ion traps for quantum information processing. Micro Nano Syst. Lett. 2015, 3, 1–12. [Google Scholar] [CrossRef]

- Stick, D.; Fortier, K.M.; Haltli, R.; Highstrete, C.; Moehring, D.L.; Tigges, C.; Blain, M.G. Demonstration of a Microfabricated Surface Electrode Ion Trap. 2010. arXiv:1008.0990; arXiv.org e‐Print archive. Available online: http://arxiv.org/pdf/1008.0990v2.pdf (accessed on 27 April 2016).

- Lacroûte, C.; Souidi, M.; Bourgeois, P.Y.; Millo, J.; Saleh, K.; Bigler, E.; Boudot, R.; Giordano, V.; Kersalé, Y. Compact Yb+ Optical Atomic Clock Project: Design Principle and Current Status. 2016. arXiv:1603.05816, arXiv.org e‐Print archive. Available online: http://arxiv.org/pdf/1603.05816v1.pdf (accessed on 27 April 2016).

- Amini, J.M.; Britton, J.; Leibfried, D.; Wineland, D.J. Atom Chips; Wiley: New York, NY, USA, 2008. [Google Scholar]

- House, M.G. Analytic model for electrostatic fields in surface-electrode ion traps. Phys. Rev. A 2008, 78, 033402. [Google Scholar] [CrossRef]

- Wesenberg, J.H. Electrostatics of surface-electrode ion traps. Phys. Rev. A 2008, 78, 063410. [Google Scholar] [CrossRef]

- Chiaverini, J.; Blakestad, R.B.; Britton, J.; Jost, J.D.; Langer, C.; Leibfried, D.; Ozeri, R.; Wineland, D.J. Surface-electrode architecture for ion-trap quantum information processing. Quantum Inf. Comput. 2005, 5, 419–439. [Google Scholar]

- Madsen, M.J.; Hensinger, W.K.; Stick, D.; Rabchuk, J.A.; Monroe, C. Planar ion trap geometry for microfabrication. Appl. Phys. B 2004, 78, 639–651. [Google Scholar] [CrossRef]

- Pearson, C.E.; Leibrandt, D.R.; Bakr, W.S.; Mallard, W.J.; Brown, K.R.; Chuang, I.L. Experimental investigation of planar ion traps. Phys. Rev. A 2006, 73, 032307. [Google Scholar] [CrossRef]

- Brownnutt, M.; Wilpers, G.; Gill, P.; Thompson, R.C.; Sinclair, A.G. Monolithic microfabricated ion trap chip design for scaleable quantum processors. New J. Phys. 2006, 8, 232. [Google Scholar] [CrossRef]

- Allcock, D.T.C.; Sherman, J.A.; Stacey, D.N.; Burrell, A.H.; Curtis, M.J.; Imreh, G.; Linke, N.M.; Szwer, D.J.; Webster, S.C.; Steane, A.M.; et al. Implementation of a symmetric surface-electrode ion trap with field compensation using a modulated Raman effect. New J. Phys. 2010, 12, 053026. [Google Scholar] [CrossRef]

- Nizamani, A.H.; Hensinger, W.K. Optimum electrode configurations for fast ion separation in microfabricated surface ion traps. Appl. Phys. B 2012, 106, 327–338. [Google Scholar] [CrossRef]

- Siverns, J.D.; Weidt, S.; Lake, K.; Lekitsch, B.; Hughes, M.D.; Hensinger, W.K. Optimization of two-dimensional ion trap arrays for quantum simulation. New J. Phys. 2012, 14, 085009. [Google Scholar] [CrossRef]

- Doret, S.C.; Amini, J.M.; Wright, K.; Volin, C.; Killian, T.; Ozakin, A.; Denison, D.; Hayden, H.; Pai, C.S.; Slusher, R.E.; et al. Controlling trapping potentials and stray electric fields in a microfabricated ion trap through design and compensation. New J. Phys. 2012, 14, 073012. [Google Scholar] [CrossRef]

- Amini, J.M.; Uys, H.; Wesenberg, J.H.; Seidelin, S.; Britton, J.; Bollinger, J.J.; Leibfried, D.; Ospelkaus, C.; VanDevender, A.P.; Wineland, D.J. Toward scalable ion traps for quantum information processing. New J. Phys. 2010, 12, 033031. [Google Scholar] [CrossRef]

- Moehring, D.L.; Highstrete, C.; Stick, D.; Fortier, K.M.; Haltli, R.; Tigges, C.; Blain, M.G. Design, fabrication and experimental demonstration of junction surface ion traps. New J. Phys. 2011, 13, 075018. [Google Scholar] [CrossRef]

- Wright, K.; Amini, J.M.; Faircloth, D.L.; Volin, C.; Doret, S.C.; Hayden, H.; Pai, C.S.; Landgren, D.W.; Denison, D.; Killian, T.; et al. Reliable transport through a microfabricated X-junction surface-electrode ion trap. New J. Phys. 2013, 15, 033004. [Google Scholar] [CrossRef]

- Stick, D.L. Fabrication and Characterization of Semiconductor Ion Traps for Quantum Information Processing. Ph.D. Thesis, University of Michigan, Ann Arbor, MI, USA, September 2007. [Google Scholar]

- Splatt, F.E. Development and Operation of Miniaturised Ion Traps for Scalable Quantum Computation. Ph.D. Thesis, University of Innsbruck, Innsbruck, Austria, August 2009. [Google Scholar]

- Schulz, S.A. Scalable Microchip Ion Traps for Quantum Computation. Available online: https://www.quantenbit.physik.uni-mainz.de/files/2015/11/pub_phd_Schulz2009.pdf (accessed on 27 April 2016).

- Britton, J. Microfabrication Techniques for Trapped Ion Quantum Information Processing. Ph.D. Thesis, University of Colorado, Boulder, MT, USA, December 2008. [Google Scholar]

- Leibrandt, D.R.; Labaziewicz, J.; Clark, R.J.; Chuang, I.L.; Epstein, R.J.; Ospelkaus, C.; Sesenberg, J.H.; Bollinger, J.J.; Leibfried, D.; Wineland, D.J.; et al. Demonstration of a scalable, multiplexed ion trap for quantum information processing. Quantum Inf. Comput. 2009, 9, 901–919. [Google Scholar]

- Allcock, D.T.C.; Harty, T.P.; Ballance, C.J.; Keitch, B.C.; Linke, N.M.; Stacey, D.N.; Lucas, D.M. A microfabricated ion trap with integrated microwave circuitry. Appl. Phys. Lett. 2013, 102, 044103. [Google Scholar] [CrossRef]

- Niedermayr, M.; Lakhmanskiy, K.; Kumph, M.; Partel, S.; Edlinger, J.; Brownnutt, M.; Blatt, R. Cryogenic Silicon Surface Ion Trap. New J. Phys. 2014. [Google Scholar] [CrossRef]

- Singer, K.; Poschinger, U.; Murphy, M.; Ivanov, P.; Ziesel, F.; Calarco, T.; Schmidt-Kaler, F. Colloquium: Trapped ions as quantum bits: Essential numerical tools. Rev. Mod. Phys. 2010, 82, 2609. [Google Scholar] [CrossRef]

- Leibfried, D.; Blatt, R.; Monroe, C.; Wineland, D. Quantum dynamics of single trapped ions. Rev. Mod. Phys. 2003, 75, 281. [Google Scholar] [CrossRef]

- Ozakin, A.; Shaikh, F. Stability Analysis of Surface Ion Traps. J. Appl. Phys. 2012. [Google Scholar] [CrossRef]

- Hucul, D.; Yeo, M.; Olmschenk, S.; Monroe, C.; Hensinger, W.K.; Rabchuk, J. On the transport of atomic ions in linear and multidimensional ion trap arrays. Quantum Inf. Comput. 2008, 8, 501–578. [Google Scholar]

- Zhu, S.L.; Monroe, C.; Duan, L.M. Trapped ion quantum computation with transverse phonon modes. Phys. Rev. Lett. 2006, 97, 050505. [Google Scholar] [CrossRef] [PubMed]

- Cirac, J.I.; Zoller, P. Quantum computations with cold trapped ions. Phys. Rev. Lett. 1995, 74, 4091. [Google Scholar] [CrossRef] [PubMed]

- Svelto, O. Principles of Lasers; Springer: New York, NY, USA, 2010. [Google Scholar]

- Wilpers, G.; See, P.; Gill, P.; Sinclair, A.G. A monolithic array of three-dimensional ion traps fabricated with conventional semiconductor technology. Nat. Nanotechnol. 2012, 7, 572–576. [Google Scholar] [CrossRef] [PubMed]

- Nagata, M.; Yokoi, Y.; Miyachi, I. Electrical breakdown characteristics in high-temperature gases. Electr. Eng. Jan. 1977, 97, 1–6. [Google Scholar] [CrossRef]

- Gerhard, A.; Kurz, M.; Brutscher, J.; Klein, H.; Schempp, A. RF sparking experiments at 108.5 and 216 MHz. IEEE Trans. Electr. Insul. 1989, 24, 1033–1036. [Google Scholar] [CrossRef]

- Blackburn, A.M.; Hasko, D.G.; Ahmed, H.; Williams, D.A. Tungsten pedestal structure for nanotriode devices. J. Vac. Sci. Technol. B 2004, 22, 1298–1302. [Google Scholar] [CrossRef]

- Guise, N.D.; Fallek, S.D.; Stevens, K.E.; Brown, K.R.; Volin, C.; Harter, A.W.; Amini, J.; Higashi, R.E.; Lu, S.T.; Chanhvongsak, H.M.; et al. Ball-grid array architecture for microfabricated ion traps. J. Appl. Phys. 2015, 117, 174901. [Google Scholar] [CrossRef]

- Olmschenk, S.; Younge, K.C.; Moehring, D.L.; Matsukevich, D.N.; Maunz, P.; Monroe, C. Manipulation and detection of a trapped Yb+ hyperfine qubit. Phys. Rev. A 2007, 76, 052314. [Google Scholar] [CrossRef]

- Reichle, R.; Leibfried, D.; Blakestad, R.B.; Britton, J.; Jost, J.D.; Knill, E.; Langer, C.; Ozeri, R.; Seidelin, S.; Wineland, D.J. Transport dynamics of single ions in segmented microstructured Paul trap arrays. Fortschr. Phys. 2006, 54, 666–685. [Google Scholar] [CrossRef]

- Steane, A. The ion trap quantum information processor. Appl. Phys. B Lasers Opt. 1997, 64, 623–643. [Google Scholar] [CrossRef]

| Ref No. | a (µm) | b (µm) | VRF (V) | ΩRF/2π (MHz) | Ion Species | Trap Depth (meV) | q-Parameter | Radial Secular Frequency (MHz) | Ion Height (µm) |

|---|---|---|---|---|---|---|---|---|---|

| [12] | 77 | 137 | 50–140 | 33 | 40Ca+ | - | 0.25–0.34 * | 3–4 | 84 |

| [21] | 100 | 247 | 223 | 25.8 | Ca+ | 188 | 0.43 | 4.02 | 150 |

| [24] | asymmetric | 100 | 60 | 40Ca+ | - | 0.16–0.19 * | 3.5–4 | 63 | |

| [25] | asymmetric | 51 | 90.7 | 24Mg+ | - | 0.25 * | 8 | 40 | |

| [27] | 44 | 84 | 91 | 58.55 | 40Ca+ | - | 0.05–0.12 * | 1–2.5 | 60 |

| [32] | 75 | 95 | 155 | 40.6 | 88Sr+ | 25 | 0.15 *, 0.12 * | 2.1, 1.7 | 79 |

| [33] | 45 | 136 | 72 | 38.7 | 43Ca+ | 59 | 0.3 | 4 | 75 |

| [34] | asymmetric | 140 | 20.6 | 40Ca+ | 75 | - | - | 230 | |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hong, S.; Lee, M.; Cheon, H.; Kim, T.; Cho, D.-i.“. Guidelines for Designing Surface Ion Traps Using the Boundary Element Method. Sensors 2016, 16, 616. https://doi.org/10.3390/s16050616

Hong S, Lee M, Cheon H, Kim T, Cho D-i“. Guidelines for Designing Surface Ion Traps Using the Boundary Element Method. Sensors. 2016; 16(5):616. https://doi.org/10.3390/s16050616

Chicago/Turabian StyleHong, Seokjun, Minjae Lee, Hongjin Cheon, Taehyun Kim, and Dong-il “Dan” Cho. 2016. "Guidelines for Designing Surface Ion Traps Using the Boundary Element Method" Sensors 16, no. 5: 616. https://doi.org/10.3390/s16050616