Technical Note

# A Dynamic Instrumentation Amplifier for Low-Power and Low-Noise Biopotential Acquisition

Jongpal Kim<sup>1</sup> and Hyoungho Ko<sup>2,\*</sup>

- <sup>1</sup> Samsung Electronics Inc., Suwon 16678, Korea; jongpalk@samsung.com

- <sup>2</sup> Department of Electronics, Chungnam National University, Daejeon 34134, Korea

- \* Correspondence: hhko@cnu.ac.kr; Tel.: +82-42-821-5664; Fax: +82-42-823-5436

Academic Editor: Vittorio M. N. Passaro Received: 24 January 2016; Accepted: 4 March 2016; Published: 9 March 2016

Abstract: A low-power and low-noise dynamic instrumentation amplifier (IA) for biopotential acquisition is presented. A dynamic IA that can reduce power consumption with a timely piecewise power-gating method, and noise level with an alternating input and chopper stabilization technique is fabricated with a 0.13- $\mu$ m CMOS. Using the reconfigurable architecture of the IA, various combinations of the low-noise schemes are investigated. The combination of power gating and chopper stabilization shows a lower noise performance than the combination of power gating and alternating input switching scheme. This dynamic IA achieved a power reduction level of 50% from 10  $\mu$ A to 5  $\mu$ A and a noise reduction of 90% from 9.1  $\mu$ Vrms to 0.92  $\mu$ Vrms with the combination of the power gating and chopper stabilization scheme.

**Keywords:** biopotential; dynamic instrumentation amplifier; power gating; alternating input; chopper stabilization

# 1. Introduction

Currently, attempts are being made to perform comfortable and continuous health monitoring in daily life through a wearable system [1–5]. Many biosignals, including electrocardiogram, electroencephalogram, electromyogram, body fat, and heart rate are monitored in contemporary commercialized wearable devices [6–8]. Such battery-operated wearable systems inherently require low power, and, thereby, an ultra-low-power health monitoring circuit. An instrumentation amplifier (IA) is one of the most important building blocks for biopotential signal acquisition. High signal-to-noise ratio at the amplifier output is required for further processing in subsequent stages. Generally, a low-noise design requires higher power consumption, because the input-referred noise can be lowered by increasing the power consumption.

In biopotential applications, reducing the flicker noise is an important issue because the flicker noise (1/f noise) is dominant in the low-frequency band. The dominant factors of flicker noise are fluctuations in carrier number and mobility due to the traps at the interface of the silicon and gate oxide [9]. Many research studies have reported a reduction in the flicker noise by various techniques, including correlated double sampling [10], chopper stabilization [11–14], large signal excitation [15,16], and bulk switching scheme [17].

In this paper, we present a dynamic IA scheme to reduce power consumption in an analog readout channel using power gating (PG). In addition, to recover worsened noise level according to the dynamic IA adaptation, chopper-stabilization (CS), and alternating input switching (AIS) techniques are investigated. The IA is designed to be fully reconfigurable, and can be operated in various combinations with power gating, chopper stabilization, and alternating input switching. In this paper, the optimal combination and operating conditions between PG, CS, and AIS are also investigated.

## 2. Circuit Design

#### 2.1. Top Level Architecture

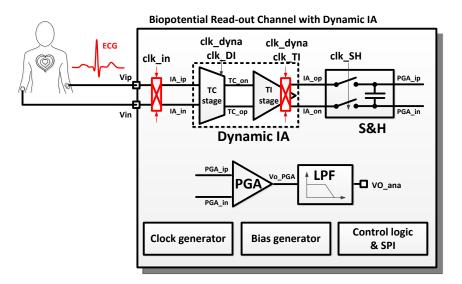

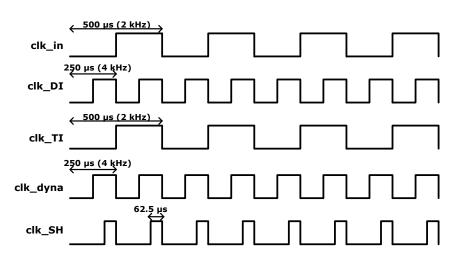

Figure 1 shows the block diagram of the biopotential readout channel with the dynamic IA. The electrocardiogram (ECG) signal is modulated by the chopping clock, "clk\_in". The chopper operation is controlled by programming the chopping clock. The modulated inputs, "IA\_ip" and "IA\_in", are amplified by the dynamic IA. The dynamic IA consists of a transconductance (TC) input stage and transimpedance (TI) output stage. The amplified ECG signal is sampled and held in the "S and H" stage. An additional amplification is performed by the programmable gain amplifier (PGA). Finally, the high-frequency noise in the amplified ECG signal is removed by the low-pass filter (LPF). The readout channel is designed to be fully reconfigurable. The operation mode of each sub-block can be controlled by the control registers. The clock generator can generate the fully programmable clocks using 32-bit bitstream registers. The internal registers can be accessed via the serial peripheral interface (SPI). The clock timing examples for the biopotential readout channel are shown in Figure 2. The biopotential readout channel can be configured in various operating mode for low power and low noise applications. The PG and the appropriate sampling operations are controlled by programming "clk\_dyna" and "clk\_SH". The AIS mode is controlled by programming "clk\_DI".

Figure 1. Block diagram of the biopotential readout channel.

Figure 2. Clock timing examples for the biopotential readout channel.

#### 2.2. Dynamic IA

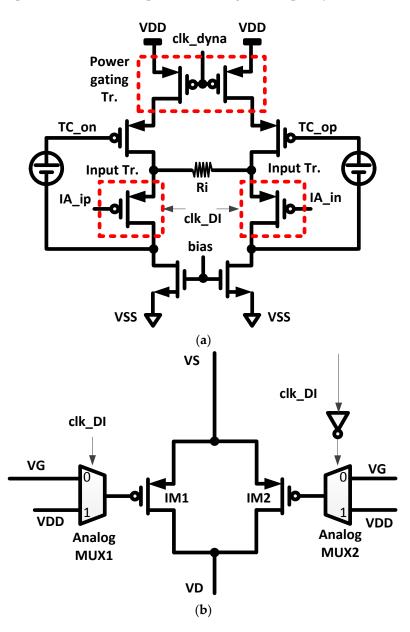

The schematic of the TC input stage, which converts the input differential voltage to output differential current, is shown in Figure 3a. The input transistors are operated in a weak inversion region for achieving higher transconductance ( $g_m$ ) efficiency. In DC operating points, the  $V_{GS}$  (= $V_{GB}$ ) and  $V_{TH}$  of the input transistors are 255 mV and 329 mV, respectively. The dynamic IA is powered on and off by a control clock signal "clk\_dyna". When the control clock signal "clk\_dyna" of a low logic level is supplied to the power gating transistors in the TC stage, the TC stage will be powered off and *vice versa*. According to the duty ratio of the control clock "clk\_dyna", the time-averaged power consumption of the dynamic IA is reduced proportionally. The input stage transistors using alternating input switching (AIS) scheme are composed of two MOS and two analog MUX, as shown in Figure 3b. With the control signal "clk\_DI", either MOS "IM1" or MOS "IM2" is activated. This type of technique with alternating input is known to be helpful in reducing low-frequency band noise [16,18].

**Figure 3.** Transconductance (TC) input stage of dynamic IA. (**a**) Schematic of TC input stage; and (**b**) input transistor with alternating input switching (AIS).

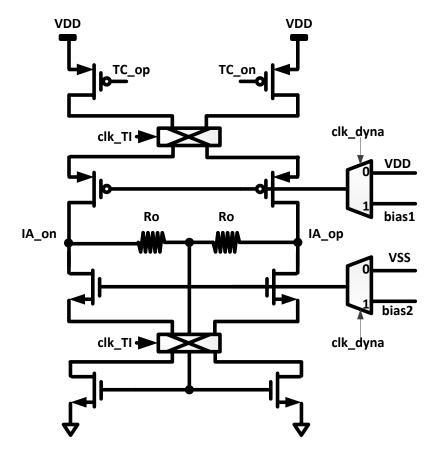

The schematic of the TI output stage is shown in Figure 4. In this stage, the differential currents from TC stage is converted to output voltages using the resistors, Ro. The resistors, Ro, are also used as resistive common mode feedback. The power gating is also applied in the TI stage. When the power gating clock "clk\_dyna" is high, the gate bias voltage is applied, and the TI stage is turned on. When "clk\_dyna" is low, the gate bias voltages of PMOS and NMOS become VDD and VSS, respectively; thus, the TI stage is turned off.

Figure 4. Transimpedance (TI) output stage of dynamic IA.

The input impedance is mainly affected by input capacitance, input leakage current, and switching frequency of CS or AIS. When the switching frequency of 4 kHz, the simulated input impedance of this circuit in ECG bandwidth is 415 M $\Omega$ . The input impedance of 415 M $\Omega$  is much larger than the typical impedance of 51 k $\Omega$ /47 nF in Ag/AgCl wet electrodes.

### 3. Experimental Results

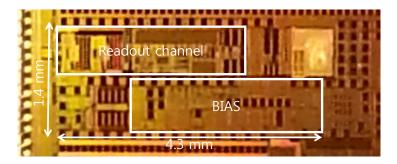

Figure 5 shows the micrograph of the fabricated readout circuit in the 0.13-µm CMOS technology. The chip size is 1.4 mm by 4.3 mm. The supply voltage is 1.2 V, and the supply current without PG is 10 µA.

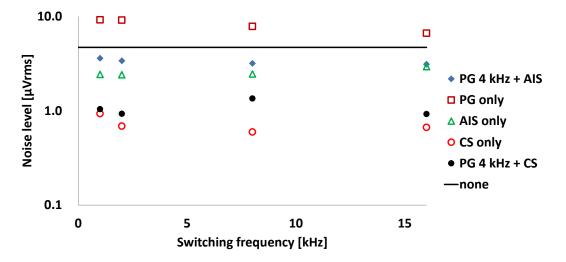

The noise spectrum is measured using a spectrum analyzer, 35670A by Keysight Technologies, Inc. (Santa Rosa, CA, USA), and the input-referred noise is calculated and plotted according to the various operation conditions in Figure 6. The clock configurations for operation conditions are shown in Table 1. The bandwidth of the IA is limited by the fourth-order Bessel low pass filter with 100 Hz cut-off frequency. The bandwidth of the filter can be digitally reconfigurable from 50 Hz to 400 Hz. With the control clocks of "clk\_dyna = L", "clk\_LSE = H", "clk\_in = H", and "clk\_TI = H", the IA is operated in a static condition and the input-referred noise level is 4.7 µVrms marked as "none" in Figure 6. In the static mode with the condition of always "clk\_dyna = L", the conventional chopping technique and the alternating input switching (AIS) technique are helpful in reducing the noise level. To reduce the power consumption, the power gating (PG) technique is applied with a clock signal having a duty ratio of 50% to the control signal "clk\_dyna". The PG technique reduces the power consumption proportionally to the duty ratio of the power gating control signal; however, it increases the noise level by almost double. The noise level of the dynamic IA is investigated with the chopper stabilization (CS) and AIS techniques.

Figure 5. Chip micrograph of the biopotential readout channel with the dynamic IA.

Figure 6. Input-referred noise level according to various operation conditions.

|          | PG 4 kHz + AIS                     | PG only                               | AIS only        | CS only                | PG 4 kHz + CS                      |

|----------|------------------------------------|---------------------------------------|-----------------|------------------------|------------------------------------|

| clk_in   | Static "H"                         | Static "H"                            | Static "H"      | Chopper freq.<br>clock | Chopper freq. clock                |

| clk_DI   | AIS freq. clock                    | Static "H"                            | AIS freq. clock | Static "H"             | Static "H"                         |

| clk_TI   | Static "H"                         | Static "H"                            | Static "H"      | Chopper freq.<br>clock | Chopper freq. clock                |

| clk_dyna | 4 kHz clock                        | PG freq. clock                        | Static "H"      | Static "H"             | Static "H"                         |

| clk_SH   | 4 kHz clock with<br>1/4 duty ratio | PG freq. clock<br>with 1/4 duty ratio | Static "H"      | Static "H"             | 4 kHz clock with<br>1/4 duty ratio |

Table 1. Clock configurations for various operation conditions.

The performance comparisons including noise efficiency factor (NEF) between the various operating conditions at 2 kHz switching frequency are also summarized in Table 2. The NEF is calculated as Equation (1):

$$NEF = V_{ni,rms} \sqrt{\frac{2I_{tot}}{\pi U_T \cdot 4kT \cdot BW}}$$

(1)

where  $V_{ni,rms}$  is the input referred noise, *BW* is the 3-dB bandwidth of the amplifier,  $U_T$  refers to the thermal voltage, and  $I_{tot}$  is the supply current of the amplifier.

|                     | PG 4 kHz + AIS<br>2 kHz | PG only<br>2 kHz | AIS only<br>2 kHz | CS only<br>2 kHz | PG 4 kHz + CS<br>2 kHz |

|---------------------|-------------------------|------------------|-------------------|------------------|------------------------|

| Input noise (µVrms) | 3.4                     | 9.1              | 2.4               | 0.69             | 0.92                   |

| Supply current (µA) | 5                       | 5                | 10                | 10               | 5                      |

| Bandwidth (Hz)      | 100                     | 100              | 100               | 100              | 100                    |

| NEF                 | 29.8                    | 79.9             | 29.8              | 8.6              | 7.9                    |

Table 2. Comparison of operation conditions at 2 kHz switching frequency.

The lowest noise level of 0.69  $\mu$ Vrms is measured at the chopper frequency of 2 kHz, wherein the input-referred noise is measured to be 9.1  $\mu$ Vrms with PG only. At the same chopper frequency of 2 kHz, the input-referred noise is reduced to be 3.4  $\mu$ Vrms with the combination of PG and AIS.

The most helpful technique in the dynamic IA is the combination of the PG and CS method. The input referred noise and NEF with the combination of PG 4 kHz and CS 2 kHz are 0.92  $\mu$ Vrms and 7.9, respectively. In terms of the power consumption, PG with the half duty cycle is equivalent to reducing the bias current to one half. When the bias current is reduced to one half, the thermal noise component, which is dominant in chopper stabilized amplifier, will increase approximately by a factor of  $\sqrt{2}$ . In this case, the input referred noise with CS with half bias current is expected to be 0.97  $\mu$ Vrms (= $\sqrt{2} \cdot 0.69 \mu$ Vrms). The combination of PG and CS shows better NEF and lower input referred noise level than the expected values of CS and half bias current.

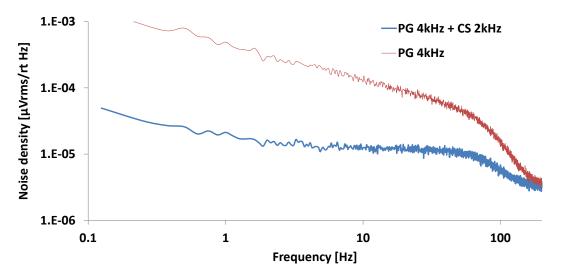

Figure 7 shows noise spectrum examples in cases of power gating with a 4 kHz clock and a combination of power gating with 4 kHz and chopping with 2 kHz. By adding the chopping technique, the low-frequency band noise in the power gating technique is reduced. The input-referred noise is reduced to 0.92  $\mu$ Vrms with the combination of PG and CS. By applying the half duty-cycled PG and CS, a power reduction of 50% from 10  $\mu$ A to 5  $\mu$ A, and a noise reduction of 90% from 9.1  $\mu$ Vrms to 0.92  $\mu$ Vrms can be achieved.

Figure 7. Input-referred noise spectrum of PG 4 kHz and PG 4 kHz + CS 2 kHz.

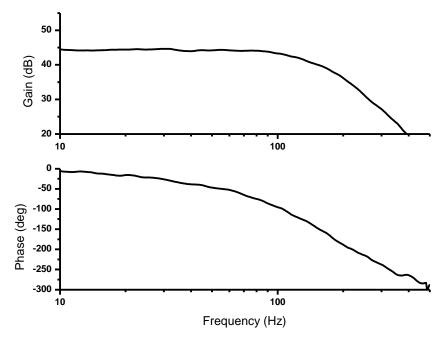

The measured frequency responses including gain and phase plot are shown in Figure 8. The phase distortions are important parameter for high quality ECG recording [19,20]. Although the post-processed digital filter can be used for reducing the phase distortions, the analog filters with inherent phase distortions are used in this system to achieve low power, small size, and real-time signal acquisition, which are important in wearable devices.

Figure 8. Measured frequency response.

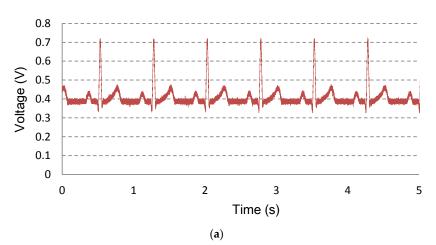

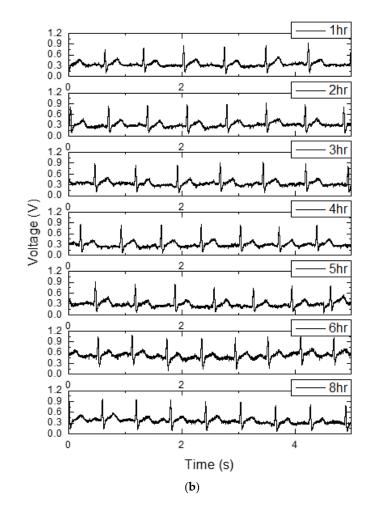

In the time domain, the measured waveform using ECG simulator is shown in Figure 9a. The measured ECG waveforms for 8 h with wet electrodes are shown in Figure 9b. The Ag/AgCl wet electrodes of  $3M^{TM}$  Red Dot<sup>TM</sup> [21] are used for ECG signal acquisition. The gain of the readout channel is set to 171 V/V. The input ECG signal is preserved with a 50% power reduction compared to the static condition and 90% noise reduction compared to the power gating condition. The transient switching noises due to the switching operations in PG and CS are removed by the fourth-order 100 Hz low pass filter. For example, the 2 kHz switching noises are attenuated by -104 dB (= $-80 \text{ dB/dec} \cdot \log(2 \text{ kHz}/100 \text{ Hz})$  dec). The bandwidth of the filter can be digitally reconfigurable from 50 Hz to 400 Hz.

Figure 9. Cont.

**Figure 9.** Measured ECG signals in the time domain. (**a**) Measured waveform using ECG simulator; and (**b**) measured ECG signals for eight hours with wet electrodes.

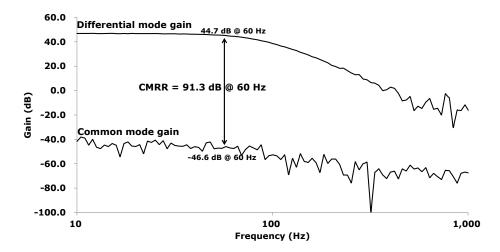

The measured common mode rejection ratio (CMRR) is shown in Figure 10. At 60 Hz, the differential mode gain and the common mode gain are measured to be 44.7 dB and -46.6 dB; thus, the CMRR is calculated to 91.3 dB.

Figure 10. Measured CMRR.

# 4. Conclusions

A low-noise and low-power dynamic IA scheme was presented. A dynamic IA that can reduce power consumption with a timely piecewise power-gating method and noise level with an alternating input and chopper stabilization technique is fabricated with a 0.13- $\mu$ m CMOS. The combination of power gating and chopper stabilization results in a lower noise performance than the combination of power gating and alternating input switching scheme. With the combination of power gating and chopper stabilization, the supply current is reduced from 10  $\mu$ A to 5  $\mu$ A, and the input-referred noise is reduced from 9.1  $\mu$ Vrms to 0.92  $\mu$ Vrms. The power consumption and noise level of the fabricated chip are summarized and compared with the recently-published results summarized in Table 3. In our proposed architecture, we have shown that the dynamic IA technique can achieve a 50% reduction in power consumption and recover the signal-quality deterioration by 90%.

|                                   | This Work                                                                 | [22]      | [23]      | <b>[24]</b> |

|-----------------------------------|---------------------------------------------------------------------------|-----------|-----------|-------------|

| Technology                        | 130 nm                                                                    | 180 nm    | 65 nm     | 180 nm      |

| Supply                            | 1.2 V                                                                     | 1.2 V     | 1 V       | 1 V         |

| IA current                        | 10 μA (static mode) 5 μA (half<br>duty-cycled power gating mode)          | 5 μΑ      | 1.8 µA    | 3.5 μΑ      |

| Input-referred<br>noise (~100 Hz) | 0.6 μVrms (static mode) 0.9 μVrms<br>(half duty-cycled power gating mode) | 1.3 μVrms | 6.7 μVrms | 1.3 µVrms   |

| Input impedance                   | 415 M $\Omega$ (simulated)                                                | 1 GΩ      | N/A       | 700 MΩ      |

| CMRR                              | 91.3 dB                                                                   | 120 dB    | 134 dB    | 60 dB       |

|                                   |                                                                           |           |           |             |

| Table 3. IA | performance summar  | y and con   | nparison v | with 1 | previous wor | ks. |

|-------------|---------------------|-------------|------------|--------|--------------|-----|

|             | periorinance canana | y anter con |            |        |              |     |

Acknowledgments: This work was supported by Chungnam National University.

**Author Contributions:** Jongpal Kim is the first author, and he drafted the manuscript. He also implemented the circuit blocks and designed the top architecture of the IC. Hyoungho Ko is the corresponding author, and he designed the analog blocks of the IC.

Conflicts of Interest: The authors declare no conflict of interest.

# References

- Shin, K.; Park, G.; Kim, J.; Lee, T.; Ko, B.; Kim, Y. An ultra-low power (ULP) bandage-type ECG sensor for efficient cardiac disease management. In Proceedings of the Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA, USA, 28 August–1 September 2012; pp. 1474–1477.

- Wong, A.; McDonagh, D.; Omeni, O.; Nunn, C.; Hernandez-Silveira, M.; Burdett, A. An ultra-low-power wireless body sensor network platform: Design & application challenges. In Proceedings of the Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Minneapolis, MN, USA, 3–6 September 2009; pp. 6576–6579.

- 3. Miao, F.; Cheng, Y.; He, Y.; He, Q.; Li, Y. A wearable context-aware ECG monitoring system integrated with built-in kinematic sensors of the smartphone. *Sensors* **2015**, *15*, 11465–11484. [CrossRef] [PubMed]

- Van Helleputte, N.; Konijnenburg, M.; Pettine, J.; Jee, D.-W.; Kim, H.; Morgado, A.; Van Wegberg, R.; Torfs, T.; Mohan, R.; Breeschoten, A. A 345 μw multi-sensor biomedical soc with bio-impedance, 3-channel ECG, motion artifact reduction, and integrated DSP. *IEEE J. Solid-State Circuits* 2015, *50*, 230–244. [CrossRef]

- 5. Baig, M.M.; Gholamhosseini, H.; Connolly, M.J. A comprehensive survey of wearable and wireless ECG monitoring systems for older adults. *Med. Biol. Eng. Comput.* **2013**, *51*, 485–495. [CrossRef] [PubMed]

- 6. Stoppa, M.; Chiolerio, A. Wearable electronics and smart textiles: A critical review. *Sensors* **2014**, *14*, 11957–11992. [CrossRef] [PubMed]

- Wang, J.B.; Cadmus-Bertram, L.A.; Natarajan, L.; White, M.M.; Madanat, H.; Nichols, J.F.; Ayala, G.X.; Pierce, J.P. Wearable sensor/device (Fitbit one) and SMS text-messaging prompts to increase physical activity in overweight and obese adults: A randomized controlled trial. *Telemed. e-Health* 2015, *21*, 782–792. [CrossRef] [PubMed]

- 8. Mukhopadhyay, S.C. Wearable sensors for human activity monitoring: A review. *IEEE Sens.* 2015, 15, 1321–1330. [CrossRef]

- 9. Hung, K.K.; Ko, P.K.; Hu, C.; Cheng, Y.C. A unified model for the flicker noise in metal-oxide-semiconductor field-effect transistors. *IEEE Trans. Electron Devices* **1990**, *37*, 654–665. [CrossRef]

- 10. Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. *Proc. IEEE* **1996**, *84*, 1584–1614. [CrossRef]

- 11. Tseng, Y.; Ho, Y.; Kao, S.; Su, C. A 0.09 W low power front-end biopotential amplifier for biosignal recording. *IEEE Trans. Biomed. Circuits Syst.* **2012**, *6*, 508–516. [CrossRef] [PubMed]

- 12. Zhang, F.; Holleman, J.; Otis, B.P. Design of ultra-low power biopotential amplifiers for biosignal acquisition applications. *IEEE Trans. Biomed. Circuits Syst.* **2012**, *6*, 344–355. [CrossRef] [PubMed]

- 13. Xu, J.; Fan, Q.; Huijsing, J.H.; Van Hoof, C.; Yazicioglu, R.F.; Makinwa, K. Measurement and analysis of current noise in chopper amplifiers. *IEEE J. Solid-State Circuits* **2013**, *48*, 1575–1584.

- 14. Kusuda, Y. A 60 V auto-zero and chopper operational amplifier with 800 kHz interleaved clocks and input bias current trimming. *IEEE J. Solid-State Circuits* **2015**, *50*, 2804–2813. [CrossRef]

- 15. Wirth, G.; Koh, J.; Silva, R.D.; Thewes, R.; Brederlow, R. Modeling of statistical low-frequency noise of deep-submicrometer MOSFETS. *IEEE Trans. Electron Devices* **2005**, *52*, 1576–1588. [CrossRef]

- 16. Koh, J.; Schmitt-Landsiedel, D.; Thewes, R.; Brederlow, R. A complementary switched mosfet architecture for the 1/f noise reduction in linear analog CMOS ICS. *IEEE J. Solid-State Circuits* **2007**, *42*, 1352–1361.

- 17. Han, M.; Kim, B.; Chen, Y.-A.; Lee, H.; Park, S.-H.; Cheong, E.; Hong, J.; Han, G.; Chae, Y. Bulk switching instrumentation amplifier for a high-impedance source in neural signal recording. *IEEE Trans. Circuits Syst. II Exp. Briefs* **2015**, *62*, 194–198. [CrossRef]

- Van Der Wel, A.P.; Klumperink, E.A.; Kolhatkar, J.S.; Hoekstra, E.; Snoeij, M.F.; Salm, C.; Wallinga, H.; Nauta, B. Low-frequency noise phenomena in switched mosfets. *IEEE J. Solid-State Circuits* 2007, 42, 540–550. [CrossRef]

- 19. Luo, S.; Johnston, P. A review of electrocardiogram filtering. *J. Electrocardiol.* **2010**, *43*, 486–496. [CrossRef] [PubMed]

- Buendía-Fuentes, F.; Arnau-Vives, M.; Arnau-Vives, A.; Jiménez-Jiménez, Y.; Rueda-Soriano, J.; Zorio-Grima, E.; Osa-Sáez, A.; Martínez-Dolz, L.; Almenar-Bonet, L.; Palencia-Pérez, M. High-bandpass filters in electrocardiography: Source of error in the interpretation of the st segment. *ISRN Cardiol.* 2012, 2012, 706217. [CrossRef] [PubMed]

- 21. 3M<sup>™</sup> Red Dot<sup>™</sup> Monitoring Electrodes. Available online: http://multimedia.3m.com/mws/media/ 513875O/red-dot-electrodes.pdf (accessed on 18 February 2016).

- 22. Van Helleputte, N.; Kim, S.; Kim, H.; Kim, J.P.; Van Hoof, C.; Yazicioglu, R.F. A 160 μa biopotential acquisition ASIC with fully integrated IA and motion-artifact suppression. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 19–23 February 2012; pp. 118–120.

- 23. Fan, Q.; Sebastiano, F.; Huijsing, J.H.; Makinwa, K.A. A 1.8 W 60 nV Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes. *IEEE J. Solid-State Circuits* **2011**, *46*, 1534–1543. [CrossRef]

- 24. Verma, N.; Shoeb, A.; Bohorquez, J.; Dawson, J.; Guttag, J.; Chandrakasan, A.P. A micro-power EEG acquisition SOC with integrated feature extraction processor for a chronic seizure detection system. *IEEE J. Solid-State Circuits* **2010**, *45*, 804–816. [CrossRef]

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).