Wafer-Level Vacuum Packaging of Smart Sensors

Abstract

:1. Introduction

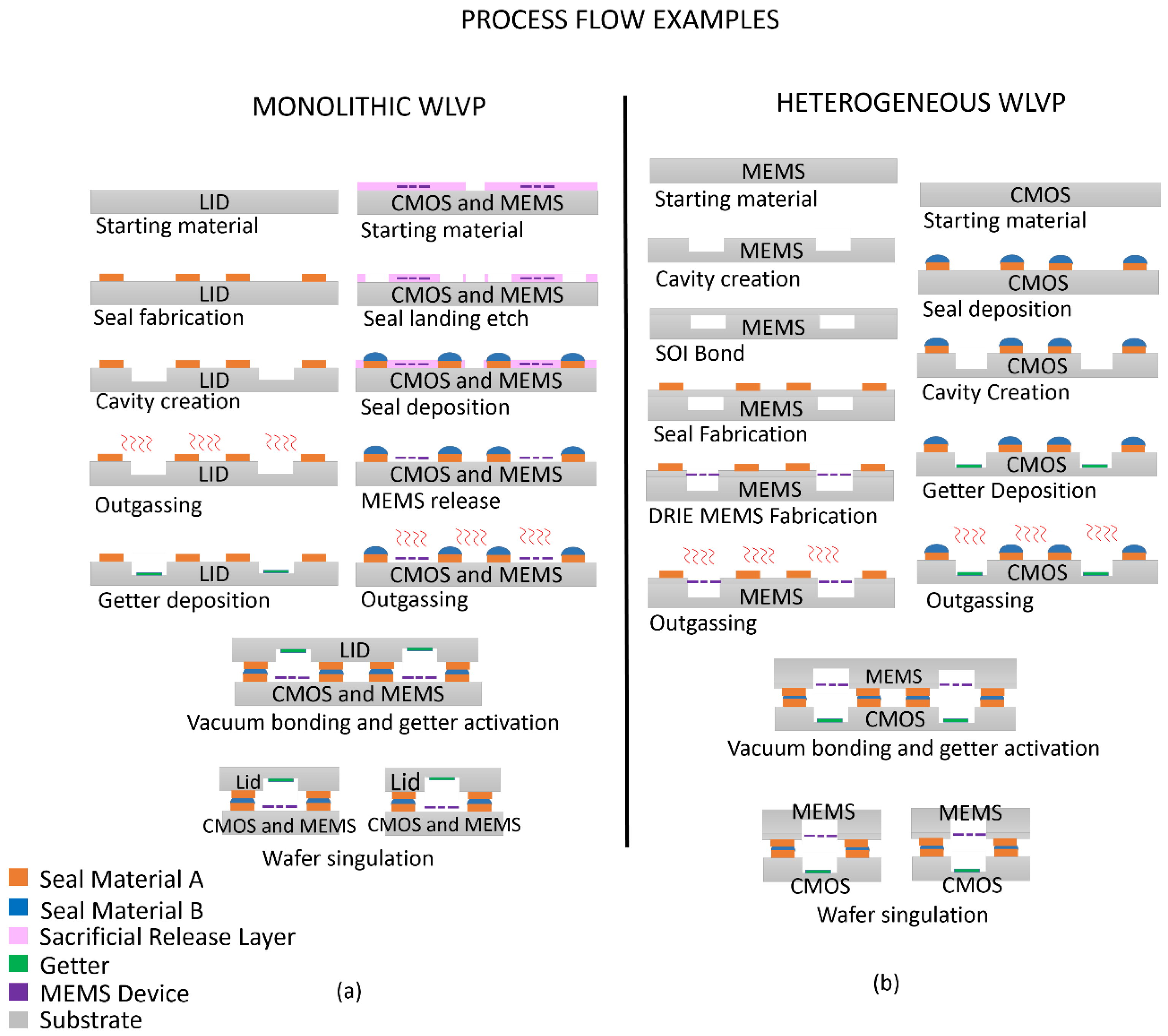

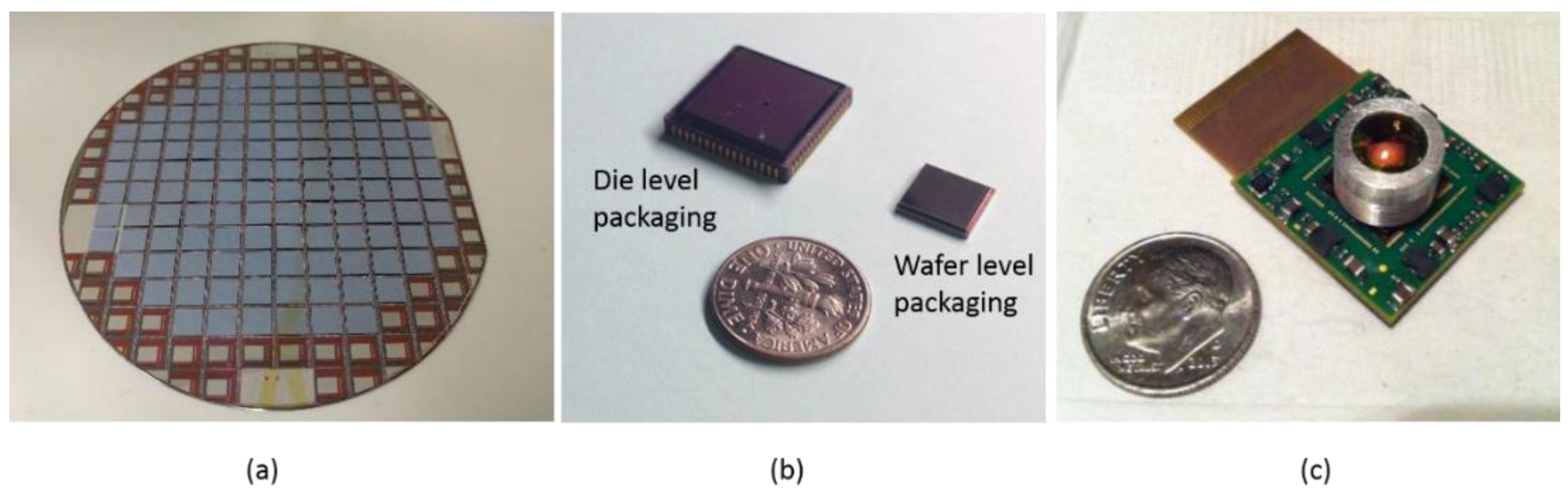

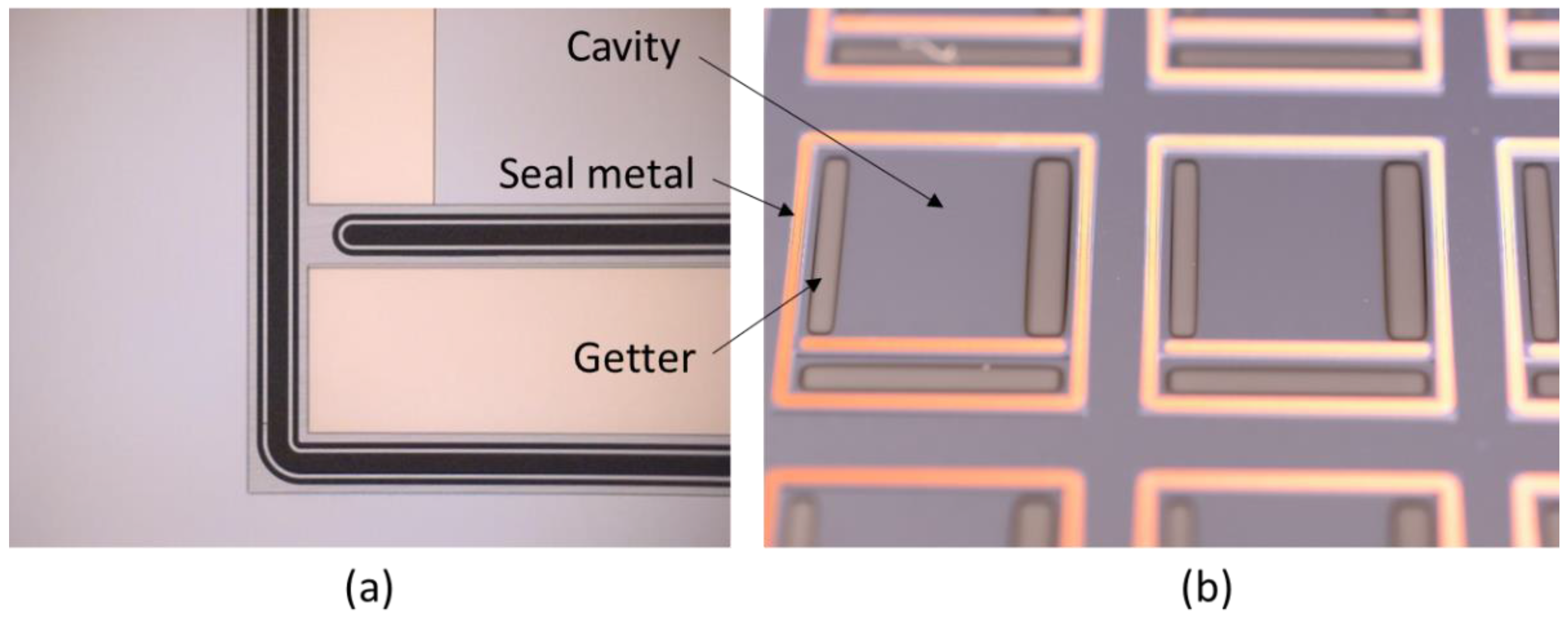

2. Introduction to WLVP Process

3. Bonding Approaches

3.1. Eutectic Bonding

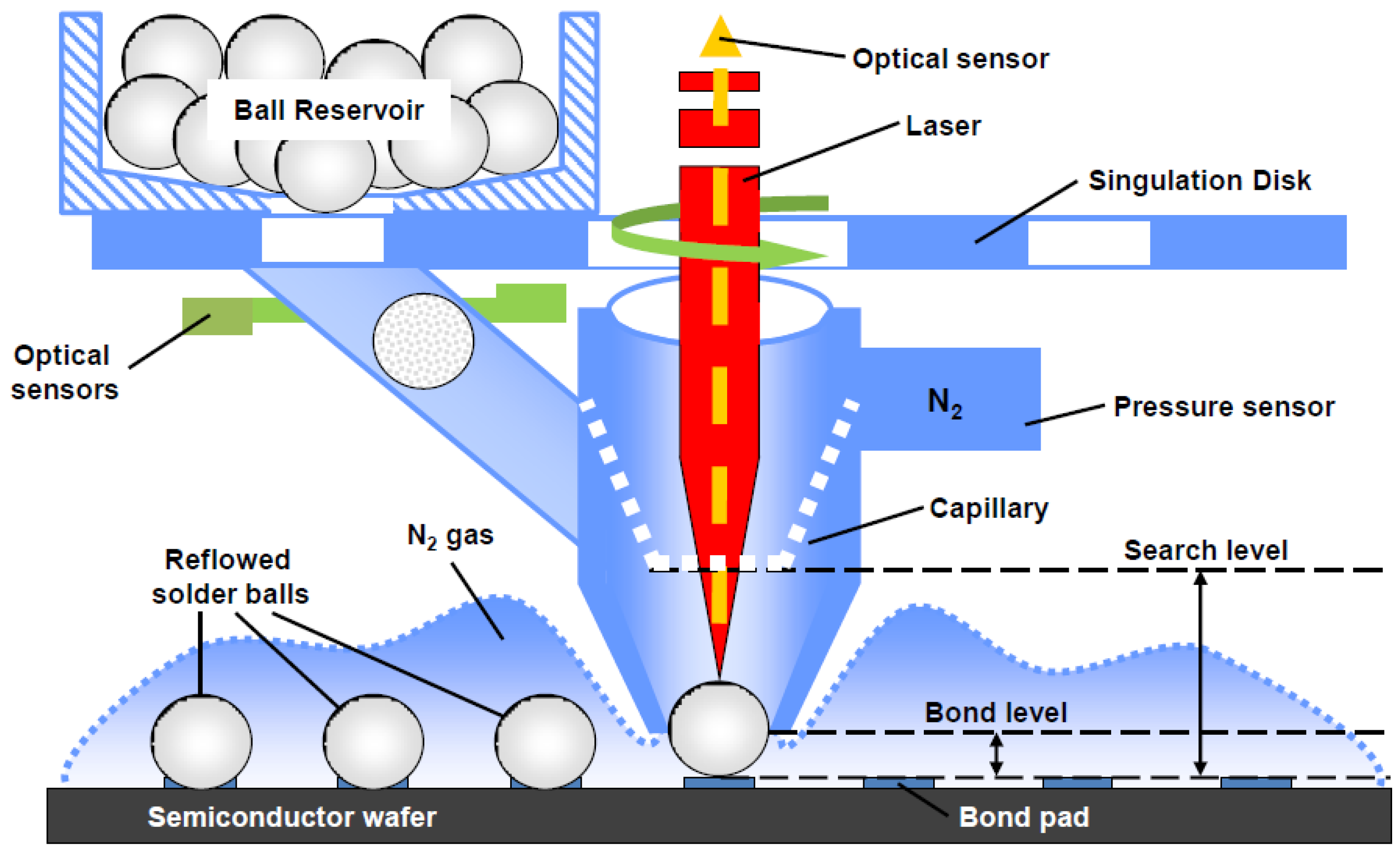

3.1.1. Gold-Tin (Au-Sn) Eutectic Bonding

3.1.2. Au-Si Eutectic Bonding

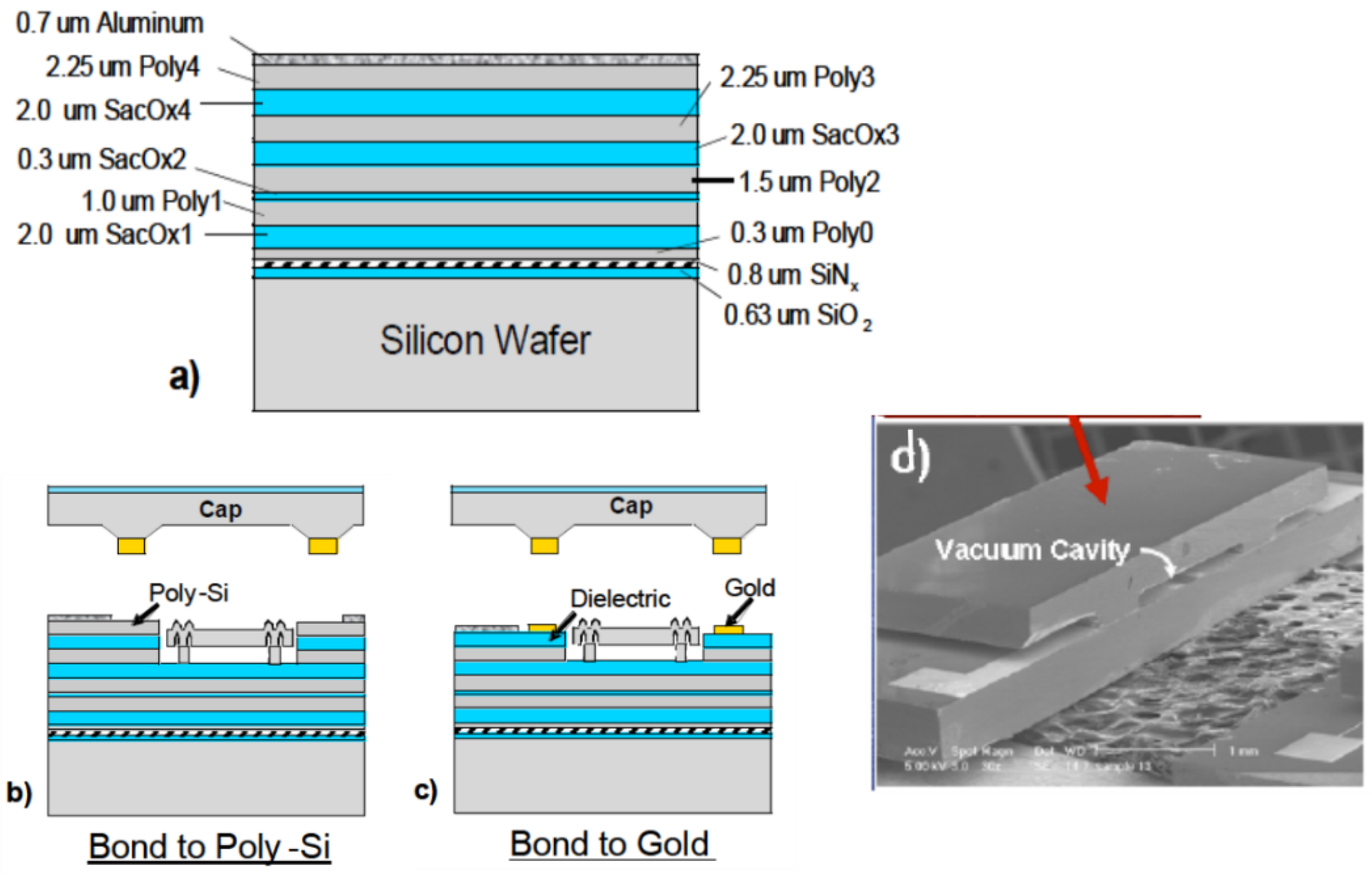

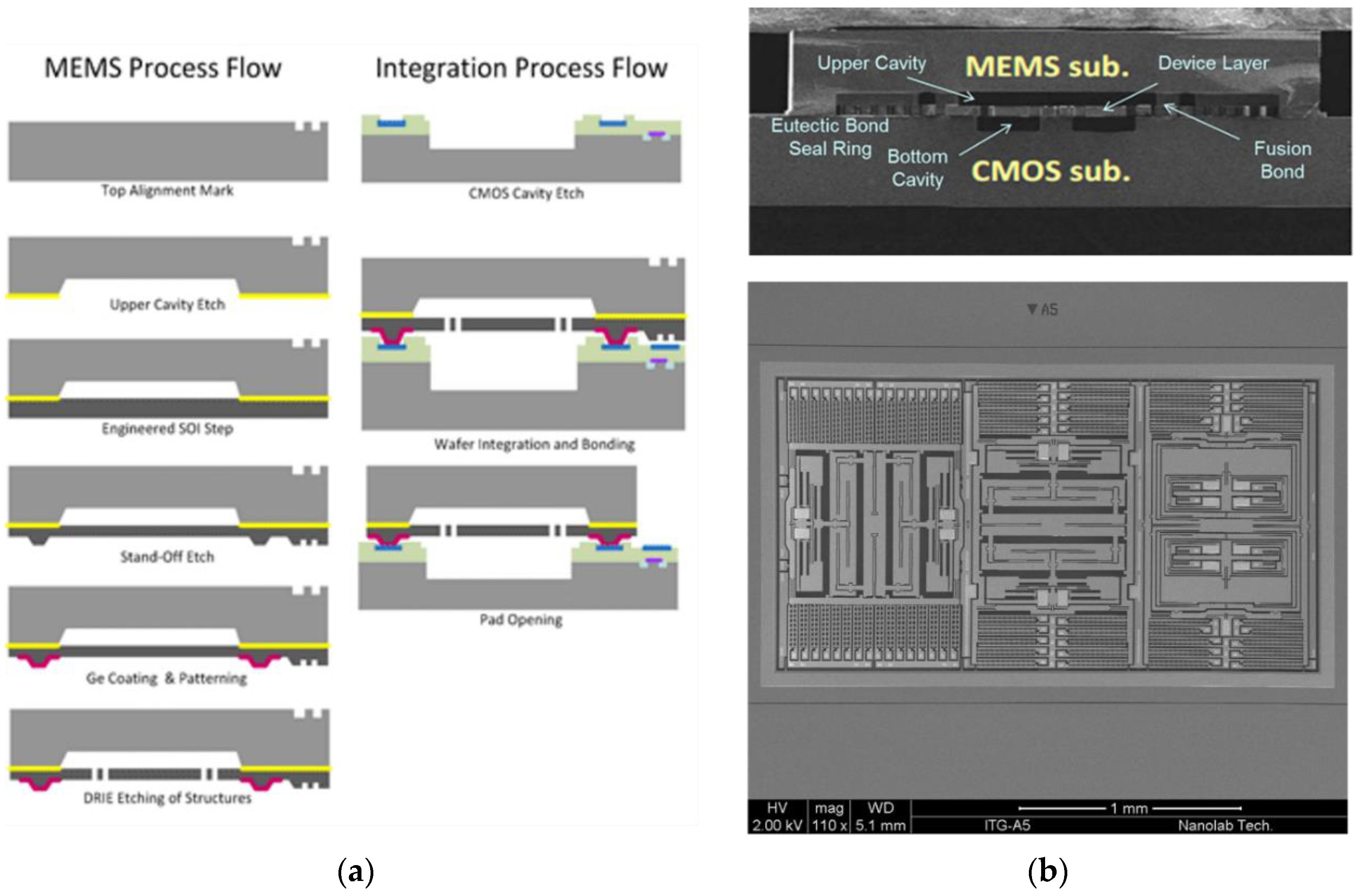

3.1.3. Aluminum-Germanium (Al-Ge) Eutectic Bonding

3.2. SLID Bonding

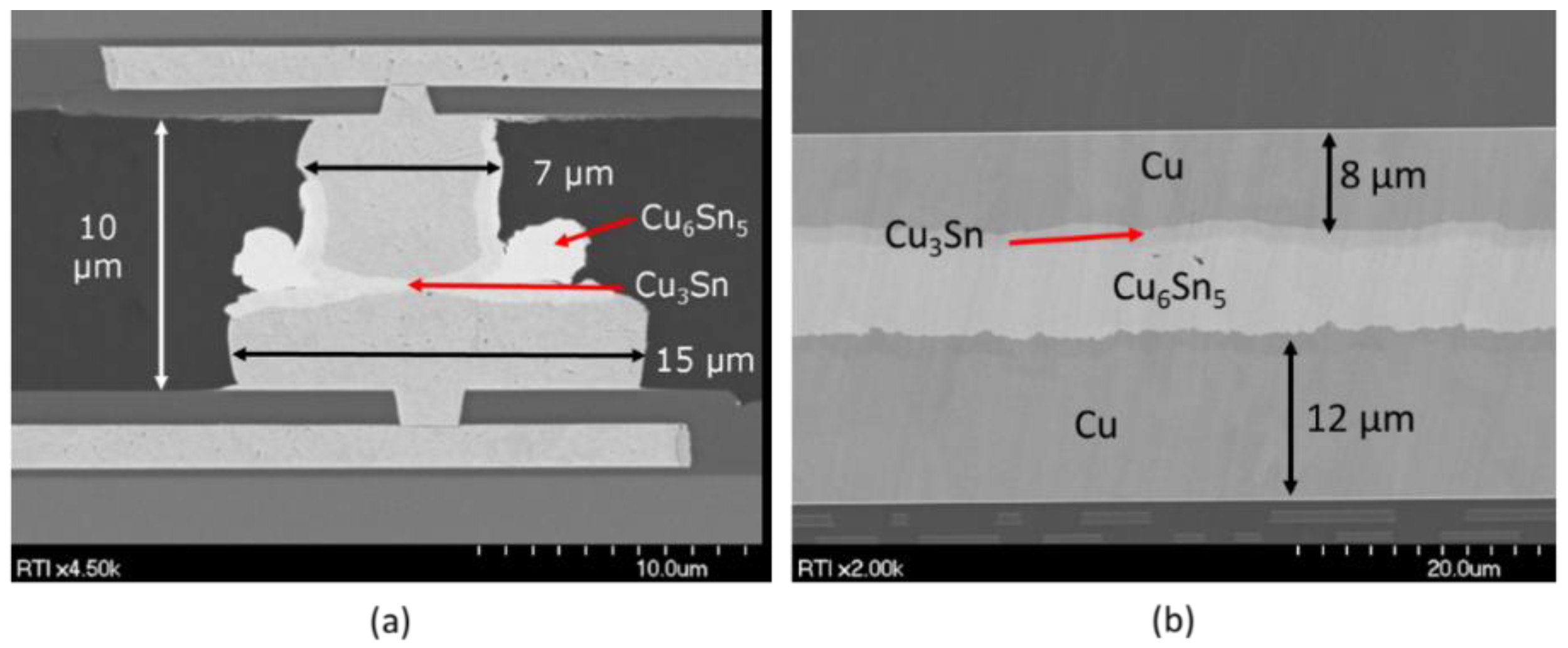

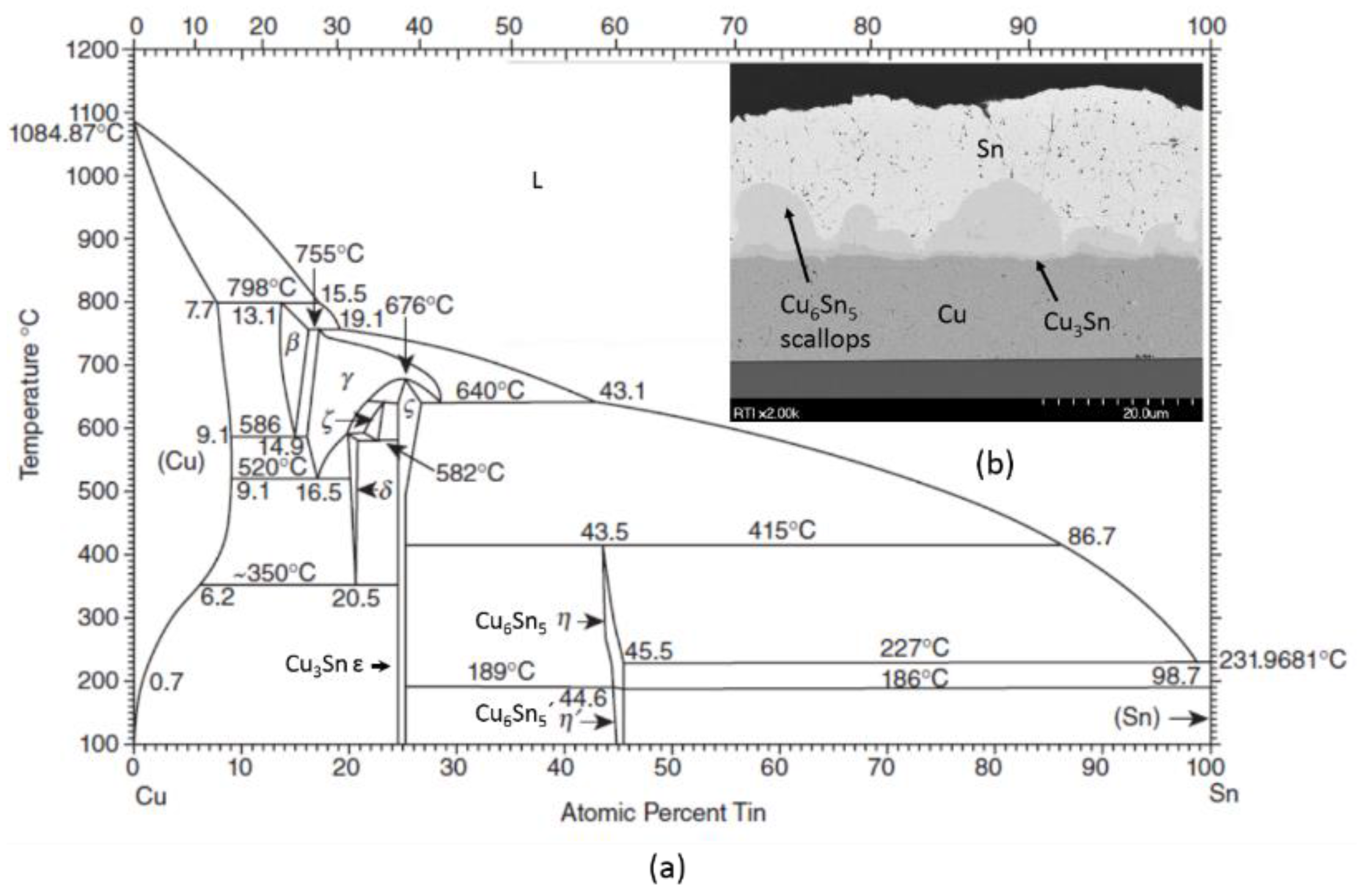

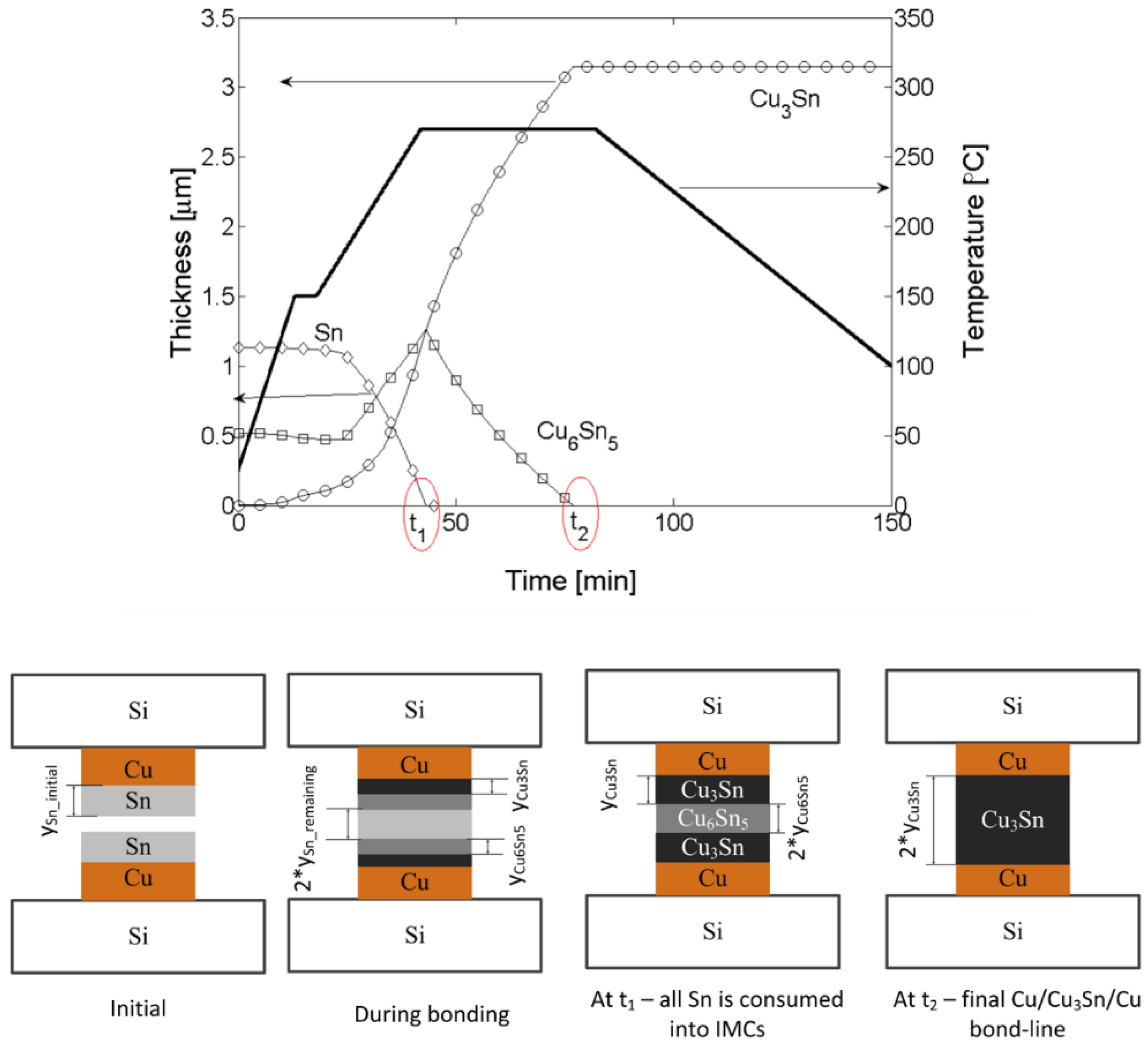

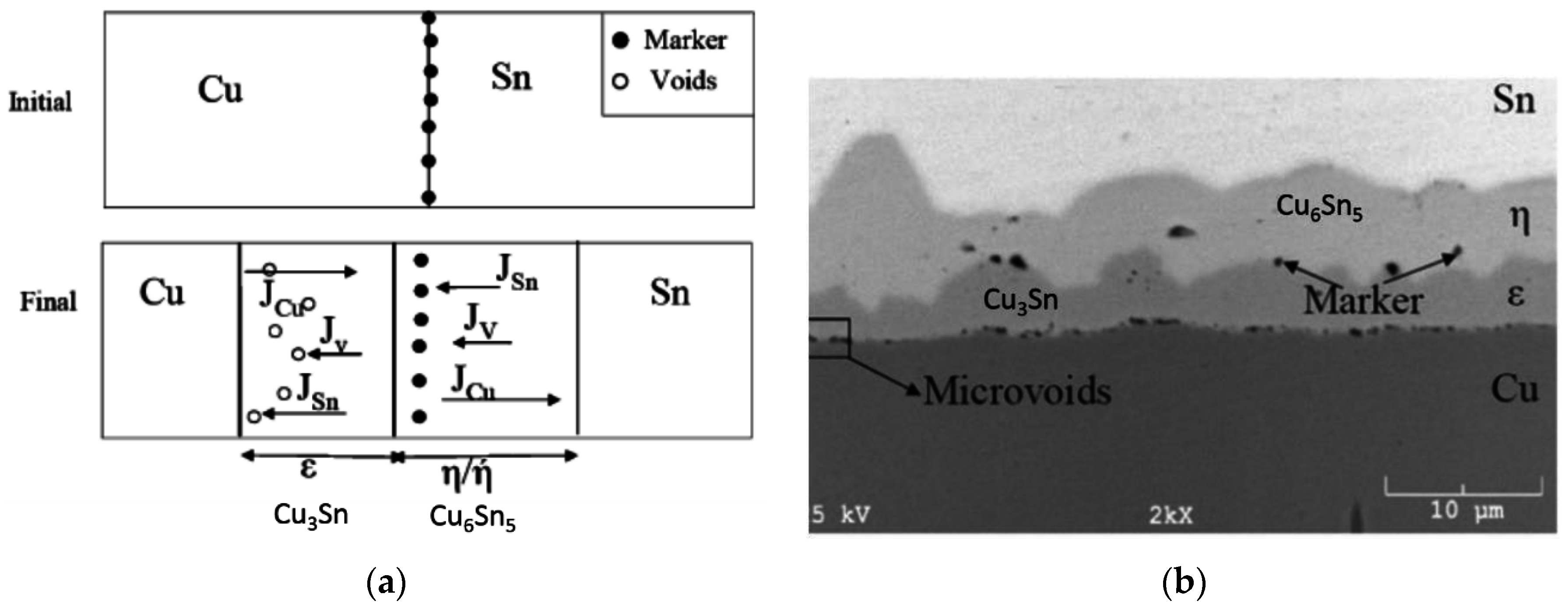

3.2.1. Cu-Sn SLID Bonding

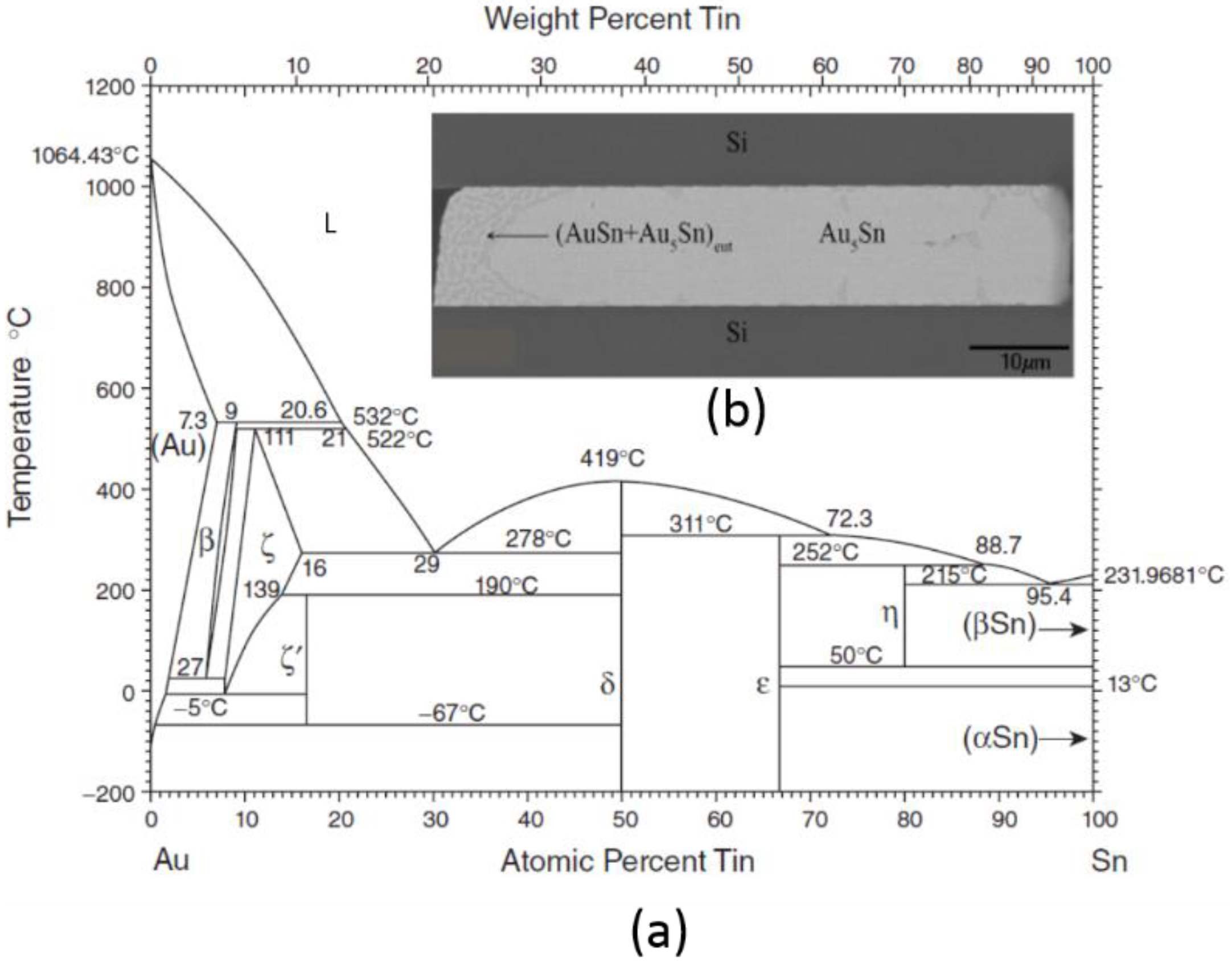

3.2.2. Au-Sn SLID Bonding

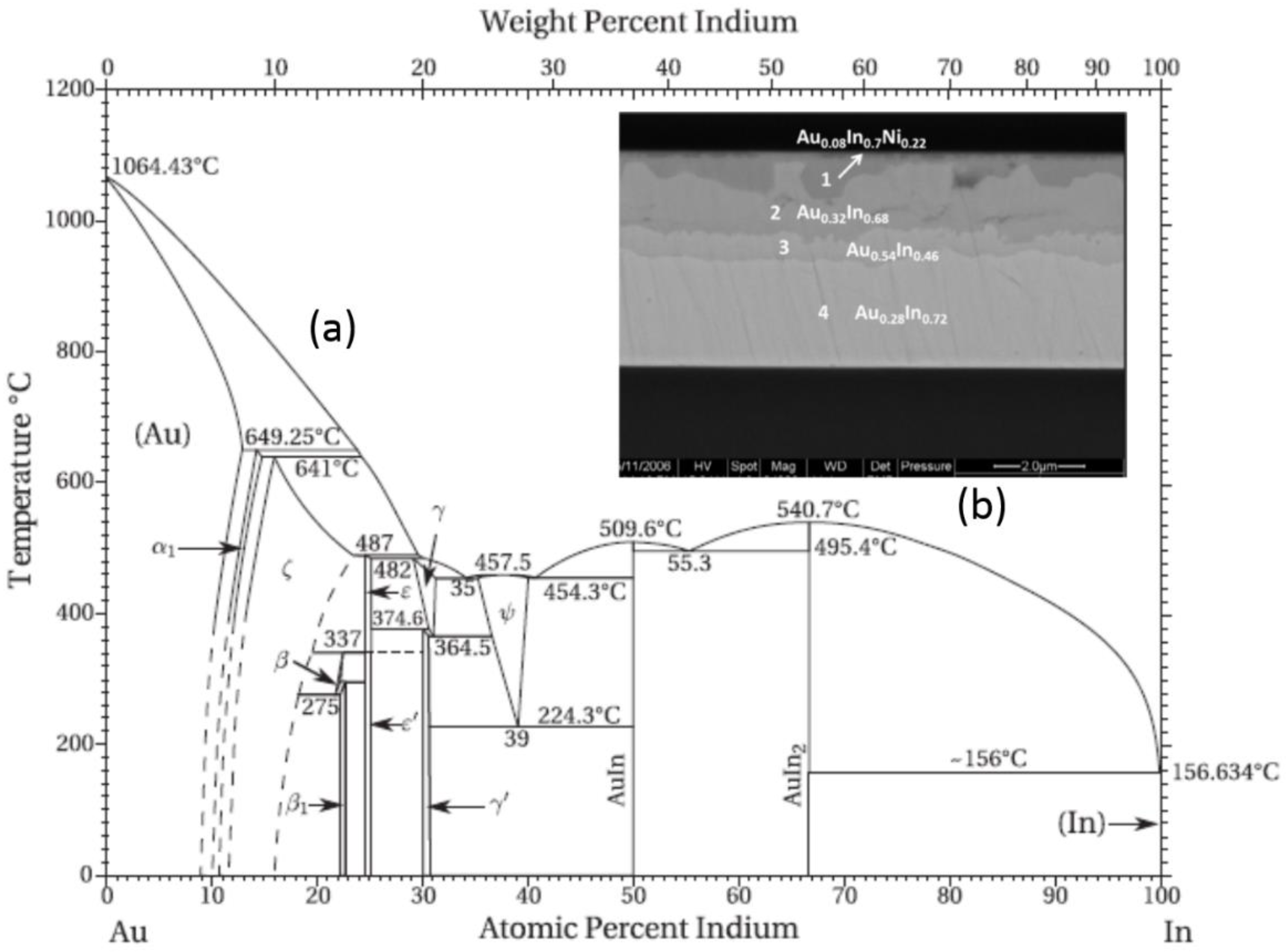

3.2.3. Au-In SLID Bonding

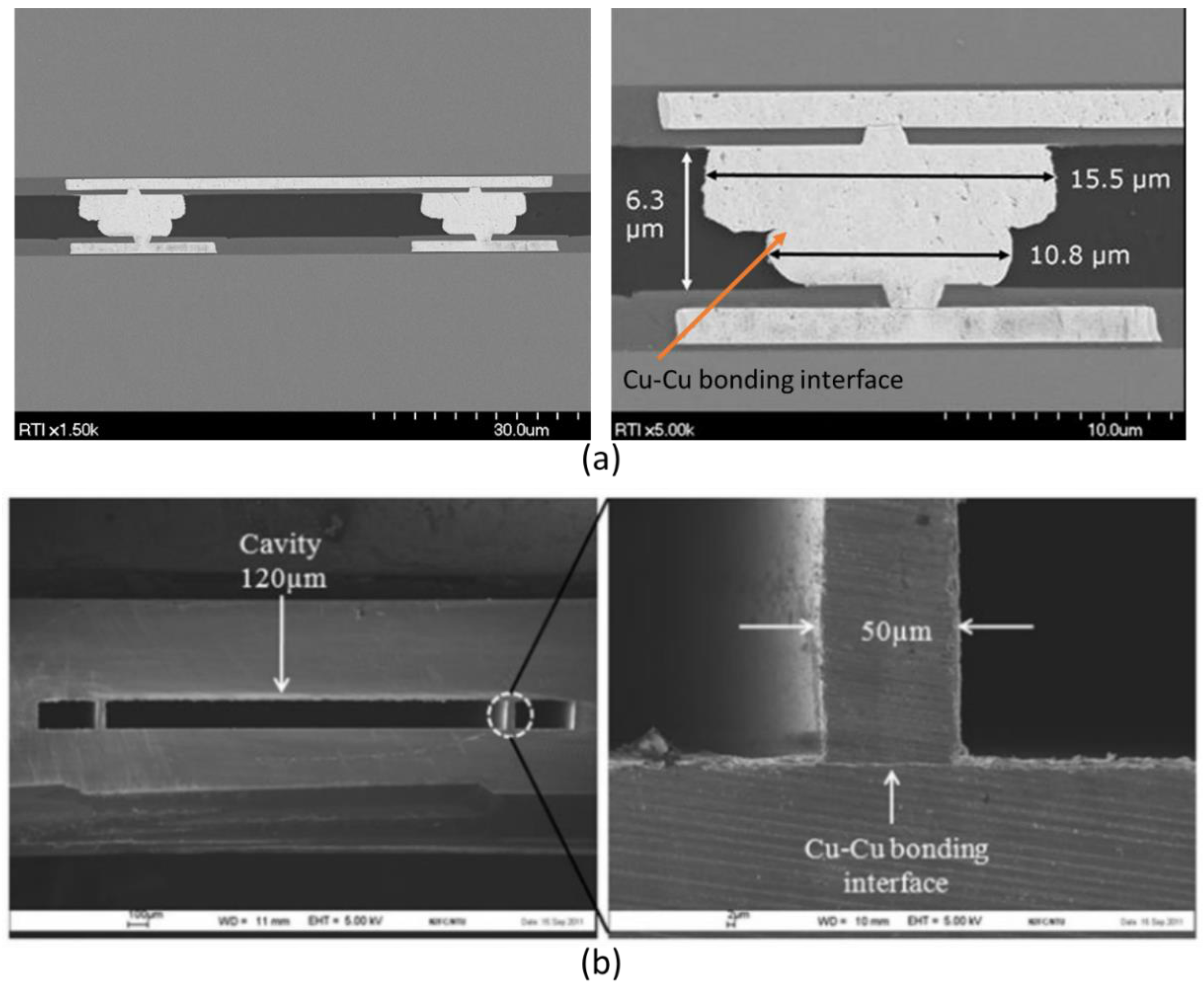

3.3. Metal-to-Metal Thermocompression Bonding

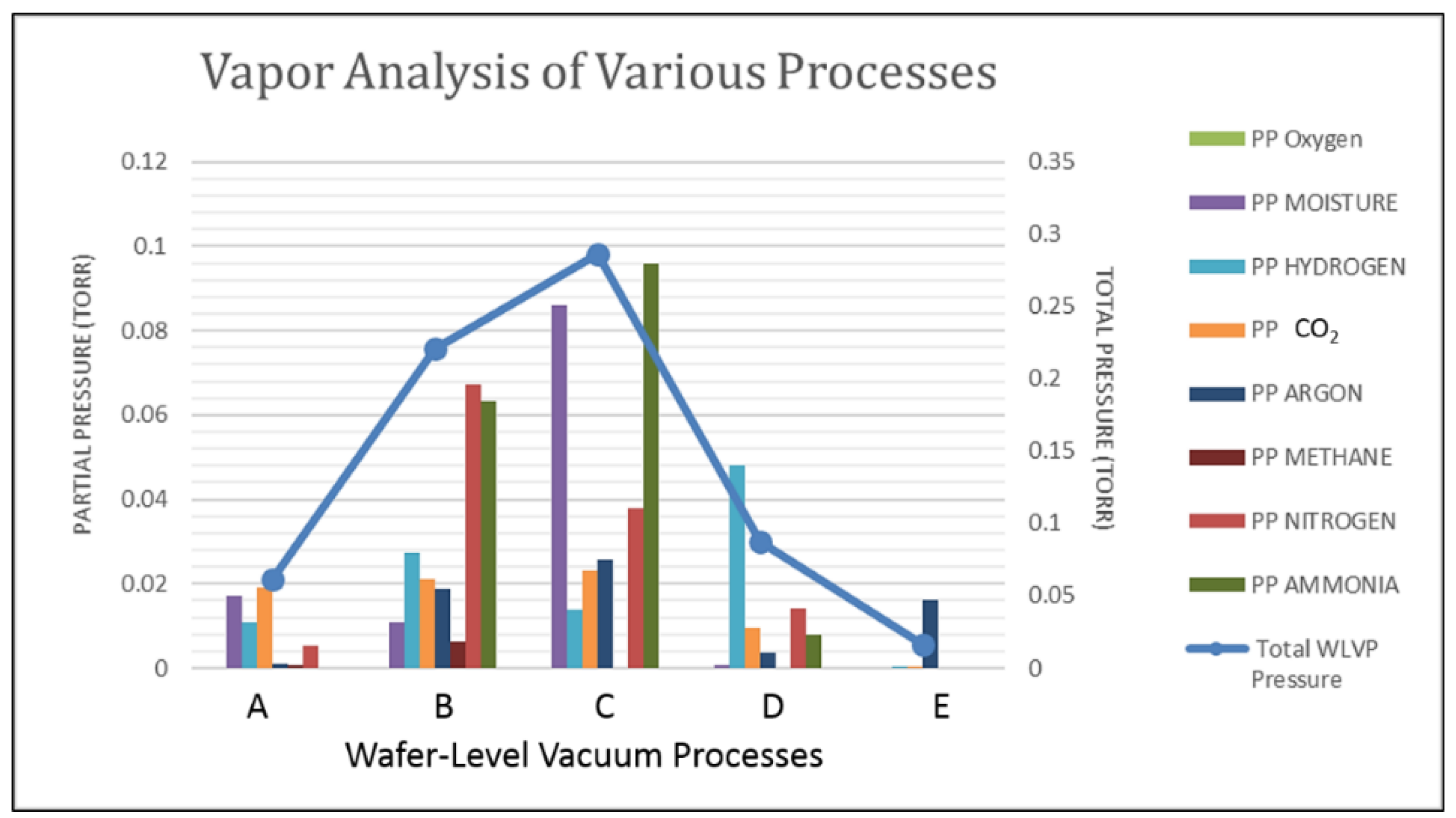

4. Thin Film Getters

5. Outlook and Conclusions

Acknowledgments

Conflicts of Interest

Abbreviations

| 2D | two-dimensional |

| 3D | three-dimensional |

| Al | aluminum |

| Au | gold |

| CMOS | complementary metal-oxide semiconductor (CMOS) |

| CMP | chemical mechanical planarization |

| CO | carbon monoxide |

| CO2 | carbon dioxide |

| Cr | chromium |

| CTE | coefficient of thermal expansion |

| Cu | copper |

| eV | electron volt |

| Ge | germanium |

| H2 | hydrogen |

| HF | hydrofluoric |

| HR-IVA | high-resolution internal vapor analysis |

| IC | integrated circuit |

| IMC | intermetallic compound |

| In | indium |

| IoT | Internet-of-Things |

| MEMS | microelectromechanical systems |

| MOEMS | micro-optoelectromechanical systems |

| MPa | Megapascal |

| N2 | nitrogen |

| Ni | nickel |

| nm | nanometers |

| O2 | oxygen |

| ORS | Oneida Research Services |

| PADS | plasma-assisted dry soldering |

| Pb | lead |

| RF | radiofrequency |

| RGA | residual gas analysis |

| ROIC | readout integrated circuit |

| SAM | self-assembled monolayer |

| Si | silicon |

| SLID | solid-liquid interdiffusion |

| Sn | tin |

| SoC | system-on-chip |

| SPIE | Society of Photo-optical Instrumentation Engineers |

| SWaP-C | size, weight, power, and cost |

| TaN | tantalum nitride |

| Ti | titanium |

| TLP | transient liquid phase |

| USM | under-seal metal |

| WLP | wafer-level packaging |

| WLVP | wafer-level vacuum packaging |

| Zr | zirconium |

References

- Shanklin, T.A. CERIAS Tech Report 2012-07, an Agent-Based Model for Navigation Simulation in a Heterogeneous Environment. Available online: https://www.cerias.purdue.edu/assets/pdf/bibtex_archive/2012-07.pdf (accessed on 21 October 2016).

- Fischer, A.C.; Forsberg, F.; Lapisa, M.; Bleiker, S.J.; Stemme, G.; Roxhed, N.; Niklaus, F. Integrating MEMS and ICs. Microsyst. Nanoeng. 2015, 1, 15005. [Google Scholar] [CrossRef]

- Pelzer, R.; Kirchberger, H.; Kettner, P. Wafer-to-Wafer Bonding Techniques: From MEMS Packaging to IC Integration Applications. In Proceedings of the 2005 6th International Conference on Electronic Packaging Technology, Shenzhen, China, 30 August–2 September 2005; pp. 1–6.

- Knechtel, R. Aspects of bonding processed CMOS wafers. ECS Trans. 2008, 16, 39–46. [Google Scholar]

- Hausner, R. Wafer-bonding for MEMS—Status and trends. ECS Trans. 2014, 64, 245–251. [Google Scholar] [CrossRef]

- Lapisa, M.; Stemme, G.; Niklaus, F. Wafer-level heterogeneous integration for MOEMS, MEMS, and NEMS. IEEE J. Sel. Top. Quantum Electron. 2011, 17, 629–644. [Google Scholar] [CrossRef]

- Niklaus, F.; Lapisa, M.; Bleiker, S.J.; Dubois, V.; Roxhed, N.; Fischer, A.C.; Forsberg, F.; Stemme, G.; Grogg, D.; Despont, M. Wafer-level heterogeneous 3D integration for MEMS and NEMS. In Proceedings of the 2012 3rd IEEE International Workshop on Low Temperature Bonding for 3D Integration (LTB-3D), Tokyo, Japan, 22–23 May 2012; pp. 247–252.

- Kuisma, H. Introduction to Encapsulation of MEMS-Chapter Thirty; Elsevier Inc.: Burlington, MA, USA, 2010; pp. 501–504. [Google Scholar]

- Esashi, M. Wafer level packaging of MEMS. J. Micromech. Microeng. 2008, 18, 073001. [Google Scholar] [CrossRef]

- Dragoi, V.; Pabo, E. Wafer bonding technology for new generation vacuum MEMS: Challenges and promises. In Proceedings of the Smart Sensors, Actuators, and MEMS VII; and Cyber Physical Systems, Barcelona, Spain, 21 May 2015.

- Dragoi, V.; Cakmak, E.; Pabo, E. Wafer bonding with metal layers for MEMS applications. In Proceedings of the CAS 2009 International Semiconductor Conference, Sinaia, Romania, 12–14 October 2009; pp. 215–218.

- Chiao, M.; Cheng, Y.-T.; Lin, L. Introduction to MEMS packaging. In Microsystems and Nanotechnology; Zhou, Z., Wang, Z., Lin, L., Eds.; Springer: Berlin/Heidelberg, Germany, 2012; pp. 415–446. [Google Scholar]

- Lee, S.-H.; Mitchell, J.; Welch, W.; Lee, S.; Najafi, K. Wafer-level vacuum/hermetic packaging technologies for MEMS. In Proceedings of the Reliability, Packaging, Testing, and Characterization of MEMS/MOEMS and Nanodevices IX, San Francisco, CA, USA, 5 February 2010.

- Garcia-Blanco, S.; Topart, P.; Le Foulgoc, K.; Caron, J.-S.; Desroches, Y.; Alain, C.; Chateauneuf, F.; Jerominek, H. Hybrid wafer-level vacuum hermetic micropackaging technology for MOEMS-MEMS. In Proceedings of the Reliability, Packaging, Testing, and Characterization of MEMS/MOEMS and Nanodevices VIII, San Jose, CA, USA, 24 January 2009.

- Dragoi, V.; Pawlak, M.; Flotgen, C.; Mittendorfer, G.; Pabo, E. Wafer bonding for vacuum encapsulated MEMS. In Proceedings of the 2013 International Semiconductor Conference (CAS), Sinaia, Romania, 14–16 October 2013; pp. 17–20.

- Byeungleul, L.; Seonho, S.; Kukjin, C. A study on wafer level vacuum packaging for MEMS devices. J. Micromech. Microeng. 2003, 13, 663. [Google Scholar]

- Kullberg, R.C. Review of vacuum packaging and maintenance of MEMS and the use of getters therein. J. Micro Nanolithogr. MEMS MOEMS 2009, 8, 031307. [Google Scholar] [CrossRef]

- Shimbo, M.; Furukawa, K.; Fukuda, K.; Tanzawa, K. Silicon-to-silicon direct bonding method. J. Appl. Phys. 1986, 60, 2987–2989. [Google Scholar] [CrossRef]

- Gösele, U.; Tong, Q.-Y. Semiconductor wafer bonding. Annu. Rev. Mater. Sci. 1998, 28, 215–241. [Google Scholar] [CrossRef]

- Dragoi, V.; Matthias, T.; Rebhan, B.; Huysmans, F. Low temperature wafer bonding of CMOS wafers. In Proceedings of the 2012 IEEE 14th Electronics Packaging Technology Conference (EPTC), Singapore, 5–7 December 2012; pp. 197–201.

- Plach, T.; Dragoi, V.; Murauer, F.; Hingerl, K. Plasma activation for low temperature wafer bonding. ECS Trans. 2008, 16, 549–559. [Google Scholar]

- Henttinena, K.; Sunib, T. Silicon direct bonding. In Handbook of Silicon Based MEMS Materials and Technologies; Elsevier Inc.: Burlington, MA, USA, 2010; pp. 505–512. [Google Scholar]

- Israelachvili, J.N. Intermolecular and Surface Forces; Academic Press: San Diego, CA, USA, 2011. [Google Scholar]

- Reiche, M.; Gösele, U. Direct wafer bonding. In Handbook of Wafer Bonding; Wiley-VCH Verlag GmbH & Co. KGaA: Weinheim, Germany, 2012; pp. 81–100. [Google Scholar]

- Cozma Lapadatu, A.; Jakobsen, H. Anodic bonding-chapter thirty two. In Handbook of Silicon Based MEMS Materials and Technologies; Elsevier Inc.: Burlington, MA, USA, 2010; pp. 513–520. [Google Scholar]

- Wallis, G.; Pomerantz, D.I. Field assisted glass-metal sealing. J. Appl. Phys. 1969, 40, 3946–3949. [Google Scholar] [CrossRef]

- Lapadatu, A.C.; Schjølberg-Henriksen, K. Anodic bonding. In Handbook of Wafer Bonding; Wiley-VCH Verlag GmbH & Co. KGaA: Weinheim, Germany, 2012; pp. 63–80. [Google Scholar]

- Knechtel, R. Bonding of CMOS processed wafers-chapter thirty five. In Handbook of Silicon Based MEMS Materials and Technologies; Elsevier Inc.: Burlington, MA, USA, 2010; pp. 543–550. [Google Scholar]

- Knechtel, R. Glass frit bonding: An universal technology for wafer level encapsulation and packaging. Microsyst. Technol. 2005, 12, 63–68. [Google Scholar] [CrossRef]

- Knechtel, R. Glass frit wafer bonding. In Handbook of Wafer Bonding; Wiley-VCH Verlag GmbH & Co. KGaA: Weinheim, Germany, 2012; pp. 1–17. [Google Scholar]

- Garnier, A.; Lagoutte, E.; Baillin, X.; Gillot, C.; Sillon, N. Gold-tin bonding for 200mm wafer level hermetic MEMS packaging. In Proceedings of the IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 1610–1615.

- Demir, E.C.; Torunbalci, M.M.; Donmez, I.; Kalay, Y.E.; Akin, T. Fabrication and characterization of gold-tin eutectic bonding for hermetic packaging of MEMS devices. In Proceedings of the 2014 IEEE 16th Electronics Packaging Technology Conference (EPTC), Singapore, 3–5 December 2014; pp. 241–245.

- Choa, S.-H. Reliability study of hermetic wafer level MEMS packaging with through-wafer interconnect. Microsyst. Technol. 2009, 15, 677–686. [Google Scholar] [CrossRef]

- Belov, N.; Chou, T.K.; Heck, J.; Kornelsen, K.; Spicer, D.; Akhlaghi, S.; Wang, M.; Zhu, T. Thin-layer Au-Sn solder bonding process for wafer-level packaging, electrical interconnections and MEMS applications. In Proceedings of the IEEE International Interconnect Technology Conference, Sapporo, Japan, 1–3 June 2009; pp. 128–130.

- Torunbalci, M.M.; Demir, E.C.; Donmez, I.; Alper, S.E.; Akin, T. Gold-tin eutectic bonding for hermetic packaging of MEMS devices with vertical feedthroughs. In Proceedings of the 2014 IEEE SENSORS, Valencia, Spain, 2–5 November 2014; pp. 2187–2190.

- Cai, J.; Wang, Q.; Li, X.; Kim, W.; Wang, S.; Hwang, J.; Moon, C. Microstructure of AuSn wafer bonding for RF-MEMS packaging. In Proceedings of the 2005 6th International Conference on Electronic Packaging Technology, Shenzhen, China, 31 August–2 September 2005; pp. 1–5.

- Kim, W.; Wang, Q.; Hwang, J.; Lee, M.; Jung, K.; Ham, S.; Moon, C.; Baeks, K.; Ha, B.; Song, I. A low temperature, hermetic wafer level packaging method for RF MEMS switch. In Proceedings of the 55th Electronic Components and Technology Conference, San Diego, CA, USA, 31 May–3 June 2005; pp. 1103–1108.

- Kim, W.; Wang, Q.; Jung, K.; Hwang, J.; Moon, C. Application of Au-Sn eutectic bonding in hermetic RF MEMS wafer level packaging. In Proceedings of the 9th International Symposium on Advanced Packaging Materials: Processes, Properties and Interfaces, Atlanta, GA, USA, 24–26 March 2004; pp. 215–219.

- Yu, A.; Premachandran, C.S.; Nagarajan, R.; Kyoung, C.W.; Trang, L.Q.; Kumar, R.; Lim, L.S.; Han, J.H.; Jie, Y.G.; Damaruganath, P. Design, process integration and characterization of wafer level vacuum packaging for MEMS resonator. In Proceedings of the 2010 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 1669–1673.

- Kim, H.Y.; Yang, C.; Park, J.H.; Jung, H.; Kim, T.; Kim, K.T.; Lim, S.K.; Lee, S.W.; Mitchell, J.; Hwang, W.J.; et al. Wafer-level reliability characterization for wafer-level packaged microbolometer with ultra-small array size. In Proceedings of the Infrared Technology and Applications XXXIX, Baltimore, MD, USA, 29 April 2013.

- Oppermann, H.; Hutter, M. Au/Sn solder. In Handbook of Wafer Bonding; Wiley-VCH Verlag GmbH & Co. KGaA: Weinheim, Germany, 2012; pp. 119–138. [Google Scholar]

- Pactech Website. Available online: http://pactech.de/ (accessed on 21 October 2016).

- Oppert, T. Advanced Technologies and Equipment for 3D-packaging. Available online: http://stg.semiconrussia.org/en/sites/semiconrussia.org/files/docs/2.%20SEMI_2014_Oppert_%20PacTech%202014.pdf (accessed on 21 October 2016).

- Huang, M.L.; Huang, F.F.; Pan, J.L.; Zhang, T.X. Composition control of co-electroplating Au–Sn deposits using experimental strategies. J. Mater. Sci. Mater. Electron. 2014, 25, 4933–4942. [Google Scholar] [CrossRef]

- Pan, J.; Huang, M. Au-Sn co-electroplating solution for flip chip-LED bumps. In Proceedings of the 2010 11th International Conference on Electronic Packaging Technology & High Density Packaging (ICEPT-HDP), Xi’an, China, 16–19 August 2010; pp. 283–287.

- Sun, W.; Ivey, D.G. Development of an electroplating solution for codepositing Au–Sn alloys. Mater. Sci. Engin B 1999, 65, 111–122. [Google Scholar] [CrossRef]

- Zhang, L.; Ng Seow, C.; Li, Z.; Fang Shu, N.; Nguty, T.; de Bruin, E.; An, X.; Thoonen, H. Development of advanced AuSn alloy plating technology for semiconductor application. In Proceedings of the 2014 15th International Conference on Electronic Packaging Technology (ICEPT), Chengdu, China, 12–15 August 2014; pp. 113–116.

- Yoon, J.-W.; Chun, H.-S.; Koo, J.-M.; Jung, S.-B. Au–Sn flip-chip solder bump for microelectronic and optoelectronic applications. Microsyst. Technol. 2007, 13, 1463–1469. [Google Scholar] [CrossRef]

- Dietrich, L.; Engelmann, G.; Ehrmann, O.; Reichl, H. Gold and gold-tin wafer bumping by electrochemical deposition for flip chip and tab. DVS Berichte 1998, 191, 28–31. [Google Scholar]

- Lee, C.C.; Wang, C.Y.; Matijasevic, G.S. A new bonding technology using gold and tin multilayer composite structures. IEEE Trans. Compon. Hybrids Manuf. Technol. 1991, 14, 407–412. [Google Scholar] [CrossRef]

- Bonafede, S.; Huffman, A.; Palmer, W.D. Layer structure and thickness effects on electroplated AuSn solder bump composition. IEEE Trans. Compon. Packag. Technol. 2006, 29, 604–609. [Google Scholar] [CrossRef]

- Hutter, M.; Oppermann, H.; Engelmann, G.; Wolf, J.; Ehrmann, O.; Aschenbrenner, R.; Reichl, H. Calculation of shape and experimental creation of AuSn solder bumps for flip chip applications. In Proceedings of the 52nd Electronic Components and Technology Conference, San Diego, CA, USA, 28–31 May 2002; pp. 282–288.

- Wolffenbuttel, R.F. Low-temperature intermediate Au-Si wafer bonding; eutectic or silicide bond. Sens. Actuators A Phys. 1997, 62, 680–686. [Google Scholar] [CrossRef]

- Lin, B.W.; Wu, N.J.; Wu, Y.C.S.; Hsu, S.C. A stress analysis of transferred thin-GaN light-emitting diodes fabricated by Au-Si wafer bonding. J. Disp. Technol. 2013, 9, 371–376. [Google Scholar] [CrossRef]

- Lee, K.R.; Kim, K.; Park, H.-D.; Kim, Y.K.; Choi, S.-W.; Choi, W.B. Fabrication of capacitive absolute pressure sensor using Si-Au eutectic bonding in SOI wafer. J. Phys. Conf. Ser. 2006, 34, 393. [Google Scholar] [CrossRef]

- Mitchell, J. Low temperature wafer level vacuum packaging using Au-Si eutectic bonding and localized heating. Ph.D. Thesis, University of Michigan, Ann Arbor, MI, USA, 2008. [Google Scholar]

- Mitchell, J.; Lahiji, G.R.; Najafi, K. Encapsulation of vacuum sensors in a wafer level package using a gold-silicon eutectic. In Proceedings of the 13th International Conference on Solid-State Sensors, Actuators and Microsystems, Seoul, Korea, 5–9 June 2005; pp. 928–931.

- Mitchell, J.S.; Najafi, K. A detailed study of yield and reliability for vacuum packages fabricated in a wafer-level Au-Si eutectic bonding process. In Proceedings of the International Solid-State Sensors, Actuators and Microsystems Conference, Denver, CO, USA, 21–25 June 2009; pp. 841–844.

- Haubold, M.; Lin, Y.-C.; Frömel, J.; Wiemer, M.; Esashi, M.; Geßner, T. A novel approach for increasing the strength of an Au/Si eutectic bonded interface on an oxidized silicon surface. Microsyst. Technol. 2012, 18, 515–521. [Google Scholar] [CrossRef]

- Henry, M.D.; Ahlers, C.R. Platinum diffusion barrier breakdown in a-Si/Au eutectic wafer bonding. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 899–903. [Google Scholar] [CrossRef]

- Iliescu, C.; Poenar, D.P.; Nanyang, J.M. Aluminum-silicon and gold-silicon eutectics: New opportunities for MEMS technologies. MRS Online Proc. Libr. 2001, 687. [Google Scholar] [CrossRef]

- Jing, E.; Xiong, B.; Wang, Y. Low-temperature Au/a-Si wafer bonding. Electron. Lett. 2010, 46, 1143–1144. [Google Scholar] [CrossRef]

- Lani, S.; Bosseboeuf, A.; Belier, B.; Clerc, C.; Gousset, C.; Aubert, J. Gold metallizations for eutectic bonding of silicon wafers. Microsyst. Technol. 2006, 12, 1021–1025. [Google Scholar] [CrossRef]

- Lin, Y.C.; Baum, M.; Haubold, M.; Fromel, J.; Wiemer, M.; Gessner, T.; Esashi, M. Development and evaluation of AuSi eutectic wafer bonding. In Proceedings of the International Solid-State Sensors, Actuators and Microsystems Conference, Denver, CO, USA, 21–25 June 2009; pp. 244–247.

- Ye, T.; Song, Z.; Du, Y.; Wang, Z. Reliability of Au-Si eutectic bonding. In Proceedings of the 2014 15th International Conference on Electronic Packaging Technology (ICEPT), Chengdu, China, 12–15 August 2014; pp. 1080–1082.

- Wolffenbuttel, R.F.; Wise, K.D. Low-temperature silicon wafer-to-wafer bonding using gold at eutectic temperature. Sens. Actuators A Phys. 1994, 43, 223–229. [Google Scholar] [CrossRef]

- Hiraki, A. Low temperature reactions at Si-metal contacts –from SIO2 growth due to Si–Au reaction to the mechanism of silicide formation. Jpn. J. Appl. Phys. 1983, 22, 549. [Google Scholar] [CrossRef]

- Nakashima, K.; Iwami, M.; Hiraki, A. Low temperature diffusion of Au into Si in the Si(substrate)-Au(film) system. Thin Solid Films 1975, 25, 423–430. [Google Scholar] [CrossRef]

- Narusawa, T.; Komiya, S.; Hiraki, A. Auger spectroscopic observation of Si–Au mixed-phase formation at low temperatures. Appl. Phys. Lett. 1972, 21, 272–273. [Google Scholar] [CrossRef]

- Torunbalci, M.M.; Alper, S.E.; Akin, T. Advanced MEMS process for wafer level hermetic encapsulation of MEMS devices using SOI cap wafers with vertical feedthroughs. J. Microelectromech. Syst. 2015, 24, 556–564. [Google Scholar] [CrossRef]

- Crnogorac, F.; Birringer, R.; Dauskardt, R.; Pease, F. Aluminum-germanium eutectic bonding for 3D integration. In Proceedings of the IEEE International Conference on 3D System Integration, San Francisco, CA, USA, 28–30 September 2009; pp. 1–5.

- Goßler, C.; Kunzer, M.; Baum, M.; Wiemer, M.; Moser, R.; Passow, T.; Köhler, K.; Schwarz, U.T.; Wagner, J. Aluminum–germanium wafer bonding of (AlGain)N thin-film light-emitting diodes. Microsyst. Technol. 2012, 19, 655–659. [Google Scholar] [CrossRef]

- Zavracky, P.M.; Vu, B. Patterned eutectic bonding with Al/Ge thin films for MEMS. In Proceedings of the Micromachining and Microfabrication Process Technology, Austin, TX, USA, 23 October 1995; pp. 46–52.

- Perez-Quintana, I.; Ottaviani, G.; Tonini, R.; Felisari, L.; Garavaglia, M.; Oggioni, L.; Morin, D. An aluminum-germanium eutectic structure for silicon wafer bonding technology. Phys. Status Solidi C 2005, 2, 3706–3709. [Google Scholar] [CrossRef]

- Park, W.-T.; Jang, J.-W.; Clare, T.; Liu, L. Microstructure and mechanical properties of aluminum–germanium eutectic bonding with polysilicon metallization for microelectromechanical systems (MEMS) packaging. Scr. Mater. 2011, 64, 733–736. [Google Scholar] [CrossRef]

- Chidambaram, V.; Wickramanayaka, S. Al-Ge diffusion bonding for hermetic sealing application. J. Electron. Mater. 2015, 44, 2387–2395. [Google Scholar] [CrossRef]

- Chidambaram, V.; Yeung, H.; Shan, G. Development of metallic hermetic sealing for MEMS packaging for harsh environment applications. J. Electron. Mater. 2012, 41, 2256–2266. [Google Scholar] [CrossRef]

- Sood, S.; Farrens, S.; Pinker, R.; Xie, J.; Cataby, W. Al-Ge eutectic wafer bonding and bond characterization for CMOS compatible wafer packaging. ECS Trans. 2010, 33, 93–101. [Google Scholar]

- Gu, A.; Lin, P.-C.; Chang, V.; Li, T.; Zhang, J.-W.; Jiang, J.-Y.; Xing, C. Study on Al-Ge bonding and quality improvement in CMEMS process. ECS Trans. 2012, 44, 1393–1399. [Google Scholar]

- Chua, G.L.; Chen, B.; Singh, N. Investigation of Al and Ge surfaces for Al-Ge wafer level eutectic bonding. In Proceedings of the 2015 IEEE 17th Electronics Packaging and Technology Conference (EPTC), Singapore, 2–4 December 2015; pp. 1–5.

- Nasiri, S. New innovations in MEMS fabrications are responsible for meeting the demand for low-cost intertial sensors for consumer markets. In Proceedings of the International Symposium on Microelectronics, San Jose, CA, USA, 11–15 November 2007; pp. 407–412.

- Nasiri, S.S.; Flannery, A.F. Method of fabrication of a Al/Ge bonding in a wafer packaging environment and a product produced therefrom. US Patent 7,442,570, October 2008. [Google Scholar]

- Clarke, P. InvenSense Opens up Process to Enable Fabless MEMS. EE Times. 2012. Available online: http://www.eetimes.com/document.asp?doc_id=1261856 (accessed on 21 October 2016).

- Crnogorac, F.; Pease, F.R.W.; Birringer, R.P.; Dauskardt, R.H. Low-temperature Al–Ge bonding for 3D integration. J. Vac. Sci. Technol. B 2012, 30, 06FK01. [Google Scholar] [CrossRef]

- Jacobson, D.M.; Humpston, G. Diffusion soldering. Solder. Surf. Mt. Technol. 1992, 4, 27–32. [Google Scholar] [CrossRef]

- Hoivik, N.; Aasmundtveit, K. Wafer-level solid–liquid interdiffusion bonding. In Handbook of Wafer Bonding; Wiley-VCH Verlag GmbH & Co. KGaA: Weinheim, Germany, 2012; pp. 181–214. [Google Scholar]

- Reed, J.D.; Lueck, M.; Gregory, C.; Huffman, C.A.; Lannon, J.M.; Temple, D. Reliability and ultra-low temperature bonding of high density large area arrays with Cu/Sn-Cu interconnects for 3D integration. In Proceedings of the 2010 International Interconnect Technology Conference (IITC), Burlingame, CA, USA, 6–9 June 2010; pp. 1–3.

- Reed, J.D.; Lueck, M.; Gregory, C.; Huffman, A.; Lannon, J.M.; Temple, D. High density interconnect at 10um pitch with mechanically keyed Cu/Sn-Cu and Cu-Cu bonding for 3-D integration. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 846–852.

- Tanida, K.; Umemoto, M.; Tomita, Y.; Tago, M.; Nemoto, Y.; Ando, T.; Takahashi, K. Ultra-high-density 3D chip stacking technology. In Proceedings of the 53rd Electronic Components and Technology Conference, New Orleans, LA, USA, 27–30 May 2003; pp. 1084–1089.

- He, L.; Salomonsen, G.; Kaiying, W.; Aasmundtveit, K.E.; Hoivik, N. Wafer-level Cu/Sn to Cu/Sn slid-bonded interconnects with increased strength. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1350–1358. [Google Scholar]

- Lueck, M.R.; Reed, J.D.; Gregory, C.W.; Huffman, A.; Lannon, J.M.; Temple, D.S. High-density large-area-array interconnects formed by low-temperature Cu/Sn—Cu bonding for three-dimensional integrated circuits. IEEE Trans. Electron. Devices 2012, 59, 1941–1947. [Google Scholar] [CrossRef]

- Lannon, J.M.; Gregory, C.; Lueck, M.; Reed, J.D.; Huffman, C.A.; Temple, D. High density metal—Metal interconnect bonding for 3-D integration. IEEE Trans. Compon. Packag. Manuf. Technol. 2012, 2, 71–78. [Google Scholar] [CrossRef]

- Xu, H.; Suni, T.; Vuorinen, V.; Li, J.; Heikkinen, H.; Monnoyer, P.; Paulasto-Kröckel, M. Wafer-level slid bonding for MEMS encapsulation. Adv. Manuf. 2013, 1, 226–235. [Google Scholar] [CrossRef]

- Xu, H.; Rautiainen, A.; Vuorinen, V.; Osterlund, E.; Suni, T.; Heikkinen, H.; Monnoyer, P.; Paulasto-Krockel, M. Reliability performance of Au-Sn and Cu-Sn wafer level slid bonds for MEMS. In Proceedings of the Electronics System-Integration Technology Conference (ESTC), Helsinki, Finland, 16–18 September 2014; pp. 1–5.

- Van de Wiel, H.J.; Vardoy, A.S.B.; Hayes, G.; Kouters, M.H.M.; van der Waal, A.; Erinc, M.; Lapadatu, A.; Martinsen, S.; Taklo, M.M.V.; Fischer, H.R. Systematic characterization of key parameters of hermetic wafer-level Cu-Sn slid bonding. In Proceedings of the European Microelectronics Packaging Conference (EMPC), Grenoble, France, 9–12 September 2013; pp. 1–6.

- Van de Wiel, H.J.; Vardoy, A.S.B.; Hayes, G.; Fischer, H.R.; Lapadatu, A.; Taklo, M.M.V. Characterization of hermetic wafer-level Cu-Sn slid bonding. In Proceedings of the 4th Electronic System-Integration Technology Conference (ESTC), Amsterdam, The Netherlands, 17–20 September 2012; pp. 1–7.

- Schmid, U.; Flötgen, C.; Pawlak, M.; Pabo, E.; van de Wiel, H.J.; Hayes, G.R.; Dragoi, V.; Sánchez de Rojas Aldavero, J.L.; Leester-Schaedel, M. Cu-Sn transient liquid phase wafer bonding for MEMS applications. In Proceedings of the Smart Sensors, Actuators, and MEMS VI, Grenoble, France, 24 April 2013.

- Pham, N.P.; Limaye, P.; Czarnecki, P.; Olalla, V.P.; Cherman, V.; Tezcan, D.S.; Tilmans, H.A.C. Metal-bonded, hermetic 0-level package for MEMS. In Proceedings of the 12th Electronics Packaging Technology Conference (EPTC), Singapore, 8–10 December 2010; pp. 1–6.

- Marauska, S.; Claus, M.; Lisec, T.; Wagner, B. Low temperature transient liquid phase bonding of Au/Sn and Cu/Sn electroplated material systems for MEMS wafer-level packaging. Microsyst. Technol. 2012, 19, 1119–1130. [Google Scholar] [CrossRef]

- Ani, D.; Aasmundtveit, K.; Hoivik, N. Ultra-low leak detection of Cu-Sn slid for high density wafer level packaging. In Proceedings of the 2011 12th International Conference on Electronic Packaging Technology and High Density Packaging (ICEPT-HDP), Shanghai, China, 8–11 August 2011; pp. 1–4.

- Taklo, M.M.V.; Vardøy, A.-S.; De Wolf, I.; Simons, V.; van de Wiel, H.J.; van der Waal, A.; Lapadatu, A.; Martinsen, S.; Wunderle, B. Residual stress in silicon caused by Cu-Sn wafer-level packaging. In Proceedings of the ASME 2013 International Technical Conference and Exhibition on Packaging and Integration of Electronic and Photonic Microsystems, Burlingame, CA, USA, 16–18 July 2013.

- Forsberg, F.; Roxhed, N.; Fischer, A.C.; Samel, B.; Ericsson, P.; Hoivik, N.; Lapadatu, A.; Bring, M.; Kittilsland, G.; Stemme, G.; et al. Very large scale heterogeneous integration (VLSHI) and wafer-level vacuum packaging for infrared bolometer focal plane arrays. Infrared Phys. Technol. 2013, 60, 251–259. [Google Scholar] [CrossRef]

- Hilton, A.; Temple, D.; Lannon, J.M.; Schimert, T.; Gooch, R.; Trujillo, C.; Miskimins, S.; Chuan, L. Wafer-level vacuum packaging of microbolometer-based infared imagers. In Proceedings of the International Wafer-Level Packaging Conference, San Jose, CA, USA, 19–20 October 2016.

- Li, C.; Han, C.J.; Skidmore, G.D.; Cook, G.; Kubala, K.; Bates, R.; Temple, D.; Lannon, J.; Hilton, A.; Glukh, K.; et al. Low-cost uncooled VOx infrared camera development. In Proceedings of the Infrared Technology and Applications XXXIX, Baltimore, MD, USA, 2013.

- Ramanarayanan, T.; Rapp, R. The diffusivity and solubility of oxygen in liquid tin and solid silver and the diffusivity. Metall. Trans. 1972, 3, 3239–3246. [Google Scholar] [CrossRef]

- Wei, L.; Lee, Y.C. Study of fluxless soldering using formic acid vapor. IEEE Trans. Adv. Packag. 1999, 22, 592–601. [Google Scholar]

- Liu, H.; Wang, K.; Aasmundtveit, K.; Hoivik, N. Intermetallic Cu3Sn as oxidation barrier for fluxless Cu-Sn bonding. In Proceedings of the 2010 Proceedings 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 853–857.

- Hoivik, N.; Kaiying, W.; Aasmundtveit, K.; Salomonsen, G.; Lapadatu, A.; Kittilsland, G.; Stark, B. Fluxless wafer-level Cu-Sn bonding for micro- and nanosystems packaging. In Proceedings of the 3rd Electronic System-Integration Technology Conference (ESTC), Berlin, Germany, 13–16 September 2010; pp. 1–5.

- Bosco, N.S.; Zok, F.W. Critical interlayer thickness for transient liquid phase bonding in the Cu–Sn system. Acta Mater. 2004, 52, 2965–2972. [Google Scholar] [CrossRef]

- Luu, T.-T.; Duan, A.; Aasmundtveit, K.; Hoivik, N. Optimized Cu-Sn wafer-level bonding using intermetallic phase characterization. J. Electron. Mater. 2013, 42, 3582–3592. [Google Scholar] [CrossRef]

- Luu, T.-T.; Duan, A.; Wang, K.; Aasmundtveit, K.E.; Hoivik, N. Optimization of Cu/Sn wafer-level bonding based upon intermetallic characterization. In Proceedings of the 2012 4th Electronic System-Integration Technology Conference (ESTC), Amsterdam, The Netherlands, 17–20 September 2012; pp. 1–5.

- Luu, T.-T. Solid Liquid Inter-Diffusion Wafer-Level Bonding for MEMS Packaging. Ph.D. Thesis, Buskerud and Vestfold University College, Horten, Norway, July 2015. [Google Scholar]

- Chiu, T.C.; Zeng, K.; Stierman, R.; Edwards, D.; Ano, K. Effect of thermal aging on board level drop reliability for Pb-free BGA packages. In Proceedings of the 54th Electronic Components and Technology Conference, Las Vegas, NV, USA, 1–4 June 2004; pp. 1256–1262.

- Borgesen, P.; Yin, L.; Kondos, P.; Henderson, D.W.; Servis, G.; Therriault, J.; Wang, J.; Srihari, K. Sporadic degradation in board level drop reliability—Those aren’t all kirkendall voids! In Proceedings of the 2007 57th Electronic Components and Technology Conference, Sparks, NV, USA, 29 May–1 June 2007; pp. 136–146.

- Zou, J.; Mo, L.; Wu, F.; Wang, B.; Liu, H.; Zhang, J.; Wu, Y. Effect of Cu substrate and solder alloy on the formation of kirkendall voids in the solder joints during thermal aging. In Proceedings of the 2010 11th International Conference on Electronic Packaging Technology & High Density Packaging (ICEPT-HDP), Xi’an, China, 16–19 August 2010; pp. 944–948.

- Yang, W.; Messler, R.W.; Felton, L.E. Microstructure evolution of eutectic Sn-Ag solder joints. J. Electron. Mater. 1994, 23, 765–772. [Google Scholar] [CrossRef]

- Kim, J.Y.; Yu, J. Effects of residual impurities in electroplated Cu on the kirkendall void formation during soldering. Appl. Phys. Lett. 2008, 92, 092109. [Google Scholar] [CrossRef]

- Yu, J.; Kim, J.Y. Effects of residuals on kirkendall void formation at Cu/Sn–3.5Ag solder joints. Acta Mater. 2008, 56, 5514–5523. [Google Scholar] [CrossRef]

- Kumar, S.; Handwerker, C.A.; Dayananda, M.A. Intrinsic and interdiffusion in Cu-Sn system. J. Ph. Equilib. Diffus. 2011, 32, 309–319. [Google Scholar] [CrossRef]

- Labie, R.; Limaye, P.; Lee, K.; Berry, C.; Beyne, E.; Wolf, I.D. Reliability testing of Cu-Sn intermetallic micro-bump interconnections for 3D-device stacking. In Proceedings of the 2010 3rd Electronic System-Integration Technology Conference (ESTC), Berlin, Germany, 13–16 September 2010; pp. 1–5.

- Labie, R.; Ruythooren, W.; Baert, K.; Beyne, E.; Swinnen, B. Resistance to electromigration of purely intermetallic micro-bump interconnections for 3D-device stacking. In Proceedings of the 2008 International Interconnect Technology Conference, Burlingame, CA, USA, 1–4 June 2008; pp. 19–21.

- Mu, D.; Huang, H.; Mcdonald, S.D.; Nogita, K. Creep and mechanical properties of Cu6Sn5 and (Cu,Ni)6Sn5 at elevated temperatures. J. Electron. Mater. 2013, 42. [Google Scholar] [CrossRef]

- Rautiainen, A.; Xu, H.; Österlund, E.; Li, J.; Vuorinen, V.; Paulasto-Kröckel, M. Microstructural characterization and mechanical performance of wafer-level slid bonded Au-Sn and Cu-Sn seal rings for MEMS encapsulation. J. Electron. Mater. 2015, 44, 4533–4548. [Google Scholar] [CrossRef]

- Gregory, C.; Lueck, M.; Huffman, A.; Lannon, J.M.; Temple, D.S. High density metal-metal interconnect bonding with pre-applied fluxing underfill. In Proceedings of the 2012 IEEE 62nd Electronic Components and Technology Conference, San Diego, CA, USA, 29 May–1 June 2012; pp. 20–25.

- Duffy, D.; Gregory, C.; Breach, C.; Huffman, A. 3D and 2.5D packaging assembly with highly silica filled one step chip attach materials for both thermal compression bonding and mass reflow processes. In Proceedings of the 2014 IEEE 64th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 27–30 May 2014; pp. 1803–1809.

- Ghosh, G. Elastic properties, hardness, and indentation fracture toughness of intermetallics relevant to electronic packaging. J. Mater. Res. 2004, 19, 1439–1454. [Google Scholar] [CrossRef]

- Siewert, T.; Liu, S.; Smith, D.R.; Madeni, J.C. Database for Solder Properties with Emphasis on New Lead-free Solders. 2002. Available online: http://www.msed.nist.gov/solder/NIST_LeadfreeSolder_v4.pdf (accessed on 24 October 2016). [Google Scholar]

- Johnson, R.W.; Cai, W.; Yi, L.; Scofield, J.D. Power device packaging technologies for extreme environments. IEEE Trans. Electron. Packag. Manuf. 2007, 30, 182–193. [Google Scholar] [CrossRef]

- Aasmundtveit, K.E.; Thi-Thuy, L.; Vardoy, A.S.B.; Tollefsen, T.A.; Kaiying, W.; Hoivik, N. High-temperature shear strength of solid-liquid interdiffusion (SLID) bonding: Cu-Sn, Au-Sn and Au-In. In Proceedings of the Electronics System-Integration Technology Conference (ESTC), Helsinki, Finnland, 16–18 September 2014; pp. 1–6.

- Tollefsen, T.A.; Taklo, M.M.V.; Aasmundtveit, K.E.; Larsson, A. Reliable HT electronic packaging—Optimization of a Au-Sn slid joint. In Proceedings of the 2012 4th Electronic System-Integration Technology Conference (ESTC), Amsterdam, The Netherlands, 17–20 September 2012; pp. 1–6.

- Tollefsen, T.; Larsson, A.; Taklo, M.; Neels, A.; Maeder, X.; Høydalsvik, K.; Breiby, D.; Aasmundtveit, K. Au-Sn slid bonding: A reliable HT interconnect and die attach technology. Metall. Mater. Trans. B 2013, 44, 406–413. [Google Scholar] [CrossRef]

- Tollefsen, T.; Larsson, A.; Løvvik, O.; Aasmundtveit, K. Au-Sn slid bonding—Properties and possibilities. Metall. Mater. Trans. B 2012, 43, 397–405. [Google Scholar] [CrossRef]

- Giudice, S.; Bosshard, C. Au-Sn transient liquid phase bonding for hermetic sealing and getter activation. In Proceedings of the 2013 European Microelectronics Packaging Conference (EMPC), Grenoble, France, 9–12 September 2013; pp. 1–5.

- Cain, S.; Wilcox, J.; Venkatraman, R. A diffusional model for transient liquid phase bonding. Acta Mater. 1997, 45, 701–707. [Google Scholar] [CrossRef]

- Rodriguez, R.; Ibitayo, D.; Quintero, P. Kinetics of dissolution and isothermal solidification for gold-enriched solid–liquid interdiffusion (SLID) bonding. J. Electron. Mater. 2013, 42, 2677–2685. [Google Scholar] [CrossRef]

- Venkatraman, R.; Wilcox, J.; Cain, S. Experimental study of the kinetics of transient liquid phase solidification reaction in electroplated gold-tin layers on copper. Metall. Mater. Trans. A 1997, 28, 699–706. [Google Scholar] [CrossRef]

- Vuorinen, V.; Dong, H.; Xu, H.; Vahanen, S.; Suni, T.; Laurila, T.; Paulasto-Krockel, M. Analysis of microstructural evolution in slid-bonding used for hermetic encapsulation of MEMS devices. In Proceedings of the 2012 4th Electronic System-Integration Technology Conference (ESTC), Amsterdam, The Netherlands, 17–20 September 2012; pp. 1–5.

- Zhong, C.H.; Yi, S. Solder joint reliability of plastic ball grid array packages. Solder. Surf. Mt. Technol. 1999, 11, 44–48. [Google Scholar] [CrossRef]

- Alam, M.O.; Chan, Y.C.; Tu, K.N. Elimination of Au-embrittlement in solder joints on Au/Ni metallization. J. Mater. Res. 2004, 19, 1303–1306. [Google Scholar] [CrossRef]

- Grummel, B.; Mustain, H.A.; Shen, Z.J.; Hefner, A.R. Reliability study of Au-In transient liquid phase bonding for SIC power semiconductor packaging. In Proceedings of the 2011 IEEE 23rd International Symposium on Power Semiconductor Devices and ICs (ISPSD), San Diego, CA, USA, 23–26 May 2011; pp. 260–263.

- Grummel, B.J.; Shen, Z.J.; Mustain, H.A.; Hefner, A.R. Thermo-mechanical characterization of Au-In transient liquid phase bonding die-attach. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 716–723. [Google Scholar] [CrossRef]

- Mustain, H.; Brown, W.D.; Ang, S.S. Transient liquid phase die attach for high-temperature silicon carbide power devices. IEEE Trans. Compon. Packag. Technol. 2010, 33, 563–570. [Google Scholar] [CrossRef]

- Qian, W.; Kyudong, J.; Minseog, C.; Woonbae, K.; Sukjin, H.; Byunggil, J.; Changyoul, M. Low temperature, wafer level Au-In bonding for ISM packaging. In Proceedings of the 7th International Conference on Electronic Packaging Technology, Shanghai, China, 26–29 August 2006; pp. 1–5.

- Zhang, W.; Matin, A.; Beyne, E.; Ruythooren, W. Optimizing Au and In micro-bumping for 3D chip stacking. In Proceedings of the 58th Electronic Components and Technology Conference, Lake Buena Vista, FL, USA, 27–30 May 2008; pp. 1984–1989.

- Zhang, W.; Ruythooren, W. Study of the Au/In reaction for transient liquid-phase bonding and 3D chip stacking. J. Electron. Mater. 2008, 37, 1095–1101. [Google Scholar] [CrossRef]

- Wang, T.B.; Shen, Z.Z.; Ye, R.Q.; Xie, X.M.; Stubhan, F.; Freytag, J. Die bonding with Au/In isothermal solidification technique. J. Electron. Mater. 2000, 29, 443–447. [Google Scholar] [CrossRef]

- Welch, W.C.; Najafi, K. Gold-indium transient liquid phase (TLP) wafer bonding for MEMS vacuum packaging. In Proceedings of the IEEE 21st International Conference on Micro Electro Mechanical Systems, Tucson, AZ, USA, 13–17 January 2008; pp. 806–809.

- Yoon-Chul, S.; Qian, W.; Suk-jin, H.; Byung-Gil, J.; Kyu-Dong, J.; Min-Seog, C.; Woon-Bae, K.; Chang-Youl, M. Wafer-level low temperature bonding with Au-In system. In Proceedings of the 57th Electronic Components and Technology Conference, Sparks, NV, USA, 29 May–1 June 2007; pp. 633–637.

- Lee, C.C.; Wang, C.Y.; Matijasevic, G. Au-In bonding below the eutectic temperature. IEEE Trans. Compon. Hybrids Manuf. Technol. 1993, 16, 311–316. [Google Scholar] [CrossRef]

- So, W.W.; Lee, C.C. Fluxless process of fabricating In-Au joints on copper substrates. IEEE Trans. Compon. Packag. Technol. 2000, 23, 377–382. [Google Scholar] [CrossRef]

- Bjøntegaard, J.; Buene, L.; Finstad, T.; Lønsjø, O.; Olsen, T. Low temperature interdiffusion in Au/In thin film couples. Thin Solid Films 1983, 101, 253–262. [Google Scholar] [CrossRef]

- Lian, J.; Chun, S.; Goorsky, M.; Wang, J. Mechanical behavior of Au-In intermetallics for low temperature solder diffusion bonding. J. Mater. Sci. 2009, 44, 6155–6161. [Google Scholar] [CrossRef]

- Yu, C.-F.; Cheng, H.-C.; Chen, W.-H. Structural, mechanical and thermodynamic properties of AuIn2 crystal under pressure: A first-principles density functional theory calculation. J. Alloys Compd. 2015, 619, 576–584. [Google Scholar] [CrossRef]

- Huffman, A. Bump interconnect for 2.5D and 3D integration. In Handbook of 3D Integration; Wiley-VCH Verlag GmbH & Co. KGaA: Weinheim, Germany, 2014; pp. 313–324. [Google Scholar]

- Froemel, J.; Baum, M.; Wiemer, M.; Roscher, F.; Haubold, M.; Jia, C.; Gessner, T. Investigations of thermocompression bonding with thin metal layers. In Proceedings of the 2011 16th International Solid-State Sensors, Actuators and Microsystems Conference (TRANSDUCERS), Beijing, China, 5–9 June 2011; pp. 990–993.

- Yun, C.H.; Martin, J.; Chen, L.; Frey, T. Clean and conductive wafer bonding for MEMS. ECS Trans. 2008, 16, 117–124. [Google Scholar]

- Xu, D.; Jing, E.; Xiong, B.; Wang, Y. Wafer-level vacuum packaging of micromachined thermoelectric IR sensors. IEEE Trans. Adv. Packag. 2010, 33, 904–911. [Google Scholar] [CrossRef]

- Tan, C.S.; Fan, J. Wafer level hermetic packaging with IMC-less Cu-Cu bonding for 3D microsystems. In Proceedings of the 2011 6th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, Taiwan, 19–21 October 2011; pp. 339–342.

- Tan, C.S.; Peng, L.; Fan, J.; Li, H.; Gau, S. Three-dimensional wafer stacking using Cu—Cu bonding for simultaneous formation of electrical, mechanical, and hermetic bonds. IEEE Trans. Device Mater. Reliab. 2012, 12, 194–200. [Google Scholar] [CrossRef]

- Fan, J.; Lim, D.F.; Peng, L.; Li, K.H.; Tan, C.S. Effect of bonding temperature on hermetic seal and mechanical support of wafer-level Cu-to-Cu thermo-compression bonding for 3D integration. Microsyst. Technol. 2013, 19, 661–667. [Google Scholar] [CrossRef]

- Lim, D.F.; Fan, J.; Peng, L.; Leong, K.C.; Tan, C.S. Cu–Cu hermetic seal enhancement using self-assembled monolayer passivation. J. Electron. Mater. 2013, 42, 502–506. [Google Scholar] [CrossRef]

- Peng, L.; Fan, J.; Li, H.Y.; Gao, S.; Tan, C.S. Simultaneous formation of electrical connection, mechanical support and hermetic seal with bump-less Cu-Cu bonding for 3D wafer stacking. In Proceedings of the 2012 International Symposium on VLSI Technology, Systems, and Applications (VLSI-TSA), Hsinchu, Taiwan, 23–25 April 2012; pp. 1–2.

- Peng, L.; Li, H.Y.; Lim, D.F.; Gao, S.; Tan, C.S. Thermal reliability of fine pitch cu-cu bonding with self-assembled monolayer (SAM) passivation for wafer-on-wafer 3D-stacking. In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 22–26.

- Tan, C.S.; Lim, D.F.; Singh, S.G.; Goulet, S.K.; Bergkvist, M. Cu–Cu diffusion bonding enhancement at low temperature by surface passivation using self-assembled monolayer of alkane-thiol. Appl. Phys. Lett. 2009, 95, 192108. [Google Scholar] [CrossRef]

- Peng, L.; Li, H.; Lim, D.F.; Gao, S.; Tan, C.S. High-density 3-D interconnect of Cu—Cu contacts with enhanced contact resistance by self-assembled monolayer (SAM) passivation. IEEE Trans. Electron. Devices 2011, 58, 2500–2506. [Google Scholar] [CrossRef]

- 13-diffusion in metals. In Smithells Metals Reference Book, 7th ed.; Brandes, E.A.; Brook, G.B. (Eds.) Butterworth-Heinemann: Oxford, UK, 1992; pp. 13-11–13-119.

- Morrison, H.M.; Yuen, V.L.S. Self-diffusion in gold. Can. J. Phys. 1971, 49, 2704–2709. [Google Scholar] [CrossRef]

- US Department of Defense, Test Methods Standard. Mil-STD-883e Method 1010.7. 1996. Available online: http://scipp.ucsc.edu/groups/fermi/electronics/mil-std-883.pdf (accessed on 25 October 2016).

- US Department of Defense, Test Methods Standard. Mil-STD-750eEnvironmental Test Methods for Semiconductor Devices. 2012. Available online: https://snebulos.mit.edu/projects/reference/MIL-STD/MIL-STD-750-1.pdf (accessed on 25 October 2016).

- Prodromides, A.E.; Scheuerlein, C.; Taborelli, M. Lowering the activation temperature of TiZrV non-evaporable getter films. Vacuum 2001, 60, 35–41. [Google Scholar] [CrossRef]

- Oneida Research Services. Available online: https://www.orslabs.com/ (accessed on 24 October 2016).

- Paquet, A.; Deshaies, S.; Desroches, Y.; Whalin, J.; Topart, P. Influence of ceramic package internal components on the performance of vacuum sealed uncooled bolometric detectors. In Proceedings of the Reliability, Packaging, Testing, and Characterization of MOEMS/MEMS and Nanodevices XII, San Francisco, CA, USA, 2 February 2013.

- Ko, C.-T.; Chen, K.-N. Low temperature bonding technology for 3D integration. Microelectron. Reliab. 2012, 52, 302–311. [Google Scholar] [CrossRef]

| Comparison of Bonding Approaches for Smart Sensors | |||||||

|---|---|---|---|---|---|---|---|

| Bonding Approach | Bonding Temperature (°C) | Topography Tolerance | Outgassing | Substrate Flexibility | Seal Area | CMOS Compatibility | |

| Traditional Approaches | Anodic | 300–450 | Low | High | Low | Low | Poor |

| Direct | >800 | Very low | Mid | Low | Low | Poor | |

| Glass frit | 430–450 | High | High | Low | High | Good | |

| Metal Bonding Approaches | Eutectic | >200 | High | Low | High | Low | Good |

| SLID | >200 | High | Low | High | Low | Good | |

| Metal-to-metal | >250 | Low | Low | High | Low | Good | |

| Comparison of Metal-Based Bonding Approaches | ||

|---|---|---|

| Bonding Approach | Main Advantages | Main Disadvantages |

| Eutectic alloy |

|

|

| SLID |

|

|

| Metal-to-metal |

|

|

| Eutectic Bonding Alloys and Corresponding Eutectic Temperatures | |||

|---|---|---|---|

| Alloy | Eutectic Temperature (°C) | Advantages | Disadvantages |

| Au0.8Sn0.2 | 280 |

|

|

| Au0.82Si0.18 | 363 |

|

|

| Al0.72Ge0.28 | 423 |

|

|

| Comparison of Gold-Tin (Au-Sn) Eutectic Deposition Methods | ||

|---|---|---|

| Deposition Method | Main Advantages | Main Disadvantages |

| Ball laser jetting |

|

|

| Electroplating Au0.8Sn0.2 alloy |

|

|

| Alternating layers of Au and Sn |

|

|

| Materials Properties of Copper-Tin (Cu-Sn) Solid-Liquid Interdiffusion (SLID) Compounds and Common Solders | ||||||

|---|---|---|---|---|---|---|

| Metallurgy | Bonding Temperature (°C) | Compound | Elastic Modulus (GPa) | Yield Strength (MPa) | CTE (ppm K−1) | Melting Temperature (°C) |

| Cu-Sn SLID | >230 | Cu | 110 | 180 | 17 | 1084 |

| Sn | 41 | 35 | 23 | 232 | ||

| Cu3Sn(ɛ phase) | 79–153 | 1787 | 19 | 676 | ||

| Cu6Sn5(ɲ phase) | 84–119 | 2009 | 16 | 415 | ||

| Common Solders | >185 | Pb0.38Sn0.62 wt% | 15.7 | 30.2 | 18.7 | 183 |

| >220 | SnAg0.03 wt% | 26.2 | 50 | 20 | 221 | |

| Materials Properties of Compounds Formed During Slid Bonding | |||||

|---|---|---|---|---|---|

| Metallurgy | Bonding Temperature (°C) | Compound | Elastic Modulus (GPa) | CTE (ppm K−1) | Melting Temperature (°C) |

| Gold-Tin (Au-Sn) Solid-Liquid Interdiffusion (SLID) | >280 | Au | 77.2 | 14.4 | 1064 |

| Sn | 41 | 23 | 232 | ||

| AuSn (δ phase) | 70–101 | 14 | 419 | ||

| Eutectic AuSn (mixture of δ and ζ’) | 69–74 | 16 | 278 | ||

| Au5Sn (ζ’ phase) | 62–76 | 18 | 190 | ||

| AuSn0.18–0.10 at % (ζ phase) | 58 | 20 | 519 | ||

| Au10Sn (β phase) | 88 | N/A | 532 | ||

| Properties of Commonly Used Materials for Metal-to-Metal Thermocompression Bonding | |||||

|---|---|---|---|---|---|

| Metal | Bonding Temperature (°C) | Self-Diffusivity (m2/s) | Activation Energy (eV) | CTE (μm/m·K at 25 °C) | Melting Temperature (°C) |

| Aluminum (Al) | >400 | 4.2 × 10−19 (at 500 °C) | 1.49 | 23.1 | 660 |

| Copper (Cu) | >350 | 4.2 × 10−14 (at 500 °C) | 2.19 | 16.5 | 1084 |

| Gold (Au) | >260 | 1.0 × 10−18–1.0 × 10−19 (at 400 °C) | 1.81 | 14.2 | 1064 |

| Summary of Bonding Approaches Reviewed | ||||

|---|---|---|---|---|

| Bonding Type | Material | Bonding Temperature (°C) | Primary Advantages | Primary Disadvantages |

| Eutectic | Au0.8Sn0.2 | >280 |

|

|

| Au0.82Si0.18 | >363 |

|

| |

| Al0.72Ge0.28 | >423 |

|

| |

| Solid-liquid diffusion (SLID) | Cu-Sn | >232 |

|

|

| Au-Sn | >280 |

|

| |

| Au-In | >156 |

|

| |

| Metal-to-Metal | Al | >400 |

|

|

| Cu | >350 |

|

| |

| Au | >260 |

|

| |

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hilton, A.; Temple, D.S. Wafer-Level Vacuum Packaging of Smart Sensors. Sensors 2016, 16, 1819. https://doi.org/10.3390/s16111819

Hilton A, Temple DS. Wafer-Level Vacuum Packaging of Smart Sensors. Sensors. 2016; 16(11):1819. https://doi.org/10.3390/s16111819

Chicago/Turabian StyleHilton, Allan, and Dorota S. Temple. 2016. "Wafer-Level Vacuum Packaging of Smart Sensors" Sensors 16, no. 11: 1819. https://doi.org/10.3390/s16111819