1. Introduction

Recently, CMOS image sensors (CISs) have replaced charge-coupled devices (CCD) in most applications due to their low power consumption, high speed, and low cost. Since CISs are built using the same CMOS manufacturing processes used for building analog and digital integrated circuits (ICs), they are suitable for system-on-chip (SOC) integration. CIS SOCs integrate readout electronics, digital control, timing, and image processing circuits and other system components on the same die to build compact imaging systems. In addition, the introduction of backside illumination (BSI) has improved the pixel fill factor and quantum efficiency of CIS pixels that in turn has improved low-light performance, surpassing CCD quality.

Today, low-power consumption is a critical requirement that enables standalone operation of sensors and systems in isolated environments for extended durations. This becomes especially critical for implantable medical systems [

1,

2,

3]. A system capable of harvesting ambient energy in the environment can achieve significantly longer operating lifetime. Integrating an energy harvester on the same silicon die to power up the system can avoid many unnecessary energy loss paths while conserving available energy. Since most CISs operate in illuminated environments, photovoltaic (PV) energy harvesting is the natural choice among all the different kinds of energy harvesters. PV energy harvesters have relatively high conversion efficiency and they are compatible with standard CMOS processes as well [

4,

5].

A CIS can achieve energy autonomous operation by harvesting its own energy from light in the environment it is placed in. However, in order to achieve this, it is imperative to design it by using ultra-low power design techniques at all levels of abstraction, while maximizing the energy harvesting and management efficiencies. Several CIS designs with integrated energy harvesting photodiodes have been reported in the past [

1,

6,

7,

8,

9]. The self-powered image sensor (SPS) concept introduced in [

6,

7] is based on connecting a floating photodiode in series with the battery supply. Thus, despite its name, the SPS is not really self-powered, but rather generates only a boosted supply voltage. Pixels proposed in [

8,

9] are based on reconfigurable PN-junctions that could perform both image capture and energy harvesting operations. However, drain junctions of the pixel transistors connected to the anode of energy harvesting photodiode cause significant leakage decreasing the energy harvesting efficiency In pixel transistors receive light and light induced leakage in a PN-junction is much higher than reverse leakage current of an unilluminated junction. The light induced leakage of the reverse biased drain to the substrate junctions of these transistors decreases the energy harvesting efficiency significantly. The energy harvesting and imaging (EHI) pixel structure introduced in [

1] is also based on reconfigurable PN-junction photodiodes. As opposed to others, better energy harvesting efficiency was achieved in EHI by decoupling the anode of the energy harvesting photodiode from pixel transistors and other loss paths. However, high power consumption of readout electronics and low energy harvesting capability of the EHI structure made it impossible to attain self-powered operation. The primary focus of these works was to develop a pixel structure with good energy harvesting capability. As a result, none of them addressed low-power electronics and power management circuit design issues for energy autonomous image sensors.

In this paper, the first energy harvesting type CIS design with integrated power management system (PMS) is introduced. The PMS running a low-power maximum power point tracking (MPPT) algorithm was integrated with a dual-mode CIS that contains new, highly efficient EHI pixels and ultra-low power readout electronics. The PMS controls the operating point of energy harvesting photodiodes during energy harvesting, performs DC-DC conversion and voltage regulation, powers the chip with harvested energy when sufficient energy is stored and switches back to battery power when harvested energy is not sufficient.

This article is organized as follows:

Section 2 introduces the overall architecture of the proposed EHI imager with PMS.

Section 3 explains the design details of the new EHI pixel structure as well as other ultra-low power functional imaging and energy harvesting blocks.

Section 4 presents the details of the PMS integrated in the design. Simulated and measured performance characteristics of the EHI CIS are presented in

Section 5, while the discussion and conclusions are given in

Section 6.

2. Architecture Overview

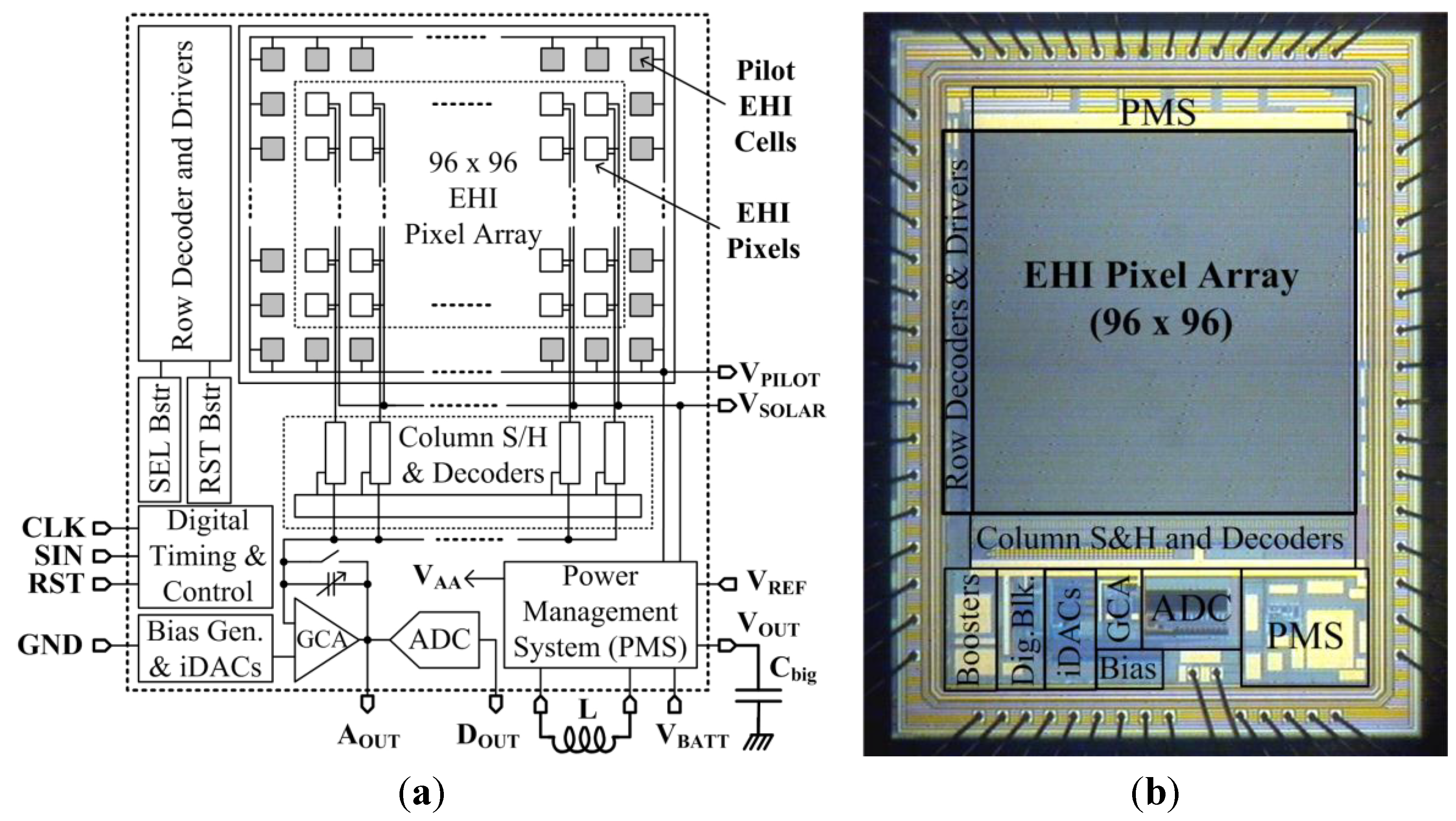

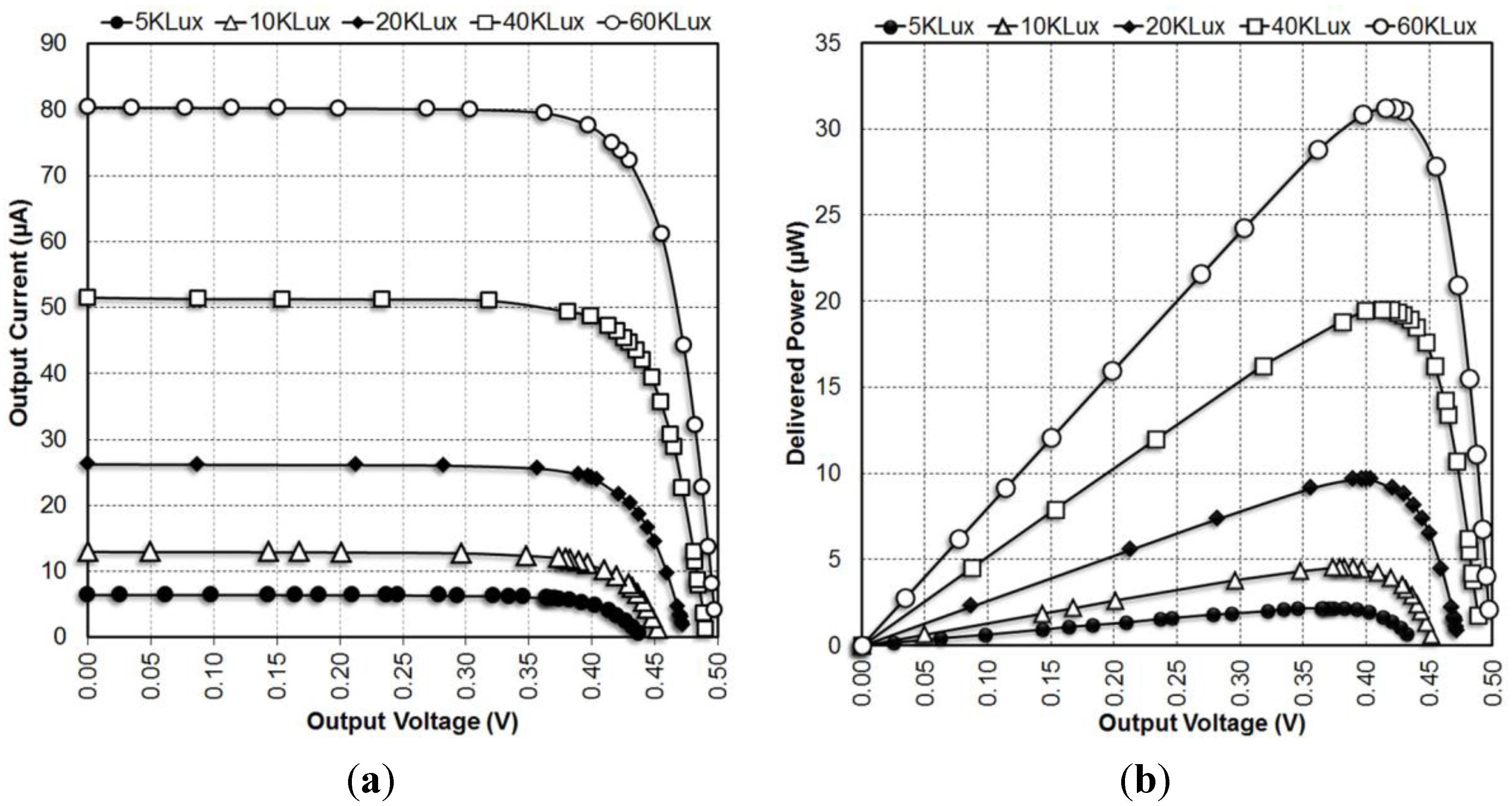

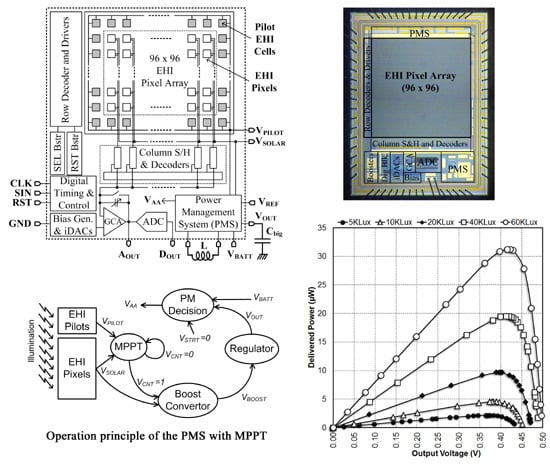

A block diagram and die micrograph of the new ultra-low power EHI type CIS with 96 × 96 pixel array is shown in

Figure 1. The new EHI pixel structure achieves improved energy harvesting efficiency and wider spectral response. The design works in two modes sequentially: (1) imaging mode; and (2) energy harvesting mode.

Figure 1.

Block diagram and die micrographs of the ultra-low power EHI type CIS.

Figure 1.

Block diagram and die micrographs of the ultra-low power EHI type CIS.

In

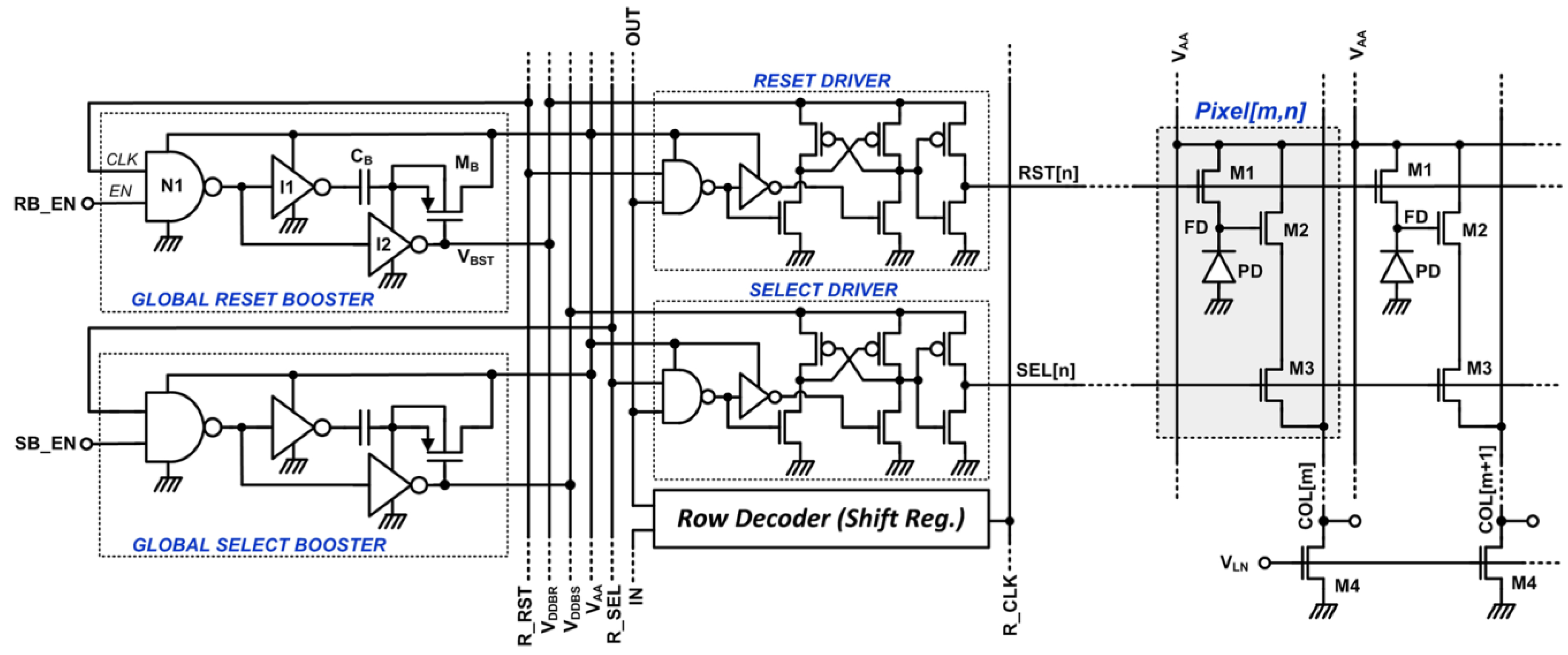

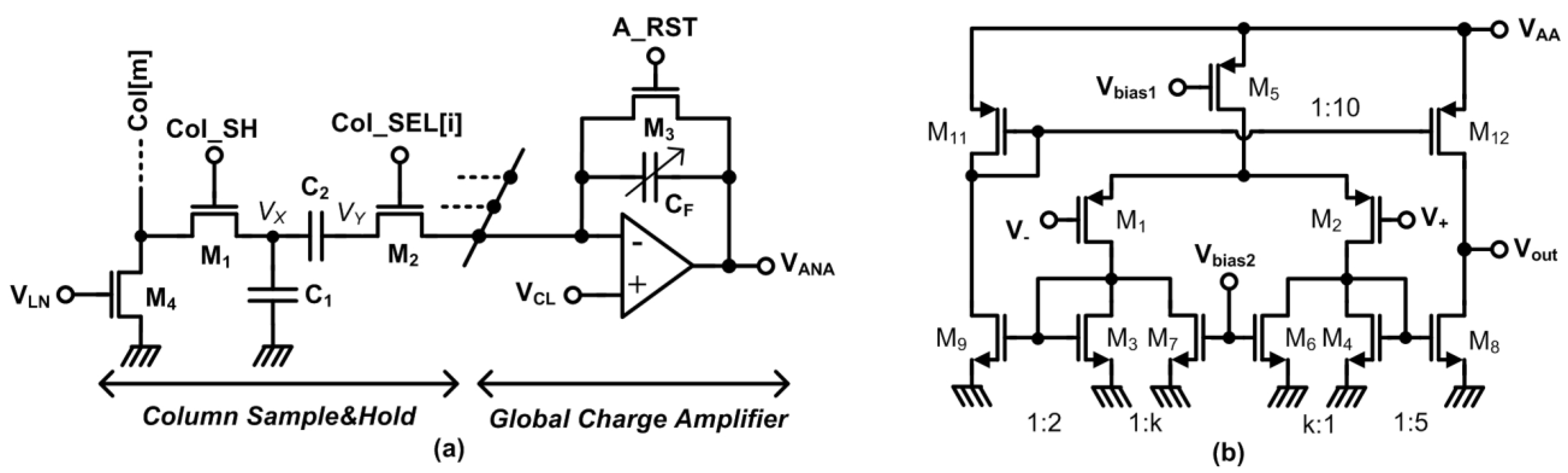

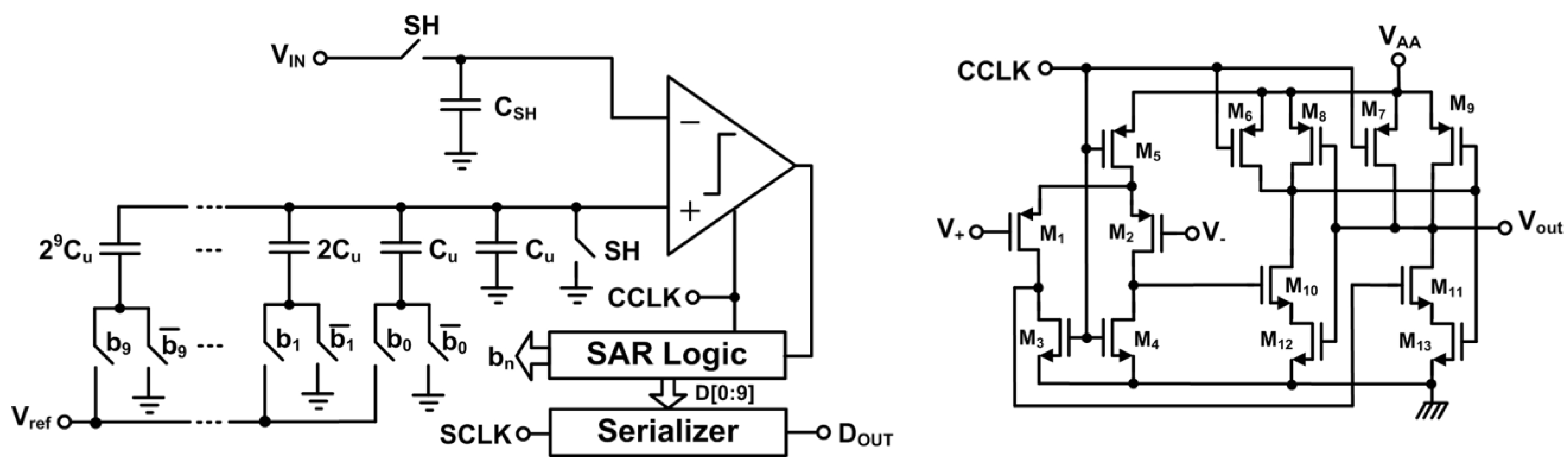

imaging mode (IM), the pixel photodiodes work as image capturing devices and convert the light incident on them into voltage. A column series readout architecture with a global charge amplifier and an analog-to-digital converter (ADC) is integrated with a pixel array similar to the EHI imager described in [

1]. The pixel array is read out sequentially, like a regular CMOS APS imager with rolling shutter. The pixel output from each row is first sampled by column sample and hold (S & H) circuits. The absolute pixel signal after correlated-double-sampling (CDS) is amplified by a global charge amplifier and converted into digital by a 10-bit successive approximation register (SAR) type ADC. During

energy harvesting mode (EHM), pixel photodiodes are configured as solar cells to harvest the solar energy. It is important to harvest the maximum available power from solar cells in this mode. The maximum power point (MPP) of a solar cell changes with illumination level and ambient temperature. Therefore, a maximum power point tracking (MPPT) circuit is integrated in the power management system (PMS) in order to collect energy more efficiently. The PMS monitors the illumination conditions using integrated pilot solar cells, tracks the maximum power point (MPP), and stores the harvested solar energy onto a storage capacitor. Since the solar energy harvester output voltage is less than 0.5 V, an on-chip self-timing boost converter with line regulator is integrated in the PMS to generate the desired supply voltage. The PMS connects the image sensor supply bus to the storage capacitor that holds the harvested energy when sufficient energy is stored. Once the storage capacitor is discharged to a certain level, PMS connects the imager supply back to battery. During EHM all blocks related to imaging are turned off to save power.

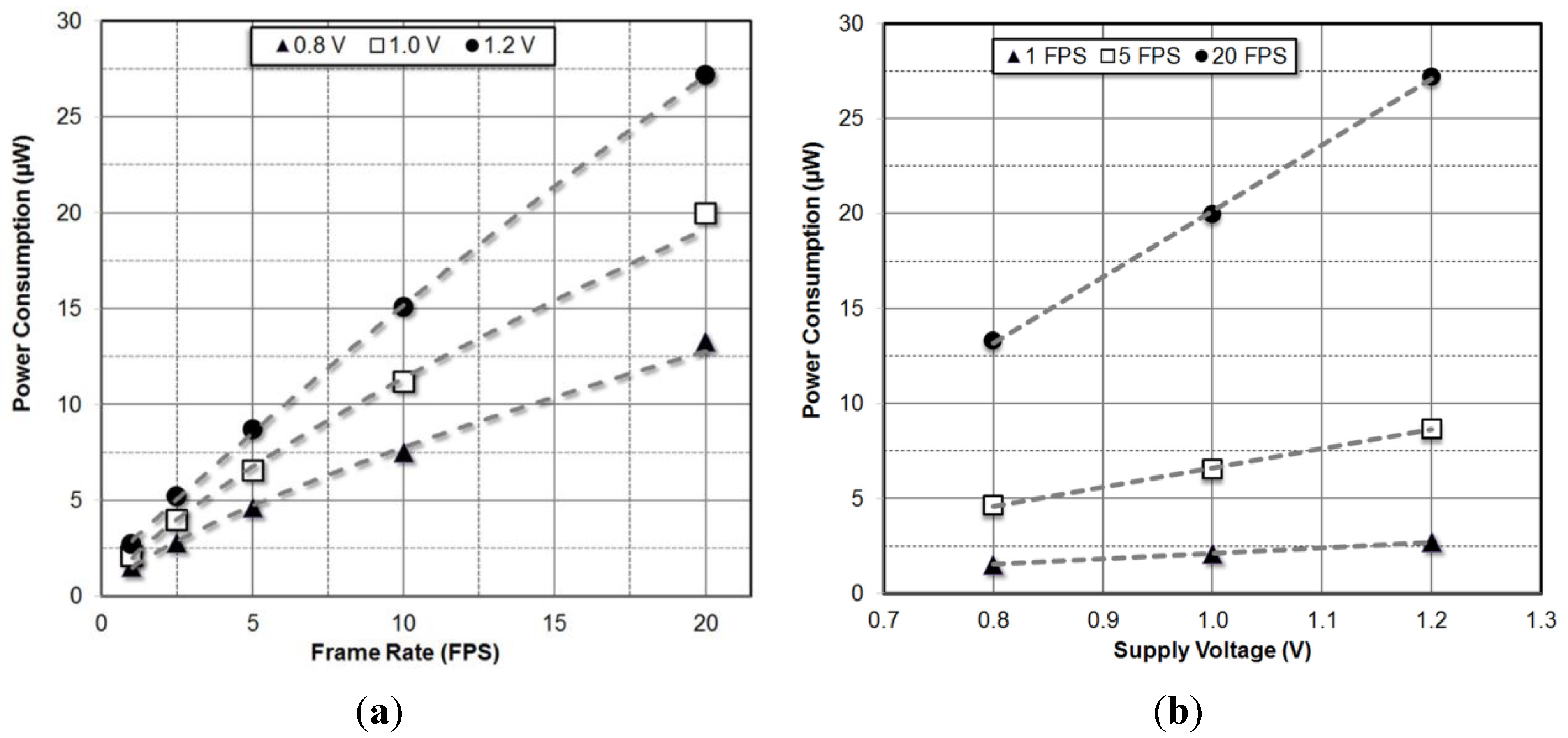

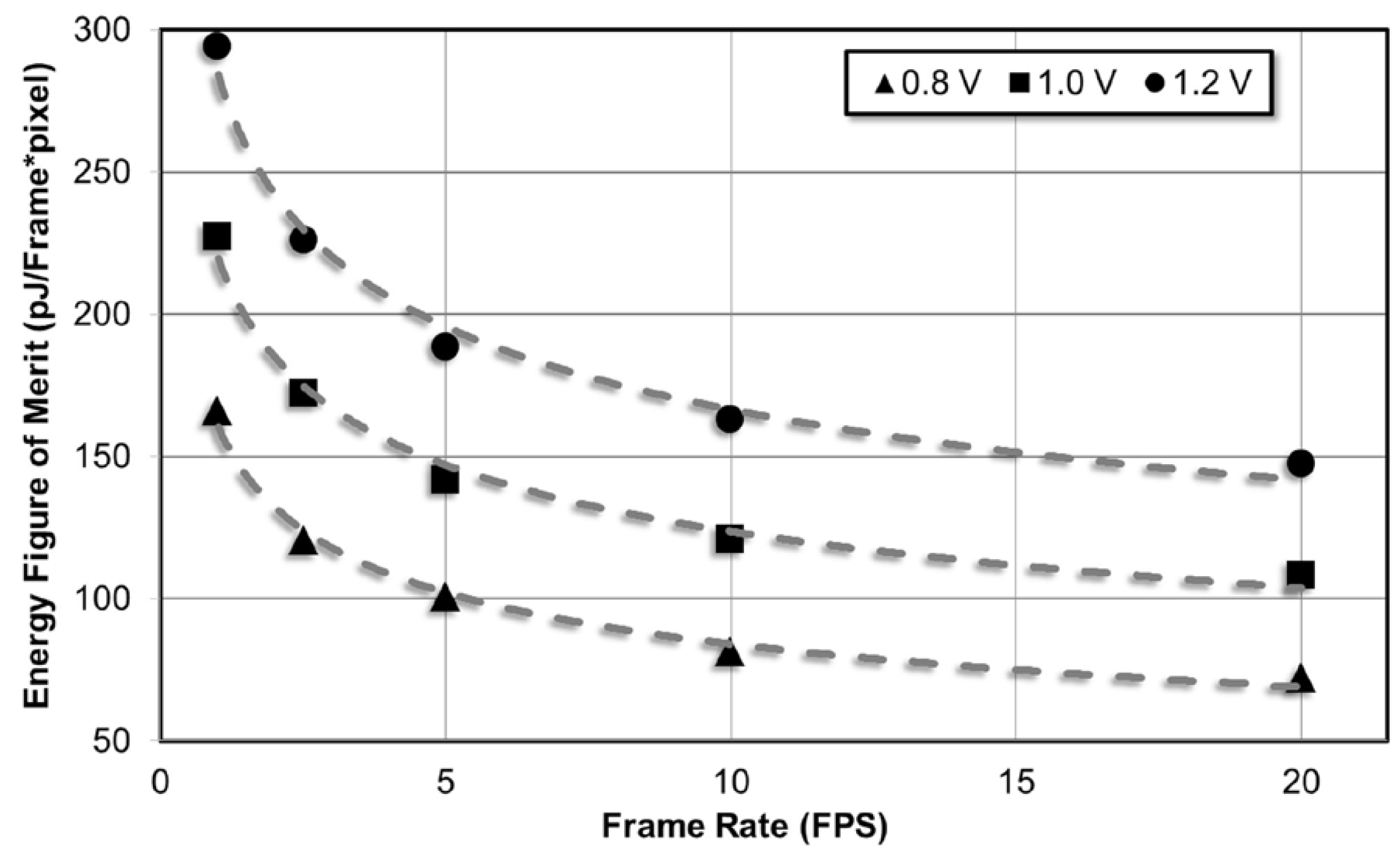

Power consumption of the imager is scaled down by using additional low-power circuit design techniques. Supply voltage reduction is an effective tool for reducing the power consumption of both digital and analog circuits. Power consumption in digital circuit blocks is proportional to the square of the supply voltage while in analog blocks it is typically proportional to the supply voltage. Thus, when the supply voltage is reduced from 1.2 V to 1.0 V, the power consumed by digital and analog blocks are reduced approximately 30% and 17%, respectively. Smart use of low-power design techniques for power-hungry blocks such as a global charge amplifier and on-chip ADC without sacrificing performance further reduced the power consumption. Power scheduling in active analog and digital blocks were also adopted. Typically the minimum supply voltage requirement of the pixel electronics is higher than that of other blocks to achieve a good pixel dynamic range. The pixel dynamic range diminishes almost to zero for sub-1 V supply voltages. In the proposed image sensor, global voltage boosters are used for critical nodes in the pixel array to increase the dynamic range of the pixel instead of increasing the supply voltage. As a result, the whole sensor can work under 1-V supply without sacrificing the performance metrics. Additionally, an overridable digital timing and control block is integrated on-chip to reduce the power dissipated by the digital IO pads. The chip was fabricated in a standard 1.8 V, 1P6M, 0.18 µm CMOS process. The total power consumption of the proposed EHI CIS is 6.53 µW on 1 V power supply for a 96 × 96 pixel array while operating at 5 fps frame rates.

4. Energy Harvesting Circuits

When a photon is absorbed by a semiconductor material, an electron hole pair is generated. The electron and hole eventually recombine unless they are separated. The built-in electric field in the depletion region of a PN-junction drifts electrons from P-region to N-region and holes from N-region to P-region. Thus, photo-generated electrons from holes are separated. Drift of photo-generated minority carriers across the depletion region results in a photo-generated current flowing from the N-region to the P-region of the semiconductor junction. Since the electric field is zero outside of the depletion region, only the carriers generated in the depletion region and those carriers that can reach the depletion region through diffusion are separated by the electric field. Therefore, more carriers can be separated in materials with wider depletion regions and longer diffusion lengths. The depletion region width is wider if lighter doping concentrations are used for the junctions. Excess carriers recombine through several mechanisms, [

25,

26]. The recombination rate increases with increased doping concentration in all these mechanisms. Carriers diffuse longer distances when the recombination rate is lower. Therefore, diffusion lengths are longer in lightly doped semiconductors. The photo-generated current (I

ph) is given by Equation (4) [

10]:

where A is the junction area, G is the carrier generation rate proportional to illumination, W

D is the depletion layer width, and L

P and L

N are the diffusion lengths of holes and electrons, respectively. Since both depletion region width and diffusion lengths are longer in lightly doped semiconductors, the power generation capacity of lightly doped P and N junctions is higher.

Photo-generated carriers flowing across the depletion layer result in a net positive charge in the P-region and a net negative charge in the N-region and the built-in potential of junction is lowered. This change in built-in potential results in a measurable potential difference between the two sides of the junction. When the built in potential of a PN-junction is reduced either by an applied positive bias voltage or excess carrier build up, diffusion of holes from the P-region to the N-region and of electrons from the N-region to the P-region increases. This forward current (I

f) is the exponential current of the PN-junction independent of light and is only a function of the potential difference between the P and N regions of the photodiode (V

out). I

f and I

ph flow in opposite directions and net current flowing out of the anode of a photodiode (I

out) as a function of photodiode voltage is given by Equation (5) [

10]:

Here n is the diode ideality factor, I

f is the forward current, I

ph is the photo-generated current, V

out is the voltage across the PN-junction, V

T is the thermal voltage, and I

s is the reverse saturation current of the junction. This equation suggests a first order photodiode model composed of an ideal current source and an ideal diode. Models based on measurements suggest additional shunt and series resistances [

27]. However, the deviation from the first order model due to these added parasitic resistances are not significant and relations derived using this first order equation are accurate enough.

When no external circuit is connected between the terminals of a PN-junction photodiode, no net current flows. The forward current due to the potential barrier lowering and photo-generated current are equal. The potential difference between the terminals in this condition is known as open circuit voltage (V

oc) and is given in Equation (6):

The power output for a specific output voltage (V

out) is given by Equation (7). V

out corresponding to maximum power output (V

MPP) can be calculated by setting the derivative of Equation (7) to zero. The relation between V

MPP and other solar cell parameters is given in Equation (8). Substituting Equation (6) into Equation (8) we get the relation between V

MPP and V

oc as in Equation (9):

Even though

Voc and

VMPP does not have a linear relation, the logarithmic curve defined by Equation (9) is quite linear when

Voc changes by a few hundred millivolts. Since both

VMPP and

Voc are logarithmic functions of illumination, large changes in illumination results in small changes in these voltages. Measurements confirm that ratio of

Voc and

VMPP is fairly constant over a wide range of illumination conditions as it is summarized in Equation (10).

This equation is the basis of fractional voltage maximum power point tracking (FVMPPT) method [

28]. MPPT circuits based on FVMPPT method are very simple to implement. The voltage fraction is determined by measurements under various illumination levels. The MPPT circuit measures the open-circuit voltage (V

oc) either by using an identical solar cell (pilot cell) or interrupting the solar cell operation and measuring the actual V

oc. Load of the solar cell is controlled to set the photodiode output voltage equal to the appropriate fraction of open circuit voltage.

Since the predefined

kv value is just an approximation, FVMPPT circuit is not a true MPPT circuit. The solar cell operating point will miss the MPP point slightly for different illumination levels and temperatures and the solar cell output power might be a little less than the maximum available. However, MPPT circuits themselves consume power. The power consumed by MPPT circuits increases with increased tracking circuit complexity. Naturally, it is desirable to minimize MPPT circuit power consumption, so that it doesn’t reduce the overall power efficiency of the energy harvesting system. The FVMPPT-based MPPT circuits consume very little power compared to complicated true MPPT circuits, so these circuits are the most energy efficient [

29].

4.1. Integrated Power Management System (PMS)

When the imager is in standby, the EH signal is set to logic high and all imaging mode circuits are powered down. The in-pixel EH switch (M4 in

Figure 2a) shorts the anode of permanently grounded photodiode PD1 and the cathode of reconfigurable photodiode PD2 to ground. Anodes of all PD2 photodiodes in 9216 pixels are connected to the energy harvesting bus (EHB). In EH mode the EHB is disconnected from ground and connected to the power management system (PMS). The PD2 photodiodes in all pixels are configured as a micro solar cell array.

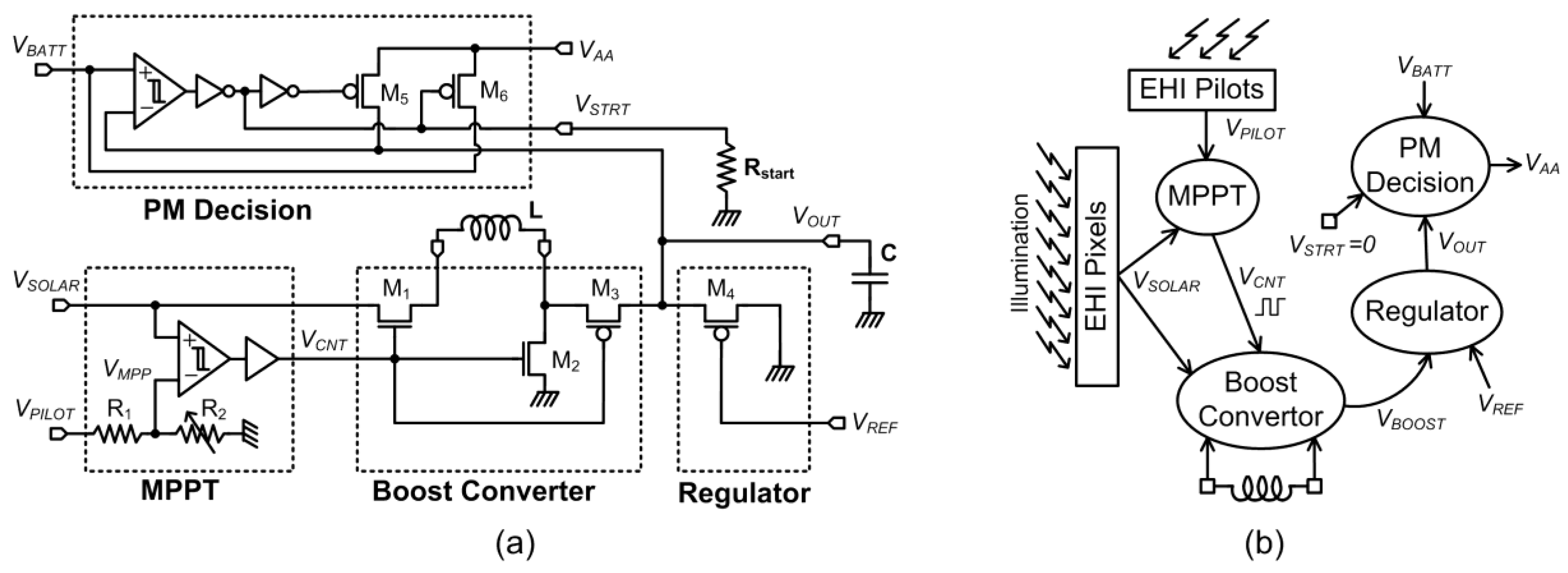

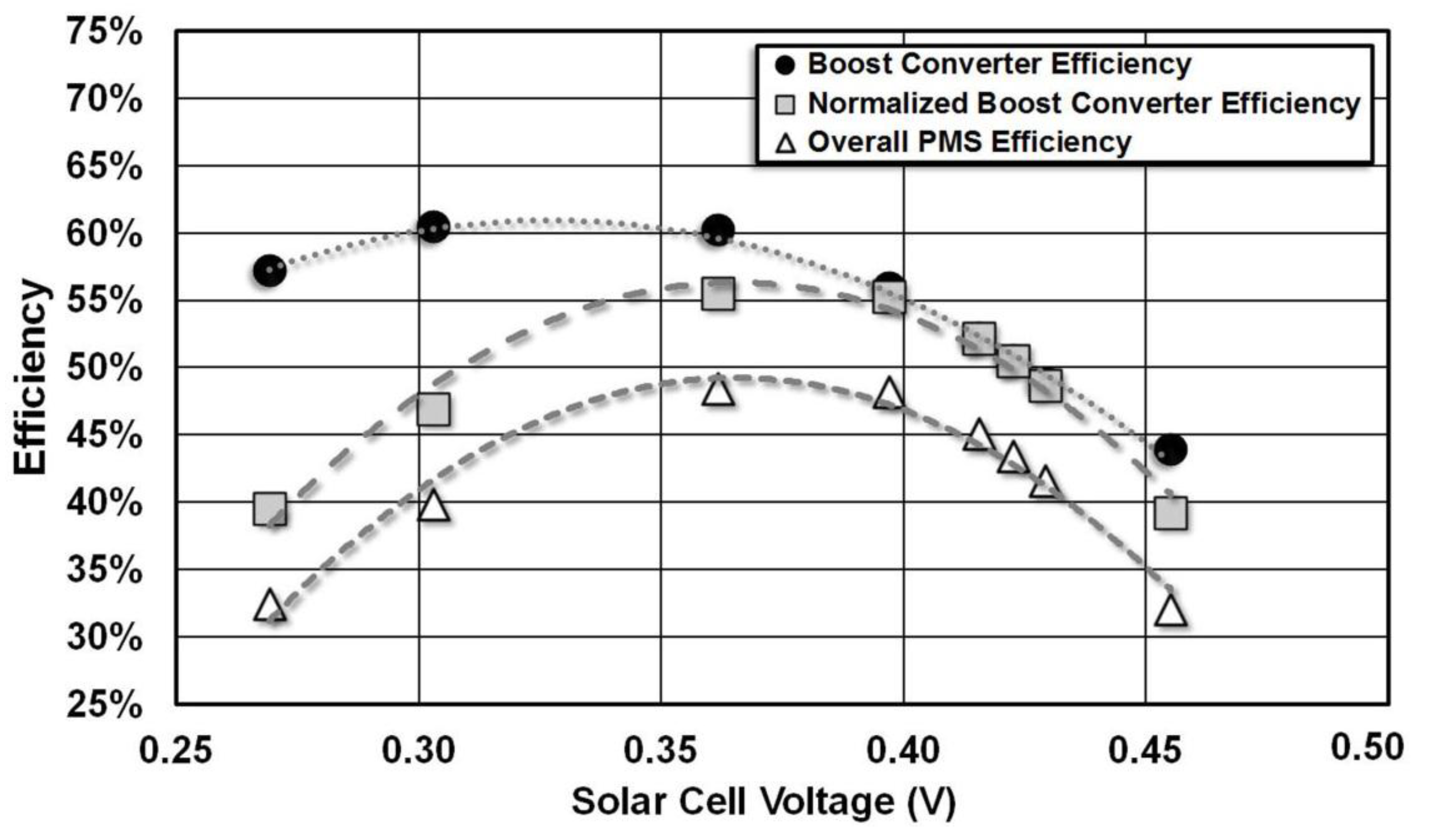

The unique integrated power management system (PMS) consists of a maximum power point tracking circuit (MPPT), a boost converter, a voltage regulator, and a power management decision block. PMS circuit and its operation principles are shown in

Figure 7.

Solar cells in the array are operated at the maximum power point (MPP) by the maximum power point tracking (MPPT) circuit. The output voltage of the solar cell array is boosted by an inductive boost converter. The output of the boost converter is stored in a large off-chip storage capacitor. The storage capacitor voltage is regulated to a level slightly higher than the battery voltage by using an anti-blooming gate. The power management decision block compares the voltage at the storage capacitor VOUT to the battery voltage VBATT. Once Vout reaches a sufficient level, the chip internal supply voltage (VAA) is switched from battery supply to harvested voltage. In other words, the chip uses the battery voltage for VAA until VOUT is charged to a sufficient level. Once VOUT is charged to this level, the chip is supplied by the harvested energy.

Figure 7.

(a) Circuit diagram of the power management system (PMS); (b) operation principle of the PMS.

Figure 7.

(a) Circuit diagram of the power management system (PMS); (b) operation principle of the PMS.

4.2. Maximum Power Point Tracker (MPPT) Circuit

Since the power generated on chip is limited, the MPPT circuit has to be as low power as possible. The on-chip MPPT circuit is implemented using a pilot solar cell, a comparator and a 4-bit programmable resistive voltage divider as shown in

Figure 7. The open circuit output voltage is generated by a distributed pilot cell structure surrounding the EHI pixel array. The pilot cell is constructed using the same CMOS layers used for building the energy harvesting photodiodes so that pilot cell and pixel energy harvesting photodiodes have the same open circuit voltage. The resistive voltage divider output is the reference voltage (V

MPP) and

kv is ideally equal to resistive division ratio

kR given in Equation (11):

Measurements have shown that integrated micro solar cells built in different CMOS processes have a voltage fraction

kv in the range between 0.80 and 0.85. The

kR ratio is controlled by the programmable bottom resistor R

2 to set

kv to the correct value. Ideally, pilot cells should not be loaded so that pilot cell output voltage (V

PILOT) is equal to the open circuit voltage. The resistive voltage divider is implemented with a very large on-chip resistor string so that the current drawn from the pilot cell is much smaller than the short circuit current of the pilot cells. Deviation of

VPILOT from

Voc is insignificant for small output currents due the logarithmic dependence of photodiode voltage on the output current. Since the resistive chain is programmable,

kR can be adjusted to include the deviation of

VPILOT from

Voc. The required value for resistive division ratio is given in Equation (12):

The MPPT block comparator continuously monitors whether VSOLAR is larger than VMPP and generates a control/clock output (VCNT) used by the boost converter. The comparator functions as an asynchronous control signal generator for the boost converter. Since the boost converter is the load for the solar cell array, the comparator controls the amount of current sourced from the solar cell array by switching the boost converter. Therefore, it keeps solar cells operating at maximum power point thus optimizing harvesting efficiency.

4.3. Boost Converter

When M1 and M2 in the boost converter block are turned on, the solar cell current flows through the off-chip inductor to ground. The output voltage of solar cell (VSOLAR) drops as the current drawn from the solar cell increases. If VSOLAR becomes 0 V, the current reaches the maximum available current (short circuit current). MPPT circuit tries to keep the current at the optimum level by sensing the VSOLAR voltage. When VSOLAR drops one hysteresis voltage below the VMPP, the MPPT comparator turns the NMOS switches (M1, M2) off and turns the PMOS switch (M3) on. At this moment, the inductor is floating with one terminal connected to the storage capacitor. Since the inductor current cannot change instantly, the floating inductor will go on supplying a decaying current. Thus, the solar energy stored in the EMF of the inductor is transferred to a large external storage capacitor. Meanwhile, the VSOLAR voltage rises. When it raises one hysteresis voltage above VMPP, the output of the MPPT comparator is toggled starting a new cycle. This operation continues indefinitely charging the VOUT node voltage higher at each cycle with maximum efficiency. The switches in the boost converter are driven by the MPPT circuit. This integrated topology requires no clocks to drive the switches, so the circuit ends up being very simple compared to other switched capacitor charge pump designs. The MPPT algorithm is implemented with no extra power consumption.

4.4. Regulator

In order to regulate the harvested voltage output at VOUT node with low-power consumption, a charge skimming regulation technique was utilized. As the floating inductor (acting like a current source) pumps charge to the storage capacitor, the voltage across the capacitor increases proportionally and decreases as load removes charge from it. If the current consumed from the capacitor is larger than the current supplied, the capacitor will eventually discharge. However, when the supplied current is larger, voltage will go on increasing indefinitely. The charge skimming gate is a simple switch that turns on when the storage capacitor voltage reaches VREF+|VTHP|. When the charge skimming gate turns ON, it will dump the excess charge to ground. As the excess charge is dumped and the voltage level falls, the charge skimming gate will turn OFF. The output voltage might have a small ripple due to transistor switching, but satisfactory performance is achieved using such a simple regulator.

4.5. PM Decision Block

The job of the power management (PM) decision block is to switch the chip power supply (VAA) between the energy storage node (VOUT) and battery (VBATT) voltages. It compares the VOUT and VBATT with a hysteresis. If VOUT is one hysteresis voltage (VHYST) above the VBATT voltage, then M5 turns on, and M6 turns off allowing self-powered operation. Meanwhile, MPPT and the boost converter continue to transfer charge from the solar cells to the external capacitor keeping VOUT high. If the harvested and transferred energy is more than the energy consumed by the imager, then regulator transistor M4 turns on and skims the excess charge from the VOUT node. Here, the regulator turn on voltage could be adjusted above the VOUT+VHYST so that more charge is stored on the external capacitor beyond the optimum operating voltage.

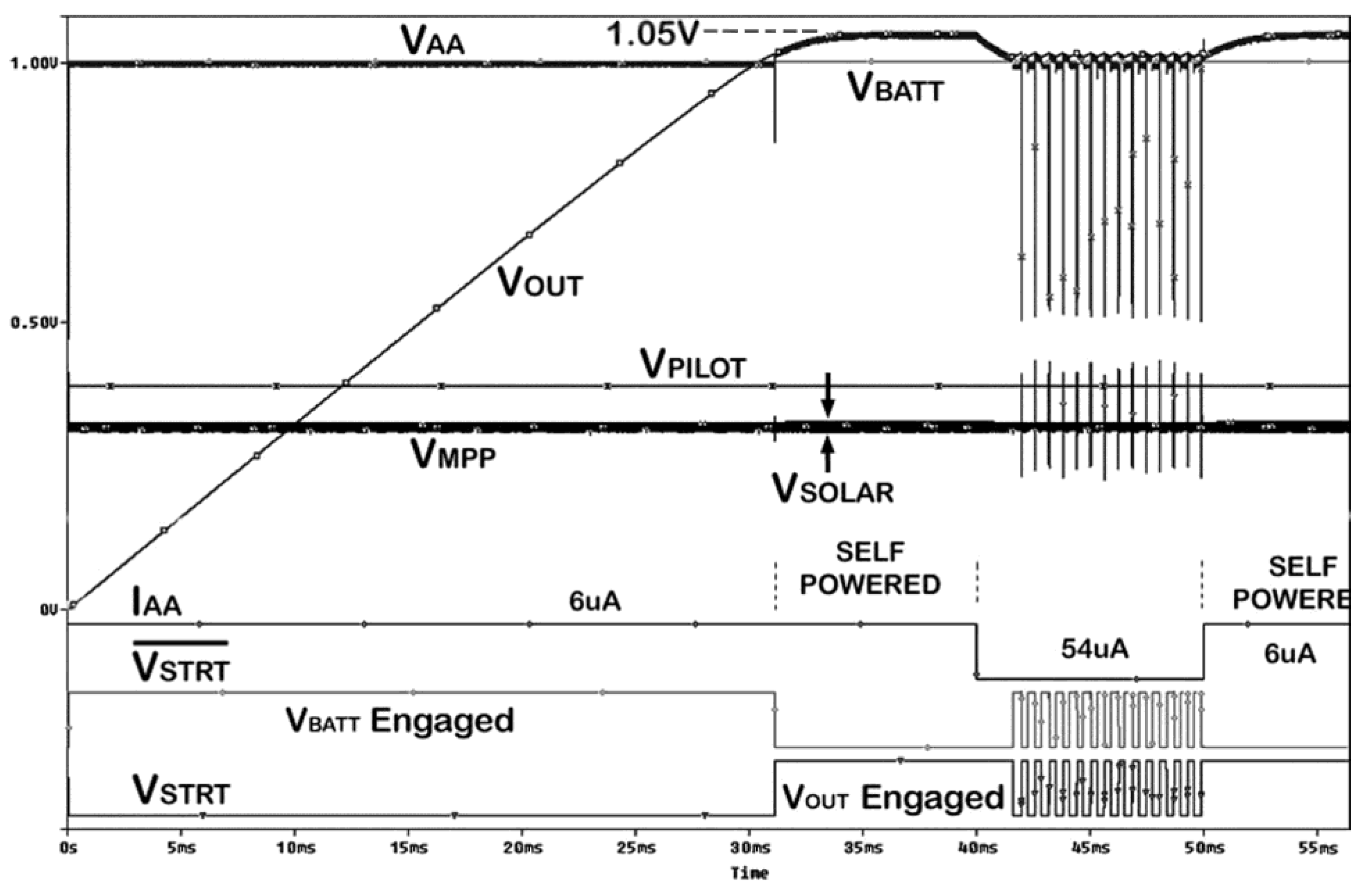

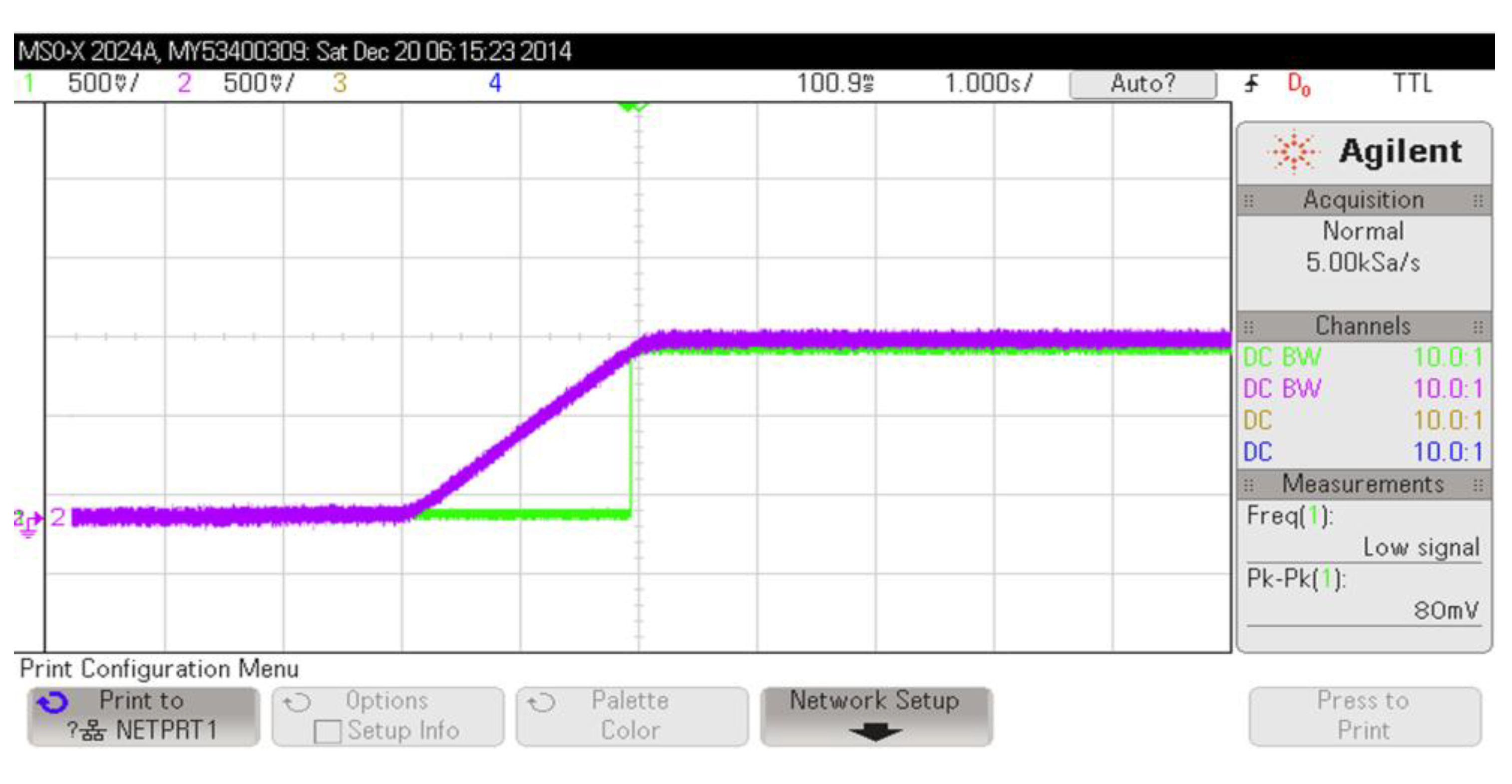

A simulation representing full operation cycles of the PMS is shown in

Figure 8. In this simulation the battery voltage was set to 1 V, while

kR is 0.8,

VSOLAR is 400 mV and the comparators have 50 mV hysterisis. The storage capacitor charges and the system is self powered when the load current is set to 6 μA. Then it is switched to 54 μA to show the adaptive operation of the PMS under larger loading conditions. The PMS repeatedly switches the supply rail between battery and the harvested energy.

Note that the whole chip including the PMS is powered through the internal VAA supply line. Thus, VAA line has to be connected to an auxiliary power source or a battery when the chip is first powered. This is achieved by grounding the gate of M6 through a large off chip resistor (RSTART > 5 MΩ). The inverter driving the gate of M6 is made stronger accommodating this component. In energy autonomous mode of operation, VSTART signal is used as EH signal and imager is switched to energy harvesting mode when VOUT drops below VBATT and once VOUT increases above VBATT, the imager switches back to imaging mode. Full energy autonomy is possible in this mode. When the incoming light increases, more power is harvested and the imager will stay in energy harvesting mode for a shorter time. As harvested power decreases, the imager will need to harvest energy for a longer time to power the imager for the same amount of time.

Figure 8.

Simulation result of the full operating cycles of the PMS.

Figure 8.

Simulation result of the full operating cycles of the PMS.