A Dynamic Range Enhanced Readout Technique with a Two-Step TDC for High Speed Linear CMOS Image Sensors

Abstract

:1. Introduction

2. Dynamic Range Enhanced Readout Circuit

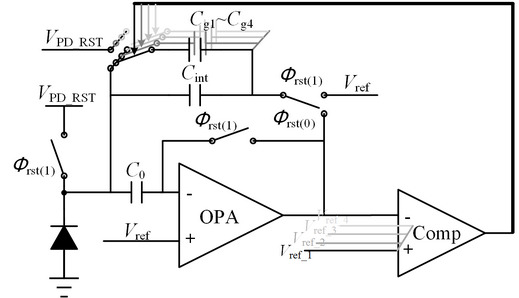

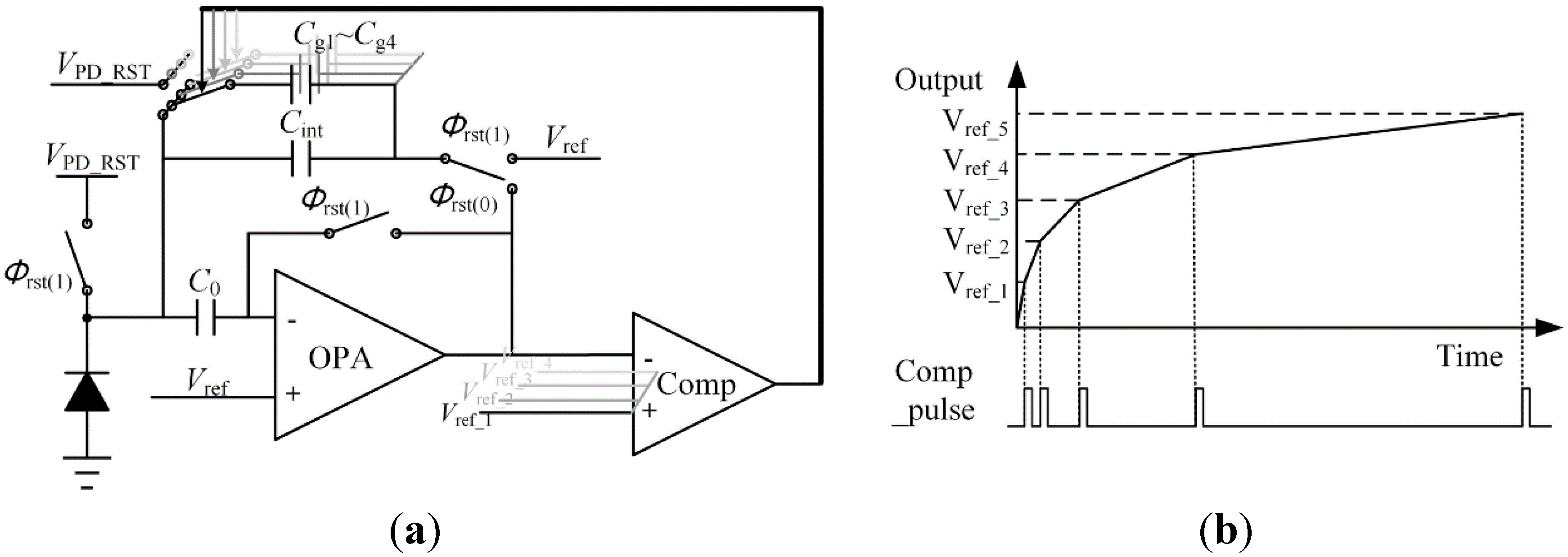

2.1. Capacitor Trans-Impedance Amplifier (CTIA)

2.1.1. Offset Cancellation

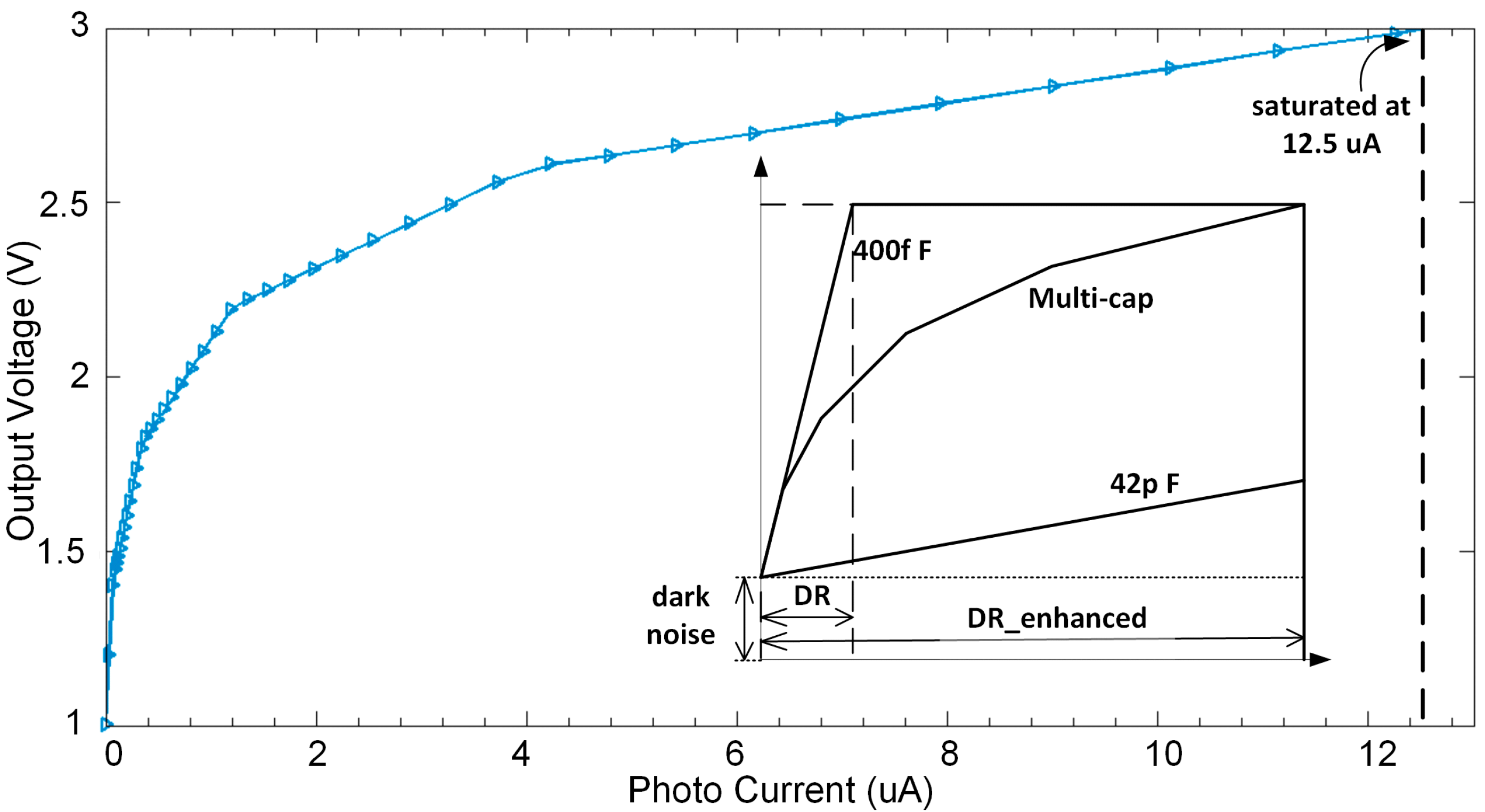

2.1.2. Dynamic Range Extension

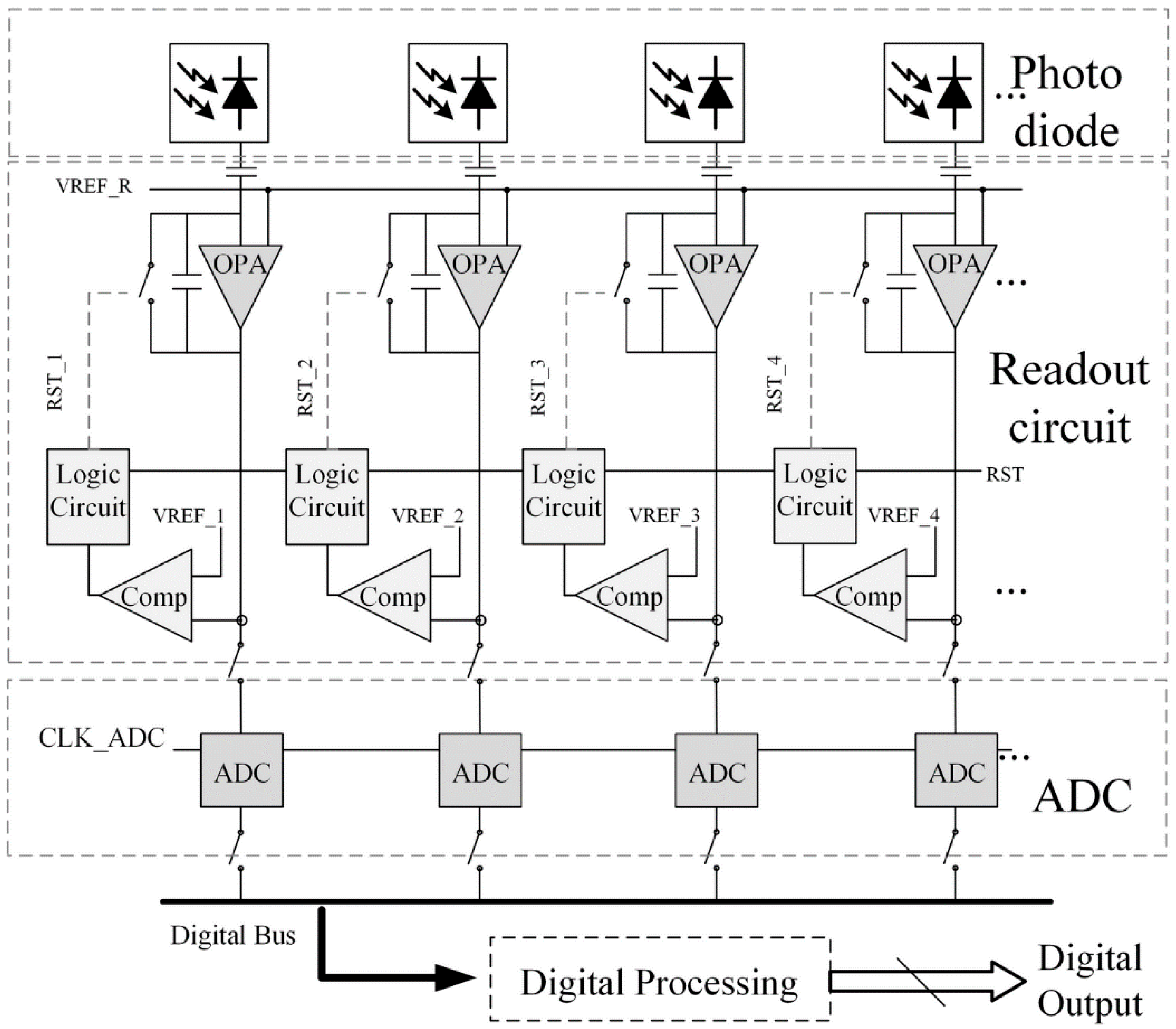

2.2. Readout Circuits Implementation

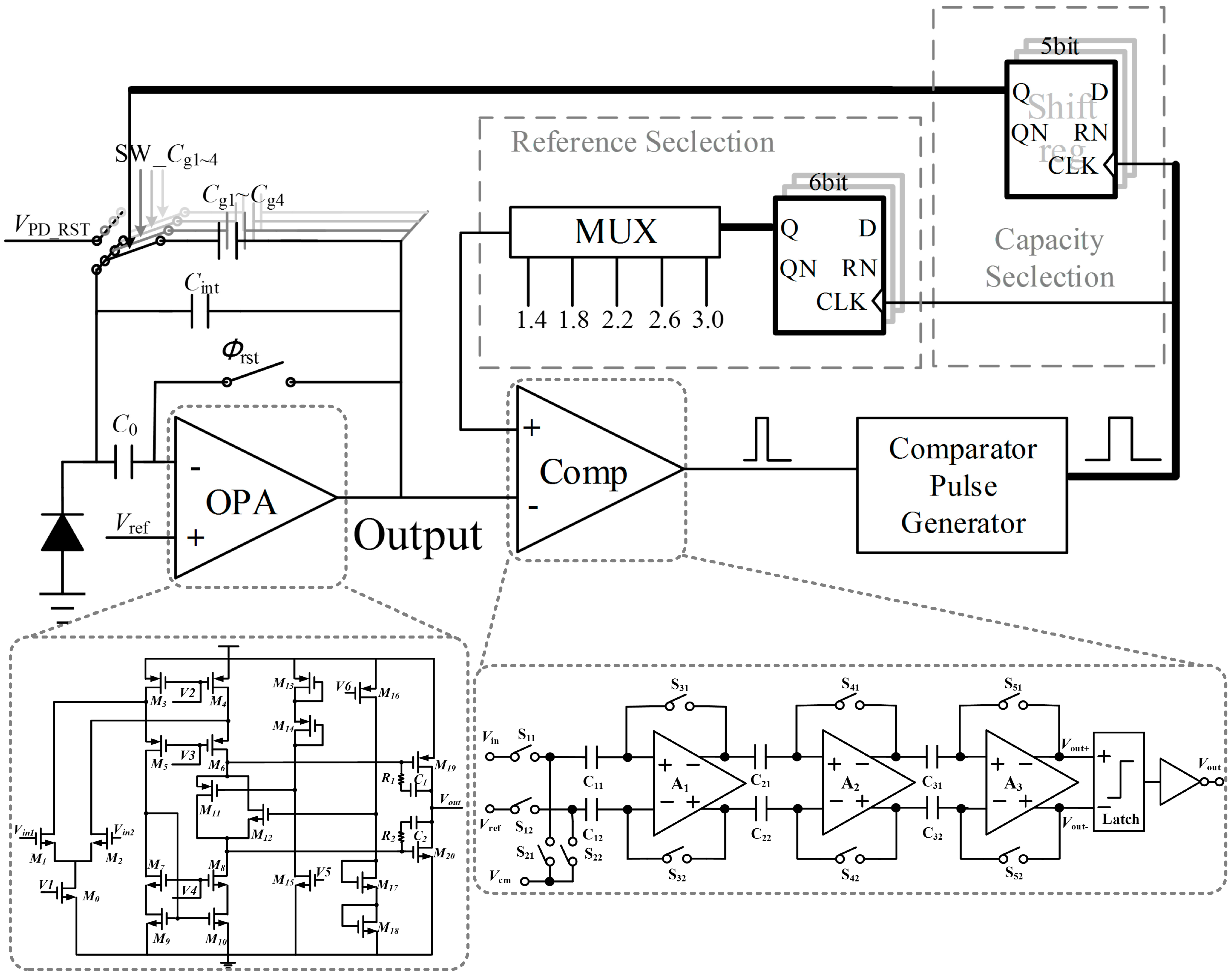

2.2.1. OPA Design

2.2.2. Logic Control and Comparator Design

3. Design of Column-Level ADC with Two-Step TDC

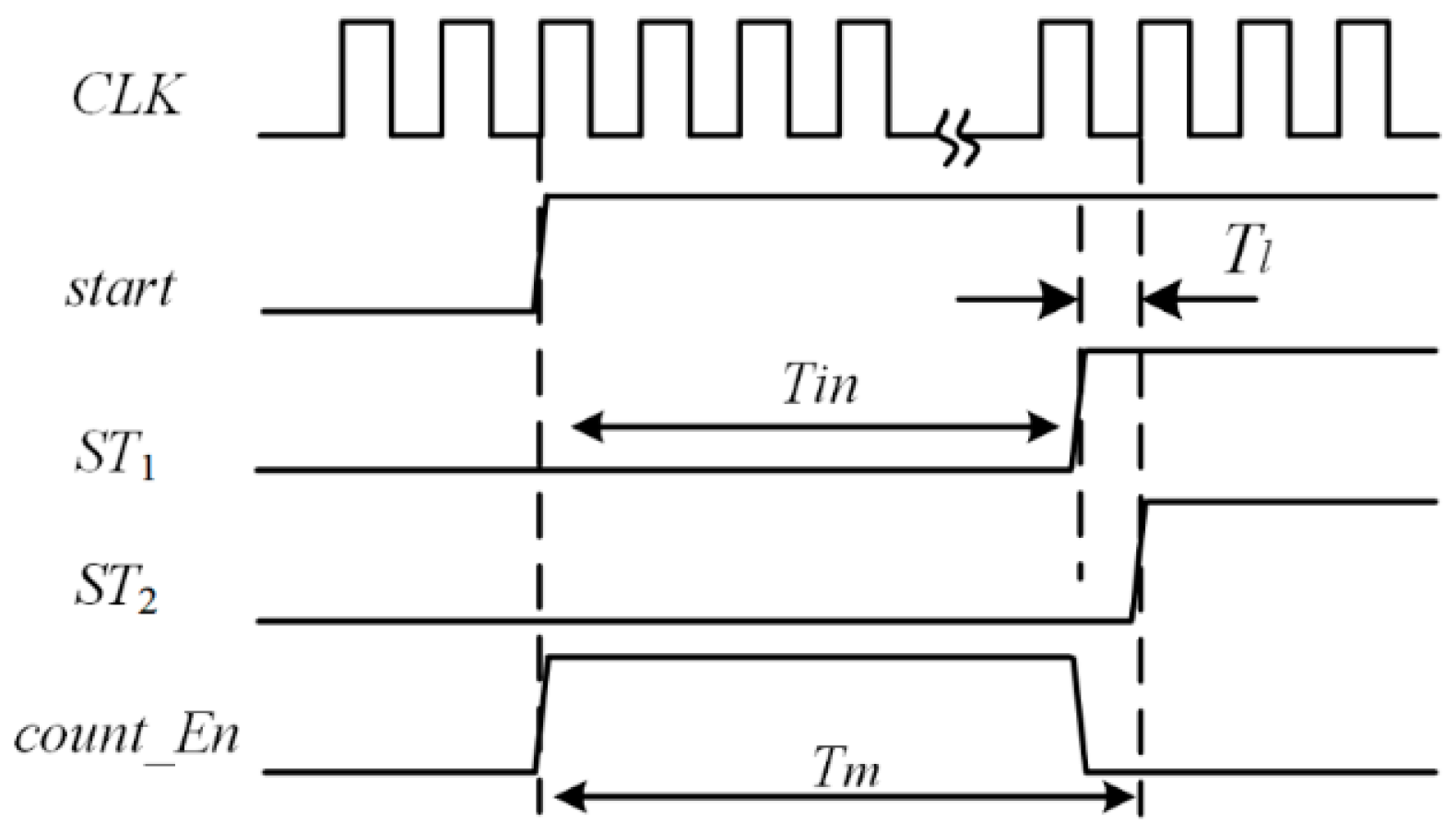

3.1. Operation Principle

3.2. ATC

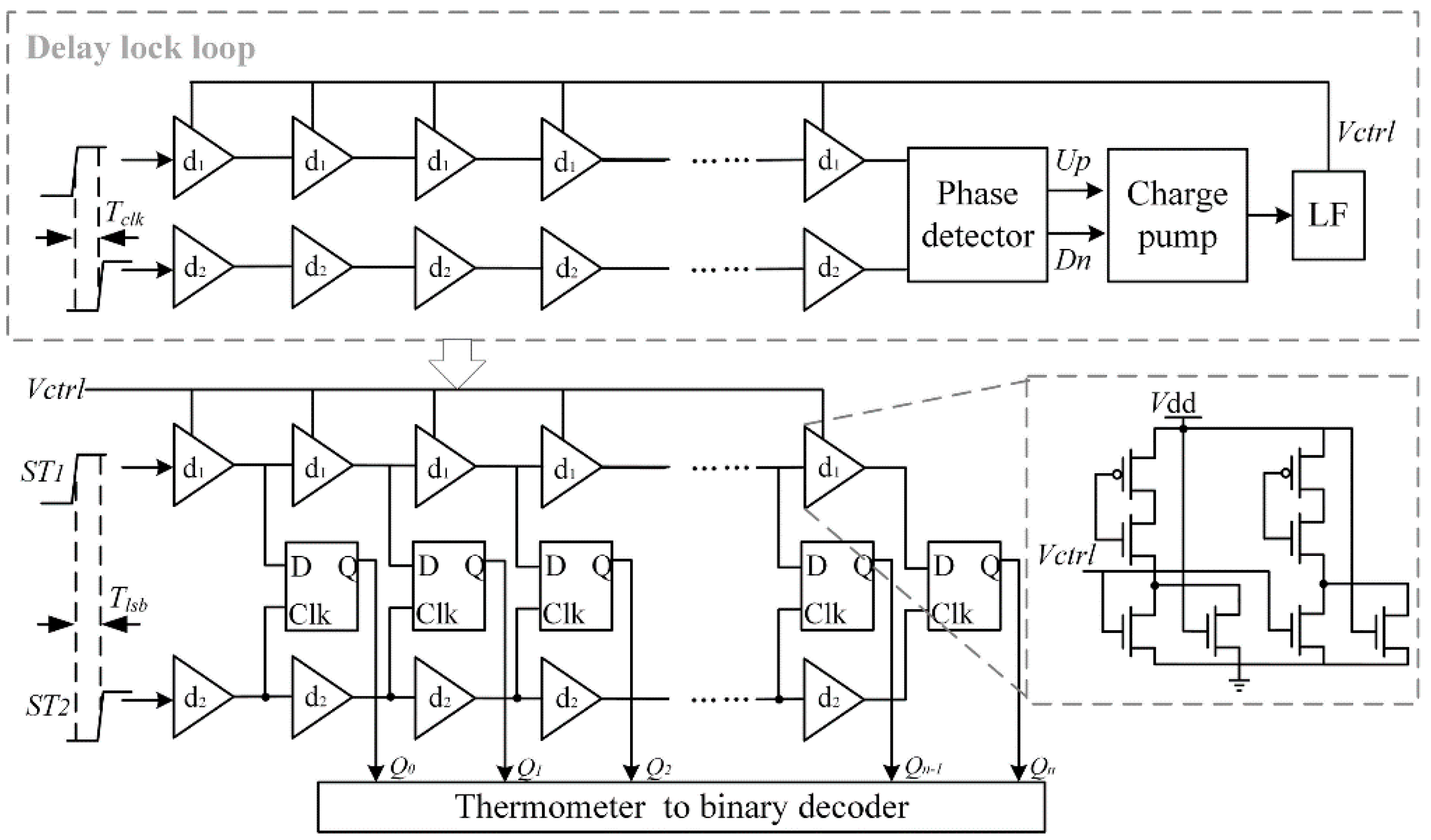

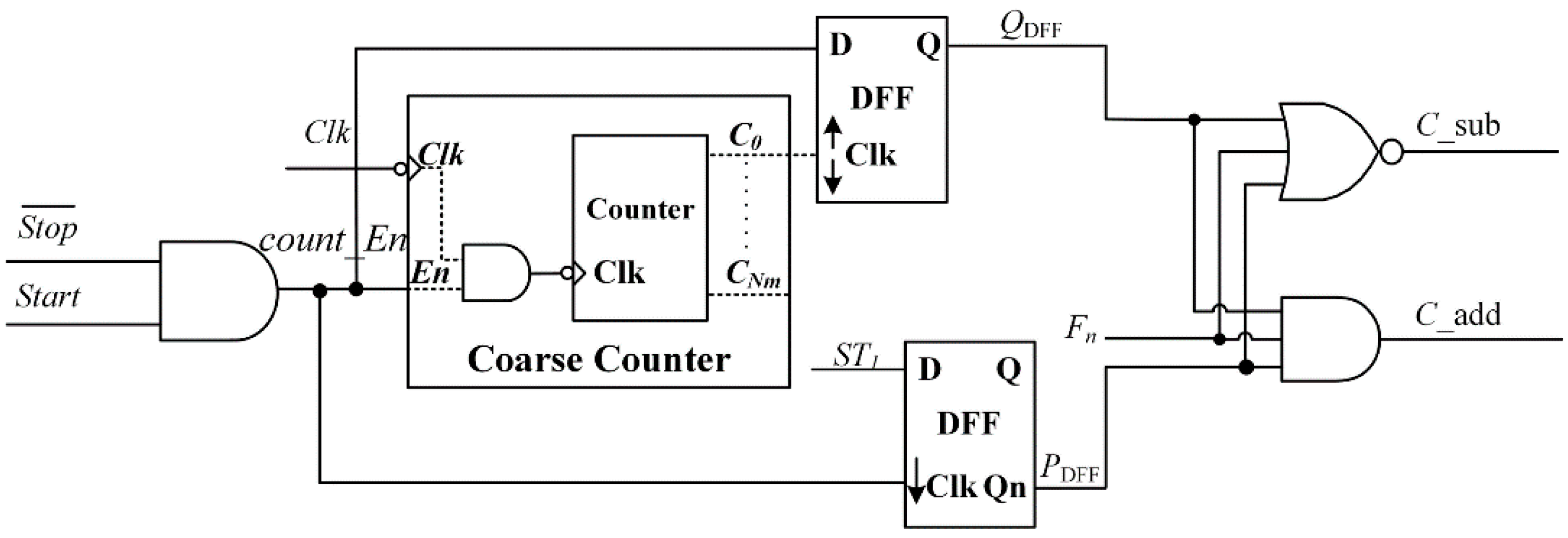

3.3. TDC

3.4. Quantization Error and Calibration

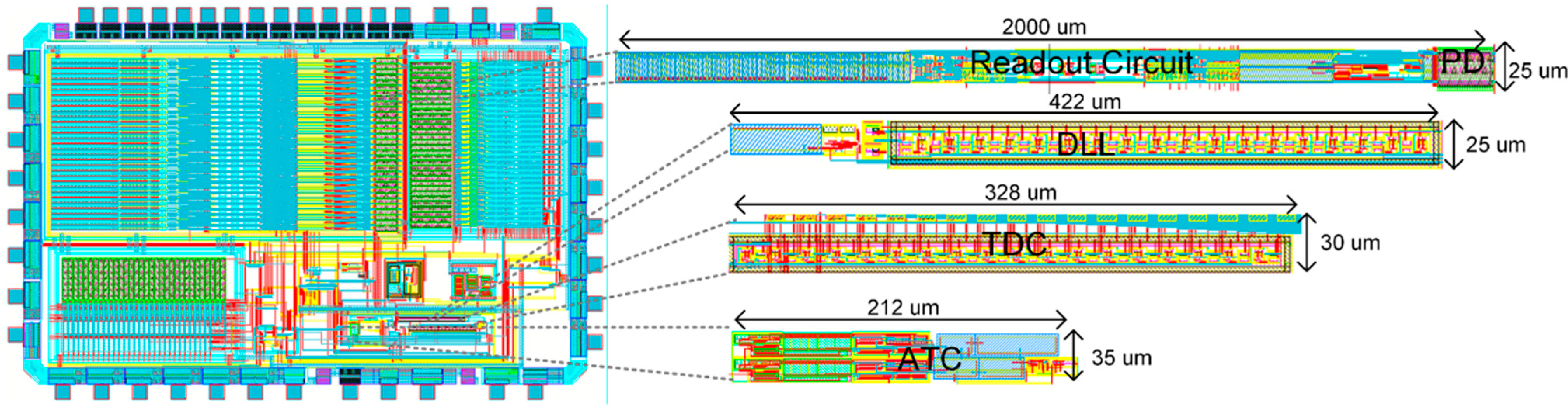

4. Results

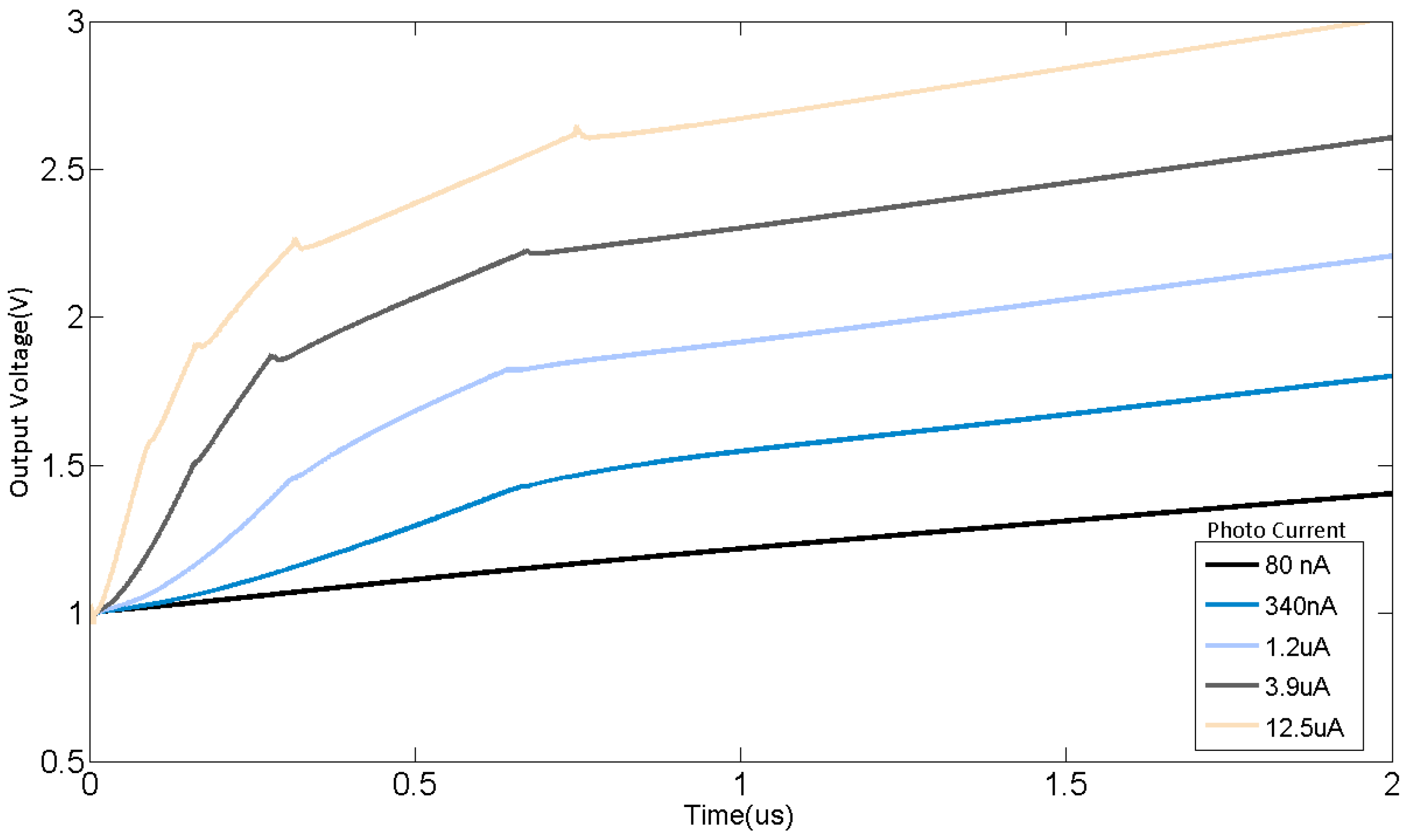

4.1. Readout Circuits

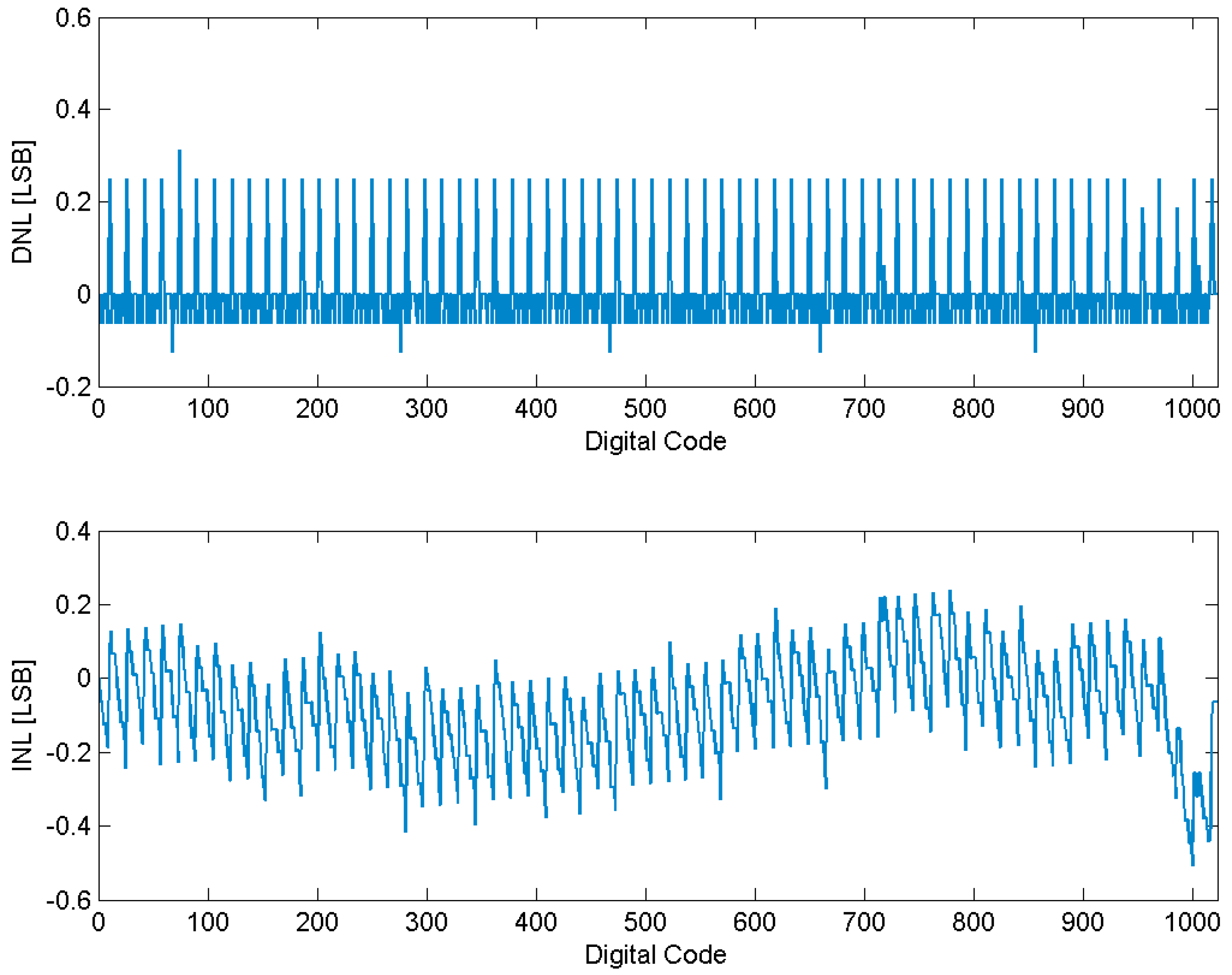

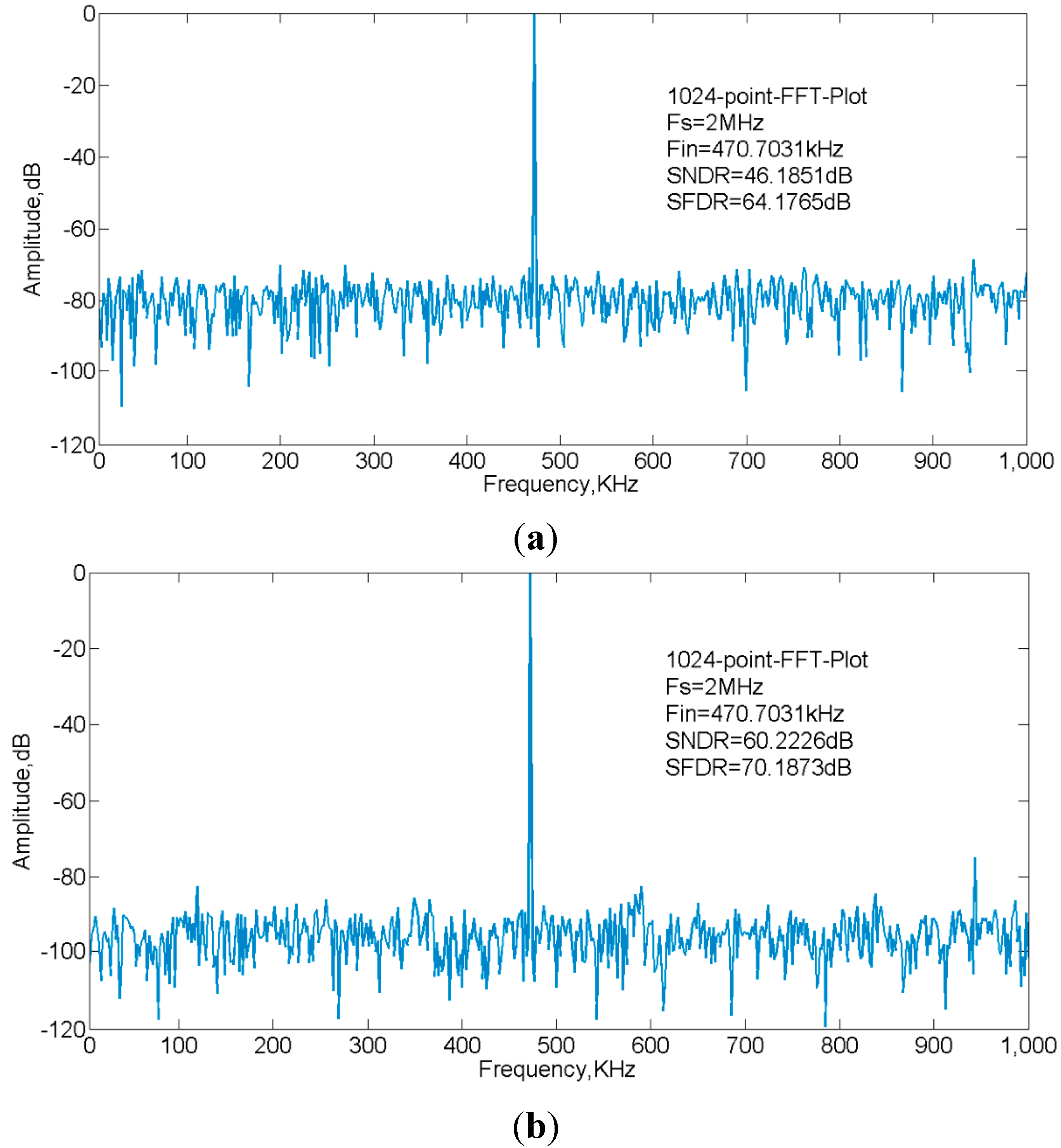

4.2. ADC

| Without Calibration | With Calibration | |

|---|---|---|

| SFDR(@470.7031k), SNDR(@470.7031k) | 64.17 dB 46.18 dB | 70.18 dB 60.22 dB |

| ENOB(@470.7031k) | 7.31 bit | 9.71 bit |

| SFDR(@1.9531k), SNDR(@1.9531k) | 49.87 dB 39.38 dB | 69.59 dB 60.19 dB |

| ENOB(@1.9531k) | 6.25 bit | 9.72 bit |

| DNL(max) | +15.90/−15.36 LSB | +0.31/−0.11 LSB |

| INL(max) | +1.78/−15.76 LSB | +0.25/−0.51 LSB |

| Reference | [10] | [12] | [14] | [15] | [18] | This Work |

|---|---|---|---|---|---|---|

| Technology | 0.18-μm | 0.18-μm | 0.18-μm | 0.35-μm | 0.25-μm | 0.13-μm |

| Architecture | SAR | Cyclic | Single Slope | Two-step SS | Multiple-ramp SS | SS With TDC |

| Resolution/bit | 8 | 13 | 12 | 10 | 10 | 10 |

| Conversion time/μs | 1.2 | 6.4 | 9.5 | 4 | 16 | 0.5 |

| Power/μW | 209 | 450 * | 166.7 * | 150 | 91 | 355 |

| FOM/fJ/step | 983.6 | 442.6 | 385.9 | 585.9 | 1138 | 211 |

| Technology Photodiode Size | 0.13 μm 1P3M 25 μm × 100 μm |

|---|---|

| Supply Voltage | 3.3 V/1.5 V |

| Line Rate | 2 M |

| Sensitivity | 2.5 V/pA·s (max); 0.025 V/pA·s (min) |

| Noise Floor | 0.7 mV |

| Dynamic Range | 99.02 dB |

| ADC resolution | 10 bit |

| ADC ENOB | 9.72 bit (with calibration); 7.31 bit (without calibration) |

| Power Consumption | 1048 μW/column |

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Srikantha, A.; Sidibé, D. Ghost detection and removal for high dynamic range images: Recent advances. Signal Process. Image Commun. 2012, 27, 650–662. [Google Scholar] [CrossRef]

- Spivak, A.; Benlenky, A.; Fish, A.; Yadid, P.O. Wide-Dynamic-Range CMOS Image Sensors—Comparative Performance Analysis. Electron Devices IEEE Trans. 2009, 56, 2446–2461. [Google Scholar] [CrossRef]

- Posch, C.; Matolin, D.; Wohlgenannt, R. A QVGA 143dB dynamic range asynchronous address-event PWM dynamic image sensor with lossless pixel-level video compression. In Proceeding of the 2010 IEEE International Conference on Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 400–401.

- Kavusi, S.; Gamal, A.E. Quantitative study of high-dynamic-range image sensor architectures. Proc. SPIE 2004, 5301, 264–275. [Google Scholar]

- Ruan, A.W.; Shen, K.; Hu, B. Adjustable gain CTIA cell with variable integration time for IRFPA applications. In Proceeding of the International Conference on Communications, Circuits and Systems (ICCCAS), Milpitas, CA, USA, 23–25 July 2009; pp. 1066–1069.

- Hsieh, C.C.; Wu, C.Y.; Sun, T.P.; Jih, F.W.; Cherng, Y.T. High-Performance CMOS Buffered Gate Modulation Input (BGMI) Readout Circuits for IRFPA. IEEE J. Solid-State Circuits 1998, 33, 1188–1198. [Google Scholar] [CrossRef]

- Cao, Y.; Pan, X.F.; Zhao, X.J.; Wu, H.S. An Analog Gamma Correction Scheme for High Dynamic Range CMOS Logarithmic Image Sensors. Sensors 2014, 14, 24132–24145. [Google Scholar] [CrossRef] [PubMed]

- Inkyu, B.; Byeungseok, Y.; Kyounghoon, Y. In-pixel calibration of temperature dependent FPN for a wide dynamic-range dual-capture CMOS image sensor. In Proceeding of the IEEE International Conference on Consumer Electronics (ISCE), JeJu Island, Korea, 22–25 June 2014; pp. 1–3.

- Sasaki, M.; Mase, M.; Kawahito, S.; Tadokoro, Y. A wide-dynamic-range CMOS image sensor based on multiple short exposure-time readout with multiple-resolution column-parallel ADC. IEEE Sens. J. 2007, 7, 151–158. [Google Scholar] [CrossRef]

- Chen, D.G.; Fang, T.; Bermak, A. A Low-Power Pilot-DAC Based Column Parallel 8b SAR ADC with Forward Error Correction for CMOS Image Sensors. IEEE Trans. Circuits Syst. 2013, 60, 2572–2583. [Google Scholar] [CrossRef]

- Shin, M.-S.; Kwon, O.-K. 14-bit two-step successive approximation ADC with calibration circuit for high-resolution CMOS imagers. Electron. Lett. 2011, 47, 790–791. [Google Scholar] [CrossRef]

- Seo, M.-W.; Suh, S.-H.; Iida, T.; Takasawa, T.; Isobe, K.; Watanabe, T.; Itoh, S.; Yasutomi, K.; Kawahito, S. A low-noise high intrascene dynamic range CMOS image sensor with a 13 to 19b variable-resolution column-parallel folding-integration/cyclic ADC. Solid-State Circuits IEEE J. 2012, 47, 272–283. [Google Scholar] [CrossRef]

- Yeh, S.-F.; Hsieh, C.-C.; Cheng, C.-J.; Liu, C.-K. A novel single slope ADC design for wide dynamic range CMOS image sensors. In Proceeding of 2011 IEEE on Sensors, Limerick, Ireland, 28–31 October 2011; pp. 889–892.

- Yoshihara, S.; Nitta, Y.; Kikuchi, M.; Koseki, K.; Ito, Y.; Inada, Y.; Kuramochi, S.; Wakabayashi, H.; Okano, M.; Kuriyama, H.; et al. A 1/ l.8-ineh 6.4M Pixel 60 frames/s CMOS Image Sensor with Seamless Mode Change. IEEE J. Solid-State Circuits 2006, 41, 2998–3006. [Google Scholar] [CrossRef]

- Lim, S.; Lee, J.; Kim, D.; Han, G. A high-speed CMOS image sensor with column-parallel two-step single-slope ADCs. IEEE Trans. Electron Devices 2009, 56, 393–398. [Google Scholar] [CrossRef]

- Bae, J.; Kim, D.; Ham, S.; Chae, Y.; Song, M. A two-step a/d conversion and column self-calibration technique for low noise CMOS image sensors. Sensors 2014, 14, 11825–11843. [Google Scholar] [CrossRef] [PubMed]

- Lyu, T.; Yao, S.Y.; Nie, K.M.; Xu, J.T. A 12-Bit High-Speed Column-Parallel Two-Step Single-Slope ADC for CMOS Image Sensors. Sensors 2014, 14, 21603–21625. [Google Scholar] [CrossRef] [PubMed]

- Snoeij, M.F.; Theuwissen, A.J.P.; Makinwa, K.A.A.; Huijsing, J.H. Multiple-ramp column-parallel ADC architectures for CMOS image sensors. IEEE J. Solid-State Circuits 2007, 42, 2968–2977. [Google Scholar] [CrossRef]

- Muung, S.; Ikebe, M.; Motohisa, J.; Sano, E. Column parallel single-slope ADC with time to digital converter for CMOS imager. In Proceeding of the IEEE International Conference on Electronics, Circuits, and Systems (ICECS) 2010, Athens, Greece, 12–15 December 2010; pp. 863–866.

- Naraghi, S.; Courcy, M.; Flynn, M.P. A 9-bit, 14 μW and 0.06 mm Pulse Position Modulation ADC in 90 nm Digital CMOS. IEEE J. Solid-State Circuits 2010, 45, 1870–1880. [Google Scholar] [CrossRef]

- Murari, K.; Etienne-Cumimings, R.; Thakor, N.V.; Cauwenberghs, G. A CMOS In-Pixel CTIA High Sensitivity Fluorescence Imager. IEEE Trans. Biomed. Circuits Syst. 2011, 5, 449–458. [Google Scholar] [CrossRef] [PubMed]

- Kavusi, S.; Ghosh, K.; Abbas, E.G. Architectures for high Dynamic Range, High Speed Image Sensor Readout Circuits. In Proceeding of the International Conference on Very Large Scale Integration (VLSI), 2006 IFIP, Nice, France, 16–18 October 2006; pp. 36–41.

- Dudek, P.; Szczepanski, S.; Hatfield, J.V. A high-resolution CMOS time-to-digital converter utilizing a Vernier delay line. IEEE J. Solid-State Circuits 2000, 35, 240–247. [Google Scholar] [CrossRef]

© 2015 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gao, Z.; Yang, C.; Xu, J.; Nie, K. A Dynamic Range Enhanced Readout Technique with a Two-Step TDC for High Speed Linear CMOS Image Sensors. Sensors 2015, 15, 28224-28243. https://doi.org/10.3390/s151128224

Gao Z, Yang C, Xu J, Nie K. A Dynamic Range Enhanced Readout Technique with a Two-Step TDC for High Speed Linear CMOS Image Sensors. Sensors. 2015; 15(11):28224-28243. https://doi.org/10.3390/s151128224

Chicago/Turabian StyleGao, Zhiyuan, Congjie Yang, Jiangtao Xu, and Kaiming Nie. 2015. "A Dynamic Range Enhanced Readout Technique with a Two-Step TDC for High Speed Linear CMOS Image Sensors" Sensors 15, no. 11: 28224-28243. https://doi.org/10.3390/s151128224