Single-Walled Carbon-Nanotubes-Based Organic Memory Structures

Abstract

:1. Introduction

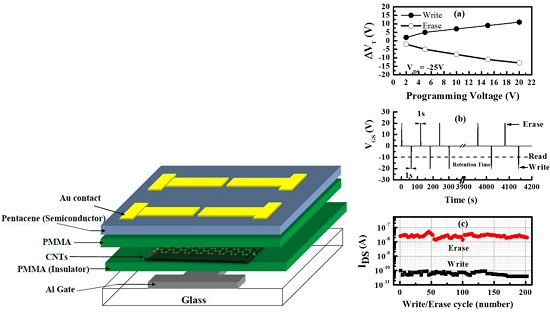

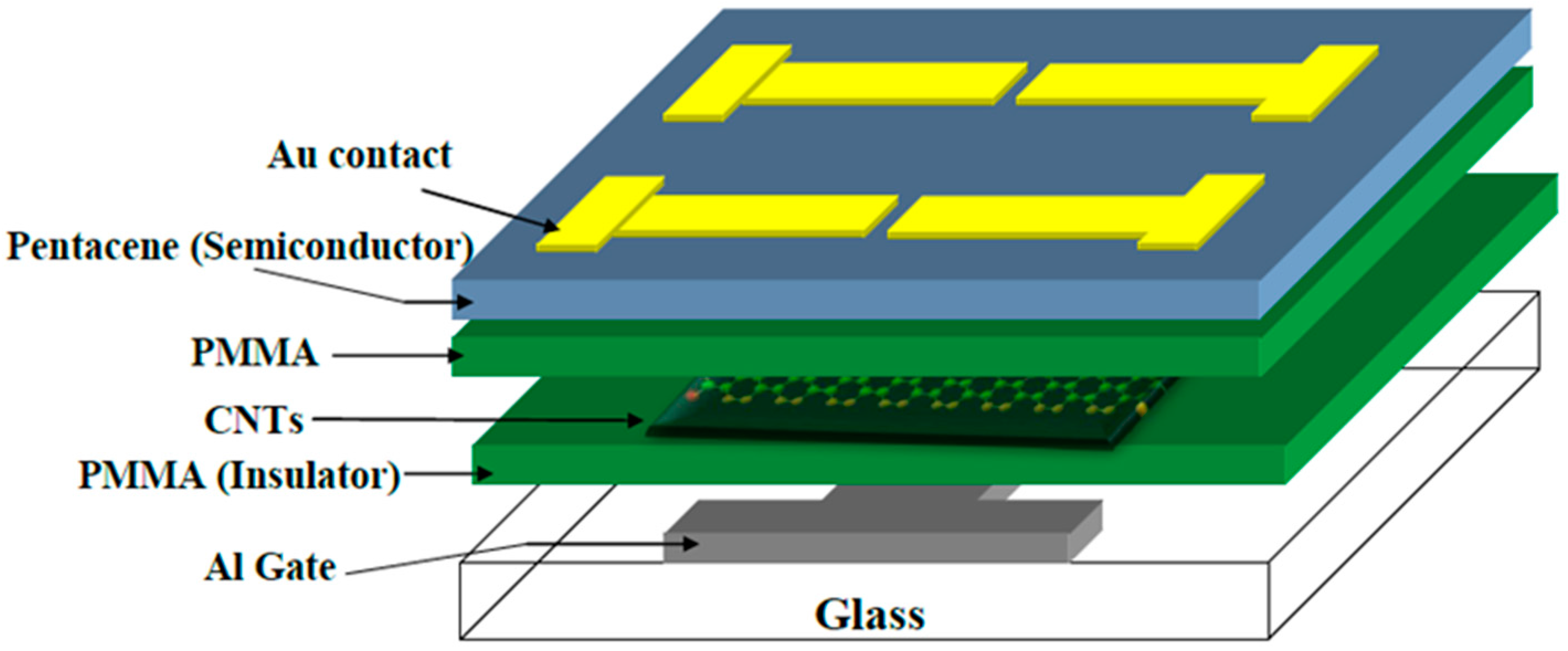

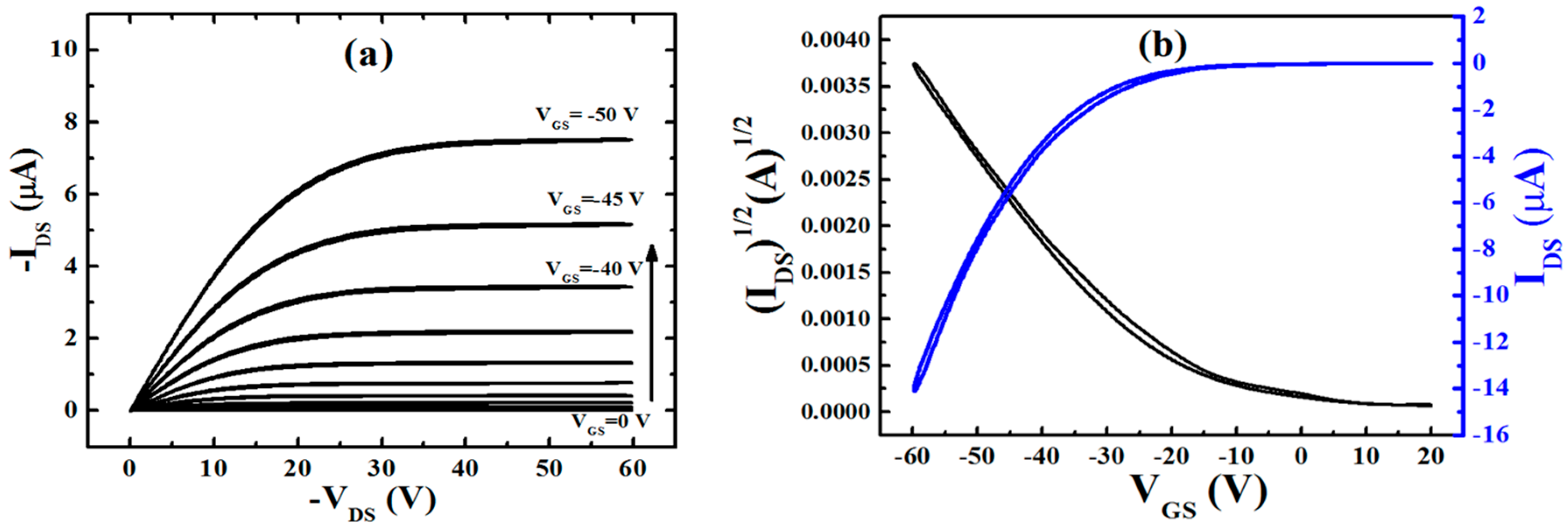

2. Results and Discussion

2.1. C–V Characteristics for MIS Memory Devices

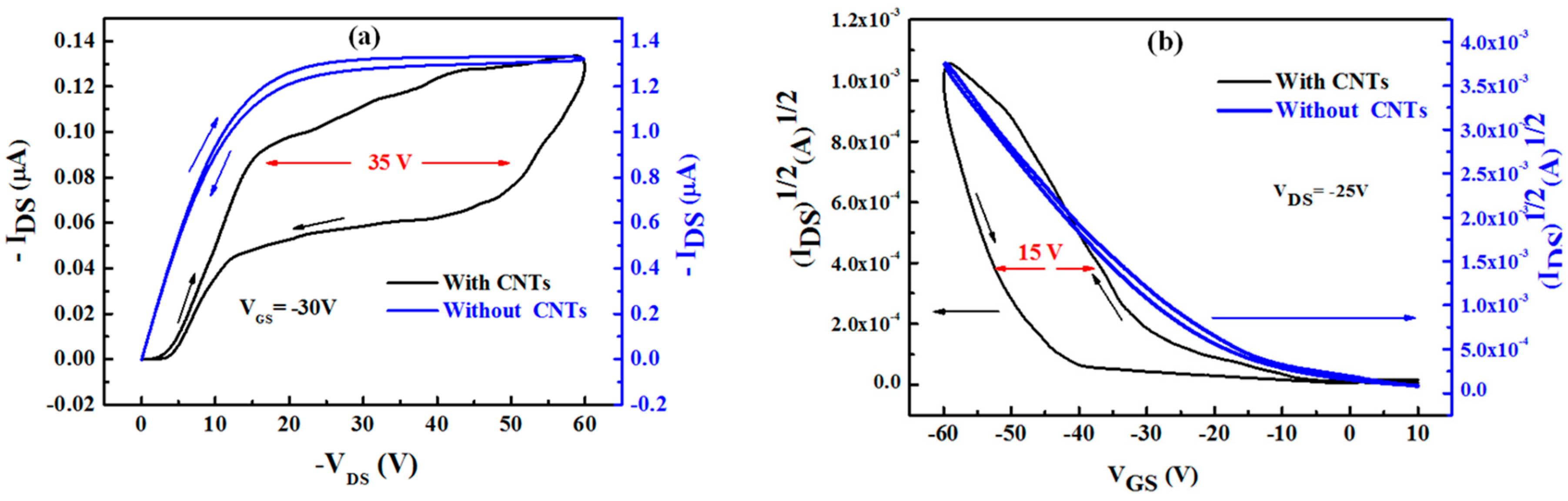

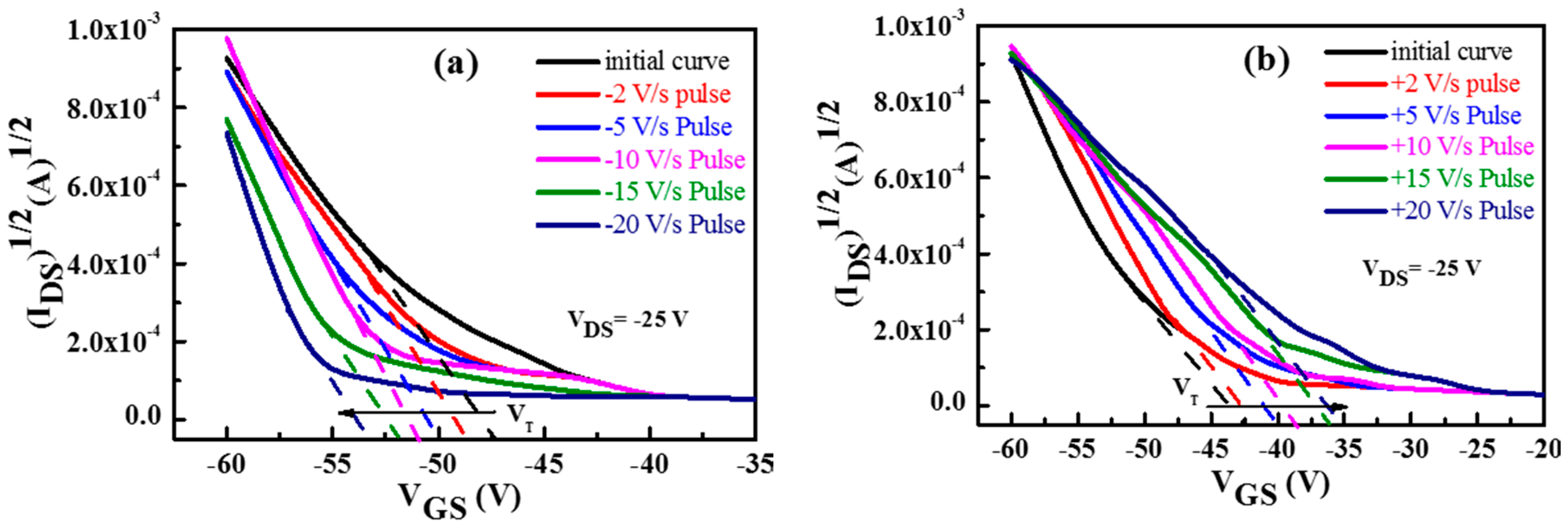

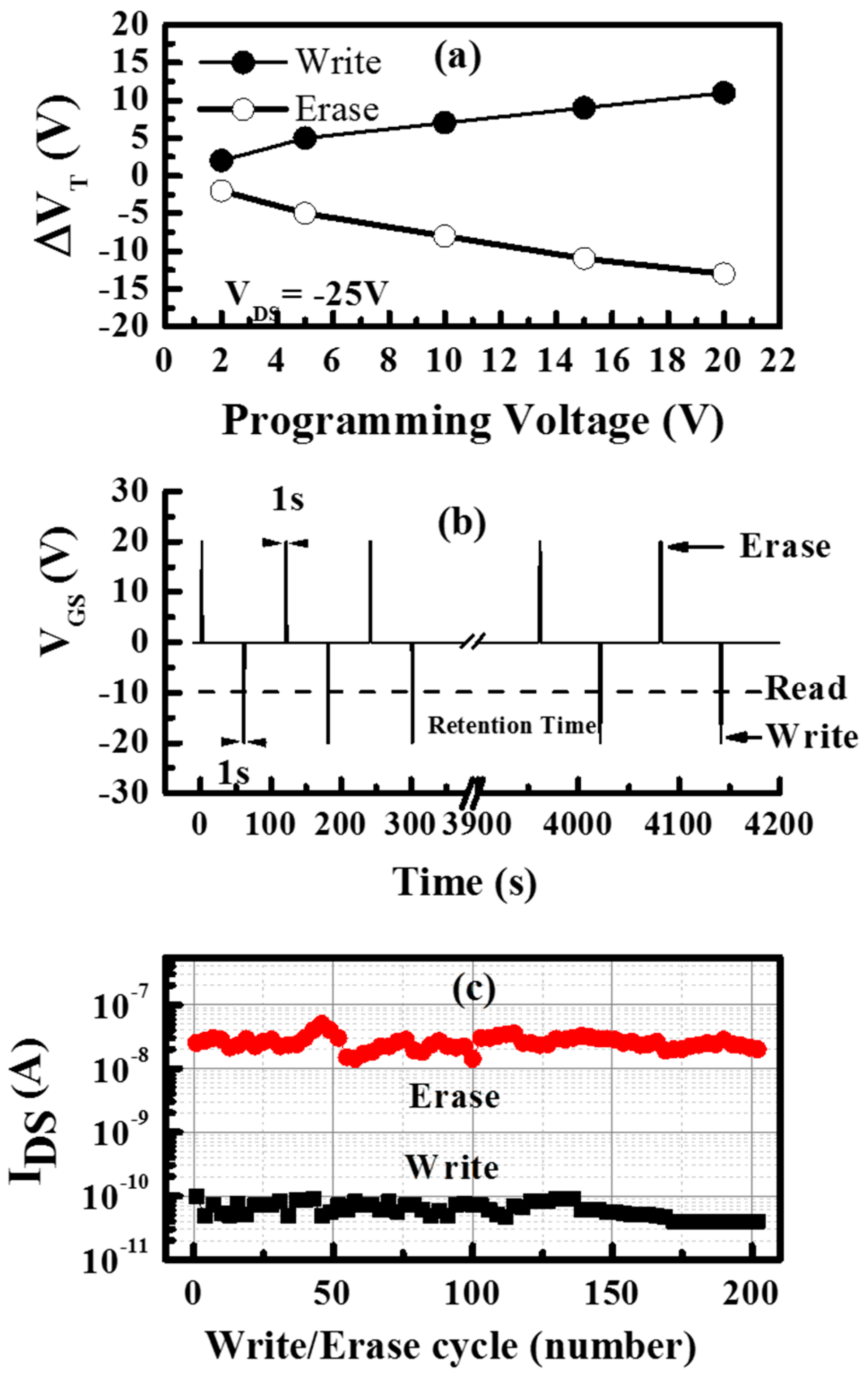

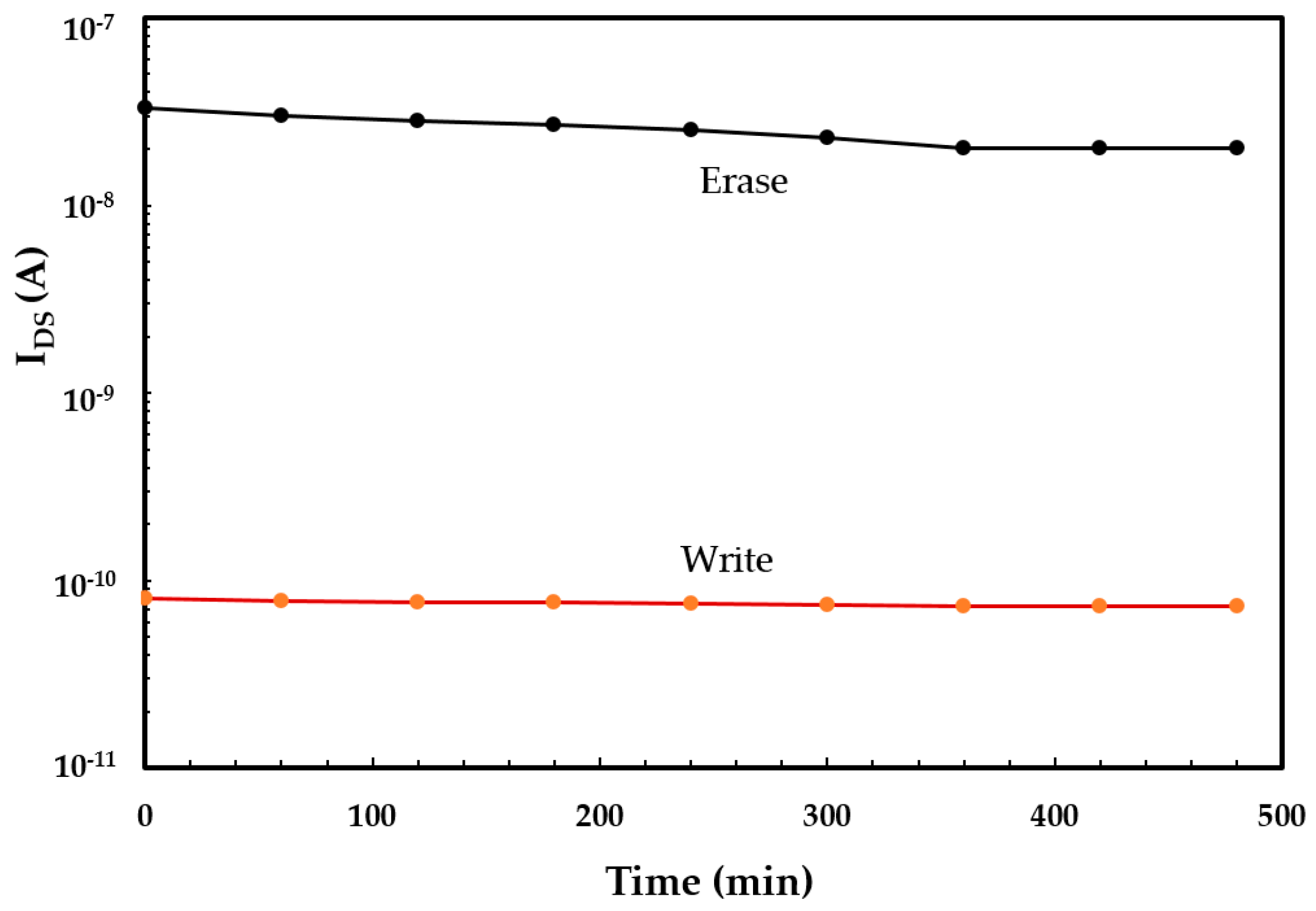

2.2. I–V Characteristics for TFMT Devices

3. Materials and Methods

4. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Cui, C.; Guo, X.; Min, J.; Guo, B.; Cheng, X.; Zhang, M.; Brabec, C.J.; Li, Y. High-performance organic solar cells based on a small molecule with alkylthio-thienyl-conjugated side chains without extra treatments. Adv. Mater. 2015, 27, 7469–7475. [Google Scholar] [CrossRef] [PubMed]

- Liu, Z.; Ojima, H.; Hong, Z.; Kido, J.; Tian, W.; Wang, X.-F. Solution-processed organic photovoltaics based on indoline dye molecules developed in dye-sensitized solar cells. Molecules 2013, 18, 3107–3117. [Google Scholar] [CrossRef] [PubMed]

- Yang, Y.; Chen, W.; Dou, L.; Chang, W.-H.; Duan, H.-S.; Bob, B.; Li, G.; Yang, Y. High-performance multiple-donor bulk heterojunction solar cells. Nat. Photonics 2015, 9, 190–198. [Google Scholar] [CrossRef]

- Patil, H.; Chang, J.; Gupta, A.; Bilic, A.; Wu, J.; Sonar, P.; Bhosale, S.V. Isoindigo-based small molecules with varied donor components for solution-processable organic field effect transistor devices. Molecules 2015, 20, 17362–17377. [Google Scholar] [CrossRef] [PubMed]

- Lee, B.H.; Hsu, B.B.Y.; Patel, S.N.; Labram, J.; Luo, C.; Bazan, G.C.; Heeger, A.J. Flexible organic transistors with controlled nanomorphology. Nano Lett. 2016, 16, 314–319. [Google Scholar] [CrossRef] [PubMed]

- Fakher, S.J.; Hassan, A.K.; Mabrook, M.F. Bias stress effect on high mobility-hysteresis free pentacene-based organic thin film transistors. Synth. Met. 2014, 191, 53–58. [Google Scholar] [CrossRef]

- Yang, X.; Zhou, G.; Wong, W. Functionalization of phosphorescent emitters and their host materials by main-group elements for phosphorescent organic light-emitting devices. Chem. Soc. Rev. 2015, 44, 8484–8575. [Google Scholar] [CrossRef] [PubMed]

- Cantatore, E.; Geuns, T.C.T.; Gelinck, G.H.; Veenendaal, E.V.; Gruijthuijsen, A.F.A.; Schrijnemakers, L.; Drews, S.; Leeuw, D.M.D. A 13.56-MHz RFID system based on organic transponders. IEEE J. Solid-State Circuits 2007, 42, 84–92. [Google Scholar] [CrossRef]

- Zhang, C.; Chen, P.; Hu, W. Organic field-effect transistor-based gas sensors. Chem. Soc. Rev. 2015, 44, 2087–2107. [Google Scholar] [CrossRef] [PubMed]

- Kelly, T.W.; Baude, P.F.; Gerlach, C.; Ender, D.E.; Muyres, D.; Haase, M.A.; Vogel, D.E.; Thiess, S.D. Recent progress in organic electronics: Materials, devices, and processes. Chem. Mater. 2004, 16, 4413–4422. [Google Scholar] [CrossRef]

- Sleiman, A.; Mabrook, M.F.; Nejm, R.R.; Ayesh, A.; Al-Ghafri, A.; Petty, M.C.; Zeze, D.A. Organic bistable devices utilizing carbon nanotubes embedded in poly(methyl methacrylate). J. Appl. Phys. 2012, 112, 024509. [Google Scholar] [CrossRef]

- Ramana, C.H.V.V.; Moodely, M.K.; Kannan, V.; Maity, A.; Jayaramudu, J.; Clarke, W. Fabrication of stable low voltage organic bistable memory device. Sens. Actuators B 2012, 161, 684–688. [Google Scholar] [CrossRef]

- Yun, D.Y.; Arul, N.S.; Lee, D.U.; Lee, N.H.; Kim, T.W. Memory stabilities and mechanisms of organic bistable devices with giant memory margins based on Cu2ZnSnS4 nanoparticles/PMMA nanocomposites. Org. Electron. 2015, 24, 320–324. [Google Scholar] [CrossRef]

- Nejim, R.R.; Ayesh, A.; Zeze, D.A.; Sleiman, A.; Mabrook, M.F.; Al-Ghaferi, A.; Hussein, M. Electrical characteristics of hybrid-organic memory devices based on Au nanoparticles. J. Electron. Mater. 2015, 44, 2835–2841. [Google Scholar] [CrossRef]

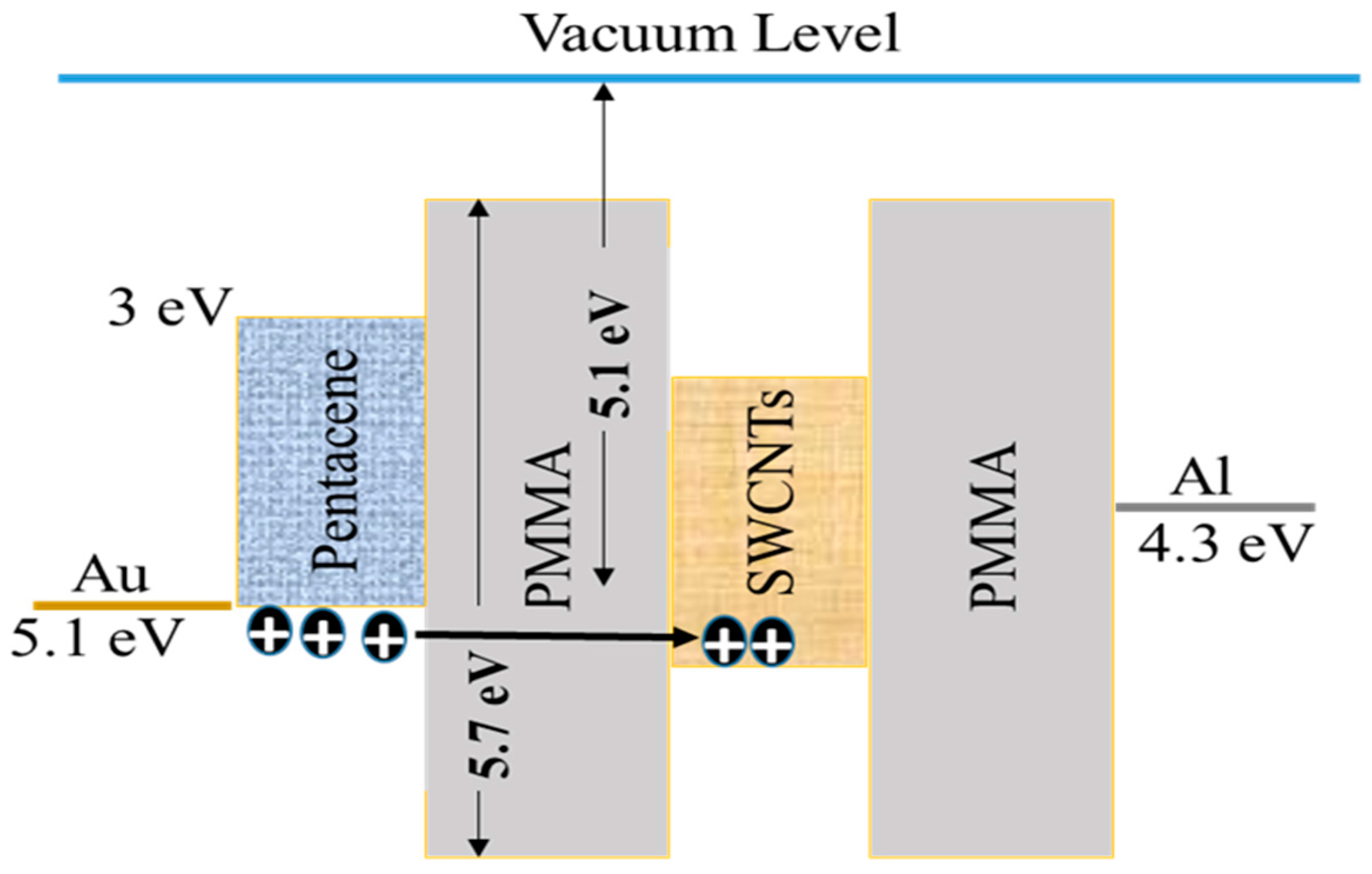

- Sleiman, A.; Rosamond, M.C.; Alba Martin, M.; Ayesh, A.; Al Ghaferi, A.; Gallant, A.J.; Mabrook, M.F.; Zeze, D.A. Pentacene-based metal-insulator-semiconductor memory structures utilizing single walled carbon nanotubes as a nanofloating gate. Appl. Phys. Lett. 2012, 100, 023302. [Google Scholar] [CrossRef]

- Kim, H.-G.; Gim, M.-J.; Jeon, H.-J.; Kim, M.; Jeun, J.-H.; Kim, J.-M.; Kim, Y.-S. Nonvolatile organic memory devices with CdTe quantum dots. Microelectron. Eng. 2013, 111, 210–213. [Google Scholar] [CrossRef]

- William, S.; Mabrook, M.F.; Taylor, D.M. Floating-gate memory based on an organic metal-insulator-semiconductor capacitor. Appl. Phys. Lett. 2009, 95, 093309. [Google Scholar] [CrossRef]

- Alaabdlqader, H.S.; Sleiman, A.; Sayers, P.; Mabrook, M.F. Graphene oxide-based non-volatile organic field effect memory transistors. IET Circuits Devices Syst. 2015, 9, 67–71. [Google Scholar] [CrossRef]

- Mabrook, M.F.; Yun, Y.; Pearson, C.; Zeze, D.A.; Petty, M.C. A pentacene-based organic thin film memory transistor. Appl. Phys. Lett. 2009, 94, 173302. [Google Scholar] [CrossRef]

- Guo, Y.; Zhang, J.; Yu, G.; Zheng, J.; Zhang, L.; Zhao, Y.; Wen, Y.; Liu, Y. Lowering programmed voltage of organic memory transistors based on polymer gate electrets through heterojunction fabrication. Org. Electron. 2012, 3, 1969–1974. [Google Scholar] [CrossRef]

- Tsai, T.-D.; Chang, J.-W.; Wen, T.-C.; Guo, T.-F. Manipulating the Hysteresis in poly(vinyl alcohol)-dielectric organic field-effect transistors toward memory elements. Adv. Funct. Mater. 2013, 23, 4206–4214. [Google Scholar] [CrossRef]

- Lu, X.B.; Daia, Y.J. Memory effects of carbon nanotubes as charge storage nodes for floating gate memory applications. Appl. Phys. Lett. 2006, 88, 113104. [Google Scholar] [CrossRef]

- Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H.J. Ballistic carbon nanotube field-effect transistors. Nature 2003, 424, 654–657. [Google Scholar] [CrossRef]

- Ohishi, M.; Shiraishi, M.; Ochi, K.; Kubozono, Y.; Kataura, H. Improvements in the device characteristics of random-network single-walled carbon nanotube transistors by using high-κ gate insulators. Appl. Phys. Lett. 2006, 89, 203505. [Google Scholar] [CrossRef]

- Rispal, L.; Tschischke, T.; Yang, H.; Schwalke, U. Polymethyl methacrylate passivation of carbon nanotube field-effect transistors: Novel self-aligned process and effect on device transfer characteristic hysteresis. Jpn. J. Appl. Phys. 2008, 47, 3287–3291. [Google Scholar] [CrossRef]

- Fakher, S.J.; Mabrook, M.F. Fabrication and characterization of non-volatile organic thin film memory transistors operating at low programming voltages. Eur. Phys. J. Appl. Phys. 2012, 60, 10201. [Google Scholar] [CrossRef]

- Feng, L.-W.; Chang, C.-Y.; Chang, T.-C.; Tu, C.-H.; Wang, P.-S.; Chang, Y.-F.; Chen, M.-C.; Huang, H.-C. Role of germanium in the reduced temperature dependence of Ti-based nanocrystals formation for nonvolatile memory applications. App. Phys. Lett. 2009, 96, 262110. [Google Scholar] [CrossRef]

- Alba-Martin, M.; Firmager, T.; Atherton, J.; Rosamond, M.C.; Ashall, D.; Al Ghaferi, A.; Ayesh, A.; Gallant, A.J.; Mabrook, M.F.; Petty, M.C.; et al. Improved memory behaviour of single-walled carbon nanotubes charge storage nodes. J. Phys. D: Appl. Phys. 2012, 45, 295401. [Google Scholar] [CrossRef]

- Guo, A.; Fu, Y.; Wang, C.; Guan, L.; Liu, J.; Shi, Z.; Gu, Z.; Huang, R.; Zhang, X. Two-bit memory devices based on single-wall carbon nanotubes: Demonstration and mechanism. Nanotechnology 2007, 18, 125206–125211. [Google Scholar] [CrossRef]

- Mabrook, M.F.; Yun, Y.; Pearson, C.; Zeze, D.A.; Petty, M.C. Charge storage in pentacene/Polymethylmethacrylate memory devices. IEEE Electron. Device Lett. 2009, 30, 632–634. [Google Scholar] [CrossRef]

- Fu, W.Y.; Xu, Z.; Liu, L.; Bai, X.D.; Wang, E.G. Two-bit ferroelectric field-effect transistor memories assembled on individual nanotubes. Nanotechnology 2009, 20, 475305-1–475305-5. [Google Scholar] [CrossRef] [PubMed]

- Kim, W.T.; Jung, J.H.; Kim, T.W. Carrier transport mechanisms in nonvolatile memory devices fabricated utilizing multiwalled carbon nanotubes embedded in a poly-4-vinyl-phenol layer. Appl. Phys. Lett. 2009, 95, 022104. [Google Scholar] [CrossRef]

- Jombert, A.S.; Coleman, K.S.; Wood, D.; Petty, M.C.; Zeze, D.A. Poole–Frenkel conduction in single wall carbon nanotube composite films built up by electrostatic layer-by-layer deposition. J. Appl. Phys. 2008, 104, 094503. [Google Scholar] [CrossRef]

- Sample Availability: Not Available.

© 2016 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC-BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Fakher, S.; Nejm, R.; Ayesh, A.; AL-Ghaferi, A.; Zeze, D.; Mabrook, M. Single-Walled Carbon-Nanotubes-Based Organic Memory Structures. Molecules 2016, 21, 1166. https://doi.org/10.3390/molecules21091166

Fakher S, Nejm R, Ayesh A, AL-Ghaferi A, Zeze D, Mabrook M. Single-Walled Carbon-Nanotubes-Based Organic Memory Structures. Molecules. 2016; 21(9):1166. https://doi.org/10.3390/molecules21091166

Chicago/Turabian StyleFakher, Sundes, Razan Nejm, Ahmad Ayesh, Amal AL-Ghaferi, Dagou Zeze, and Mohammed Mabrook. 2016. "Single-Walled Carbon-Nanotubes-Based Organic Memory Structures" Molecules 21, no. 9: 1166. https://doi.org/10.3390/molecules21091166