Yen-Ming Chen 🗅 and Ching-Jan Chen \*🗅

Department of Electrical Engineering, National Taiwan University, No. 1, Sec. 4, Roosevelt Rd., Taipei 10617, Taiwan; f07921027@ntu.edu.tw

\* Correspondence: chenjim@ntu.edu.tw; Tel.: +886-2-3366-3366 (ext. 348)

Abstract: Digital low-dropout (DLDO) is widely used for power management in the system-on-chip (SoC) because of its low-voltage operation and process scalability. However, conventional DLDOs suffer from the trade-off between transient response and power consumption of the DLDO and the clock generator. This paper proposes an event-driven self-clocked DLDO regulator. The proposed low quiescent current ( $I_Q$ ) event-driven adaptive frequency clock generator (EACG) adapts its frequency in different load conditions without a current sensor or complex compensation circuit for stable operation in the entire load range. The proposed DLDO does not need any external clocking signal and can maintain low output ripple and low power consumption in the steady-state. The clock-less transient detector (CLTD), consisting of two clock-independent transient detection paths, uses power more efficiently and improves the transient response significantly without sacrificing the power consumption. This work was fabricated in a 40 nm CMOS process with an 0.3 nF on-chip capacitor. The measurement results show that with the step load current between 1 mA and 60 mA, the proposed DLDO achieves a transient recovery time of 220 ns. The total  $I_Q$  of the proposed DLDO is only 26  $\mu$ A in steady-state, and it achieves stable operation in the entire load range.

**Keywords:** digital low-dropout (DLDO) regulator; event-driven; low power consumption; adaptive frequency; system-on-chip (SoC)

# 1. Introduction

Modern system-on-chip (SoC) designs employ low-dropout regulators to generate multiple distributed power domains for different sub-circuits, such as radio frequency (RF) circuits, analog circuits, and digital circuits. Each of them has its own operating power level, and the features of the supply voltages are quite different, too. Analog low-dropout (ALDO) regulators have been widely used for such demands for a long time because of their advantage of high power density [1–5]. The ALDOs have mature developments and great characteristics such as low quiescent current [1], high power supply rejection ratio [2,3], and fast transient response [4,5]. However, when the supply voltage (VDD) becomes less than 1 V, the ALDOs' performance faces several difficulties due to degrading voltage gain and greater susceptibility to the process-voltage-temperature (PVT) variations. Instead, digital low-dropout (DLDO) regulators have been widely used for low input voltage power processing in SoC [6–23]. With the process advances and the growing demand for portable devices, digital circuits' supply voltages (VDDs) are now lower.

The DLDOs can be classified into synchronous DLDOs [6–14] and asynchronous DLDOs [15–23]. Synchronous DLDOs use a constantly toggling synchronous clock signal to drive the comparator and the digital controller. Therefore, the control loop latency and the droop response of the synchronous system are highly dependent on the sampling frequency  $F_{CLK}$ . Because the dynamic comparator (or the clock-triggered analog-to-digital

Citation: Chen, Y.-M.; Chen, C.-J. An Event-Driven Self-Clocked Digital Low-Dropout Regulator with Adaptive Frequency Control. *Energies* 2023, *16*, 4749. https://doi.org/ 10.3390/en16124749

Academic Editors: Mohsin Jamil, Yuanmao Ye and Tomasz Pajchrowski

Received: 24 April 2023 Revised: 6 June 2023 Accepted: 9 June 2023 Published: 15 June 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). converter (ADC)) and the controller switch at the edge of the clock signal, the response time ( $T_{RES}$ ) is around 1~1.5 clock cycles for a synchronous DLDO to respond to the load transient. From the capacitor charging equation, we can obtain the output voltage drop:

$$V_{DROP} = \frac{\Delta I_{LOAD} \cdot T_{CLK}}{C_{OUT}}$$

(1)

where  $\Delta I_{LOAD}$  is the difference in load current,  $T_{CLK}$  is the clock cycle time, and  $C_{OUT}$  is the output capacitance. Therefore, to reduce the voltage drop caused by a severe load current change, the synchronous DLDOs have to use a high-frequency clock or a large output decoupling capacitor. However, a fast clock inevitably results in high power dissipation, and a large on-chip capacitor occupies a large area and leads to higher costs. Thus, synchronous DLDOs intrinsically suffer from the bottleneck of clock frequencydependent delay.

Asynchronous DLDOs have gained great attention in recent years since they break the limitation of synchronous DLDOs. In [15–18], they change the digital controller output directly to avoid the bottleneck of clock speed. The design in [19,20] uses a continuous-time ADC to detect the output voltage ( $V_{OUT}$ ) deviations. However, using a pipeline control loop working with a synchronous controller still takes a long recovery time ( $T_R$ ) unless using a fast clock signal. Using continuous-time ADC makes the architecture more complex and sensitive to input voltage variation. Furthermore, using a high-speed continuous-time ADC or a high-speed comparator to detect load transient consumes huge power to maintain a fast response since it has to sense the actual voltage level. Many asynchronous DLDOs require high-frequency external clocks. These high-frequency voltage-controlled oscillators (VCO) consume huge amounts of power and are sometimes even larger than the power consumption of a DLDO.

Another common issue for DLDOs is the stability problem at light-load conditions. Not only does a DLDOs' output pole frequency vary with the load current, but the stability criteria are also related to the sampling frequency of the digital circuits. To avoid this problem, some prior research has used a fixed sampling frequency designed for the minimum load current condition [6]. However, this will make the recovery time longer and limit the loading range. For pursuing better performance, the fixed frequency DLDO designs in recent years mostly add a complex digital compensator to avoid unstable operation. In [14], they analyzed the limit cycle oscillation (LCO) phenomenon of conventional fixed-frequency DLDO. They present a solution by adding auxiliary power transistors to add a zero at the output node. In addition, most of the capacitor-less DLDOs ignored the parasitic capacitance at the output node, which is often quite large in a Very Large-Scale Integration (VLSI) system [18]. When the parasitic capacitance at the supply node of enormous digital circuits is up to dozens of pF levels, it likely will affect the stability of a high-frequency clock capacitor-less DLDO.

In this paper, an event-driven self-clocked DLDO regulator is proposed to solve the aforementioned issues of synchronous and asynchronous DLDOs. A clock-less transient detector (CLTD) and an event-driven adaptive frequency clock generator (EACG) are presented in the proposed DLDO. Furthermore, EACG adapts its frequency to load current without a current sensor. Thus, stable operation in the entire load range is achieved with a simple circuit. We separate the detect path into the fast path and slow path, where one can provide a fast response, and the other can ensure the accuracy of the  $V_{OUT}$ . Since the fast path only has to transfer the output voltage swing into a pulse signal to activate the switching controller, a fast load transient response with a low quiescent current can be achieved. The slow transient detection path ensures a smaller DC error. This paper is organized as follows. In Section 2, we introduce the architecture and the operation of the proposed DLDO and give some introductions to its stability. Section 3 presents the detailed circuit implementation and analysis of this work. The measurement results are shown in Section 4. Finally, we give a conclusion in Section 5.

## 2. The Concept of the Proposed DLDO

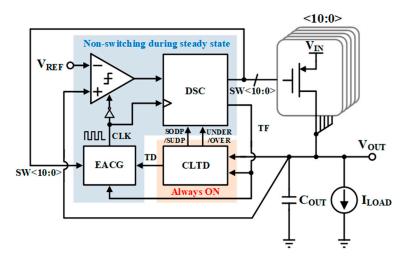

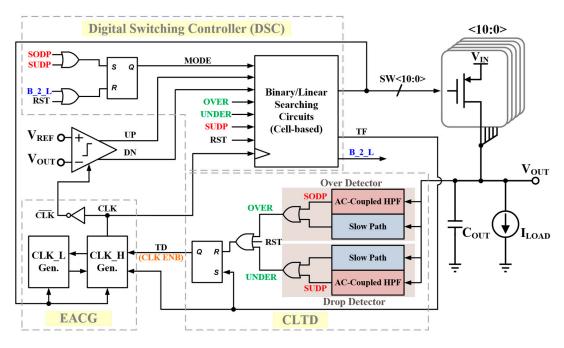

The simplified block diagram of the proposed event-driven self-clocked DLDO is shown in Figure 1. There are five main parts in the system, including the clock-less transient detector (CLTD), the event-driven adaptive frequency clock generator (EACG), the digital switching controller (DSC), the binary-weighted pMOS power transistor array, and a dynamic comparator. During the transient period, CLTD distinguishes the V<sub>OUT</sub> slope (sharp/smooth) and direction (under-/over-shoot), and EACG adapts its clock signal (CLK) frequency based on turn-on bits SW<10:0>. The TD signal is the "transient detected signal" generated by the CLTD to trigger the system at the beginning of the transient event. The TF signal is the "transient finished signal" generated by the DSC to shut down EACG, the comparator, and DSC and reset the CLTD at the end of the transient event.

Figure 1. Simplified block diagram of the proposed DLDO.

#### 2.1. Steady-State Operation

When the system is in the steady-state (between two transient events), only the CLTD will remain operational. Because the EACG will not generate the clock signal at this time, the DSC and the dynamic comparator will not switch and will consume little power. The total quiescent current of the system comes from the CLTD and leakage current. Since the power transistor array will not switch, no ripple will occur at the  $V_{OUT}$  node. This can make the output voltage cleaner.

### 2.2. Transient Period Operation

As Figure 1 shows, when a load transient (event) occurs, the CLTD tells the DSC which direction (under or over) and what kind (sharp or smooth) the load transient is and sends the TD signal to trigger the EACG simultaneously. After the EACG receives the TD signal, it generates the clock signal immediately and adapts the sampling frequency based on the present load current ( $I_{Load}$ ) to ensure stable operation. Due to the feature of DLDOs, in that the power transistor's turn-on bits represent the output current, this work achieves load adaptive clock frequency by feedbacking SW signal (turn-on bits) instead of using complicated load current sensing methods. The adaptive frequency control method details will be introduced in Section 3.

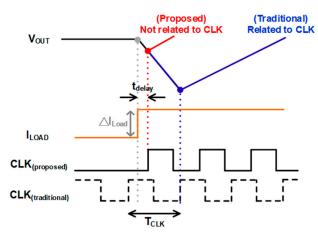

The proposed event-driven DLDO can significantly reduce the  $V_{OUT}$  drop compared to traditional DLDOs, which use a clock-related detecting technique. Figure 2 shows the load transient response of the synchronous DLDO and the proposed DLDO, where  $t_{delay}$ is the delay of CLTD. It can be seen that the first positive edge of the clock will always follow closely to the load current change for the proposed DLDO. Therefore, the system's response time will no longer be related to sampling frequency.

Figure 2. Load transient response of the synchronous DLDO and the proposed DLDO.

After the EACG starts generating clock signals, the DSC will start to search the correct turn-on bits of the pMOS power transistor array according to the load transient features, as shown in Table 1.

| Fast Path Output | Slow Path Output | MODE             | DSC Reaction                                                                                                                                                 |  |

|------------------|------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                | Х                | 1<br>(sharp)     | Binary search<br>① V <sub>OUT</sub> drops:<br>Turn on MSB<br>at the first clock edge<br>② V <sub>OUT</sub> rises:<br>Turn off MSB<br>at the first clock edge |  |

| 0                | 1                | 0<br>(smooth)    | Linear search                                                                                                                                                |  |

| 0                | 0                | 0<br>(unchanged) | Steady-state                                                                                                                                                 |  |

Table 1. The searching method of DSC with different CLTD outputs and different types of V<sub>OUT</sub> transient.

Once the V<sub>OUT</sub> slope rises/falls sharply ( $|dV_{OUT}/dt|$  is large), the signal "MODE" in the DSC will pull high, which means that a severe load transient occurred. Therefore, the DSC will begin the binary search when the CLK starts toggling. The operation of the DSC will depend on the V<sub>OUT</sub> direction told by the CLTD. If the V<sub>OUT</sub> rises sharply, the DSC will turn on the most significant bit (MSB) of the power transistors array at the first positive edge of the clock. Then, at every negative edge of the clock, the dynamic comparator will compare the V<sub>OUT</sub> and the reference voltage (V<sub>REF</sub>), and send the result to the DSC. The DSC will switch the [MSB-1] bit at the next positive clock edge and do this cyclically to the least significant bit (LSB).

When the binary search is over, the DSC will turn to use the linear search to ensure the  $V_{OUT}$  is back to  $V_{REF}$ . If the output of the comparator is three consecutive opposite values, the DSC will determine that the system is back to steady-state and send out the TF signal. The signal TF will shut down the EACG and reset the CLTD. Finally, the system will stop switching and wait for the next event.

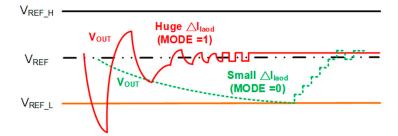

If the TD goes high while MODE is still 0, it means there is a slight load transient occurring or the  $V_{OUT}$  deviates outside the design window. When the clock starts toggling, the DSC will carry out the linear search directly to prevent unnecessary huge  $V_{OUT}$  swings caused by the binary search. Similarly, if the output of the comparator is three consecutive opposite values, the DSC will send out the TF signal to shut the EACG down and reset the CLTD, too. The transient behaviors of MODE = 1 and 0 are shown in Figure 3.

Figure 3. Transient behaviors of MODE = 1 and 0.

Since the proposed DLDO separates the transient detector into two parts, it achieves a fast transient response and maintains low power consumption in the steady-state. The fast paths only have to detect the severe  $V_{OUT}$  swings instead of obtaining the actual  $V_{OUT}$  level. Therefore, the detecting circuits can utilize the power more efficiently and do not need a high-speed but power-hungry detecting circuit. Meanwhile, the slow paths ensure the  $V_{OUT}$  will not gradually deviate from the  $V_{REF}$ . This deviation may happen when there is a slow load transient event, or the load current does not exactly match the discrete steps of current being provided by the pass transistors array. Thus, the DLDO can turn off its clock during steady-state but still ensure a small DC error. The window consisting of  $V_{REF_H}$  and  $V_{REF_L}$  can clamp the  $V_{OUT}$  in an acceptable DC deviation range. Most importantly, both the fast paths and the slow paths can be realized by simple low-quiescent current circuits.

### 2.3. Stability

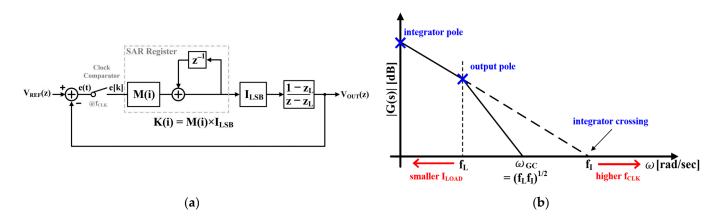

In [13,19], the stability of common fixed sampling frequency DLDOs with PI controllers was analyzed in detail. The linear small-signal ac model of a binary search DLDO in the z-domain is derived in [13], as shown in Figure 4a. The loop gain of such a second-order feedback control loop is given by

$$G(z) = \frac{K(i) \cdot (1 - z_L) \cdot z}{(z - 1) \cdot (z - z_L)}$$

$$\tag{2}$$

where K(i) is the gain, and the loop gain has two poles: the integrator pole (z = 1) and the output pole ( $z_L = e^{-fL/fCLK}$ ). The corresponding continuous-time loop gain transfer function G(s) can be given by

$$G(s) = \frac{{\omega_n}^2}{s \cdot (s + 2\eta \omega_n)} \tag{3}$$

The loop gain G(s) contains two poles, where z = 1 and  $z_L$  in the z-domain map to s = 0 and  $f_L$  in the s-domain. The Bode diagram of G(s) is shown in Figure 4b.

Figure 4. (a) Small-signal ac model of the binary search DLDO. (b) Bode diagram of DLDO loop gain.

The phase margin of loop gain is determined by  $f_L$  and  $f_I$ , where  $f_L$  is inversely proportional to the output load RC-time constant and  $f_I$  is proportional to the sampling frequency  $f_{CLK}$ . The phase margin of G(s) is derived as (4) [13].

$$PM = 90^{\circ} - \tan^{-1} \left(\frac{f_{\rm I}}{f_{\rm L}}\right)^{1/2}$$

(4)

Increasing the sampling frequency can lead to a wider bandwidth and a faster response for a given output load. However, the phase margin is reduced at light-load conditions, causing an instability problem. In [13,19], they insert a proportional derivative (PD) controller or compensator into the loop to ensure the stability of the DLDO.

This paper proposes an event-driven adaptive frequency clock generator (EACG) to tackle this issue. The EACG can adapt its frequency to be proportional to the  $I_{LOAD}$ , making  $f_I$  track  $f_L$ . According to the previous analysis, the phase margin can be kept at a fixed value at various loading conditions. Thus, the system can operate stably. Instead of adding a current sensor to sense the load information, this paper proposes a method to estimate load information from power transistors' turn-on bits SW<10:0> as shown in Figure 1. This method is an easy and low quiescent power way to solve instability issue without using complex circuits. The design detail will be presented in Section 3.3.

## 3. Circuit Implementation

The detailed architecture of the proposed DLDO is shown in Figure 5. The control circuits include three main parts: the DSC, the CLTD, and the EACG. The proposed CLTD can distinguish which direction (under or over) and what kind (sharp or smooth) the load transient is and wakes the system up. The proposed EACG is only active in the transient period to save power consumption, and it can adapt the clock frequency to achieve a stable operation. The DSC consists of binary/linear searching circuits, an SR-latch, and an OR gate. These circuits control the whole system and switch the pMOS power transistor array to maintain V<sub>OUT</sub> at the required level. This section will give detailed introductions to the three individual sub-circuits.

Figure 5. Architecture of the proposed DLDO.

## 3.1. Control Logic of the Digital Switching Controller (DSC)

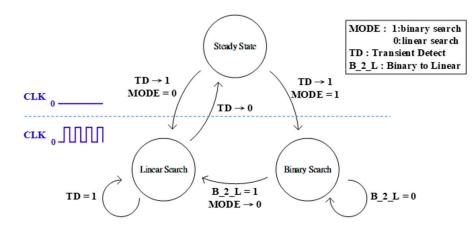

The control logic of the DSC is shown in Figure 6. Once the TD goes high, it means that there occurs a load transient, and the clock will start toggling and make the DSC start operating. The DSC will choose the proper searching method base on the "MODE" signal, as shown in Table 1. Once the V<sub>OUT</sub> slope rises/falls sharply ( $|dV_{OUT}/dt|$  is large, huge  $\Delta I_{LOAD}/\Delta t$ ), the signal "MODE" will be logic-high (=1). Relatively, if the V<sub>OUT</sub> slope rises/falls smoothly ( $|dV_{OUT}/dt|$  is small, less  $\Delta I_{LOAD}/\Delta t$ ), the signal "MODE" will be logic-low (=0).

Figure 6. State diagram of the proposed DLDO.

As in Figure 5, once the "severe over-shoot detected pulse" (SODP) or the "severe under-shoot detected pulse" (SUDP) pulls high, which means there is a severe load (large  $|dV_{OUT}/dt|$ ), the signal MODE will be pulled to 1, and the TD signal will also be pulled up. Therefore, the DSC will start doing the binary search to recover the V<sub>OUT</sub> immediately when the CLK starts toggling. Until the binary search is over (search to LSB), the DSC will send out a signal "B\_2\_L" to reset the SR-latch, and the MODE will be set to 0. Thus, the DSC will carry out the linear search until the system is back to steady-state. Finally, the DSC will send out a pulse "TF" to shut the EACG down and reset the CLTD.

On the contrary, if TD pulls high but MODE still =0, that means the  $V_{OUT}$  is out of the clamping window, but the  $V_{OUT}$  slope is not sharp enough to activate the ac-couple HPF path. There occurs a slight load (small  $|dV_{OUT}/dt|$ ) transient, and the DSC will start carrying out the linear search to correct the output current without causing huge VOUT swings. Until the system is back to steady-state, the TF pulls high, the TD pulls low, the CLTD is reset, and the clock stops toggling.

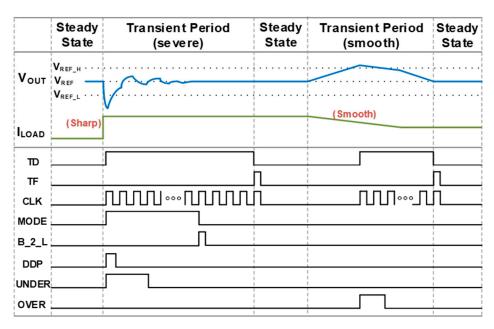

Figure 7 shows the timing diagram of an overall operating waveform of the proposed DLDO, taking two load transient events as examples. Assume that there comes a severe I<sub>LOAD</sub> step-up load transient event (large dI<sub>LOAD</sub>/dt, dI<sub>LOAD</sub>/dt > 0, large  $|dV_{OUT}/dt|$ ) first and then a slight I<sub>LOAD</sub> step-down event occurs (small dI<sub>LOAD</sub>/dt, dI<sub>LOAD</sub>/dt < 0, small  $|dV_{OUT}/dt|$ ) later.

In the steady-state, all the signals remain 0. When the first load transient occurs, SUDP goes high and pulls up TD. Then, TD triggers the CLK signal, and the system starts using binary search to raise  $V_{OUT}$  immediately. After the binary search is over, the DSC sends a B\_2\_L pulse, and the system will turn to use a linear search to make sure  $V_{OUT}$  is back to  $V_{REF}$  correctly.

In slight load transient conditions, the system will react after V<sub>OUT</sub> is out of the windows consisting of V<sub>REF\_H</sub> and V<sub>REF\_L</sub>. The OVER signal pulls up when V<sub>OUT</sub> exceeds V<sub>REF\_H</sub> and activates the system. Then the DSC will use a linear search to regulate the V<sub>OUT</sub> back. The MODE remains 0 from the beginning to the end. After V<sub>OUT</sub> equals V<sub>REF</sub>, TF will pull high and shut the system down.

Figure 7. The timing diagram of an overall operating waveform.

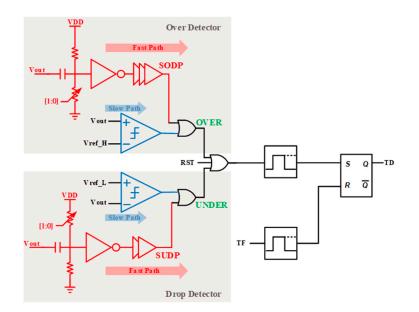

### 3.2. Clock-Less Transient Detector (CLTD)

The proposed clock-less transient detector (CLTD) is shown in Figure 8. The CLTD consists of two blocks, one is for  $V_{OUT}$  over-shoot detection, and the other is for  $V_{OUT}$  under-shoot detection. Both of them have a fast signal path and a slow signal path, and this means the CLTD can distinguish which type of load transient occurred and let the digital switching controller (DSC) select the appropriate searching method.

Figure 8. The architecture of the proposed CLTD.

The fast signal paths are the  $V_{OUT}$  drop detector and the  $V_{OUT}$  over detector. They are two ac-coupled pulse generators of a high-pass capacitor, a resistor voltage divider, and an inverter chain. The fast signal paths design is inspired by [18], which demonstrated an efficient drop-detecting method. Thus, similar undershoot performance can be achieved. These simple circuits can transfer a voltage swing to a pulse signal in a short time. Since low VDD conditions or the trigger points of the inverters varied by the process will degenerate the noise immunity, we added two trimming bits to adjust the resistance voltage divider. These trimming bits can adjust the noise margin of the high-pass paths depending on the different operating situations.

The two slow paths are two 2.5  $\mu$ A-quiescent-current continuous-time comparators, which compare V<sub>OUT</sub> with V<sub>REF\_H</sub> and V<sub>REF\_L</sub>, respectively. V<sub>REF\_H</sub> and V<sub>REF\_L</sub> determine the upper-bound and lower-bound of steady-state V<sub>OUT</sub> range. Once V<sub>OUT</sub> deviates out of the window, the TD will pull high to trigger the whole system.

With the fast paths and the slow paths in the CLTD, the proposed DLDO can distinguish different load transient situations ( $V_{OUT}$  rises/drops, large/small  $|dV_{OUT}/dt|$ ). Hence, the DSC can choose the proper searching method to regulate the output voltage, as shown in Table 1.

#### 3.3. Event-Driven Adaptive Frequency Clock Generator (EACG)

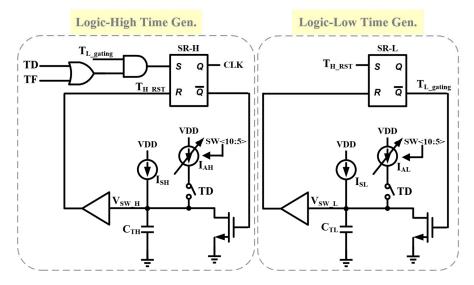

The proposed event-driven adaptive frequency clock generator (EACG) is shown in Figure 9. The EACG consists of two similar clock generator sub-circuits, and they control the logic-high time and logic-low time of the clock signal, respectively.

Figure 9. Circuit of the proposed event-driven adaptive frequency clock generator (EACG).

As Figure 9 shows, a logic-high time is initiated when the triggered signal TD goes high. The sawtooth voltage  $V_{SW_H}$  starts to rise due to two currents,  $I_{SH}$  and  $I_{AH}$ , charging a capacitor  $C_{TH}$ . When  $V_{SW_H}$  reaches 1/2 VDD (assume  $V_{IN} = VDD$ ), the inverter chain output  $T_{H_RST}$  will reset the SR-H latch circuit and set the SR-L latch circuit simultaneously. After SR-L latch is set, a logic-low time is initiated. Like the logic-high time, when  $V_{SW_L}$  reaches 1/2 VDD, the SR-L latch is reset, and  $T_{L_gating}$  will set the SR-H latch. Thus, a toggling clock signal is obtained. After the TD signal is 0 and the TF pulse pulls low, the SR-H latch stops set/reset, and the clock signal will stop toggling. Both logic-high time generator and logic-low time generator have two current sources: a static small current  $I_{SH}/I_{SL}$  and a dynamic binary-weighted current array  $I_{AH}/I_{AL}$ . The dynamic current array will only be connected to the capacitor when the transient event occurs (TD = 1). The dynamic current array can be adapted to the different load currents to achieve adapting frequency for stable operation.

Since the logic-high/low time  $(T_H/T_L)$  of the EACG is generated by current charging a capacitor, they can be expressed as:

$$T_{\rm H} = \frac{\frac{1}{2} \text{VDD} \cdot C_{\rm TH}}{(I_{\rm SH} + I_{\rm AH})}$$

(5)

$$T_{L} = \frac{\frac{1}{2} VDD \cdot C_{TL}}{(I_{SL} + I_{AL})}$$

(6)

We can simplify the power stage of DLDO as an RC circuit, and its time constant can be expressed as:

$$\tau = (\mathbf{R}_{\text{ON}\_\text{EQ}} || \mathbf{R}_{\text{LOAD}}) \cdot \mathbf{C}_{\text{OUT}}$$

(7)

where  $R_{ON\_EQ}$  is the equivalent resistance of the power transistor array,  $R_{LOAD}$  is the equivalent resistance of the output load, and  $C_{OUT}$  is the output capacitance. It can be seen that the output pole will vary with different load current conditions. In other words, the charging/discharging time of the output node will vary with different load current conditions. In Section 2.3, we cited [13] to give a short discussion about how the output pole and the sampling clock frequency affect the stability of DLDO. To tackle this issue, the proposed EACG adapts the clock frequency with the output current. That is, the clock frequency is designed to be proportional to the output pole frequency. Thus, the phase margin is fixed at various load conditions according to the analysis in reference [13].

Because the DSC switches at the positive clock edge and the  $V_{OUT}$  node is sampled at the negative clock edge, the logic-high time  $T_H$  is designed to be proportional to the time constant of the power stage, as shown in (8). The proportional coefficient is chosen as more than five, which indicates that the output voltage is fully charged before sampling,

$$T_{\rm H} \ge 5 \cdot \tau = 5 \cdot (R_{\rm ON\_EQ} || R_{\rm LOAD}) \cdot C_{\rm OUT}$$

(8)

Assuming  $\beta = V_{OUT}/V_{IN}$ , we can derive (9) from the equivalent circuit. Then,  $R_{ON_EQ}$  can be rearranged as (10).

$$\beta = \frac{V_{OUT}}{V_{IN}} = \frac{R_{LOAD}}{R_{ON\_EQ} + R_{LOAD}}$$

(9)

$$R_{ON\_EQ} = \left(\frac{1-\beta}{\beta}\right) \cdot R_{LOAD}$$

(10)

From Equations (5) and (8)–(10), we can obtain the stable design criterion of the charging currents ( $I_{SH} + I_{AH}$ ) of the logic-high time generator versus the load current  $I_{LOAD}$  (assume  $V_{IN} = VDD$ ) as (11).

$$I_{SH} + I_{AH} \le \frac{C_{TH}}{10 \cdot C_{OUT} \cdot (1 - \beta)\beta} \cdot R_{LOAD}$$

(11)

As can be seen from (8), logic-high time  $(T_H)$  should be adapted with the load current to ensure  $V_{OUT}$  stability. Therefore, the charging current  $(I_{SH} + I_{AH})$  of the proposed EACG is designed to be proportional to the load current.

Suppose we just use a fixed high-frequency clock signal for fast transient recovery. In that case, it might violate the criteria of (8) and cause unstable operations, particularly in the light-load condition. Figure 10 shows that if the load current changes from heavy-load to light-load, we still use the high-frequency designed for heavy-load, which might cause the  $V_{OUT}$  to start ringing and the system cannot go back to the steady-state. This is because the output node's time constant in the light-load becomes much larger than in the heavy-load, and the clock frequency cannot meet the criteria of (8).

Figure 10. The unstable phenomenon in the light-load if the clock frequency cannot meet the criteria of (8).

Moreover, since only the logic-high time needs to fulfill the designed timing criteria of (8), the logic-low time can be shrunk to accelerate the response and reduce the recovery time. In other words, to obtain a shorter recovery time, the duty of CLK could be larger than 50%. The duty of CLK is  $C_{TH}/(C_{TH} + C_{TL})$ . For example, if  $C_{TH}$ : $C_{TL} = 3:1$ , the duty will be 75%.

The load current information can be obtained from the gate signal of the binaryweighted power transistors array, SW<10:0> in Figures 1 and 5 of the proposed DLDO. The current value of SW<10:0> is the turn-on bits of the pMOS array, and it is proportional to the current I<sub>LOAD</sub>. Hence, adaptive charging current I<sub>AH</sub> is implemented with a binaryweighted current array and pass switches controlled by the TD signal and the gate signal of the DLDO's power transistors array. When the I<sub>LOAD</sub> is at the lightest condition, the most significant bit (MSB) of turn-on bits is SW<4>. Therefore, the adaptive charging current I<sub>AH(AL)</sub> is controlled by TD, and the rest bits of SW<10:0> (SW<5>~SW<10>). Considering the power consumption, the adaptive charging current is gated in the steady-state (TD = 0). When the system is in the transient period (TD = 1), the adaptive charging currents provide current I<sub>AH(AL)</sub> and make (I<sub>SH(SL)</sub> + I<sub>AH(AL)</sub>) proportional to the present output current.

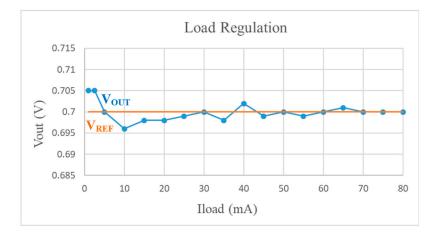

The DC error is caused by the resolution of the equivalent  $R_{ON}$  of the power transistor array. Assume that the system is in steady-state and at the lightest load; the turn-on bit "N" makes  $V_{OUT}$  slightly lower than  $V_{REF}$ , but "N + 1" bit will make  $V_{OUT}$  slightly higher than  $V_{REF}$ . The quantization error between N and N + 1 has to be smaller than the maximum acceptable DC error. For example, if the specification of DC error is designed to be within 10 mV, the DC error value can be expressed as:

$$\begin{cases} V_{OUT} - VDD \cdot \left(\frac{R_{LOAD}}{R_{ON_{EQ(N+1)}} + R_{LOAD}}\right) \leq -10 \text{ mV} \\ V_{OUT} - VDD \cdot \left(\frac{R_{LOAD}}{R_{ON_{EQ(N)}} + R_{LOAD}}\right) \leq 10 \text{ mV} \end{cases}$$

(12)

$$\begin{cases} R_{ON\_EQ(N+1)} = \frac{R_{ON}}{N+1} \\ R_{ON\_EQ(N)} = \frac{R_{ON}}{N} \end{cases}$$

(13)

After some simulations and calculations with (12) and (13), to meet the designed steady-state DC error (<10 mV), the turn-on bits at minimum load current in this work are designed as 5 bits. Because the DC errors are caused by the quantization error of the binary-weighted power transistor array, the quantization error is limited by LSB. The effect of LSB (SW<0>) turned on or off is more significant at light-load conditions. Therefore, the DC errors usually become larger in the light-load condition, as shown in Figure 11.

Figure 11. Load regulation of the proposed DLDO. (by post-layout simulation,  $V_{\text{REF}} = 0.7$  V).

#### 4. Measurement Results

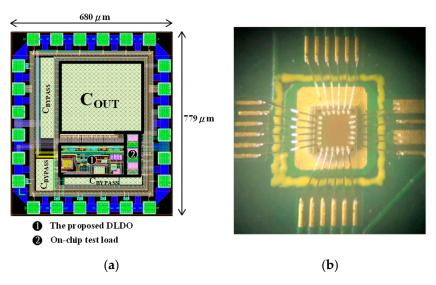

The proposed event-driven self-clock DLDO is fabricated in a 40 nm CMOS process. As shown in Figure 12, the chip area of the proposed circuit is 0.0338 mm<sup>2</sup>, which includes the power pMOS array, DSC, EACG, CLTD, the comparator, and other control logic. The remaining chip area is for the 0.3 nF on-chip decoupling capacitor, power rail decoupling capacitors, and the on-chip test load.

Figure 12. (a) Chip layout of the proposed DLDO. (b) Die photo of the test chip with bond wires.

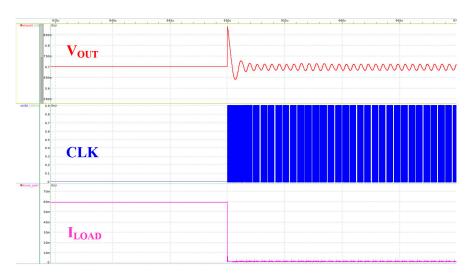

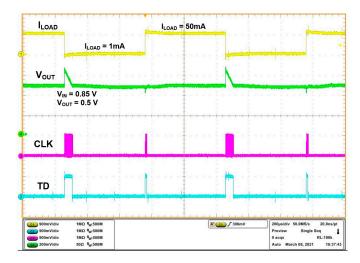

Figures 13–15 show the load transient response of the proposed DLDO with different  $V_{IN}/V_{OUT}$  and load change conditions to verify the robustness of the proposed DLDO. Figure 13 shows the load transient response with step  $I_{LOAD}$  from 1 mA to 50 mA. The load transient is realized by switching the NMOS switches in series with resistors in the on-chip test load. As shown in Figure 13, the self-generated clock signal CLK is only toggling when TD = 1. In other words, the control circuits and the power transistors will not switch when the system is in a steady-state. This implementation can save power and has a cleaner  $V_{OUT}$  waveform.

Figure 13. Measured load transient response of the proposed DLDO to a periodic square-wave load current (1 mA–50 mA) with  $V_{IN}$  = 0.85 V,  $V_{OUT}$  = 0.5 V.

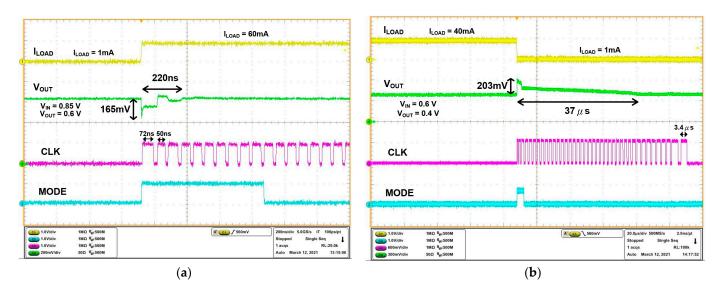

**Figure 14.** Zoomed-in measured waveform of the load transient period. (**a**) Step-up load transient period. (**b**) Step-down load transient period.

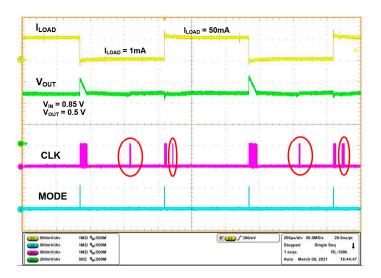

Figure 15. Transient waveforms of  $V_{OUT}$  clamping by the window of  $V_{REF\_L}$  and  $V_{REF\_H}.$

Figure 14 shows the zoomed-in oscilloscope captures of the load transient period with varying load current levels. Figure 14a shows the I<sub>LOAD</sub> step-up load transient period. The proposed DLDO shows a load transient time of 220 ns with 165 mV undershoot. As illustrated in the capture, the DSC used binary search to raise the V<sub>OUT</sub> immediately at the beginning of MODE = 1, then linear search to make it closer to V<sub>REF</sub> (MODE = 0). After the DSC turns on the MSB (SW<10>) at the first positive clock edge, the clock frequency is boosted up to match the rising load current to achieve adaptive frequency control. Figure 14a verifies that CLK's logic-high time (T<sub>H</sub>) keeps adjusting with the binary searching process. In a heavy load condition (60 mA), T<sub>H</sub>  $\approx$  50 ns, and in the light load condition, T<sub>H</sub> is extended up to 3.4 µs. Thus, there is no limit cycle oscillation that happens at light-load or heavy-loads. As illustrated in Figure 14, the duty of the clock signal is larger than 50% as we designed it to reduce the recovery time.

Figure 14b shows the zoomed-in oscilloscope captures of the load transient period with  $I_{LOAD}$  from 40 mA to 1 mA. The recovery time of the  $I_{LOAD}$  step-down transient is 37 µs, and the overshoot is 203 mV. The adaptive clock frequency is slower when the  $I_{LOAD}$  is lower. The DSC uses linear search early when  $V_{OUT}$  is close to  $V_{REF}$  to avoid unwanted undershoot caused by binary search.

The proposed DLDO can clamp the V<sub>OUT</sub> within the correct level by the window consisting of V<sub>REF\_L</sub> and V<sub>REF\_H</sub>. In Figure 15, V<sub>REF\_L</sub> is enlarged such that the difference between V<sub>REF\_L</sub> and V<sub>REF</sub> reduces from the originally designed 10 mV value as in Figure 13. According to the analysis in (12) and (13), the V<sub>OUT</sub> DC error caused by the mismatch between load current and pass transistor current is large enough to trigger the slow path in CLTD. There are four events (in the red circle) where CLK is triggered, but the MODE signal equals zero. These events show that the V<sub>OUT</sub> is slightly deviating from V<sub>REF</sub>, and the DSC uses linear search to regulate it back. This method can maintain the V<sub>OUT</sub> DC errors within the defined level.

Table 2 shows the performance comparison of this work with the state-of-the-art designs. The most common figure-of-merits (FoMs) in (14) [24] and (15) are used to fairly compare the performance considering the transient response and power trade-off.

$$FoM_{1} = C_{OUT} \cdot \frac{\Delta V_{DROP}}{(I_{Max} - I_{MIN})} \cdot \frac{I_{Q}}{(I_{Max} - I_{MIN})}$$

(14)

$$FoM_{2} = C_{OUT} \cdot \frac{\Delta V_{DROP}}{V_{OUT}} \cdot \frac{I_{Q}}{(I_{Max} - I_{MIN})}$$

(15)

The comparison table shows that the proposed DLDO achieves FoM improvement over the previous measurements in FoM1 and FoM2, which are the only two using adaptive frequency to avoid limit cycle oscillation. With the adaptive frequency self-clocked control method, the proposed DLDO can have a short recovery time and erase the limit cycle oscillation phenomenon without using a complex compensation circuit such as reference [13]. The FoM improvements are owed to the proposed CLTD and EACG. The event-driven asynchronous control means the quiescent current of the system is reduced to a very low level. The CLTD utilizes the power more efficiently than a power-hungry high-speed transient detector. Therefore, this work can achieve a fast transient response without consuming huge power. Furthermore, the quiescent current  $I_Q = 26 \mu A$  includes the power consumption of the clock generator EACG, while most of the prior research did not take the power consumption of the power-hungry clock generator into account.

| Design                                           | [ <mark>19</mark> ]<br>JSSC 2017 | [20]<br>JSSC 2017 | [13]<br>JSSC 2018 | [22]<br>ISSCC 2018 | [23]<br>VLSI 2019 | [9]<br>TPE 2022 | This Work              |

|--------------------------------------------------|----------------------------------|-------------------|-------------------|--------------------|-------------------|-----------------|------------------------|

| Process                                          | 65 nm                            | 28 nm             | 65 nm             | 40 nm              | 22 nm             | 65 nm           | 40 nm                  |

| Control                                          | Event-driven                     | Time-driven       | SAR/PWM           | Burst Mode         | Event-driven      | VCO-based       | Event-driven           |

| V <sub>IN</sub> (V)                              | 0.5–1.0                          | 1.1               | 0.5–1             | 0.6–1.1            | 0.55–1.2          | 0.9–1.2         | 0.55–1.0               |

| V <sub>OUT</sub> (V)                             | 0.45-0.95                        | 0.9               | 0.3–0.45          | 0.5–1              | 0.5–1.15          | 0.5–1.1         | 0.4–0.7                |

| Load Range                                       | 150 μΑ–500 μΑ                    | 4 mA-200 mA       | 33.6 μA–2 mA      | 1 mA-20 mA         | 400 µA–2 A        | 150 μA–19 mA    | 1 mA-60 mA             |

| C <sub>OUT</sub> (nF)                            | 0.4                              | 23.5              | 0.4               | 4.7                | 7                 | 0.2             | 0.3                    |

| I <sub>Q</sub> (μA)                              | 12.5                             | 110               | 14                | 20                 | 2400              | 131             | 26                     |

| Sampling clock rate                              | 200 MHz                          | N.R.              | 1 MHz–240 Hz      | 100 MHz            | 6 GHz             | 500 MHz         | External<br>Clock-Less |

| V <sub>DROOP</sub> @ load step<br>transient test | 22 mV<br>@0.2 mA                 | 120 mV<br>@180 mA | 40 mV<br>@1.06 mA | 40 mV<br>@19 mA    | 100 mV<br>@0.5 A  | 78 mV<br>@3 mA  | 165 mV<br>@59 mA       |

| Recovery time<br>T <sub>R</sub> (μs)             | 80                               | >10               | 0.1               | 1.3                | 0.015             | 0.08            | 0.22                   |

| FoM1 (ps)<br>(smaller is better)                 | 2750                             | 9.57              | 199               | 10.4               | 6.7               | 227             | 0.37                   |

| FoM2 (pF)<br>(smaller is better)                 | 0.57                             | 1.914             | 0.47              | 0.19               | 3.73              | 0.68            | 0.036                  |

| Adaptive frequency for stability                 | Х                                | Х                 | V                 | Х                  | Х                 | Х               | V                      |

Table 2. Performance summary of this work and comparison with state-of-the-art designs.

N.R. stands for "data not revealed".

## 5. Conclusions

This paper presents an event-driven self-clocked digital low-dropout regulator with adaptive frequency control. The measurement results based on the prototype chips in the 40 nm CMOS process demonstrate the peak current efficiency of 99.96% at 0.85 V V<sub>IN</sub> and 0.5 V V<sub>OUT</sub>. We propose a clock frequency adapting technique to improve stability and transient recovery time to 220 ns. The proposed DLDO achieves a fast transient response and low power consumption without any external clocking signal. The total quiescent current is only 26  $\mu$ A in the steady-state. The comparison table shows that the proposed DLDO is the only work that achieves adaptive frequency for stability without a complex compensation circuit and achieves FoM improvement over the previous works. No external clock and related supply current are required compared to previous work.

**Author Contributions:** Y.-M.C. substantially contributed to the control strategy design, development and implementation of the overall system, analysis and interpretation of the results, and writing and revision of the manuscript. C.-J.C. substantially contributed to the project and research management, review and proofreading of the manuscript. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported in part by Qyi Now Co., Ltd., Taiwan; and in part by the Ministry of Science and Technology, Taiwan.

**Data Availability Statement:** No new data were created or analyzed in this study. Data sharing is not applicable to this article.

Acknowledgments: The authors want to thank Taiwan Semiconductor Research Institute (TSRI), Taiwan, and Taiwan Semiconductor Manufacturing Company (TSMC), Taiwan, for chip fabrication support. The authors also want to thank SIMPLIS Technologies Corporation, USA, for providing SIMPLIS simulation tool.

Conflicts of Interest: The authors declare no conflict of interest.

# References

- 1. Ho, M.; Leung, K.N.; Mak, K.L. A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages. *IEEE J. Solid-State Circuits* **2010**, *45*, 2466–2475. [CrossRef]

- 2. Cai, C.; Lu, Y.; Zhan, C.; Martins, R.P. A fully integrated FVF LDO with enhanced full-spectrum power supply rejection. *IEEE Trans. Power Electron.* **2021**, *36*, 4326–4337. [CrossRef]

- Yuk, Y.S.; Jung, S.; Kim, C.; Gwon, H.D.; Choi, S.; Cho, G.H. PSR enhancement through super gain boosting and differential feed-forward noise cancellation in a 65-nm CMOS LDO regulator. *IEEE Trans. Very Large Scale Integr. Syst.* 2014, 22, 2181–2191. [CrossRef]

- 4. Aviles, F.L.; Torres, J.; Sinencio, E.S. A high power supply rejection and fast settling time capacitor-less LDO. *IEEE Trans. Power Electron.* **2019**, *34*, 474–484. [CrossRef]

- Roldan, J.Z.; Wang, M.; Torres, J.; Sinencio, E.S. A capacitor-less LDO with high-frequency PSR suitable for a wide range of On-chip capacitive loads. *IEEE Trans. Very Large Scale Integr. Syst.* 2016, 24, 2970–2982. [CrossRef]

- Okuma, Y.; Ishida, K.; Ryu, Y.; Zhang, X.; Chen, P.H.; Watanabe, K.; Takamiya, M.; Sakurai, T. 0.5-V input digital LDO with 98.7% current efficiency and 2.7-μA quiescent current in 65 nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC2010), San Jose, CA, USA, 19–22 September 2010; pp. 1–4.

- Lim, C.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. A 50-mA 99.2% peak current efficiency, 250-ns settling time digital low-dropout regulator with transient enhanced PI controller. *IEEE Trans. Very Large Scale Integr. Syst.* 2017, 25, 2360–2370. [CrossRef]

- 8. Chu, Y.C.; Chang-Chien, L.R. Digitally controlled low-dropout regulator with fast-transient and autotuning algorithms. *IEEE Trans. Power Electron.* **2013**, *28*, 4308–4317. [CrossRef]

- 9. Kang, J.G.; Park, J.; Jeong, M.G.; Yoo, C. Digital low-dropout regulator with voltage-controlled oscillator based control. *IEEE Trans. Power Electron.* 2022, *37*, 6951–6961. [CrossRef]

- 10. Huang, M.; Lu, Y.; Sin, S.W.; Us, P.; Martins, R.P. A fully integrated digital LDO with coarse–fine-tuning and burst-mode operation. *IEEE Trans. Circuits Syst. II Express Briefs.* **2016**, *63*, 683–687. [CrossRef]

- Ma, X.; Lu, Y.; Martins, R.P.; Li, Q. A 0.4 V 430 nA quiescent current NMOS digital LDO with NAND-based analog-assisted loop in 28nm CMOS. In Proceedings of the IEEE International Solid—State Circuits Conference (ISSCC2018), San Francisco, CA, USA, 11–15 February 2018; pp. 306–308.

- Huang, M.; Lu, Y.; US, P.; Martins, R.P. An output-capacitor-free analog-assisted digital low-dropout regulator with tri-loop control. In Proceedings of the IEEE International Solid—State Circuits Conference (ISSCC2017), San Francisco, CA, USA, 5–9 February 2017; pp. 340–341.

- 13. Salem, L.G.; Warchall, J.; Mercier, P.P. A successive approximation recursive digital low dropout voltage regulator with PD compensation and sub-LSB duty control. *IEEE J. Solid-State Circuits* **2018**, *53*, 35–49. [CrossRef]

- 14. Huang, M.; Lu, Y.; Sin, S.W.; US, P.; Martins, R.P.; Ki, W.H. Limit cycle oscillation reduction for digital low dropout regulators. *IEEE Trans. Circuits Syst. II Express Briefs.* **2016**, *63*, 903–907. [CrossRef]

- Lee, Y.H.; Peng, S.Y.; Chiu, C.C.; Wu AC, H.; Chen, K.H.; Lin, Y.H.; Wang, S.W.; Tsai, T.Y.; Huang, C.C.; Lee, C.C. A low quiescent current asynchronous digital-LDO with PLL-modulated fast-DVS power management in 40 nm SoC for MIPS performance improvement. *IEEE J. Solid-State Circuits* 2013, 48, 1018–1030. [CrossRef]

- Chiu, C.C.; Huang, P.H.; Lin, M.; Chen, K.H.; Lin, Y.H.; Tsai, T.Y.; Huang, C.C.; Lee, C.C. A 0.6 V resistance-locked loop embedded digital low dropout regulator in 40 nm CMOS with 77% power supply rejection improvement. In Proceedings of the IEEE Symposium on VLSI Circuits (VLSI2013), Kyoto, Japan, 12–14 June 2013; pp. 166–167.

- 17. Yang, F.; Mok, P.K.T. Fast-transient asynchronous digital LDO with load regulation enhancement by soft multi-step switching and adaptive timing techniques in 65-nm CMOS. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC2015), San Jose, CA, USA, 28–30 September 2015; pp. 1–4.

- Oh, J.; Park, J.E.; Hwaung, Y.H.; Jeong, D.K. A 480 mA output-capacitor-free synthesizable digital LDO using CMP-triggered oscillator and droop detector with 99.99% current efficiency, 1.3ns response time, and 9.8A/mm<sup>2</sup> current density. In Proceedings of the IEEE International Solid—State Circuits Conference (ISSCC2020), San Francisco, CA, USA, 16–20 February 2020; pp. 382–384.

- 19. Kim, D.; Seok, M. A fully integrated digital low-dropout regulator based on event-driven explicit time-coding architecture. *IEEE J. Solid-State Circuits* **2017**, *52*, 3071–3080. [CrossRef]

- 20. Lee, Y.J.; Qu, W.; Singh, S.; Kim, D.Y.; Kim, K.H.; Kim, S.H.; Park, J.J.; Cho, G.H. A 200-mA digital low drop-out regulator with coarse-fine dual loop in mobile application processor. *IEEE J. Solid-State Circuits* **2017**, *52*, 64–76. [CrossRef]

- 21. Akram, M.A.; Hong, W.; Hwang, I.C. Capacitorless self-clocked all-digital low-dropout regulator. *IEEE J. Solid-State Circuits* 2019, 54, 266–276. [CrossRef]

- Lin, J.H.; Ma, Y.S.; Huang, C.M.; Lin, L.C.; Cheng, C.H.; Chen, K.H.; Lin, Y.H.; Lin, S.R.; Tsai, T.Y. A high-efficiency and fast-transient digital-low-dropout regulator with the burst mode corresponding to the power-saving modes of DC-DC switching converters. In Proceedings of the IEEE International Solid—State Circuits Conference (ISSCC2018), San Francisco, CA, USA, 11–15 February 2018; pp. 314–316.

- Ahmed, Z.K.; Krishnamurthy, H.K.; Augustine, C.; Liu, X.; Weng, S.; Ravichandran, K.; Tschanz, J.W.; De, V. A variation-adaptive integrated computational digital LDO in 22 nm CMOS with fast transient response. In Proceedings of the IEEE Symposium on VLSI Circuits (VLSI2019), Kyoto, Japan, 9–14 June 2019; pp. 124–125.

- 24. Hazucha, P.; Karnik, T.; Bloechel, B.A.; Parsons, C.; Finan, D.; Borkar, S. Area-efficient linear regulator with ultra-fast load regulation. *IEEE J. Solid-State Circuits* **2005**, *40*, 933–940. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.